Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 16-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15324t-i-jq |

# **TABLE 2: PACKAGES**

| Device         | (S)PDIP | SOIC | SSOP | TSSOP | UQFN (4x4) |

|----------------|---------|------|------|-------|------------|

| PIC16(L)F15324 | •       | •    |      | •     | •          |

| PIC16(L)F15344 | •       | •    | •    |       | •          |

### 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear bits <4:3> and <1:0>, and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, refer to Section 36.0 "Instruction Set Summary".

Note 1: The <u>C and DC</u> bits operate as Borrow and <u>Digit Borrow</u> out bits, respectively, in subtraction.

## **REGISTER 4-1: STATUS: STATUS REGISTER**

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| _     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: | Read as '0' |

|---------|----------------|-------------|

|         |                |             |

bit 4 **TO:** Time-Out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

bit 3 PD: Power-Down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

bit 0 C: Carry/Borrow bit<sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)<sup>(1)</sup>

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

# REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|          |       | - Software Control |                 |                                    |           |

|----------|-------|--------------------|-----------------|------------------------------------|-----------|

| WDTCPS   | Value | Divider Ra         | atio            | Typical Time Out<br>(Fin = 31 kHz) | of WDTPS? |

| 11111(1) | 01011 | 1:65536            | 2 <sup>16</sup> | 2 s                                | Yes       |

| 11110    | 11110 |                    | _               |                                    |           |

| 10011    | 10011 | 1:32               | 2 <sup>5</sup>  | 1 ms                               | No        |

| 10010    | 10010 | 1:8388608          | 2 <sup>23</sup> | 256 s                              |           |

| 10001    | 10001 | 1:4194304          | 2 <sup>22</sup> | 128 s                              |           |

| 10000    | 10000 | 1:2097152          | 2 <sup>21</sup> | 64 s                               |           |

| 01111    | 01111 | 1:1048576          | 2 <sup>20</sup> | 32 s                               |           |

| 01110    | 01110 | 1:524299           | 2 <sup>19</sup> | 16 s                               |           |

| 01101    | 01101 | 1:262144           | 2 <sup>18</sup> | 8 s                                |           |

| 01100    | 01100 | 1:131072           | 2 <sup>17</sup> | 4 s                                |           |

| 01011    | 01011 | 1:65536            | 2 <sup>16</sup> | 2 s                                |           |

| 01010    | 01010 | 1:32768            | 2 <sup>15</sup> | 1 s                                |           |

| 01001    | 01001 | 1:16384            | 2 <sup>14</sup> | 512 ms                             | No        |

| 01000    | 01000 | 1:8192             | 2 <sup>13</sup> | 256 ms                             |           |

| 00111    | 00111 | 1:4096             | 2 <sup>12</sup> | 128 ms                             |           |

| 00110    | 00110 | 1:2048             | 2 <sup>11</sup> | 64 ms                              |           |

| 00101    | 00101 | 1:1024             | 2 <sup>10</sup> | 32 ms                              |           |

| 00100    | 00100 | 1:512              | 2 <sup>9</sup>  | 16 ms                              |           |

| 00011    | 00011 | 1:256              | 2 <sup>8</sup>  | 8 ms                               |           |

| 00010    | 00010 | 1:128              | 2 <sup>7</sup>  | 4 ms                               |           |

| 00001    | 00001 | 1:64               | 2 <sup>6</sup>  | 2 ms                               |           |

| 00000    | 00000 | 1:32               | 2 <sup>5</sup>  | 1 ms                               |           |

Note 1: 0b11111 is the default value of the WDTCPS bits.

# REGISTER 10-9: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|-----|---------|

| _     | _   | NVMIE   | NCO1IE  | _   | _   | _   | CWG1IE  |

| bit 7 |     |         |         |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| Unimplemented: Read as '0'.                                           |

|-----------------------------------------------------------------------|

| NVMIE: NVM Interrupt Enable bit                                       |

| 1 = NVM task complete interrupt enabled                               |

| 0 = NVM interrupt not enabled                                         |

| NCO1IE: NCO Interrupt Enable bit                                      |

| 1 = NCO rollover interrupt enabled                                    |

| 0 = NCO rollover interrupt disabled                                   |

| Unimplemented: Read as '0'.                                           |

| CWG1IE: Complementary Waveform Generator (CWG) 2 Interrupt Enable bit |

| 1 = CWG1 interrupt is enabled                                         |

| 0 = CWG1 interrupt disabled                                           |

|                                                                       |

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE7.

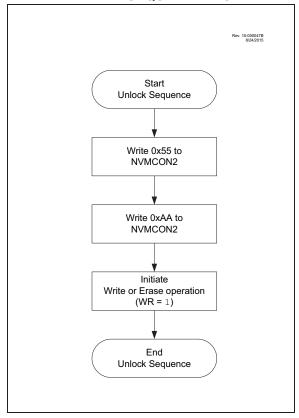

#### 13.3.2 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- · Load of PFM write latches

- · Write of PFM write latches to PFM memory

- · Write of PFM write latches to User IDs

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Note: The two NOP instructions after setting the WR bit that were required in previous devices are not required for PIC16(L)F15324/44 devices. See Figure 13-2.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

# FIGURE 13-2: NVM UNLOCK SEQUENCE FLOWCHART

# **EXAMPLE 13-2: NVM UNLOCK SEQUENCE**

```

INTCON, GIE

; Recommended so sequence is not interrupted

BANKSEL NVMCON1

NVMCON1, WREN

; Enable write/erase

BSF

MOVLW

55h

; Load 55h

; Step 1: Load 55h into NVMCON2

NVMCON2

MOVWF

AAh

; Step 2: Load W with AAh

MOVLW

; Step 3: Load AAH into NVMCON2

MOVWF

NVMCON2

BSF

NVMCON1, WR

; Step 4: Set WR bit to begin write/erase

BSF

INTCON, GIE

; Re-enable interrupts

```

Note 1: Sequence begins when NVMCON2 is written; steps 1-4 must occur in the cycle-accurate order shown.

2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

### REGISTER 14-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| _     | _   | SLRA5   | SLRA4   | _   | SLRA2   | SLRA1   | SLRA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-4 SLRA<5:4>: PORTA Slew Rate Enable bits

For RA<5:4> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

bit 3 **Unimplemented**: Read as '0'

bit 2-0 SLRA<2:0>: PORTA Slew Rate Enable bits

For RA<2:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 14-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

# REGISTER 14-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| R/W-0/0              | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| ODCC7 <sup>(1)</sup> | ODCC6 <sup>(1)</sup> | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 ODCC<7:0>: PORTC Open-Drain Enable bits

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

Note 1: Present on PIC16(L)F15344 only.

#### REGISTER 14-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

Note 1: Present on PIC16(L)F15344 only.

# REGISTER 14-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1                | R/W-1/1                | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------------------|------------------------|---------|---------|---------|---------|---------|---------|

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7                  |                        |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits

For RC<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

Note 1: Present on PIC16(L)F15344 only.

# REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

| R/W-0/0     | R/W-0/0 | U-0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |  |

|-------------|---------|-----|---------|-----|-----|-----|---------|--|

| UART2MD     | UART1MD | _   | MSSP1MD | _   | _   | _   | CWG1MD  |  |

| bit 7 bit 0 |         |     |         |     |     |     |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <b>UART2MD:</b> Disable EUSART2 bit 1 = EUSART2 module disabled 0 = EUSART2 module enabled |

|---------|--------------------------------------------------------------------------------------------|

| bit 6   | <b>UART1MD:</b> Disable EUSART1 bit 1 = EUSART1 module disabled 0 = EUSART1 module enabled |

| bit 5   | Unimplemented: Read as '0'                                                                 |

| bit 4   | MSSP1MD: Disable MSSP1 bit<br>1 = MSSP1 module disabled<br>0 = MSSP1 module enabled        |

| bit 3-1 | Unimplemented: Read as '0'                                                                 |

| bit 0   | <b>CWG1MD:</b> Disable CWG1 bit 1 = CWG1 module disabled 0 = CWG1 module enabled           |

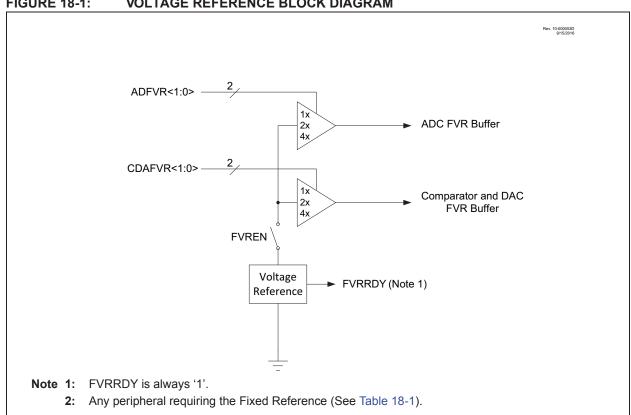

#### 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive and negative input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Fixed Voltage Reference output cannot Note: exceed VDD.

#### 18.1 **Independent Gain Amplifiers**

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference Section 20.0 "Analog-to-Digital Converter (ADC) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 23.0 "Comparator Module" for additional information.

#### **FVR Stabilization Period**

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. In the case of an LF device, or a device on which the BOR is enabled in the Configuration Word settings, then the FVRRDY bit will be high prior to setting FVREN as those module require the reference voltage.

**FIGURE 18-1:** VOLTAGE REFERENCE BLOCK DIAGRAM

**Preliminary** © 2017 Microchip Technology Inc. DS40001889A-page 221

### REGISTER 23-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | _   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 NCH<2:0>: Comparator Negative Input Channel Select bits

111 = CxVN connects to AVss

110 = CxVN connects to FVR Buffer 2

101 = CxVN unconnected

100 = CxVN unconnected

011 = CxVN connects to CxIN3- pin

010 = CxVN connects to CxIN2- pin

001 = CxVN connects to CxIN1- pin

000 = CxVN connects to CxIN0- pin

#### REGISTER 23-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | _   | _   |         | PCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 PCH<2:0>: Comparator Positive Input Channel Select bits

111 = CxVP connects to AVss

110 = CxVP connects to FVR Buffer 2

101 = CxVP connects to DAC output

100 = CxVP unconnected

011 = CxVP unconnected

010 = CxVP unconnected

001 = CxVP connects to CxIN1+ pin

000 = CxVP connects to CxIN0+ pin

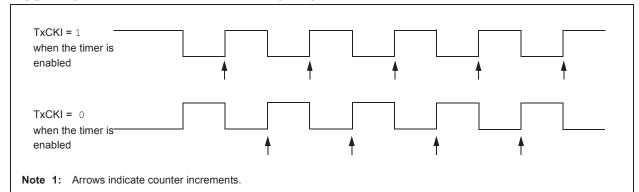

# FIGURE 26-2: TIMER1 INCREMENTING EDGE

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

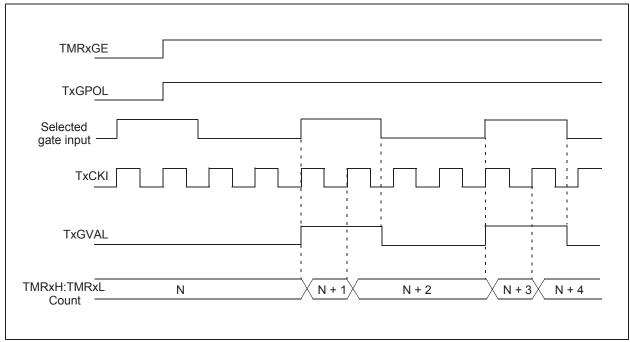

# FIGURE 26-3: TIMER1 GATE ENABLE MODE

# REGISTER 30-6: CWG1AS1: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 1

| U-1         | U-1 | U-1 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|-----|-----|---------|---------|---------|---------|---------|--|

| _           | _   | _   | AS4E    | AS3E    | AS2E    | AS1E    | AS0E    |  |

| bit 7 bit 0 |     |     |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                       |

|---------|--------------------------------------------------------------------------------------------------|

| bit 4   | AS4E: CLC2 Output bit                                                                            |

|         | 1 = LC2_out shut-down is enabled                                                                 |

|         | 0 = LC2_out shut-down is disabled                                                                |

| bit 3   | AS3E: Comparator C2 Output bit                                                                   |

|         | <ul><li>1 = C2 output shut-down is enabled</li><li>0 = C2 output shut-down is disabled</li></ul> |

| bit 2   | AS2E: Comparator C1 Output bit                                                                   |

|         | <ul><li>1 = C1 output shut-down is enabled</li><li>0 = C1 output shut-down is disabled</li></ul> |

| bit 2   | AS1E: TMR2 Postscale Output bit                                                                  |

|         | 1 = TMR2 Postscale shut-down is enabled                                                          |

|         | 0 = TMR2 Postscale shut-down is disabled                                                         |

| bit 0   | AS0E: CWG1 Input Pin bit                                                                         |

|         | 1 = Input pin selected by CWG1PPS shut-down is enabled                                           |

|         | 0 = Input pin selected by CWG1PPS shut-down is disabled                                          |

#### REGISTER 31-3: CLCxSEL0: GENERIC CLCx DATA 0 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|-------------------|---------|---------|---------|

| _     | _   |         |         | LCxD <sup>2</sup> | 1S<5:0> |         | _       |

| bit 7 |     |         |         |                   |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD1S<5:0>: CLCx Data1 Input Selection bits

See Table 31-2.

#### REGISTER 31-4: CLCxSeL1: GENERIC CLCx DATA 1 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | LCxD2   | 2S<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD2S<5:0>: CLCx Data 2 Input Selection bits

See Table 31-2.

#### REGISTER 31-5: CLCxSEL2: GENERIC CLCx DATA 2 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | LCxD    | 3S<5:0> |         | _       |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD3S<5:0>: CLCx Data 3 Input Selection bits

See Table 31-2.

### REGISTER 31-6: CLCxSeL3: GENERIC CLCx DATA 3 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | LCxD-   | 4S<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 LCxD4S<5:0>: CLCx Data 4 Input Selection bits

See Table 31-2.

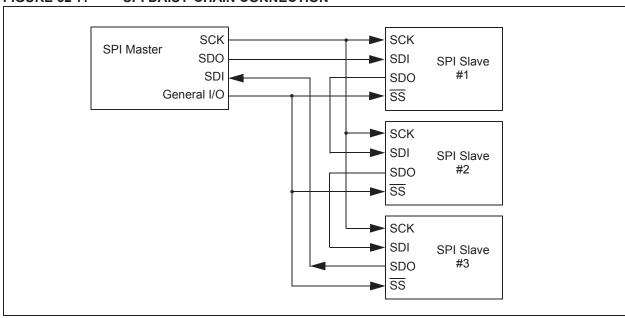

FIGURE 32-7: SPI DAISY-CHAIN CONNECTION

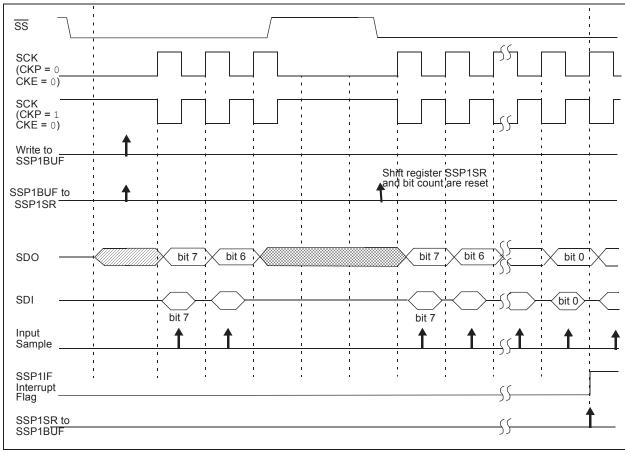

FIGURE 32-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

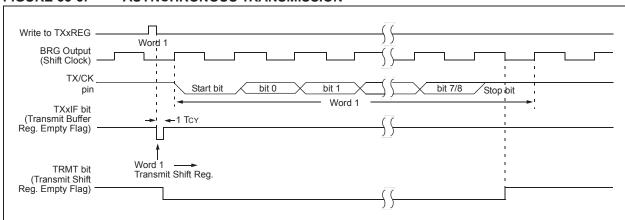

#### 33.1.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

# 33.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 33.1.2.7 "Address Detection"** for more information on the Address mode.

#### 33.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- If interrupts are desired, set the TXxIE interrupt enable bit of the PIE3 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

#### 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

# 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 33.4.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- The first character will immediately transfer to the TSR register and transmit.

- The second word will remain in the TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

# 33.4.2.2 Synchronous Slave Transmission Set-up:

- Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

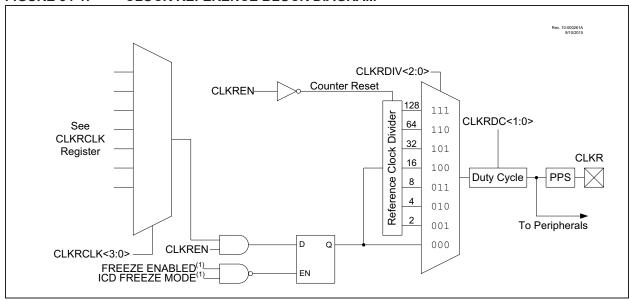

FIGURE 34-1: CLOCK REFERENCE BLOCK DIAGRAM

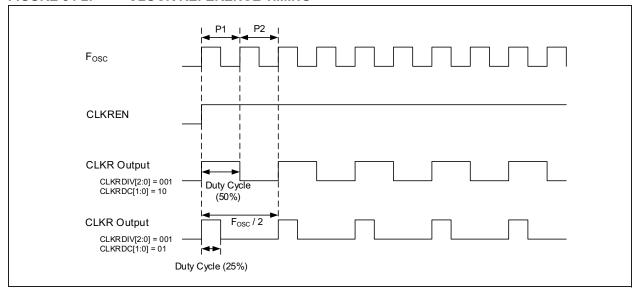

# FIGURE 34-2: CLOCK REFERENCE TIMING

| BCF              | Bit Clear f                           |

|------------------|---------------------------------------|

| Syntax:          | [ label ] BCF f,b                     |

| Operands:        | $ 0 \le f \le 127 $ $ 0 \le b \le 7 $ |

| Operation:       | $0 \rightarrow (f < b >)$             |

| Status Affected: | None                                  |

| Description:     | Bit 'b' in register 'f' is cleared.   |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                               |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         |

| Operands:        | $-256 \le label - PC + 1 \le 255$<br>$-256 \le k \le 255$                                                                                                                                                                     |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSS f,b                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                          |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed. If bit 'b' is '1', then the next instruction is discarded and a $\mathtt{NOP}$ is executed instead, making this a 2-cycle instruction. |

| BRW              | Relative Branch with W                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                           |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                           |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction. |

| BSF              | Bit Set f                         |

|------------------|-----------------------------------|

| Syntax:          | [ label ] BSF f,b                 |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$         |

| Status Affected: | None                              |

| Description:     | Bit 'b' in register 'f' is set.   |

**Preliminary** © 2017 Microchip Technology Inc. DS40001889A-page 465

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVIW ++FSRn<br>[ label ] MOVIWFSRn<br>[ label ] MOVIW FSRn++<br>[ label ] MOVIW FSRn<br>[ label ] MOVIW k[FSRn]                                                                                                                 |

| Operands:        | $n \in [0,1]$<br>$mm \in [00,01, 10, 11]$<br>$-32 \le k \le 31$                                                                                                                                                                            |

| Operation:       | INDFn → W Effective address is determined by • FSR + 1 (preincrement) • FSR - 1 (predecrement) • FSR + k (relative offset) After the Move, the FSR value will be either: • FSR + 1 (all increments) • FSR - 1 (all decrements) • Unchanged |

| Status Affected: | Z                                                                                                                                                                                                                                          |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

| Description: | This instruction is used to move data |

|--------------|---------------------------------------|

|              | between W and one of the indirect     |

registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

# MOVLB Move literal to BSR

Syntax: [ label ] MOVLB k

$$\label{eq:continuity} \begin{split} & \text{Operands:} & & 0 \leq k \leq \\ & \text{Operation:} & & k \to BSR \\ & \text{Status Affected:} & & \text{None} \end{split}$$

Description: The 6-bit literal 'k' is loaded into the

Bank Select Register (BSR).

| MOVLP            | Move literal to PCLATH                                    |

|------------------|-----------------------------------------------------------|

| Syntax:          | [ label ] MOVLP k                                         |

| Operands:        | $0 \leq k \leq 127$                                       |

| Operation:       | $k \rightarrow PCLATH$                                    |

| Status Affected: | None                                                      |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register. |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVLW k                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction W = 0x5A                                                                |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| Words:           | 1                                          |  |  |  |  |  |

| Cycles:          | 1                                          |  |  |  |  |  |

| Example:         | MOVWF LATA                                 |  |  |  |  |  |

|                  | Before Instruction                         |  |  |  |  |  |

|                  | LATA = 0xFF                                |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |

|                  | After Instruction                          |  |  |  |  |  |

|                  | LATA = 0x4F                                |  |  |  |  |  |

W = 0x4F

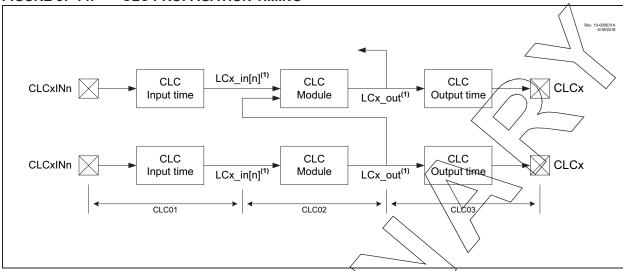

FIGURE 37-14: CLC PROPAGATION TIMING

# TABLE 37-20: CONFIGURABLE LOGIC CELL (CLC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +125°C |         |                                             |          |          |      |          |                          |  |  |

|----------------------------------------------------------------------------------------------------|---------|---------------------------------------------|----------|----------|------|----------|--------------------------|--|--|

| Param.<br>No.                                                                                      | Sym.    | Characteristic                              | Min.     | Typt     | Max. | Units    | Conditions               |  |  |

| CLC01*                                                                                             | TCLCIN  | CLC input time                              |          | 7        | 105  | ns       | (Note 1)                 |  |  |

| CLC02*                                                                                             | TCLC    | CLC module input to output propagation time | <u> </u> | 24<br>12 | _    | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |  |  |

| CLC03*                                                                                             | TCLCOUT | CLC output time Rise Time                   | _        | 107      | _    | _        | (Note 1)                 |  |  |

|                                                                                                    |         | Fall Time                                   | _        | IO8      | l    | _        | (Note 1)                 |  |  |

| CLC04*                                                                                             | FCLCMAX | CLC maximum switching frequency             | _        | 32       | Fosc | MHz      |                          |  |  |

- \* These parameters are characterized but not/tested.

- † Data in "Typ" column is at 3.0% 25 c unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Table 37-10 for 105, 107 and 108 rise and fall times.