Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | 14-TSSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15324t-i-st |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.3 Master Clear (MCLR) Pin

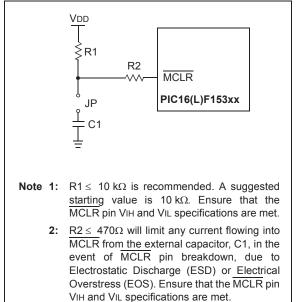

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP<sup>™</sup> Pins

The ICSPCLK and ICSPDAT pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the ICSPCLK and ICSPDAT pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., ICSPCLK/ICSPDAT pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/ emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 39.0 "Development Support**".

| TABLE 4-10: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 ( | CONTINUED |  |

|-------------|------------------------------------------------|-----------|--|

|                  |                                                 | AL I UNUTION |       | ••••••• |              |       |        |           |       |                       |                            |

|------------------|-------------------------------------------------|--------------|-------|---------|--------------|-------|--------|-----------|-------|-----------------------|----------------------------|

| Address          | Name                                            | Bit 7        | Bit 6 | Bit 5   | Bit 4        | Bit 3 | Bit 2  | Bit 1     | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 12          | Bank 12                                         |              |       |         |              |       |        |           |       |                       |                            |

|                  | CPU CORE REGISTERS; see Table 4-3 for specifics |              |       |         |              |       |        |           |       |                       |                            |

| 60Ch             | CWG1CLKCON                                      | _            | _     | —       | _            | —     | _      | _         | CS    | 0                     | 0                          |

| 60Dh             | CWG1DAT                                         | —            | _     | —       | — — DAT<3:0> |       |        |           |       | 0000                  | 0000                       |

| 60Eh             | CWG1DBR                                         | —            | —     |         | DBR<5:0>     |       |        |           |       |                       | 00 0000                    |

| 60Fh             | CWG1DBF                                         | —            | _     |         |              | DB    | F<5:0> |           |       | 00 0000               | 00 0000                    |

| 610h             | CWG1CON0                                        | EN           | LD    | —       | —            | —     |        | MODE<2:0> | >     | 00000                 | 00000                      |

| 611h             | CWG1CON1                                        | —            | —     | IN      | —            | POLD  | POLC   | POLB      | POLA  | x- 0000               | u- 0000                    |

| 612h             | CWG1AS0                                         | SHUTDOWN     | REN   | LSBD    | <2:0>        | LSAC  | <2:0>  | —         | —     | 0001 01               | 0001 01                    |

| 613h             | CWG1AS1                                         | —            | —     | —       | AS4E         | AS3E  | AS2E   | AS1E      | AS0E  | 0 0000                | u 0000                     |

| 614h             | CWG1STR                                         | OVRD         | OVRC  | OVRB    | OVRA         | STRD  | STRC   | STRB      | STRA  | 0000 0000             | 0000 0000                  |

| 615h<br><br>61Fh | — Unimplemented                                 |              |       |         |              |       |        | _         | _     |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| IABLE 4            | I-IU. SPECI | AL FUNCTION | REGISTER | SUMMAR I         | DANKS U-      |                   |           | 1           |           |                       | I                          |

|--------------------|-------------|-------------|----------|------------------|---------------|-------------------|-----------|-------------|-----------|-----------------------|----------------------------|

| Address            | Name        | Bit 7       | Bit 6    | Bit 5            | Bit 4         | Bit 3             | Bit 2     | Bit 1       | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 17            |             |             |          |                  |               |                   |           |             |           |                       | •                          |

|                    |             |             |          | CPU COF          | RE REGISTERS; | see Table 4-3 for | specifics |             |           |                       |                            |

| 88Ch               | CPUDOZE     | IDLEN       | DOZEN    | ROI              | DOE           | _                 | DOZE2     | DOZE1       | DOZE0     | 0000 -000             | u000 -000                  |

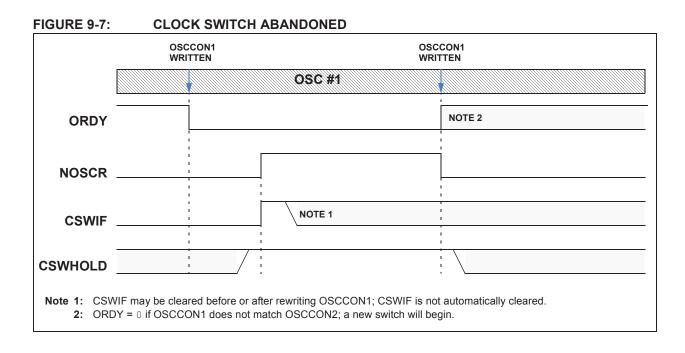

| 88Dh               | OSCCON1     | _           |          | NOSC<2:0>        |               |                   | NDIV<3:0> |             |           |                       | -qqq 0000                  |

| 88Eh               | OSCCON2     | _           |          | COSC<2:0>        |               | CDIV<3:0>         |           |             | -ddd dddd | -ddd dddd             |                            |

| 88Fh               | OSCCON3     | CSWHOLD     | _        | —                | ORDY          | NOSCR             | —         | —           |           | 00 0                  | 00 0                       |

| 890h               | OSCSTAT     | EXTOR       | HFOR     | MFOR             | LFOR          | _                 | ADOR      | —           | PLLR      | q000 -q-0             | dddd -d-d                  |

| 891h               | OSCEN       | EXTOEN      | HFOEN    | MFOEN            | LFOEN         | _                 | ADOEN     | —           | _         | 0000 -0               | 0000 -0                    |

| 892h               | OSCTUNE     | _           | _        |                  | •             | HFT               | UN<5:0>   |             |           | 10 0000               | 10 0000                    |

| 893h               | OSCFRQ      | _           | _        | —                | —             | _                 |           | HFFRQ<2:0   | >         | ddd                   | ddd                        |

| 894h               | _           |             |          |                  | Unimpler      | mented            | •         |             |           | _                     | _                          |

| 895h               | CLKRCON     | CLKREN      | _        | _                | CLKRD         | )C<1:0>           |           | CLKRDIV<2:0 | )>        | 0x xxxx               | 0u uuuu                    |

| 896h               | CLKRCLK     | _           | _        | — — CLKRCLK<3:0> |               |                   |           |             | 0000      | 0000                  |                            |

| 897h Unimplemented |             |             |          |                  |               |                   | _         | _           |           |                       |                            |

# TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15324/44

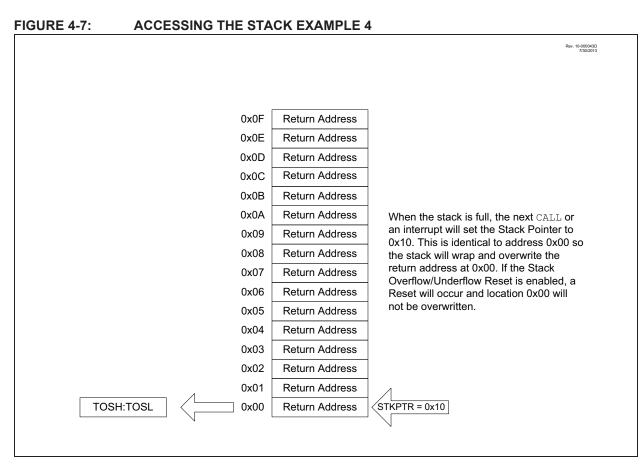

# 4.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words (Register 5-2) is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

# 4.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional/Banked Data Memory

- Linear Data Memory

- Program Flash Memory

# 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing.

Refer to Table 7-1 for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

| TABLE 7-1: | DEVICE CONFIGURATION INFORMATION FOR PIC16(L)F15324/44 DEVICES |

|------------|----------------------------------------------------------------|

|            |                                                                |

| ADDRESS      | Nomo        | Name DESCRIPTION VALUE  |       | UNITS   |

|--------------|-------------|-------------------------|-------|---------|

| ADDRESS Name | DESCRIPTION | PIC16(L)F15324/44       |       |         |

| 8200h        | ERSIZ       | Erase Row Size          | 32    | Words   |

| 8201h        | WLSIZ       | Number of write latches | 32    | Latches |

| 8202h        | URSIZ       | Number of User Rows     | 128   | Rows    |

| 8203h        | EESIZ       | EE Data memory size     | 0     | Bytes   |

| 8204h        | PCNT        | Pin Count               | 14/20 | Pins    |

# 7.1 DIA and DCI Access

The DIA and DCI data are read-only and cannot be erased or modified. See 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

# 11.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-on-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 11-1, the interrupt occurs during the  $2^{nd}$  instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

# 11.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the IDLE mode (Section 11.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The  $\overline{PD}$  bit of the STATUS register is cleared

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set

- 4. CPU Clock and System Clock

- 5. 31 kHz LFINTOSC, HFINTOSC are unaffected and peripherals using them may continue operation in Sleep.

- 6. ADC is unaffected if the dedicated FRC oscillator is selected the conversion will be left abandoned if FOSC is selected and ADRES will have an incorrect value

- 7. I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance). This does not apply in the case of any asynchronous peripheral which is active and may affect the I/O port value

- 8. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Any module with a clock source that is not Fosc can be enabled. Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module", Section 18.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 11.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.12 "Memory Execution Violation**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

# 11.4 Register Definitions: Voltage Regulator and DOZE Control

| U-0              | U-0   | U-0               | U-0  | U-0                                                | U-0 | R/W-0/0 | U-1   |  |  |

|------------------|-------|-------------------|------|----------------------------------------------------|-----|---------|-------|--|--|

| —                | —     | —                 | _    | —                                                  | —   | VREGPM  | —     |  |  |

| bit 7            |       |                   |      |                                                    |     |         | bit 0 |  |  |

|                  |       |                   |      |                                                    |     |         |       |  |  |

| Legend:          |       |                   |      |                                                    |     |         |       |  |  |

| R = Readable b   | oit   | W = Writable I    | oit  | U = Unimplemented bit, read as '0'                 |     |         |       |  |  |

| u = Bit is uncha | anged | x = Bit is unkn   | own  | -n/n = Value at POR and BOR/Value at all other Res |     |         |       |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                                                    |     |         |       |  |  |

|                  |       |                   |      |                                                    |     |         |       |  |  |

# **REGISTER 11-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

bit 7-2 Unimplemented: Read as '0'

VREGPM: Voltage Regulator Power Mode Selection bit

1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

Draws lowest current in Sleep, slower wake-up

Normal Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

bit 0 Unimplemented: Read as '1'. Maintain this bit set

Note 1: PIC16F15324/44 only.

bit 1

2: See Section 37.0 "Electrical Specifications".

| EXAMPI   | LE 13-4: \   | WRITING TO PROGRAM       | FLASH MEMORY                                       |

|----------|--------------|--------------------------|----------------------------------------------------|

|          |              | ine assumes the followir |                                                    |

| ; 1. 6   | 4 bytes of d | lata are loaded, startin | g at the address in DATA ADDR                      |

| ; 2. Ea  | ach word of  | data to be written is m  | ade up of two adjacent bytes in DATA_ADDR,         |

| ; st     | tored in lit | tle endian format        |                                                    |

| ; 3. A   | valid start  | ing address (the least   | significant bits = 00000) is loaded in ADDRH:ADDRL |

| ; 4. Al  | DDRH and ADD | ORL are located in commo | n RAM (locations 0x70 - 0x7F)                      |

| ; 5. NY  | VM interrupt | ts are not taken into ac | count                                              |

|          | BANKSEL      | NVMADRH                  |                                                    |

|          | MOVF         | ADDRH,W                  |                                                    |

|          | MOVWF        | NVMADRH                  | ; Load initial address                             |

|          | MOVF         | ADDRL,W                  |                                                    |

|          | MOVWF        | NVMADRL                  |                                                    |

|          | MOVLW        | LOW DATA ADDR            | ; Load initial data address                        |

|          | MOVWF        | <br>FSROL                |                                                    |

|          | MOVLW        | HIGH DATA ADDR           |                                                    |

|          | MOVWF        | FSR0H                    |                                                    |

|          | BCF          | NVMCON1, NVMREGS         | ; Set Program Flash Memory as write location       |

|          | BSF          | NVMCON1,WREN             | ; Enable writes                                    |

|          | BSF          | NVMCON1, LWLO            | ; Load only write latches                          |

| LOOP     |              |                          |                                                    |

|          | MOVIW        | FSR0++                   |                                                    |

|          | MOVWF        | NVMDATL                  | ; Load first data byte                             |

|          | MOVIW        | FSR0++                   |                                                    |

|          | MOVWF        | NVMDATH                  | ; Load second data byte                            |

|          | MOVF         | NVMADRL,W                |                                                    |

|          | XORLW        | 0x1F                     | ; Check if lower bits of address are 00000         |

|          | ANDLW        | 0 x 1 F                  | ; and if on last of 32 addresses                   |

|          | BTFSC        | STATUS,Z                 | ; Last of 32 words?                                |

|          | GOTO         | START_WRITE              | ; If so, go write latches into memory              |

|          | CALL         | UNLOCK SEQ               | ; If not, go load latch                            |

|          | INCF         | NVMADRL, F               | ; Increment address                                |

|          | GOTO         | LOOP                     |                                                    |

| START    | WRITE        |                          |                                                    |

| _        | BCF          | NVMCON1, LWLO            | ; Latch writes complete, now write memory          |

|          | CALL         | UNLOCK SEQ               | ; Perform required unlock sequence                 |

|          | BCF          | NVMCON1, WREN            | ; Disable writes                                   |

| UNLOCK   | SEO          |                          |                                                    |

| 01120011 | MOVLW        | 55h                      |                                                    |

|          | BCF          | INTCON, GIE              | ; Disable interrupts                               |

|          | MOVWF        | NVMCON2                  | ; Begin unlock sequence                            |

|          | MOVLW        | AAh                      |                                                    |

|          | MOVWF        | NVMCON2                  |                                                    |

|          | BSF          | NVMCON1,WR               |                                                    |

|          | BSF          | INTCON, GIE              | ; Unlock sequence complete, re-enable interrupts   |

|          | return       |                          |                                                    |

|          |              |                          |                                                    |

| R/W-0/0                               | R/W-0/0        | R/W-0/0            | R/W-0/0       | U-0            | U-0              | U-0              | U-0         |

|---------------------------------------|----------------|--------------------|---------------|----------------|------------------|------------------|-------------|

| WPUB7                                 | WPUB6          | WPUB5              | WPUB4         | _              | _                | —                | _           |

| bit 7                                 |                |                    |               |                |                  |                  | bit 0       |

|                                       |                |                    |               |                |                  |                  |             |

| Legend:                               |                |                    |               |                |                  |                  |             |

| R = Readable                          | bit            | W = Writable       | bit           | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch                       | anged          | x = Bit is unknown |               | -n/n = Value a | at POR and BOF   | R/Value at all o | ther Resets |

| '1' = Bit is set '0' = Bit is cleared |                |                    | ared          |                |                  |                  |             |

|                                       |                |                    |               |                |                  |                  |             |

| bit 7-4                               | WPUB<7:4>:     | Weak Pull-up       | Register bits |                |                  |                  |             |

|                                       | 1 = Pull-up ei | nabled             |               |                |                  |                  |             |

## REGISTER 14-13: WPUB: WEAK PULL-UP PORTB REGISTER

| bit 7-4 | WPUB<7:4>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Pull-up enabled                   |

|         | 0 = Pull-up disabled                  |

| bit 3-0 | Unimplemented: Read as '0'            |

# REGISTER 14-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 |  |

|---------|---------|---------|---------|-----|-----|-----|-----|--|

| ODCB7   | ODCB6   | ODCB5   | ODCB4   | _   | —   | —   | _   |  |

| bit 7   |         |         |         |     |     |     |     |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | <b>ODCB&lt;7:4&gt;:</b> PORTB Open-Drain Enable bits<br>For RB<7:4> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                                                             |

#### 28.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 28.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (FOSC/4).             |

### 28.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 28-1 demonstrates the code to perform this function.

#### EXAMPLE 28-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

| 1       |             |                         |

### 28.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

# 28.2 Compare Mode

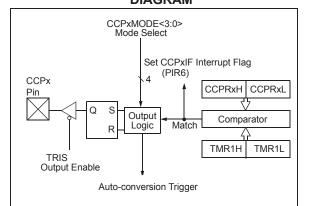

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 28-2 shows a simplified diagram of the compare operation.

#### FIGURE 28-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 28.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See Section 15.0 "Peripheral Pin Select (PPS) Module" for more details.

The CCP output can also be used as an input for other peripherals.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 28.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 28.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to Section 20.2.4 "Auto-Conversion Trigger" for more information.

| Note: | Removing the match condition by            |

|-------|--------------------------------------------|

|       | changing the contents of the CCPRxH        |

|       | and CCPRxL register pair, between the      |

|       | clock edge that generates the              |

|       | Auto-conversion Trigger and the clock      |

|       | edge that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring          |

#### 28.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

# 28.3 **PWM Overview**

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

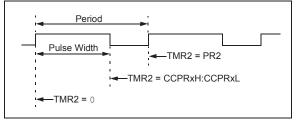

Figure 28-3 shows a typical waveform of the PWM signal.

#### 28.3.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 28-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 28-3: C

CCP PWM OUTPUT SIGNAL

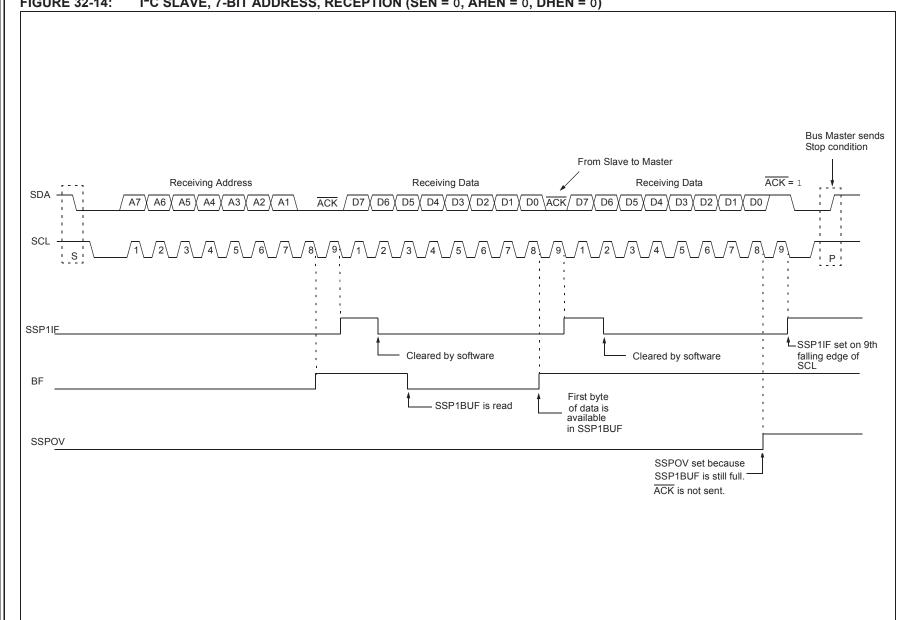

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0) **FIGURE 32-14:**

PIC16(L)F15324/4

#### **REGISTER 32-2:** SSP1CON1: SSP1 CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                       | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                                                                                               | R/W-0/0                                                                                                                             | R/W-0/0                                    | R/W-0/0                                       | R/W-0/0                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------------------------|

| WCOL              | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                             | SSPEN                                                                                                                                              | CKP                                                                                                                                                                                   |                                                                                                                                     | SSPM                                       | <3:0>                                         |                                            |

| pit 7             | ÷                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                  | ·                                                                                                                                                                                     | •                                                                                                                                   |                                            |                                               | bit                                        |

|                   |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |                                                                                                                                                                                       |                                                                                                                                     |                                            |                                               |                                            |

| _egend:           |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |                                                                                                                                                                                       |                                                                                                                                     |                                            |                                               |                                            |

| R = Readable bi   | it                                                                                                                                                                                                                                                                                                                               | W = Writable bit                                                                                                                                   |                                                                                                                                                                                       | U = Unimplement                                                                                                                     | ed bit, read as '0'                        |                                               |                                            |

| u = Bit is unchar | nged                                                                                                                                                                                                                                                                                                                             | x = Bit is unknow                                                                                                                                  | 'n                                                                                                                                                                                    | -n/n = Value at PC                                                                                                                  | OR and BOR/Value                           | at all other Resets                           |                                            |

| 1' = Bit is set   |                                                                                                                                                                                                                                                                                                                                  | '0' = Bit is cleared                                                                                                                               | d                                                                                                                                                                                     | HS = Bit is set by                                                                                                                  | hardware                                   | C = User cleared                              |                                            |

| bit 7             |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |                                                                                                                                                                                       | ()<br>smitting the previous                                                                                                         | word (must be cleare                       | ed in software)                               |                                            |

| bit 6             | In SPI mode:<br>1 = A new byte<br>lost. Overfli<br>avoid settin<br>to the SSP<br>0 = No overfloo<br>In I <sup>2</sup> C mode:<br>1 = A byte is n                                                                                                                                                                                 | ow can only occur in<br>ng overflow. In Maste<br>1BUF register (must<br>w<br>eceived while the S<br>leared in software).                           | e SSP1BUF regist<br>Slave mode. In Sl<br>r mode, the overflo<br>be cleared in softv<br>SP1BUF register                                                                                | er is still holding the p<br>ave mode, the user r<br>w bit is not set since e<br>vare).<br>is still holding the p                   | nust read the SSP1<br>each new reception ( | BUF, even if only tra<br>and transmission) is | nsmitting data, to<br>initiated by writing |

| bit 5             | In both modes, v<br>In <u>SPI mode:</u><br>1 = Enables se<br>0 = Disables s<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                                                      | erial port and configu<br>erial port and config                                                                                                    | ollowing pins mus<br>res SCK, SDO, SE<br>jures these pins a<br>rigures the SDA an                                                                                                     | d SCL pins as the so                                                                                                                | rce of the serial port                     | pins <sup>(2)</sup>                           |                                            |

| bit 4             | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCL release cor<br>1 = Enable clock                                                                                                                                                                                                                                       | c clock is a high leve<br>clock is a low level<br><u>de:</u><br>htrol<br>(<br>low (clock stretch).                                                 |                                                                                                                                                                                       | ata setup time.)                                                                                                                    |                                            |                                               |                                            |

| bit 3-0           | 1111 = I <sup>2</sup> C Slav<br>1110 = I <sup>2</sup> C Slav<br>1101 = Reserve<br>1001 = Reserve<br>1011 = I <sup>2</sup> C firmv<br>1010 = SPI Mas<br>1001 = Reserve<br>1000 = I <sup>2</sup> C Mas<br>0111 = I <sup>2</sup> C Slav<br>0110 = SPI Slav<br>0101 = SPI Slav<br>0101 = SPI Mas<br>0001 = SPI Mas<br>0001 = SPI Mas | e mode, 7-bit addre<br>d<br>ware controlled Mas<br>ter mode, clock = F<br>d<br>ter mode, clock = Fi<br>e mode, 10-bit addre<br>e mode, 7-bit addre | ess with Start and<br>ss with Start and<br>ter mode (slave ic<br>osc/(4 * (SSP1AI<br>osc / (4 * (SSP1AI<br>osc / (4 * (SSP1A<br>osc / (4 * (SSP1A<br>osc / 64<br>osc / 64<br>osc / 16 | Stop bit interrupts e<br>Stop bit interrupts er<br>(lle)<br>(DD+1)) <sup>(5)</sup><br>DD+1)) <sup>(4)</sup><br>trol disabled, SS ca | nabled                                     | n                                             |                                            |

| 2: W<br>R>        | Master mode, the ov<br>hen enabled, these p<br>kyPPS to select the p<br>hen enabled, the SD.                                                                                                                                                                                                                                     | verflow bit is not set<br>bins must be proper<br>bins.                                                                                             | since each new r<br>ly configured as ir                                                                                                                                               | put or output. Use S                                                                                                                | SSP1SSPPS, SSP1                            | CLKPPS, SSP1DA                                | •                                          |

- When enabled, the SDA and SCL pins must be configured as inputs. Use SSP1CLKPPS, SSP1DATPPS, and RxyPPS to select the pins.

SSP1ADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- 5: SSP1ADD value of '0' is not supported. Use SSPM = 0000 instead.

# 33.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RXxIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCxREG is read after the overflow occurs but before the fifth rising edge then the fifth rising edge will set the RXxIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCxREG to clear RXxIF.

- 2. If RCIDL is '0' then wait for RDCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

# 33.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RXxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 33-7), and asynchronously if the device is in Sleep mode (Figure 33-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in IDLE mode waiting to receive the next character.

#### 33.3.3.1 Special Considerations

Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RXxIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# 34.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR).

The reference clock output module has the following features:

- Selectable input clock

- Programmable clock divider

- Selectable duty cycle

# 34.1 CLOCK SOURCE

The reference clock output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

# 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

# 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- Base clock value

- Base clock value divided by 2

- · Base clock value divided by 4

- Base clock value divided by 8

- · Base clock value divided by 16

- Base clock value divided by 32

- · Base clock value divided by 64

- Base clock value divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

# 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

# 34.4 OPERATION IN SLEEP MODE

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | <b>skip if (f<b>) =</b> 0</b>                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS            | Bit Test f, Skip if Set                                                                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRA label                                                                                                                                                                                                                             | Syntax:          | [ <i>label</i> ]BTFSS f,b                                                                                                                                        |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                                        | Operands:        | $0 \leq f \leq 127$                                                                                                                                              |

| Operands:        | $-256 \le label - PC + 1 \le 255$                                                                                                                                                                                                               |                  | $0 \le b < 7$                                                                                                                                                    |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                                            | Operation:       | skip if (f <b>) = 1</b>                                                                                                                                          |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   | Status Affected: | None                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                                                                                            | Description:     | If bit 'b' in register 'f' is '0', the next                                                                                                                      |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |                  | instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |

| BRW | Relative  | Branch | with W |

|-----|-----------|--------|--------|

|     | 1.0101110 | Branon | ****   |

| Syntax:          | [ label ] BRW                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

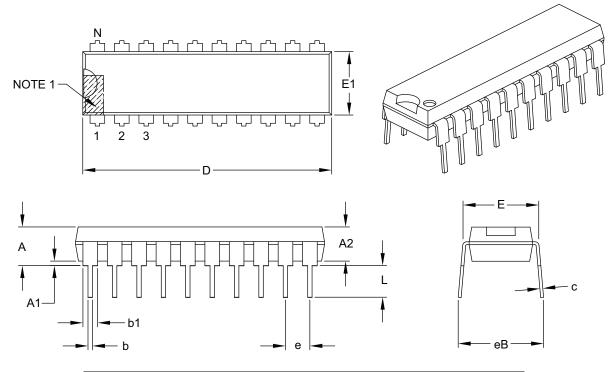

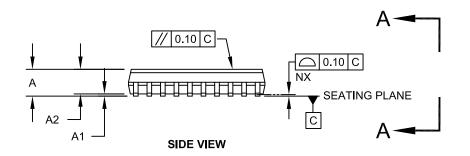

# 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |       |  |

|----------------------------|----------|------|----------|-------|--|

| Dimension                  | n Limits | MIN  | NOM      | MAX   |  |

| Number of Pins             | Ν        |      | 20       |       |  |

| Pitch                      | е        |      | .100 BSC |       |  |

| Top to Seating Plane       | Α        | -    | -        | .210  |  |

| Molded Package Thickness   | A2       | .115 | .130     | .195  |  |

| Base to Seating Plane      | A1       | .015 | -        | -     |  |

| Shoulder to Shoulder Width | Е        | .300 | .310     | .325  |  |

| Molded Package Width       | E1       | .240 | .250     | .280  |  |

| Overall Length             | D        | .980 | 1.030    | 1.060 |  |

| Tip to Seating Plane       | L        | .115 | .130     | .150  |  |

| Lead Thickness             | С        | .008 | .010     | .015  |  |

| Upper Lead Width           | b1       | .045 | .060     | .070  |  |

| Lower Lead Width           | b        | .014 | .018     | .022  |  |

| Overall Row Spacing §      | eВ       | _    | _        | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

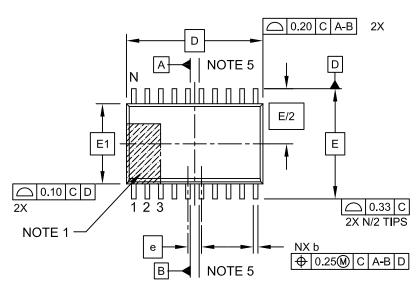

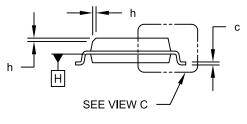

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

© 2017 Microchip Technology Inc.

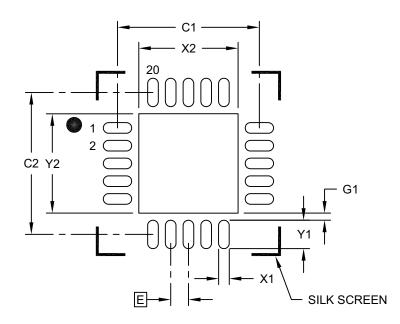

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

| Units                           |    | MILLIMETERS |      |      |

|---------------------------------|----|-------------|------|------|

| Dimension Limits                |    | MIN         | NOM  | MAX  |

| Contact Pitch                   | E  | 0.50 BSC    |      |      |

| Optional Center Pad Width       | X2 |             |      | 2.80 |

| Optional Center Pad Length      | Y2 |             |      | 2.80 |

| Contact Pad Spacing             | C1 |             | 4.00 |      |

| Contact Pad Spacing             | C2 |             | 4.00 |      |

| Contact Pad Width (X20)         | X1 |             |      | 0.30 |

| Contact Pad Length (X20)        | Y1 |             |      | 0.80 |

| Contact Pad to Center Pad (X20) | G1 | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2255A