# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15344-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC16(L)F15324/44 Microcontrollers    |     |

| 3.0  | Enhanced Mid-Range CPU                                                    |     |

| 4.0  | Memory Organization                                                       |     |

| 5.0  | Device Configuration                                                      |     |

| 6.0  | Device Information Area                                                   |     |

| 7.0  | Device Configuration Information                                          |     |

| 8.0  | Resets                                                                    |     |

| 9.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 10.0 | Interrupts                                                                | 121 |

| 11.0 | Power-Saving Operation Modes                                              |     |

| 12.0 | Windowed Watchdog Timer (WWDT)                                            | 150 |

|      | Nonvolatile Memory (NVM) Control                                          |     |

|      | I/O Ports                                                                 |     |

| 15.0 | Peripheral Pin Select (PPS) Module                                        |     |

| 16.0 | Peripheral Module Disable                                                 |     |

| 17.0 | Interrupt-On-Change                                                       |     |

| 18.0 | Fixed Voltage Reference (FVR)                                             |     |

| 19.0 | Temperature Indicator Module                                              |     |

| 20.0 | Analog-to-Digital Converter (ADC) Module                                  |     |

| 21.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           |     |

|      | Numerically Controlled Oscillator (NCO) Module                            |     |

|      | Comparator Module                                                         |     |

|      | Zero-Cross Detection (ZCD) Module                                         |     |

|      | Timer0 Module                                                             |     |

|      | Timer1 Module with Gate Control                                           |     |

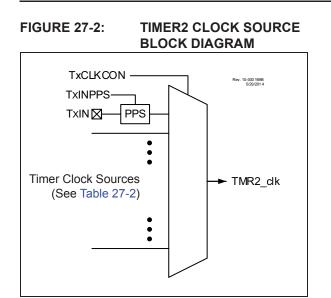

| 27.0 | Timer2 Module With Hardware Limit Timer (HLT)                             |     |

| 28.0 |                                                                           |     |

|      | Pulse-Width Modulation (PWM)                                              |     |

|      | Complementary Waveform Generator (CWG) Module                             |     |

|      | Configurable Logic Cell (CLC)                                             |     |

|      |                                                                           |     |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

|      | Reference Clock Output Module                                             |     |

|      | In-Circuit Serial Programming™ (ICSP™)                                    |     |

|      | Instruction Set Summary                                                   |     |

|      | Electrical Specifications                                                 |     |

| 38.0 |                                                                           |     |

| 39.0 | Development Support                                                       |     |

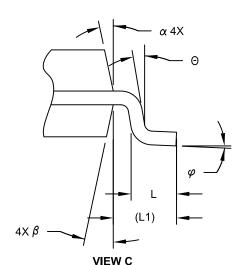

| 40.0 | Packaging Information                                                     | 508 |

#### **TABLE 4-6**: PIC16(L)F15324/44 MEMORY MAP, BANKS 16-23

|      | BANK 16                |      | BANK 17       |      | BANK 18       |      | BANK 19       |      | BANK 20       |      | BANK 21       |      | BANK 22       |      | BANK 23       |

|------|------------------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

| 800h |                        | 880h |               | 900h |               | 980h |               | A00h |               | A80h |               | B00h |               | B80h |               |

|      | Core Register          |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |

|      | (Table 4-3)            |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |

| 80Bh |                        | 88Bh |               | 90Bh |               | 98Bh |               | A0Bh |               | A8Bh |               | B0Bh |               | B8Bh |               |

| 80Ch | WDTCON0                | 88Ch | CPUDOZE       | 90Ch | FVRCON        | 98Ch | _             | A0Ch | —             | A8Ch |               | B0Ch | —             | B8Ch | _             |

| 80Dh | WDTCON1                | 88Dh | OSCCON1       | 90Dh |               | 98Dh | _             | A0Dh | —             | A8Dh |               | B0Dh | _             | B8Dh | _             |

| 80Eh | WDTL                   | 88Eh | OSCCON2       | 90Eh | DAC1CON0      | 98Eh | —             | A0Eh |               | A8Eh |               | B0Eh | _             | B8Eh | _             |

| 80Fh | WDTH                   | 88Fh | OSCCON3       | 90Fh | DAC1CON1      | 98Fh | CMOUT         | A0Fh |               | A8Fh |               | B0Fh | _             | B8Fh | _             |

| 810h | WDTU                   | 890h | OSCSTAT1      | 910h | —             | 990h | CM1CON0       | A10h | —             | A90h | —             | B10h | —             | B90h | —             |

| 811h | BORCON                 | 891h | OSCEN         | 911h | _             | 991h | CM1CON1       | A11h | _             | A91h |               | B11h | _             | B91h | —             |

| 812h | VREGCON <sup>(2)</sup> | 892h | OSCTUNE       | 912h | _             | 992h | CM1NCH        | A12h |               | A92h |               | B12h | _             | B92h | _             |

| 813h | PCON0                  | 893h | OSCFRQ        | 913h | _             | 993h | CM1PCH        | A13h | —             | A93h |               | B13h | _             | B93h | _             |

| 814h | PCON1                  | 894h | —             | 914h | —             | 994h | CM2CON0       | A14h | —             | A94h | —             | B14h | —             | B94h | —             |

| 815h | —                      | 895h | CLKRCON       | 915h | —             | 995h | CM2CON1       | A15h | —             | A95h | _             | B15h | —             | B95h | —             |

| 816h | _                      | 896h | CLKCLK        | 916h | —             | 996h | CM2NCH        | A16h | —             | A96h | —             | B16h | —             | B96h | —             |

| 817h | _                      | 897h | _             | 917h | _             | 997h | CM2PCH        | A17h | —             | A97h | _             | B17h | _             | B97h | _             |

| 818h | _                      | 898h | _             | 918h | _             | 998h | _             | A18h | —             | A98h | _             | B18h | _             | B98h | _             |

| 819h | _                      | 899h | _             | 919h | _             | 999h | _             | A19h | RC2REG        | A99h | _             | B19h | _             | B99h | _             |

| 81Ah | NVMADRL                | 89Ah | _             | 91Ah | _             | 99Ah | —             | A1Ah | TX2REG        | A9Ah | —             | B1Ah | _             | B9Ah | —             |

| 81Bh | NVMADRH                | 89Bh | _             | 91Bh | _             | 99Bh | —             | A1Bh | SP2BRGL       | A9Bh | —             | B1Bh | _             | B9Bh | _             |

| 81Ch | NVMDATL                | 89Ch | _             | 91Ch | _             | 99Ch | _             | A1Ch | SP2BRGH       | A9Ch | _             | B1Ch | _             | B9Ch | _             |

| 81Dh | NVMDATH                | 89Dh | _             | 91Dh | _             | 99Dh | _             | A1Dh | RC2STA        | A9Dh | —             | B1Dh | _             | B9Dh | —             |

| 81Eh | NVMCON1                | 89Eh | _             | 91Eh | _             | 99Eh | _             | A1Eh | TX2STA        | A9Eh | —             | B1Eh | _             | B9Eh | —             |

| 81Fh | NVMCON2                | 89Fh | —             | 91Fh | ZCDCON        | 99Fh | —             | A1Fh | BAUD2CON      | A9Fh | —             | B1Fh | —             | B9Fh | —             |

| 820h |                        | 8A0h |               | 920h |               | 9A0h |               | A20h |               | AA0h |               | B20h |               | BA0h |               |

|      | Unimplemented          |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |      | Unimplemented |

|      | Read as '0'            |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |

| 86Fh |                        | 8EFh |               | 96Fh |               | 9EFh |               | A6Fh |               | AEFh |               | B6Fh |               | BEFh |               |

| 870h | Common RAM             | 8F0h | Common RAM    | 970h | Common RAM    | 9F0h | Common RAM    | A70h | Common RAM    | AF0h | Common RAM    | B70h | Common RAM    | BF0h | Common RAM    |

|      | Accesses               |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |

| 87Fh | 70h-7Fh                | 8FFh | 70h-7Fh       | 97Fh | 70h-7Fh       | 9FFh | 70h-7Fh       | A7Fh | 70h-7Fh       | AFFh | 70h-7Fh       | B7Fh | 70h-7Fh       | BFFh | 70h-7Fh       |

Note1:Unimplemented locations read as '0'.2:Register not implemented on LF devices.

|                               |        |                           |                            |                                           |               |              |            |           |           | ,                     |                            |

|-------------------------------|--------|---------------------------|----------------------------|-------------------------------------------|---------------|--------------|------------|-----------|-----------|-----------------------|----------------------------|

| Bank Offset<br>Bank 0-Bank 63 | Name   | Bit 7                     | Bit 6                      | Bit 5                                     | Bit 4         | Bit 3        | Bit 2      | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| All Banks                     |        |                           |                            |                                           |               |              |            |           |           |                       |                            |

| x00h or x80h                  | INDF0  | Addressing<br>physical re | g this location<br>gister) | n uses cont                               | ents of FSF   | R0H/FSR0L    | to address | data memo | ry (not a | ****                  | XXXX XXXX                  |

| x01h or x81h                  | INDF1  | Addressing<br>physical re | g this location<br>gister) | n uses cont                               | ents of FSF   | R1H/FSR1L    | to address | data memo | ry (not a | XXXX XXXX             | XXXX XXXX                  |

| x02h or x82h                  | PCL    |                           |                            |                                           | PC            | CL           |            |           |           | 0000 0000             | 0000 0000                  |

| x03h or x83h                  | STATUS | —                         | —                          | _                                         | TO            | PD           | Z          | DC        | С         | 1 1000                | q quuu                     |

| x04h or x84h                  | FSR0L  | FSR0L                     | Indirect Da                | ndirect Data Memory Address 0 Low Pointer |               |              |            |           |           |                       | uuuu uuuu                  |

| x05h or x85h                  | FSR0H  | FSR0H                     | Indirect Da                | ta Memory                                 | Address 0 I   | High Pointe  | r          |           |           | 0000 0000             | 0000 0000                  |

| x06h or x86h                  | FSR1L  | FSR1L                     | Indirect Da                | ta Memory                                 | Address 1 I   | Low Pointer  |            |           |           | 0000 0000             | uuuu uuuu                  |

| x07h or x87h                  | FSR1H  | FSR1H                     | Indirect Da                | ta Memory                                 | Address 1 I   | High Pointe  | r          |           |           | 0000 0000             | 0000 0000                  |

| x08h or x88h                  | BSR    | —                         | —                          | — BSR<5:0>                                |               |              |            |           |           | 00 0000               | 00 0000                    |

| x09h or x89h                  | WREG   | Working R                 | egister                    |                                           |               |              |            |           |           | 0000 0000             | uuuu uuuu                  |

| x0Ah or x8Ah                  | PCLATH | —                         | Write Buffe                | r for the up                              | per 7 bits of | f the Progra | m Counter  |           |           | -000 0000             | -000 0000                  |

| x0Bh or x8Bh                  | INTCON | GIE                       | PEIE                       | —                                         | —             | —            | —          | _         | INTEDG    | 001                   | 001                        |

TABLE 4-9:

SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (ALL BANKS)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These Registers can be accessed from any bank.

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address             | Name                   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------------------|------------------------|------------------------|------------------------|---------|----------|---------|---------|---------|---------|-----------------------|----------------------------|

| Bank 62 (C          | Continued)             |                        | 1                      |         | 1        | 1       | I       | 1       |         |                       |                            |

| 1F38h               | ANSELA                 | _                      | _                      | ANSA5   | ANSA4    | _       | ANSA2   | ANSA1   | ANSA0   | 11 1111               | 11 1111                    |

| 1F39h               | WPUA                   | _                      | _                      | WPUA5   | WPUA4    | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 00 0000               | 00 0000                    |

| 1F3Ah               | ODCONA                 | _                      | _                      | ODCA5   | ODCA4    | _       | ODCA2   | ODCA1   | ODCA0   | 00 0000               | 00 0000                    |

| 1F3Bh               | SLRCONA                | —                      | _                      | SLRA5   | SLRA4    | —       | SLRA2   | SLRA1   | SLRA0   | 11 1111               | 11 1111                    |

| 1F3Ch               | INLVLA                 | _                      | _                      | INLVLA5 | INLVLA4  | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111               | 11 1111                    |

| 1F3Dh               | IOCAP                  | —                      | _                      | IOCAP5  | IOCAP4   | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000               | 00 0000                    |

| 1F3Eh               | IOCAN                  | _                      | _                      | IOCAN5  | IOCAN4   | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000               | 00 0000                    |

| 1F3Fh               | IOCAF                  | _                      | —                      | IOCAF5  | IOCAF4   | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000               | 00 0000                    |

| 1F40h<br>—<br>1F42h | _                      |                        |                        |         | Unimpler | nented  |         |         |         | _                     | _                          |

| 1F43h               | ANSELB <sup>(1)</sup>  | ANSB7                  | ANSB6                  | ANSB5   | ANSB4    | _       | _       | _       | _       | 1111                  | 1111                       |

| 1F44h               | WPUB <sup>(1)</sup>    | WPUB7                  | WPUB6                  | WPUB5   | WPUB4    | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F45h               | ODCONB <sup>(1)</sup>  | ODCB7                  | ODCB6                  | ODCB5   | ODCB4    | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F46h               | SLRCONB <sup>(1)</sup> | SLRB7                  | SLRB6                  | SLRB5   | SLRB4    | —       | _       | —       |         | 1111                  | 1111                       |

| 1F47h               | INLVLB <sup>(1)</sup>  | INLVLB7                | INLVLB6                | INLVLB5 | INLVLB4  | _       | _       | _       | _       | 1111                  | 1111                       |

| 1F48h               | IOCBP <sup>(1)</sup>   | IOCBP7                 | IOCBP6                 | IOCBP5  | IOCBP4   | _       | _       | _       | _       | 0000                  | 0000                       |

| 1F49h               | IOCBN <sup>(1)</sup>   | IOCBN7                 | IOCBN6                 | IOCBN5  | IOCBN4   | _       | —       | _       | _       | 0000                  | 0000                       |

| 1F4Ah               | IOCBF <sup>(1)</sup>   | IOCBF7                 | IOCBF6                 | IOCBF5  | IOCBF4   | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F4Bh<br>—<br>1F4Dh | _                      |                        |                        |         | Unimpler | nented  |         |         |         | _                     | _                          |

| 1F4Eh               | ANSELC                 | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | ANSC5   | ANSC4    | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                  |

| 1F4Fh               | WPUC                   | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4    | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                  |

| 1F50h               | ODCONC                 | ODCC7 <sup>(1)</sup>   | ODCC6 <sup>(1)</sup>   | ODCC5   | ODCC4    | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                  |

| 1F51h               | SLRCONC                | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4    | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                  |

| 1F52h               | INLVLC                 | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4  | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                  |

| 1F53h               | IOCCP                  | IOCCP7 <sup>(1)</sup>  | IOCCP6 <sup>(1)</sup>  | IOCCP5  | IOCCP4   | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                  |

| 1F54h               | IOCCN                  | IOCCN7 <sup>(1)</sup>  | IOCCN6 <sup>(1)</sup>  | IOCCN5  | IOCCN4   | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                  |

| 1F55h               | IOCCF                  | IOCCF7 <sup>(1)</sup>  | IOCCF6 <sup>(1)</sup>  | IOCCF5  | IOCCF4   | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                  |

| 1F56h<br><br>1F6Fh  | _                      | Unimplemented          |                        |         |          |         |         |         |         | -                     | _                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: Present only in PIC16(L)F15344.

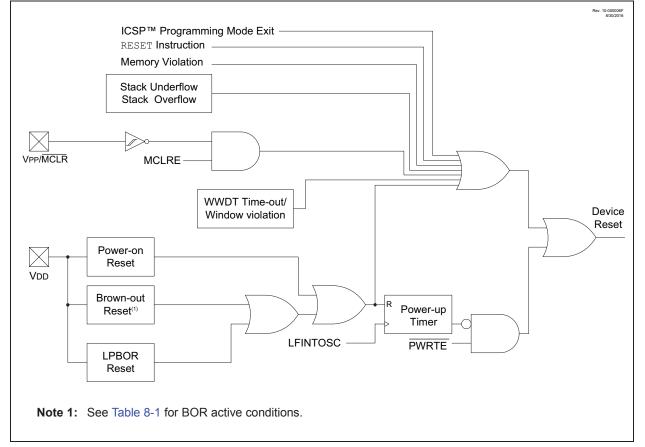

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 8-1.

# 8.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

- Memory Violation Reset (MEMV)

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

#### FIGURE 8-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 2017 Microchip Technology Inc.

# 8.15 Register Definitions: Power Control

Legend:

R = Readable bit

HC = Bit is cleared by hardware

| REGISTER 8- | 2: PCON    | D: POWER C | ONTROL RE  | GISTER 0   |            |            |            |

|-------------|------------|------------|------------|------------|------------|------------|------------|

| R/W/HS-0/q  | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

| STKOVF      | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7       |            |            | ·          |            |            |            | bit 0      |

|             |            |            |            |            |            |            |            |

HS = Bit is set by hardware

U = Unimplemented bit, read as '0'

#### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

W = Writable bit

|                  | bit                                                                                                                                                                  |                                                                                       |                                                                                            |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| u = Bit is unch  | anged                                                                                                                                                                | x = Bit is unknown                                                                    | -m/n = Value at POR/Value at all other Resets                                              |  |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                      | '0' = Bit is cleared                                                                  | q = Value depends on condition                                                             |  |  |  |  |  |  |

|                  |                                                                                                                                                                      |                                                                                       |                                                                                            |  |  |  |  |  |  |

| bit 7            | STKOVF: S                                                                                                                                                            | tack Overflow Flag bit                                                                |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | Overflow occurred                                                                     |                                                                                            |  |  |  |  |  |  |

|                  | 0 = A Stack Overflow has not occurred or cleared by firmware                                                                                                         |                                                                                       |                                                                                            |  |  |  |  |  |  |

| bit 6            |                                                                                                                                                                      | tack Underflow Flag bit                                                               |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | k Underflow occurred<br>k Underflow has not occurred or cleared by firmware           |                                                                                            |  |  |  |  |  |  |

| bit 5            |                                                                                                                                                                      | DT Window Violation Flag                                                              |                                                                                            |  |  |  |  |  |  |

| bit 0            |                                                                                                                                                                      |                                                                                       | as not occurred or set to '1' by firmware                                                  |  |  |  |  |  |  |

|                  | 0 = A WDT                                                                                                                                                            | Window Violation Reset ha                                                             | as occurred (a CLRWDT instruction was executed either without window (cleared by hardware) |  |  |  |  |  |  |

| bit 4            |                                                                                                                                                                      | chdog Timer Reset Flag bi                                                             |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      |                                                                                       | occurred or set to '1' by firmware                                                         |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | -                                                                                     | urred (cleared by hardware)                                                                |  |  |  |  |  |  |

| bit 3            | RMCLR: MO                                                                                                                                                            | CLR Reset Flag bit                                                                    |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | = A MCLR Reset has not occurred or set to '1' by firmware                             |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | Reset has occurred (clea                                                              | red by hardware)                                                                           |  |  |  |  |  |  |

| bit 2            |                                                                                                                                                                      | nstruction Flag bit                                                                   |                                                                                            |  |  |  |  |  |  |

|                  | <ul> <li>1 = A RESET instruction has not been executed or set to '1' by firmware</li> <li>0 = A RESET instruction has been executed (cleared by hardware)</li> </ul> |                                                                                       |                                                                                            |  |  |  |  |  |  |

| bit 1            |                                                                                                                                                                      | r-on Reset Status bit                                                                 |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | er-on Reset occurred                                                                  |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |                                                                                            |  |  |  |  |  |  |

| bit 0            | BOR: Brown                                                                                                                                                           | n-out Reset Status bit                                                                |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | n-out Reset occurred                                                                  |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      | -out Reset occurred (must                                                             | t be set in software after a Power-on Reset or Brown-out Reset                             |  |  |  |  |  |  |

|                  | occurs)                                                                                                                                                              |                                                                                       |                                                                                            |  |  |  |  |  |  |

|                  |                                                                                                                                                                      |                                                                                       |                                                                                            |  |  |  |  |  |  |

| U-0                                   | U-0   | R/W-x/u         | R/W-x/u | U-0                                                   | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|---------------------------------------|-------|-----------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                                     | _     | LATA5           | LATA4   |                                                       | LATA2   | LATA1   | LATA0   |  |  |

| bit 7                                 |       |                 |         |                                                       |         | •       | bit 0   |  |  |

|                                       |       |                 |         |                                                       |         |         |         |  |  |

| Legend:                               |       |                 |         |                                                       |         |         |         |  |  |

| R = Readable b                        | bit   | W = Writable    | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is uncha                      | inged | x = Bit is unkr | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set '0' = Bit is cleared |       |                 |         |                                                       |         |         |         |  |  |

#### REGISTER 14-3: LATA: PORTA DATA LATCH REGISTER

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0'                                |

bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register returns actual I/O pin values.

#### REGISTER 14-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | _   | ANSA5   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>ANSA&lt;5:4&gt;</b> : Analog Select between Analog or Digital Function on pins RA<5:4>, respectively 1 =Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.                                    |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                                         |

#### 14.7 Register Definitions: PORTC

#### REGISTER 14-17: PORTC: PORTC REGISTER

| R/W-x/u                                 | R/W-x/u            | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|--------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| RC7 <sup>(2)</sup>                      | RC6 <sup>(2)</sup> | RC5               | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |

| bit 7                                   |                    |                   |         | •                                                     |         |         | bit 0   |  |  |

|                                         |                    |                   |         |                                                       |         |         |         |  |  |

| Legend:                                 |                    |                   |         |                                                       |         |         |         |  |  |

| R = Readable b                          | bit                | W = Writable b    | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                    |                   | own     | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |                    | '0' = Bit is clea | ired    |                                                       |         |         |         |  |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

2: Present on PIC16(L)F15344 only.

#### REGISTER 14-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

- TRISC<7:0>: PORTC Tri-State Control bits

- 1 = PORTC pin configured as an input (tri-stated)

- 0 = PORTC pin configured as an output

Note 1: Present on PIC16(L)F15344 only.

#### REGISTER 14-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(2)</sup> | LATC6 <sup>(2)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

- **Note 1:** Writes to PORTC are actually written to corresponding LATC register. The actual I/O pin values are read from the PORTC register.

- 2: Present on PIC16(L)F15344 only.

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. The actual I/O pin values are read from the PORTC register.

| Name | Bit 7   | Bit 6   | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------|---------|---------|--------|---------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD  | FVRMD   | —      | —       | —      | NVMMD  | CLKRMD | IOCMD  | 205                 |

| PMD1 | NCO1MD  | _       | —      | —       | _      | TMR2MD | TMR1MD | TMR0MD | 206                 |

| PMD2 | —       | DAC1MD  | ADCMD  | —       | _      | CMP2MD | CMP1MD | ZCDMD  | 207                 |

| PMD3 | —       | —       | PWM6MD | PWM5MD  | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 208                 |

| PMD4 | UART2MD | UART1MD | —      | MSSP1MD | —      | —      | —      | CWG1MD | 209                 |

| PMD5 | —       | —       |        | CLC4MD  | CLC3MD | CLC2MD | CLC1MD | —      | 210                 |

TABLE 16-1:

SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

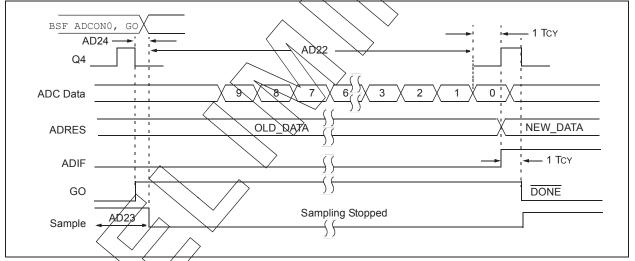

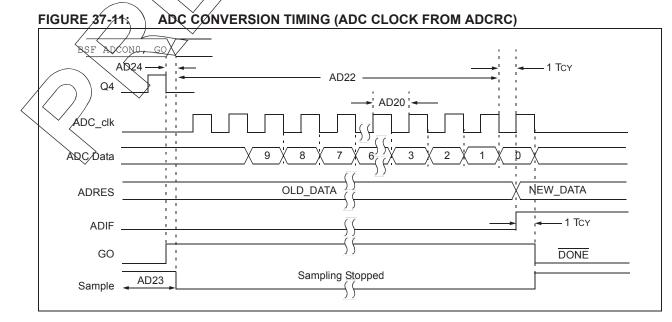

#### 20.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

|         |                                          |

**2:** The ADC operates during Sleep only when the ADCRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine (ISR).

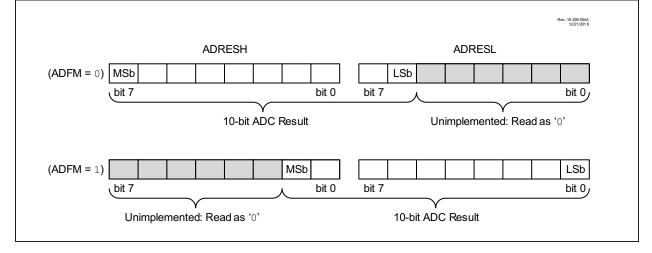

#### 20.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 20-3 shows the two output formats.

#### FIGURE 20-3: 10-BIT ADC CONVERSION RESULT FORMAT

### 27.1 Timer2 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- · any device Reset

- · External Reset Source event that resets the timer.

| Note: | TMR2     | is | not | cleared | when | T2CON | is |

|-------|----------|----|-----|---------|------|-------|----|

|       | written. |    |     |         |      |       |    |

#### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next rising TMR2\_clk edge and increments

the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

#### 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

### 27.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 28.0** "**Capture/Compare/PWM Modules**" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in **Section 27.5** "**Operation Examples**" for examples of how the varying Timer2 modes affect CCP PWM output.

#### 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

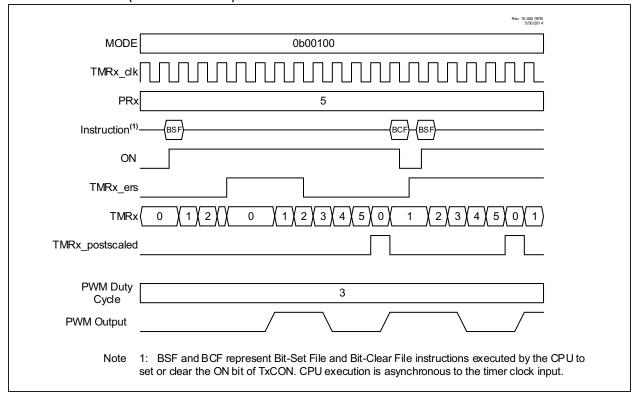

# 27.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

FIGURE 27-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 27-6.

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 28-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 28.3.8 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 28.3.9 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 28.3.10 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 32.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 32-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 32-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. Data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 32-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

Preliminary

PIC16(L)F15324/44

Note 1: If at the beginning of the Start condition,

its Idle state.

the SDA and SCL pins are already

sampled low, or if during the Start condi-

tion, the SCL line is sampled low before

the SDA line is driven low, a bus collision

occurs, the Bus Collision Interrupt Flag,

BCLIF, is set, the Start condition is

aborted and the I<sup>2</sup>C module is reset into

2: The Philips I<sup>2</sup>C specification states that a

bus collision cannot occur on a Start.

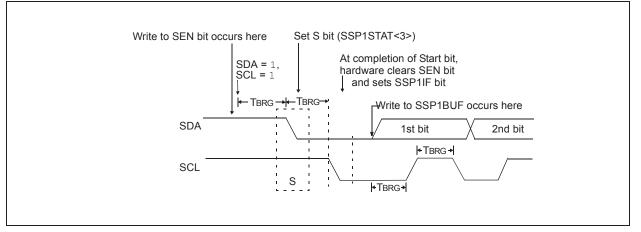

#### 32.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 32-26), the user sets the Start Enable bit, SEN bit of the SSP1CON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSP1STAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSP1CON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

#### FIGURE 32-26: FIRST START BIT TIMING

| R/W-0/0             | R/W-0/0              | R/W-0/0                                                                     | R/W-0/0          | R/W-0/0           | R-0/0             | R-0/0            | R-0/0           |  |  |  |  |

|---------------------|----------------------|-----------------------------------------------------------------------------|------------------|-------------------|-------------------|------------------|-----------------|--|--|--|--|

| SPEN <sup>(1)</sup> | RX9                  | SREN                                                                        | CREN             | ADDEN             | FERR              | OERR             | RX9D            |  |  |  |  |

| bit 7               |                      |                                                                             |                  |                   |                   |                  | bit (           |  |  |  |  |

|                     |                      |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

| Legend:             |                      |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

| R = Readable        |                      | W = Writable                                                                |                  | •                 | nented bit, read  |                  |                 |  |  |  |  |

| u = Bit is unch     | anged                | x = Bit is unki                                                             |                  | -n/n = Value a    | at POR and BO     | R/Value at all c | ther Resets     |  |  |  |  |

| '1' = Bit is set    |                      | '0' = Bit is cle                                                            | ared             |                   |                   |                  |                 |  |  |  |  |

| bit 7               | SPEN: Serial         | Port Enable bi                                                              | <sub>t</sub> (1) |                   |                   |                  |                 |  |  |  |  |

|                     | 1 = Serial po        |                                                                             | •                |                   |                   |                  |                 |  |  |  |  |

|                     |                      | rt disabled (he                                                             | d in Reset)      |                   |                   |                  |                 |  |  |  |  |

| bit 6               | <b>RX9:</b> 9-Bit Re | ceive Enable l                                                              | pit              |                   |                   |                  |                 |  |  |  |  |

|                     | 1 = Selects 9        |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

|                     | 0 = Selects 8        |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

| bit 5               | -                    | e Receive Enat                                                              | ole bit          |                   |                   |                  |                 |  |  |  |  |

|                     | Asynchronous         |                                                                             | innorod          |                   |                   |                  |                 |  |  |  |  |

|                     |                      | s mode – value<br>mode – Maste                                              |                  |                   |                   |                  |                 |  |  |  |  |

|                     | -                    | single receive                                                              | -                |                   |                   |                  |                 |  |  |  |  |

|                     |                      | ) = Disables single receive                                                 |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      | his bit is cleared after reception is complete.<br>Synchronous mode – Slave |                  |                   |                   |                  |                 |  |  |  |  |

|                     | -                    | s mode – slave                                                              | ianored          |                   |                   |                  |                 |  |  |  |  |

| bit 4               |                      | nuous Receive                                                               | •                |                   |                   |                  |                 |  |  |  |  |

|                     | Asynchronous         |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      |                                                                             | eive until enal  | ole bit CREN is   | cleared           |                  |                 |  |  |  |  |

|                     |                      | continuous red                                                              | eive             |                   |                   |                  |                 |  |  |  |  |

|                     | Synchronous          |                                                                             |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      | continuous rec<br>continuous rec                                            |                  | ole bit CREN is   | cleared (CREN     | l overrides SR   | EN)             |  |  |  |  |

| bit 3               |                      | ress Detect En                                                              |                  |                   |                   |                  |                 |  |  |  |  |

| bit 5               |                      | s mode 9-bit (F                                                             |                  |                   |                   |                  |                 |  |  |  |  |

|                     | -                    |                                                                             |                  | nterrupt and lo   | ad of the receive | e buffer when t  | he ninth bit ir |  |  |  |  |

|                     |                      | ve buffer is set                                                            |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      |                                                                             |                  | are received a    | nd ninth bit can  | be used as pa    | rity bit        |  |  |  |  |

|                     |                      | <u>s mode 8-bit (F</u>                                                      |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      | s mode – value                                                              | gnored           |                   |                   |                  |                 |  |  |  |  |

| bit 2               | FERR: Framing        | -                                                                           | ndated by rec    |                   | register and rec  | coivo povt valio | (h)(to)         |  |  |  |  |

|                     | 0 = No framing       |                                                                             |                  |                   |                   |                  | i byte)         |  |  |  |  |

| bit 1               | OERR: Overr          | •                                                                           |                  |                   |                   |                  |                 |  |  |  |  |

|                     |                      | error (can be c                                                             | leared by clea   | ring bit CREN     | )                 |                  |                 |  |  |  |  |

| bit 0               |                      | bit of Received                                                             | Data             |                   |                   |                  |                 |  |  |  |  |

|                     |                      |                                                                             |                  | and must be o     | calculated by us  | er firmware.     |                 |  |  |  |  |

|                     |                      | ule automatica                                                              | Illy changes th  | ne pin from tri-s | state to drive as |                  | gure the        |  |  |  |  |

#### REGISTER 33-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

# PIC16(L)F15324/44

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                               |

| Status Affected: | TO, PD                                                                                                                                                                                                                   |

| Description:     | The power-down Status bit, <u>PD</u> is<br>cleared. Time-out Status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>See <u>Section 11.2</u> " <u>Sleep Mode</u> " for<br>more information. |

| SUBWF            | Subtract W from f                                                                                                                                                                          |                 |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | JBWF f,d        |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                            |                 |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (d                                                                                                                                                                 | lestination)    |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                 |  |  |  |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |                 |  |  |  |

|                  | C = 0 W > f                                                                                                                                                                                |                 |  |  |  |

|                  | <b>C =</b> 1                                                                                                                                                                               | $W \leq f$      |  |  |  |

|                  | DC = 0                                                                                                                                                                                     | W<3:0> > f<3:0> |  |  |  |

|                  | DC = 1 W<3:0> ≤ f<3:0>                                                                                                                                                                     |                 |  |  |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                       |  |  |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                  |            |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Syntax:          | [label] SU                                                                                                               | JBLW k     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |            |  |  |  |  |

| Operation:       | $k -(W) \to (W$                                                                                                          | ')         |  |  |  |  |