#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15344-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1: PIC16(L)F153XX FAMILY TYPES

| Device         | Data Sheet Index | Program Flash Memory (KW) | Program Flash Memory (KB) | Storage Area Flash (B) | Data SRAM<br>(bytes) | I/OPins | 10-bit ADC | 5-bit DAC | Comparator | 8-bit/ (with HLT) Timer | 16-bit Timer | Window Watchdog Timer | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Temperature Indicator | Memory Access Partition | Device Information Area | EUSART/ I <sup>2</sup> C-SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|---------------------------|------------------------|----------------------|---------|------------|-----------|------------|-------------------------|--------------|-----------------------|----------------|-----|-----|-----|-------------------|-----------------------|-------------------------|-------------------------|------------------------------|-----------------------|---------------------------|----------------------|

| PIC16(L)F15313 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 6       | 5          | 1         | 1          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 1/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15323 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 1/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15324 | (D)              | 4                         | 7                         | 224                    | 512                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                       | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15325 | (B)              | 8                         | 14                        | 224                    | 1024                 | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15344 | (D)              | 4                         | 7                         | 224                    | 512                  | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15345 | (B)              | 8                         | 14                        | 224                    | 1024                 | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 2/1                          | Υ                     | Υ                         |                      |

| PIC16(L)F15354 | (A)              | 4                         | 7                         | 224                    | 512                  | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         |                      |

| PIC16(L)F15355 | (A)              | 8                         | 14                        | 224                    | 1024                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15356 | (E)              | 16                        | 28                        | 224                    | 2048                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Υ                 | Υ                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15375 | (E)              | 8                         | 14                        | 224                    | 1024                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15376 | (E)              | 16                        | 28                        | 224                    | 2048                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15385 | (E)              | 8                         | 14                        | 224                    | 1024                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15386 | (E)              | 16                        | 28                        | 224                    | 2048                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                       | 2/2                          | Υ                     | Υ                         | Ι                    |

**Note 1:** I - Debugging integrated on chip.

Data Sheet Index:

**A**:

| DS40001853 | PIC16(L)F15354/5 Data Sheet, 28-Pin |

|------------|-------------------------------------|

|------------|-------------------------------------|

B: DS40001865 PIC16(L)F15325/45 Data Sheet, 14/20-Pin

C: Future Release PIC16(L)F15313/23 Data Sheet, 8/14-Pin

D: DS40001889 PIC16(L)F15324/44 Data Sheet, 14/20-Pin

E: DS40001866 PIC16(L)F15356/75/76/85/86 Data Sheet, 28/40/48-Pin

**Note:** For other small form-factor package availability and marking information, visit www.microchip.com/packaging or contact your local sales office.

| ame                | Function              | Input<br>Type | Output Type | Description                                        |

|--------------------|-----------------------|---------------|-------------|----------------------------------------------------|

| )UT <sup>(2)</sup> | C1OUT                 |               | CMOS/OD     | Comparator 1 output.                               |

|                    | C2OUT                 | _             | CMOS/OD     | Comparator 2 output.                               |

|                    | SDO1                  |               | CMOS/OD     | MSSP1 SPI serial data output.                      |

|                    | SCK1                  | _             | CMOS/OD     | MSSP1 SPI serial clock output.                     |

|                    | DT1 <sup>(3)</sup>    | _             | CMOS/OD     | EUSART Synchronous mode data output.               |

|                    | TX1                   | _             | CMOS/OD     | EUSART1 Asynchronous mode transmitter data output. |

|                    | CK1                   | _             | CMOS/OD     | EUSART1 Synchronous mode clock output.             |

|                    | DT2 <sup>(3)</sup>    | _             | CMOS/OD     | EUSART Synchronous mode data output.               |

|                    | TX2                   | _             | CMOS/OD     | EUSART2 Asynchronous mode transmitter data output. |

|                    | CK2                   | _             | CMOS/OD     | EUSART2 Synchronous mode clock output.             |

|                    | SCL1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C output.                     |

|                    | SDA1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C output.                     |

|                    | TMR0                  | _             | CMOS/OD     | Timer0 output.                                     |

|                    | CCP1                  | _             | CMOS/OD     | CCP1 output (compare/PWM functions).               |

|                    | CCP2                  |               | CMOS/OD     | CCP2 output (compare/PWM functions).               |

|                    | PWM3OUT               | _             | CMOS/OD     | PWM3 output.                                       |

|                    | PWM4OUT               | _             | CMOS/OD     | PWM4 output.                                       |

|                    | PWM5OUT               | _             | CMOS/OD     | PWM5 output.                                       |

|                    | PWM6OUT               | _             | CMOS/OD     | PWM6 output.                                       |

|                    | CWG1A                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output A.       |

|                    | CWG1B                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output B.       |

|                    | CWG1C                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output C.       |

|                    | CWG1D                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output D.       |

|                    | CLC1OUT               | _             | CMOS/OD     | Configurable Logic Cell 1 output.                  |

|                    | CLC2OUT               | _             | CMOS/OD     | Configurable Logic Cell 2 output.                  |

|                    | CLC3OUT               | _             | CMOS/OD     | Configurable Logic Cell 3 output.                  |

|                    | CLC4OUT               | _             | CMOS/OD     | Configurable Logic Cell 4 output.                  |

|                    | NCO10UT               | _             | CMOS/OD     | Numerically Controller Oscillator output.          |

|                    | CLKR                  | _             | CMOS/OD     | Clock Reference module output.                     |

TABLE 1-3: PIC16(L)F15344 PINOUT DESCRIPTION (CONTINUED)

HV = High Voltage XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pipe Refer to Table 16.3 for details on which BORT ains may be used for this size?

Prins is a restricted to table 15-3 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

5: For 14/16-pin package only.

6: For 20-pin package only

## TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address             | Name                   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------------------|------------------------|------------------------|------------------------|---------|----------|---------|---------|---------|---------|-----------------------|----------------------------|

| Bank 62 (C          | Continued)             | itinued)               |                        |         |          |         |         |         |         |                       |                            |

| 1F38h               | ANSELA                 | _                      | _                      | ANSA5   | ANSA4    | _       | ANSA2   | ANSA1   | ANSA0   | 11 1111               | 11 1111                    |

| 1F39h               | WPUA                   | _                      | _                      | WPUA5   | WPUA4    | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 00 0000               | 00 0000                    |

| 1F3Ah               | ODCONA                 | _                      | _                      | ODCA5   | ODCA4    | _       | ODCA2   | ODCA1   | ODCA0   | 00 0000               | 00 0000                    |

| 1F3Bh               | SLRCONA                | —                      | _                      | SLRA5   | SLRA4    | —       | SLRA2   | SLRA1   | SLRA0   | 11 1111               | 11 1111                    |

| 1F3Ch               | INLVLA                 | _                      | _                      | INLVLA5 | INLVLA4  | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111               | 11 1111                    |

| 1F3Dh               | IOCAP                  | —                      | _                      | IOCAP5  | IOCAP4   | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000               | 00 0000                    |

| 1F3Eh               | IOCAN                  | _                      | _                      | IOCAN5  | IOCAN4   | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000               | 00 0000                    |

| 1F3Fh               | IOCAF                  | _                      | —                      | IOCAF5  | IOCAF4   | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000               | 00 0000                    |

| 1F40h<br>—<br>1F42h | _                      |                        |                        |         | Unimpler | nented  |         |         |         | _                     | _                          |

| 1F43h               | ANSELB <sup>(1)</sup>  | ANSB7                  | ANSB6                  | ANSB5   | ANSB4    | _       | _       | _       | _       | 1111                  | 1111                       |

| 1F44h               | WPUB <sup>(1)</sup>    | WPUB7                  | WPUB6                  | WPUB5   | WPUB4    | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F45h               | ODCONB <sup>(1)</sup>  | ODCB7                  | ODCB6                  | ODCB5   | ODCB4    | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F46h               | SLRCONB <sup>(1)</sup> | SLRB7                  | SLRB6                  | SLRB5   | SLRB4    | —       | _       | —       |         | 1111                  | 1111                       |

| 1F47h               | INLVLB <sup>(1)</sup>  | INLVLB7                | INLVLB6                | INLVLB5 | INLVLB4  | _       | _       | _       | _       | 1111                  | 1111                       |

| 1F48h               | IOCBP <sup>(1)</sup>   | IOCBP7                 | IOCBP6                 | IOCBP5  | IOCBP4   | _       | _       | _       | _       | 0000                  | 0000                       |

| 1F49h               | IOCBN <sup>(1)</sup>   | IOCBN7                 | IOCBN6                 | IOCBN5  | IOCBN4   | _       | —       | _       | _       | 0000                  | 0000                       |

| 1F4Ah               | IOCBF <sup>(1)</sup>   | IOCBF7                 | IOCBF6                 | IOCBF5  | IOCBF4   | —       | —       | —       | _       | 0000                  | 0000                       |

| 1F4Bh<br>—<br>1F4Dh | _                      |                        |                        |         | Unimpler | nented  |         |         |         | _                     | _                          |

| 1F4Eh               | ANSELC                 | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | ANSC5   | ANSC4    | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                  |

| 1F4Fh               | WPUC                   | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4    | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                  |

| 1F50h               | ODCONC                 | ODCC7 <sup>(1)</sup>   | ODCC6 <sup>(1)</sup>   | ODCC5   | ODCC4    | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                  |

| 1F51h               | SLRCONC                | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4    | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                  |

| 1F52h               | INLVLC                 | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4  | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                  |

| 1F53h               | IOCCP                  | IOCCP7 <sup>(1)</sup>  | IOCCP6 <sup>(1)</sup>  | IOCCP5  | IOCCP4   | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                  |

| 1F54h               | IOCCN                  | IOCCN7 <sup>(1)</sup>  | IOCCN6 <sup>(1)</sup>  | IOCCN5  | IOCCN4   | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                  |

| 1F55h               | IOCCF                  | IOCCF7 <sup>(1)</sup>  | IOCCF6 <sup>(1)</sup>  | IOCCF5  | IOCCF4   | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                  |

| 1F56h<br><br>1F6Fh  | _                      |                        | Unimplemented          |         |          |         |         |         |         |                       | _                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: Present only in PIC16(L)F15344.

## REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

| WDTCPS             | Value              | Divider R | atio            | Typical Time Out<br>(FIN = 31 kHz) | - Software Control<br>of WDTPS? |

|--------------------|--------------------|-----------|-----------------|------------------------------------|---------------------------------|

| 11111 <b>(1)</b>   | 01011              | 1:65536   | 2 <sup>16</sup> | 2 s                                | Yes                             |

| 11110<br><br>10011 | 11110<br><br>10011 | 1:32      | 2 <sup>5</sup>  | 1 ms                               | No                              |

| 10010              | 10010              | 1:8388608 | 2 <sup>23</sup> | 256 s                              |                                 |

| 10001              | 10001              | 1:4194304 | 2 <sup>22</sup> | 128 s                              |                                 |

| 10000              | 10000              | 1:2097152 | 2 <sup>21</sup> | 64 s                               |                                 |

| 01111              | 01111              | 1:1048576 | 2 <sup>20</sup> | 32 s                               |                                 |

| 01110              | 01110              | 1:524299  | 2 <sup>19</sup> | 16 s                               |                                 |

| 01101              | 01101              | 1:262144  | 2 <sup>18</sup> | 8 s                                |                                 |

| 01100              | 01100              | 1:131072  | 2 <sup>17</sup> | 4 s                                |                                 |

| 01011              | 01011              | 1:65536   | 2 <sup>16</sup> | 2 s                                |                                 |

| 01010              | 01010              | 1:32768   | 2 <sup>15</sup> | 1 s                                |                                 |

| 01001              | 01001              | 1:16384   | 2 <sup>14</sup> | 512 ms                             | No                              |

| 01000              | 01000              | 1:8192    | 2 <sup>13</sup> | 256 ms                             |                                 |

| 00111              | 00111              | 1:4096    | 2 <sup>12</sup> | 128 ms                             |                                 |

| 00110              | 00110              | 1:2048    | 2 <sup>11</sup> | 64 ms                              |                                 |

| 00101              | 00101              | 1:1024    | 2 <sup>10</sup> | 32 ms                              |                                 |

| 00100              | 00100              | 1:512     | 2 <sup>9</sup>  | 16 ms                              |                                 |

| 00011              | 00011              | 1:256     | 2 <sup>8</sup>  | 8 ms                               |                                 |

| 00010              | 00010              | 1:128     | 2 <sup>7</sup>  | 4 ms                               |                                 |

| 00001              | 00001              | 1:64      | 2 <sup>6</sup>  | 2 ms                               |                                 |

| 00000              | 00000              | 1:32      | 2 <sup>5</sup>  | 1 ms                               |                                 |

Note 1: 0b11111 is the default value of the WDTCPS bits.

#### REGISTER 10-12: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|------------|-----|-----|-----|-----|------------|------------|

|       | ZCDIF      | _   | _   | _   | —   | C2IF       | C1IF       |

| bit 7 |            |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>ZCDIF:</b> Zero-Cross Detect (ZCD1) Interrupt Flag bit                                                                                                      |

|         | <ul> <li>1 = An enabled rising and/or falling ZCD1 event has been detected (must be cleared in software)</li> <li>0 = No ZCD1 event has occurred</li> </ul>    |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1   | <b>C2IF</b> : Comparator C2 Interrupt Flag bit<br>1 = Comparator 2 interrupt asserted (must be cleared in software)<br>0 = Comparator 2 interrupt not asserted |

| bit 0   | <b>C1IF:</b> Comparator C1 Interrupt Flag bit<br>1 = Comparator 1 interrupt asserted (must be cleared in software)<br>0 = Comparator 1 interrupt not asserted  |

| Note:   | Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of                                                                     |

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |

#### REGISTER 10-14: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | _   | _   | _   | _   | _   | TMR2IF     | TMR1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7-2<br>bit 1 | Unimplemented: Read as '0'<br>TRM2IF: Timer2 Interrupt Flag bit<br>1 = The TMR2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be cleared<br>in software)<br>0 = No TMR2 event has occurred |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0            | <b>TRM1IF:</b> Timer1 Overflow Interrupt Flag bit<br>1 = Timer1 overflow occurred (must be cleared in software)<br>0 = No Timer1 overflow occurred                                                                     |

| Note:            | Interrupt flag bits are set when an interrupt                                                                                                                                                                          |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

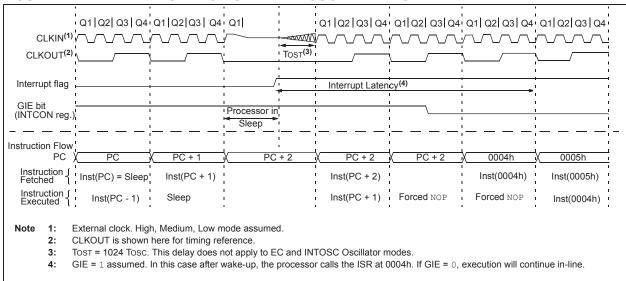

#### 11.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source, with the exception of the clock switch interrupt, has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

## FIGURE 11-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

## 11.2.3 LOW-POWER SLEEP MODE

The PIC16F15324/44 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC16F15324/44 allows the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. Depending on the configuration of these bits, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

## 11.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### REGISTER 14-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | —   | —   | _   | _     |

| bit 7   |         |         | ·       | ·   | •   | -   | bit 0 |

| DIL 7   |         |         |         |     |     |     | d     |

## Legend:

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | SLRB<7:4>: PORTB Slew Rate Enable bits |

|---------|----------------------------------------|

|         | For RB<7:4> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

|         |                                        |

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 14-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —   | —   | —   | —     |

| bit 7   | •       |         |         | •   | •   |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | INLVLB<7:4>: PORTB Input Level Select bits                |

|---------|-----------------------------------------------------------|

|         | For RB<7:4> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

| bit 3-0 | Unimplemented: Read as '0'                                |

#### TABLE 14-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|

| PORTB   | RB7     | RB6     | RB5     | RB4     |       |       |       |       | 185                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | —     | —     | _     | _     | 185                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | —     | —     | _     | _     | 186                 |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | —     | —     | _     | _     | 186                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | —     | —     | _     | _     | 187                 |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | —     | —     | —     | _     | 187                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | _     | _     | _     | _     | 188                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 |       |       |       | _     | 188                 |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

© 2017 Microchip Technology Inc.

## 18.3 Register Definitions: FVR Control

'1' = Bit is set

| R/W-0/0                                 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0     |  |

|-----------------------------------------|-----------------------|---------------------|----------------------|------------------------------------|---------------|------------------|-------------|--|

| FVREN                                   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAF\                              | /R<1:0>       | ADFVR<1:0>       |             |  |

| bit 7 bit 0                             |                       |                     |                      |                                    |               |                  |             |  |

|                                         |                       |                     |                      |                                    |               |                  |             |  |

| Legend:                                 |                       |                     |                      |                                    |               |                  |             |  |

| R = Readable bit W = Writable bit       |                       |                     |                      | U = Unimplemented bit, read as '0' |               |                  |             |  |

| u = Bit is unchanged x = Bit is unknown |                       |                     |                      | -n/n = Value a                     | t POR and BOI | R/Value at all o | ther Resets |  |

q = Value depends on condition

| bit 7         | <b>FVREN:</b> Fixed Voltage Reference Enable bit<br>1 = Fixed Voltage Reference is enabled<br>0 = Fixed Voltage Reference is disabled                                                                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6         | <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(1)</sup><br>1 = Fixed Voltage Reference output is ready for use<br>0 = Fixed Voltage Reference output is not ready or not enabled                                                                                                   |

| bit 5         | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled                                                                                                                                                   |

| bit 4         | <b>TSRNG:</b> Temperature Indicator Range Selection bit <sup>(3)</sup><br>1 = Temperature in High Range VOUT = 3VT<br>0 = Temperature in Low Range VOUT = 2VT                                                                                                                                   |

| bit 3-2       | <b>CDAFVR&lt;1:0&gt;:</b> Comparator FVR Buffer Gain Selection bits<br>11 = Comparator FVR Buffer Gain is 4x, (4.096V) <sup>(2)</sup><br>10 = Comparator FVR Buffer Gain is 2x, (2.048V) <sup>(2)</sup><br>01 = Comparator FVR Buffer Gain is 1x, (1.024V)<br>00 = Comparator FVR Buffer is off |

| bit 1-0       | <b>ADFVR&lt;1:0&gt;:</b> ADC FVR Buffer Gain Selection bit<br>11 = ADC FVR Buffer Gain is 4x, $(4.096V)^{(2)}$<br>10 = ADC FVR Buffer Gain is 2x, $(2.048V)^{(2)}$<br>01 = ADC FVR Buffer Gain is 1x, $(1.024V)$<br>00 = ADC FVR Buffer is off                                                  |

| Note 1:<br>2: | FVRRDY is always '1'.<br>Fixed Voltage Reference output cannot exceed VDD.                                                                                                                                                                                                                      |

'0' = Bit is cleared

3: See Section 19.0 "Temperature Indicator Module" for additional information.

| Name     | Bit 7  | Bit 6     | Bit 5   | Bit 4                | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on page |

|----------|--------|-----------|---------|----------------------|-------|--------|---------|--------|---------------------|

| FVRCON   | FVREN  | FVRRDY    | TSEN    | TSRNG                | CDAFV | R<1:0> | ADFVR   | <1:0>  | 222                 |

| ADCON0   |        | CHS<5:0>  |         |                      |       |        |         | ADON   | 235                 |

| ADCON1   | ADFM   | ADCS<2:0> |         |                      | _     | _      | ADPREI  | F<1:0> | 236                 |

| DAC1CON0 | DAC1EN | _         | DAC10E1 | DAC1OE2 DAC1PSS<1:0> |       | _      | DAC1NSS | 244    |                     |

TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

Legend: - = unimplemented locations read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3      | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|-------|---------|---------|------------|---------|-------|---------|---------------------|

| DAC1CON0 | DAC1EN | _     | DAC10E1 | DAC10E2 | DAC1PS     | SS<1:0> | —     | DAC1NSS | 244                 |

| DAC1CON1 | —      | —     | —       |         | 244        |         |       |         |                     |

| CM1PSEL  | —      | —     | —       | —       | —          | 264     |       |         |                     |

| CM2PSEL  | —      |       | _       | —       | — PCH<2:0> |         |       |         | 264                 |

TABLE 21-1:

SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

## 23.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 37-14 for more information.

## 23.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 26.5 "Timer Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 23.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 23-2) and the Timer1 Block Diagram (Figure 26-1) for more information.

## 23.5 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

## 23.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxPSEL register directs an internal voltage reference or an analog pin to the noninverting input of the comparator:

- CxIN0+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See Section 18.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 23.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- · Analog Ground

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

## 26.6 Timer1 Interrupts

The timer register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When the timer rolls over, the respective timer interrupt flag bit of the PIR5 register is set. To enable the interrupt on rollover, you must set these bits:

- ON bit of the T1CON register

- TMR1IE bit of the PIE4 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

| Note: | To avoid immediate interrupt vectoring,     |

|-------|---------------------------------------------|

|       | the TMR1H:TMR1L register pair should        |

|       | be preloaded with a value that is not immi- |

|       | nently about to rollover, and the TMR1IF    |

|       | flag should be cleared prior to enabling    |

|       | the timer interrupts.                       |

## 26.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- · ON bit of the T1CON register must be set

- TMR1IE bit of the PIE4 register must be set

- · PEIE bit of the INTCON register must be set

- · SYNC bit of the T1CON register must be set

- CS bits of the T1CLK register must be configured

- The timer clock source must be enabled and continue operation during sleep.

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Secondary oscillator will continue to operate in Sleep regardless of the SYNC bit setting.

#### 26.8 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

For more information, see Section 28.0 "Capture/Compare/PWM Modules".

#### 26.9 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger an auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a timer interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1.

The timer should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of the timer can cause an Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with an Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see Section 28.2.4 "Compare During Sleep".

| U-0                                                                | U-0        | R-x                                    | U-0                      | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0      |  |  |  |

|--------------------------------------------------------------------|------------|----------------------------------------|--------------------------|----------------|-----------------|------------------|--------------|--|--|--|

| 0-0                                                                | 0-0        |                                        | 0-0                      |                |                 |                  |              |  |  |  |

|                                                                    | —          | IN                                     |                          | POLD           | POLC            | POLB             | POLA         |  |  |  |

| bit 7                                                              |            |                                        |                          |                |                 |                  | bit 0        |  |  |  |

|                                                                    |            |                                        |                          |                |                 |                  |              |  |  |  |

| Legend:                                                            |            |                                        |                          |                |                 |                  |              |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |            |                                        |                          |                |                 |                  |              |  |  |  |

| u = Bit is ur                                                      | nchanged   | x = Bit is unkr                        | nown                     | -n/n = Value a | at POR and BO   | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is s                                                     | et         | '0' = Bit is cle                       | ared                     | q = Value dep  | pends on condit | ion              |              |  |  |  |

|                                                                    |            |                                        |                          |                |                 |                  |              |  |  |  |

| bit 7-6                                                            | Unimplem   | ented: Read as '                       | 0'                       |                |                 |                  |              |  |  |  |

| bit 5                                                              | IN: CWG Ir | nput Value bit                         |                          |                |                 |                  |              |  |  |  |

| bit 4                                                              | Unimplem   | ented: Read as '                       | 0'                       |                |                 |                  |              |  |  |  |

| bit 3                                                              | POLD: CW   | G1D Output Pola                        | arity bit                |                |                 |                  |              |  |  |  |

|                                                                    | 1 = Signal | output is inverted                     | put is inverted polarity |                |                 |                  |              |  |  |  |

|                                                                    | 0 = Signal | output is normal                       | polarity                 |                |                 |                  |              |  |  |  |

| bit 2                                                              | POLC: CW   | G1C Output Pola                        | arity bit                |                |                 |                  |              |  |  |  |

|                                                                    | 0          | 1 = Signal output is inverted polarity |                          |                |                 |                  |              |  |  |  |

|                                                                    | •          | output is normal                       |                          |                |                 |                  |              |  |  |  |

| bit 1                                                              |            | G1B Output Pola                        |                          |                |                 |                  |              |  |  |  |

|                                                                    |            | output is inverted                     |                          |                |                 |                  |              |  |  |  |

| 0 = Signal output is normal polarity                               |            |                                        |                          |                |                 |                  |              |  |  |  |

| bit 0                                                              |            | G1A Output Pola                        | 5                        |                |                 |                  |              |  |  |  |

|                                                                    |            | output is inverted                     |                          |                |                 |                  |              |  |  |  |

|                                                                    | 0 = Signal | 0 = Signal output is normal polarity   |                          |                |                 |                  |              |  |  |  |

#### REGISTER 30-2: CWG1CON1: CWG1 CONTROL REGISTER 1

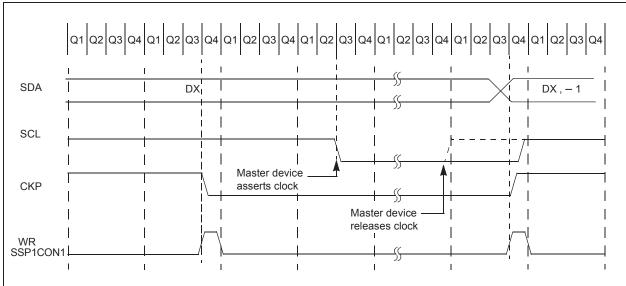

#### 32.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSP1CON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 32.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSP1STAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSP1BUF with data to transfer to the master. If the SEN bit of SSP1CON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

#### 32.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSP1ADD.

#### 32.5.6.3 Byte NACKing

When AHEN bit of SSP1CON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSP1CON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

## 32.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 32-23).

FIGURE 32-23: CLOCK SYNCHRONIZATION TIMING

$\wedge$

| TABLE 37-3: | POWER-DOWN CURRENT | (IPD) <sup>(1,2)</sup> |

|-------------|--------------------|------------------------|

|-------------|--------------------|------------------------|

| TABLE 37-3: POWER-DOWN CURRENT (IPD)(1)-7 |           |                                          |                        |                                                                       |               |                |       |       |                                  |  |

|-------------------------------------------|-----------|------------------------------------------|------------------------|-----------------------------------------------------------------------|---------------|----------------|-------|-------|----------------------------------|--|

| PIC16LF                                   | 15324/44  |                                          |                        | Standard Operating Conditions (unless otherwise stated)               |               |                |       |       |                                  |  |

| PIC16F15324/44                            |           |                                          |                        | Standard Operating Conditions (unless otherwise stated)<br>VREGPM = 1 |               |                |       |       |                                  |  |

| Param.<br>No.                             | Symbol    | Device Characteristics                   | Min.                   | Тур.†                                                                 | Max.<br>+85°C | Max.<br>+125°C | Units | VDD   | Conditions<br>Note               |  |

| D200                                      | IPD       | IPD Base                                 | —                      | 0.06                                                                  | 2             | 9              | μΑ    | 3.01  | $\langle$                        |  |

| D200                                      | IPD       | IPD Base                                 | —                      | 0.4                                                                   | 4             | 12             | /HA   | 3.0V  | $\left\langle \right\rangle$     |  |

| D200A                                     |           |                                          | _                      | 18                                                                    | 22            | 27 \           | A44   | 3.0∀  | VREGPM = 0                       |  |

| D201                                      | IPD_WDT   | Low-Frequency Internal<br>Oscillator/WDT | —                      | 0.8                                                                   | 4.0           | 11.5           | μÀ    | 73.0₩ |                                  |  |

| D201                                      | IPD_WDT   | Low-Frequency Internal<br>Oscillator/WDT | —                      | 0.9                                                                   | 5.0 <         | 13             | μA    | 3.0V  |                                  |  |

| D203                                      | IPD_FVR   | FVR                                      | _                      | 33                                                                    | <u>_47</u>    | 47             | , Aμ  | 3.0V  |                                  |  |

| D203                                      | IPD_FVR   | FVR                                      | _                      | 28                                                                    | 44            | 44             | μÀ    | 3.0V  |                                  |  |

| D204                                      | IPD_BOR   | Brown-out Reset (BOR)                    |                        | 10                                                                    | 17            | 19             | μA    | 3.0V  |                                  |  |

| D204                                      | IPD_BOR   | Brown-out Reset (BOR)                    |                        | 14                                                                    | 18            | 20             | μΑ    | 3.0V  |                                  |  |

| D205                                      | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)        |                        | 0.5                                                                   | 4             | 10             | μΑ    | 3.0V  |                                  |  |

| D207                                      | IPD_ADCA  | ADC - Active                             | $\leq$                 | 250                                                                   | $ \geq $      | > -            | μΑ    | 3.0V  | ADC is converting <sup>(4)</sup> |  |

| D207                                      | IPD_ADCA  | ADC - Active                             |                        | 280                                                                   |               | [              | μΑ    | 3.0V  | ADC is converting (4)            |  |

| D208                                      | IPD_CMP   | Comparator                               | -                      | 30                                                                    | <b>A</b> 2    | 44             | μΑ    | 3.0V  |                                  |  |

| D208                                      | IPD_CMP   | Comparator                               | $\left  \right\rangle$ | 33                                                                    | 44            | 45             | μΑ    | 3.0V  |                                  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

3: All peripheral currents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

4: ADC clock source is FRC.

5: = F device /

#### TABLE 37-14: COMPARATOR SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                        |                                   |      |      |       |       |                           |  |

|----------------------------------------------------------------------------------|------------------------|-----------------------------------|------|------|-------|-------|---------------------------|--|

| Param.<br>No.                                                                    | Sym.                   | Characteristics                   | Min. | Тур. | Max.  | Units | Comments                  |  |

| CM01                                                                             | VIOFF                  | Input Offset Voltage              | _    | —    | ±50   | mV    | VIEM = VDD/2              |  |

| CM02                                                                             | VICM                   | Input Common Mode Range           | GND  | —    | Vdd   | V     |                           |  |

| CM03                                                                             | CMRR                   | Common Mode Input Rejection Ratio | —    | 50   | —     | dB <  |                           |  |

| CM04                                                                             | VHYST                  | Comparator Hysteresis             | 15   | 25   | 35    | mV    | $\langle \langle \rangle$ |  |

| CM05                                                                             | TRESP <sup>(1)</sup>   | Response Time, Rising Edge        | _    | 300  | 600 / | _ns∕  | $\langle \rangle$         |  |

|                                                                                  |                        | Response Time, Falling Edge       | —    | 220  | 500   | Tus   |                           |  |

| CMOS6                                                                            | TMCV2VO <sup>(2)</sup> | Mode Change to Valid Output       | —    | —    | 10    | NS/   | $\sim$                    |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: A mode change includes changing any of the control register values, including module enable.

#### TABLE 37-15: 5-BIT DAC SPECIFICATIONS

|               | Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                              |                        |                        |       |       |          |  |  |  |

|---------------|----------------------------------------------------------------------------------|------------------------------|------------------------|------------------------|-------|-------|----------|--|--|--|

| Param.<br>No. | Sym.                                                                             | Characteristics              | Min.                   | Тур.                   | Max.  | Units | Comments |  |  |  |

| DSB01         | VLSB                                                                             | Step Size                    | E,                     | (VDACREF+ VDACREF-)/32 | _     | V     |          |  |  |  |

| DSB01         | VACC                                                                             | Absolute Accuracy            | $\sum$                 | $\searrow$             | ± 0.5 | LSb   |          |  |  |  |

| DSB03*        | RUNIT                                                                            | Unit Resistor Value          | $\backslash - \rangle$ | 5000                   |       | Ω     |          |  |  |  |

| DSB04*        | Tst                                                                              | Settling Time <sup>(1)</sup> | $\langle - \rangle$    | · ─ ─ ─                | 10    | μS    |          |  |  |  |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Settling time measured while DACR<4:0> transitions from '00000' to '01111'.

## TABLE 37-16: FIXED VOLTAGE REFERENCE (FVR) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |               |                                                     |      |      |      |       |                                                                                                                            |  |

|---------------------------------------------------------|---------------|-----------------------------------------------------|------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.                                           | Symbol        | Characteristic                                      | Min. | Тур. | Max. | Units | Conditions                                                                                                                 |  |

| FVR01                                                   | VEVR1         | 1x Gain (1.024V)                                    | -4   | —    | +4   | %     | $\begin{array}{l} V\text{DD} \geq 2.5\text{V}, \ \text{-40}^{\circ}\text{C} \ \text{to} \\ 85^{\circ}\text{C} \end{array}$ |  |

| FVR02                                                   | VFVR2         | 2x Gain (2.048V)                                    | -4   | —    | +4   | %     | $V\text{DD} \geq 2.5V\text{, }$ -40°C to 85°C                                                                              |  |

| FVR03                                                   | XFVR4         | 4x Gain (4.096V)                                    | -5   | —    | +5   | %     | $VDD \ge 4.75V, -40^{\circ}C$ to $85^{\circ}C$                                                                             |  |

| FVR04                                                   | TFVRST        | FVR Start-up Time                                   | _    | 25   | —    | us    |                                                                                                                            |  |

| FVR05                                                   | FVRA1x/FVRC1x | FVR output voltage for 1x setting stored in the DIA | -    | 1024 | —    | mV    |                                                                                                                            |  |

| FVR06                                                   | FVRA2x/FVRC2x | FVR output voltage for 2x setting stored in the DIA | —    | 2048 | _    | mV    |                                                                                                                            |  |

| FVR07                                                   | FVRA4x/FVRC4x | FVR output voltage for 4x setting stored in the DIA | —    | 4096 | —    | mV    |                                                                                                                            |  |

© 2017 Microchip Technology Inc.

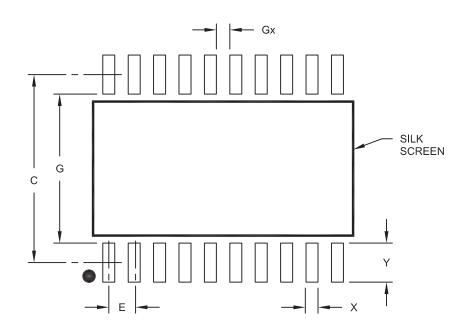

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units  |      |      |      |  |

|--------------------------|--------|------|------|------|--|

| Dimension                | Limits | MIN  | NOM  | MAX  |  |

| Contact Pitch            | E      |      |      |      |  |

| Contact Pad Spacing      | С      |      | 9.40 |      |  |

| Contact Pad Width (X20)  | Х      |      |      | 0.60 |  |

| Contact Pad Length (X20) | Y      |      |      | 1.95 |  |

| Distance Between Pads    | Gx     | 0.67 |      |      |  |

| Distance Between Pads    | G      | 7.45 |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A