Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15344-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

# 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON0 register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack**" for more details.

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See Section 4.6 "Indirect Addressing" for more details.

# 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 36.0 "Instruction Set Summary**" for more details.

| <b>TABLE 4-10:</b> | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |

|--------------------|----------------------------------------------------------|

|--------------------|----------------------------------------------------------|

|                   |                              |        |        |         |               |                   | <b>(()</b> |         |         |                       |                            |

|-------------------|------------------------------|--------|--------|---------|---------------|-------------------|------------|---------|---------|-----------------------|----------------------------|

| Address           | Name                         | Bit 7  | Bit 6  | Bit 5   | Bit 4         | Bit 3             | Bit 2      | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 18           |                              |        |        |         |               |                   |            |         |         |                       |                            |

|                   |                              |        |        | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics  |         |         |                       |                            |

| 90Ch              | FVRCON                       | FVREN  | FVRRDY | TSEN    | TSRNG         | CDAFV             | 'R<1:0>    | ADF     | VR<1:0> | 0x00 xxxx             | 0q00 uuuu                  |

| 90Dh              | _                            |        | •      |         | Unimpler      | nented            |            |         |         | _                     | _                          |

| 90Eh              | DAC1CON0                     | EN     | _      | OE1     | OE2           | PSS               | <1:0>      | —       | NSS     | 0-00 00-0             | 0-00 00-0                  |

| 90Fh              | Fh DAC1CON1 — — — DAC1R<4:0> |        |        |         |               |                   | 0 0000     | 0 0000  |         |                       |                            |

| 910hUnimplemented |                              |        |        |         |               | -                 | _          |         |         |                       |                            |

| 91Fh              | ZCDCON                       | ZCDSEN | _      | ZCDOUT  | ZCDPOL        | —                 | _          | ZCDINTP | ZCDINTN | 0-x000                | 0-x000                     |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

## REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

| WDTCPS             | Value              | Divider Ratio |                 | Typical Time Out<br>(FIN = 31 kHz) | - Software Control<br>of WDTPS? |  |

|--------------------|--------------------|---------------|-----------------|------------------------------------|---------------------------------|--|

| 11111 <b>(1)</b>   | 01011              | 1:65536       | 2 <sup>16</sup> | 2 s                                | Yes                             |  |

| 11110<br><br>10011 | 11110<br><br>10011 | 1:32          | 2 <sup>5</sup>  | 1 ms                               | No                              |  |

| 10010              | 10010              | 1:8388608     | 2 <sup>23</sup> | 256 s                              |                                 |  |

| 10001              | 10001              | 1:4194304     | 2 <sup>22</sup> | 128 s                              |                                 |  |

| 10000              | 10000              | 1:2097152     | 2 <sup>21</sup> | 64 s                               |                                 |  |

| 01111              | 01111              | 1:1048576     | 2 <sup>20</sup> | 32 s                               |                                 |  |

| 01110              | 01110              | 1:524299      | 2 <sup>19</sup> | 16 s                               |                                 |  |

| 01101              | 01101              | 1:262144      | 2 <sup>18</sup> | 8 s                                |                                 |  |

| 01100              | 01100              | 1:131072      | 2 <sup>17</sup> | 4 s                                |                                 |  |

| 01011              | 01011              | 1:65536       | 2 <sup>16</sup> | 2 s                                |                                 |  |

| 01010              | 01010              | 1:32768       | 2 <sup>15</sup> | 1 s                                |                                 |  |

| 01001              | 01001              | 1:16384       | 2 <sup>14</sup> | 512 ms                             | No                              |  |

| 01000              | 01000              | 1:8192        | 2 <sup>13</sup> | 256 ms                             |                                 |  |

| 00111              | 00111              | 1:4096        | 2 <sup>12</sup> | 128 ms                             |                                 |  |

| 00110              | 00110              | 1:2048        | 2 <sup>11</sup> | 64 ms                              |                                 |  |

| 00101              | 00101              | 1:1024        | 2 <sup>10</sup> | 32 ms                              |                                 |  |

| 00100              | 00100              | 1:512         | 2 <sup>9</sup>  | 16 ms                              |                                 |  |

| 00011              | 00011              | 1:256         | 2 <sup>8</sup>  | 8 ms                               |                                 |  |

| 00010              | 00010              | 1:128         | 2 <sup>7</sup>  | 4 ms                               |                                 |  |

| 00001              | 00001              | 1:64          | 2 <sup>6</sup>  | 2 ms                               |                                 |  |

| 00000              | 00000              | 1:32          | 2 <sup>5</sup>  | 1 ms                               |                                 |  |

Note 1: 0b11111 is the default value of the WDTCPS bits.

## 6.0 DEVICE INFORMATION AREA

The Device Information Area (DIA) is a dedicated region in the program memory space; it is a new feature in the PIC16(L)F15324/44 family of devices. The DIA contains the calibration data for the internal temperature indicator module, stores the Microchip Unique Identifier words and the Fixed Voltage Reference voltage readings measured in mV.

The complete DIA table is shown in Table 6-1: Device Information Area, followed by a description of each region and its functionality. The data is mapped from 8100h to 811Fh in the PIC16(L)F15324/44 family. These locations are read-only and cannot be erased or modified. The data is programmed into the device during manufacturing.

TABLE 6-1: DEVICE INFORMATION AREA

| Address Range | Name of Region        | Standard Device Information                                    |  |  |  |  |

|---------------|-----------------------|----------------------------------------------------------------|--|--|--|--|

|               | MUI0                  |                                                                |  |  |  |  |

|               | MUI1                  |                                                                |  |  |  |  |

|               | MUI2                  |                                                                |  |  |  |  |

| 8100h-8108h   | MUI3                  |                                                                |  |  |  |  |

|               | MUI4                  | Microchip Unique Identifier (9 Words)                          |  |  |  |  |

|               | MUI5                  |                                                                |  |  |  |  |

|               | MUI6                  |                                                                |  |  |  |  |

|               | MUI7                  |                                                                |  |  |  |  |

|               | MUI8                  |                                                                |  |  |  |  |

| 8109h         | MUI9                  | 1 Word Reserved                                                |  |  |  |  |

|               | EUI0                  |                                                                |  |  |  |  |

| 810Ah-8111h   | EUI1                  |                                                                |  |  |  |  |

|               | EUI2                  |                                                                |  |  |  |  |

|               | EUI3                  |                                                                |  |  |  |  |

|               | EUI4                  | Unassigned (8 Words)                                           |  |  |  |  |

|               | EUI5                  |                                                                |  |  |  |  |

|               | EUI6                  |                                                                |  |  |  |  |

|               | EUI7                  |                                                                |  |  |  |  |

| 8112h         | TSLR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8113h         | TSLR2                 | Temperature indicator ADC reading at 90°C (low range setting)  |  |  |  |  |

| 8114h         | TSLR3                 | Unassigned (1 word)                                            |  |  |  |  |

| 8115h         | TSHR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8116h         | TSHR2                 | Temperature indicator ADC reading at 90°C (high range setting) |  |  |  |  |

| 8117h         | TSHR3                 | Unassigned (1 Word)                                            |  |  |  |  |

| 8118h         | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)                 |  |  |  |  |

| 8119h         | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)                 |  |  |  |  |

| 811Ah         | FVRA4X <sup>(1)</sup> | ADC FVR1 Output Voltage for 4x setting (in mV)                 |  |  |  |  |

| 811Bh         | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV)          |  |  |  |  |

| 811Ch         | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV)          |  |  |  |  |

| 811Dh         | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV)          |  |  |  |  |

| 811Eh-811Fh   |                       | Unassigned (1 Word)                                            |  |  |  |  |

**Note 1:** Value not present on LF devices.

## 8.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

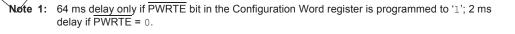

## 8.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |

| 1.0        | V      | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |

| 10         | Х      | Sleep       | Disabled | Waits for BOR Reset release                                         |

| 0.1        | 1      | Х           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |

| 01         | 0      | Х           | Disabled | Paging immediately (POPPD) =)                                       |

| 0.0        | Х      | Х           | Disabled | Begins immediately (BORRDY = $x$ )                                  |

### TABLE 8-1: BOR OPERATING MODES

Note 1: In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 8.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 8.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

## 8.14 Power Control (PCONx) Registers

The Power Control (PCONx) registers contain flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Timer Window Violation Reset

(WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

The PCON0 register bits are shown in Register 8-3. The PCON1 register bits are shown in Register 8-3.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no reset action will be generated.

## 11.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes: DOZE mode, IDLE mode, and SLEEP mode.

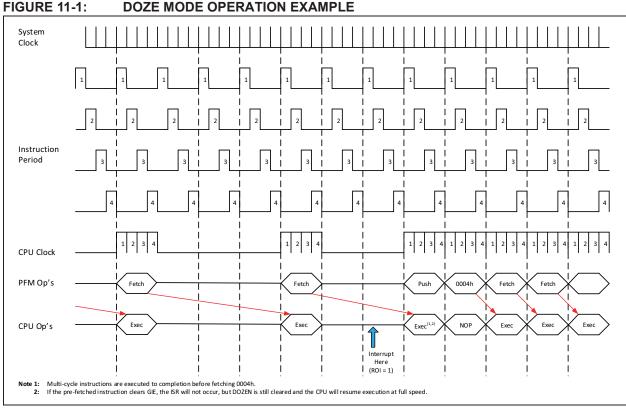

# 11.1 DOZE Mode

DOZE mode allows for power saving by reducing CPU operation and program memory (PFM) access, without affecting peripheral operation. DOZE mode differs from Sleep mode because the system oscillators continue to

operate, while only the CPU and PFM are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 100, the instruction cycle ratio is 1:32. The CPU and memory execute for one instruction cycle and then lay idle for 31 instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

# 11.1.1 DOZE OPERATION

The Doze operation is illustrated in Figure 11-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the PFM fetches for the next instruction cycle. The Q-clocks to the peripherals continue throughout.

| U-0              | U-0                      | U-0               | R/W-0/u | R/W-0/u                                               | R/W-0/u          | R/W-0/u  | R/W-0/u |  |

|------------------|--------------------------|-------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

|                  | —                        | _                 |         |                                                       | RxyPPS<4:0>      |          |         |  |

| bit 7            |                          |                   |         |                                                       |                  |          | bit 0   |  |

|                  |                          |                   |         |                                                       |                  |          |         |  |

| Legend:          |                          |                   |         |                                                       |                  |          |         |  |

| R = Readable I   | bit                      | W = Writable      | bit     | U = Unimplen                                          | nented bit, read | l as '0' |         |  |

| u = Bit is uncha | anged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set |                          | '0' = Bit is clea | ared    |                                                       |                  |          |         |  |

## REGISTER 15-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

bit 4-0 **RxyPPS<4:0>:** Pin Rxy Output Source Selection bits See Table 15-4 and Table 15-5.

Note 1: TRIS control is overridden by the peripheral as required.

### REGISTER 15-3: PPSLOCK: PPS LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | _   | —   | —   | _   | —   | —   | PPSLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0

PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

### 19.2.1 CALIBRATION

### 19.2.1.1 Single-Point Calibration

Single-point calibration is performed by application software using Equation 19-1 and the assumed Mt. A reading of VTSENSE at a known temperature is taken, and the theoretical temperature is calculated by temporarily setting TOFFSET = 0. Then TOFFSET is computed as the difference of the actual and calculated temperatures. Finally, TOFFSET is stored in nonvolatile memory within the device, and is applied to future readings to gain a more accurate measurement.

### 19.2.1.2 Higher-Order Calibration

If the application requires more precise temperature measurement, additional calibrations steps will be necessary. For these applications, two-point or three-point calibration is recommended.

| Note 1: | The TOFFSET value may be determined  |

|---------|--------------------------------------|

|         | by the user with a temperature test. |

- 2: Although the measurement range is -40°C to +125 °C due to the variations in offset error, the single-point uncalibrated calculated TSENSE value may indicate a temperature from -140°C to +225°C before the calibration offset is applied.

- The user must take into consideration self-heating of the device at different clock frequencies and output pin loading. For package related thermal characteristics information, refer to Section TABLE 37-6: "Thermal Characteristics".

### 19.2.2 TEMPERATURE RESOLUTION

The resolution of the ADC reading, Ma (°C/count), depends on both the ADC resolution N and the reference voltage used for conversion, as shown in Equation 19-2. It is recommended to use the smallest VREF value, such as 2.048 FVR reference voltage, instead of VDD.

| Note: | Refer   | to              | Sec    | tion 3 | 37.0 | "Electrical |

|-------|---------|-----------------|--------|--------|------|-------------|

|       | Specifi | Specifications" |        |        | FVR  | reference   |

|       | voltage | accu            | iracy. |        |      |             |

### EQUATION 19-2: TEMPERATURE RESOLUTION (°C/LSb)

$$Ma = \frac{V_{REF}}{2^N} \times Mt$$

$$\frac{V_{REF}}{2^N}$$

$$Ma = \frac{2^N}{Mv}$$

Where:

Mv = sensor voltage sensitivity (V/°C)

VREF = Reference voltage of the ADC module (in Volts)

N = Resolution of the ADC

The typical Mv value for a single diode is approximately -1.267 to -1.32 mV/C. The typical Mv value for a stack of two diodes (low range setting) is approximately -2.533 mV/C. The typical Mv value for a stack of three diodes (high range setting) is approximately -3.8 mV/C.

# **19.3 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait a minimum of 25 us for the ADC value to settle, after the ADC input multiplexer is connected to the temperature indicator output, before the conversion is performed.

# PIC16(L)F15324/44

| R/W-0/0                   | R/W-0/0      | R/W-0/0                                         | U-0             | R/W-0/0                    | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|---------------------------|--------------|-------------------------------------------------|-----------------|----------------------------|------------------|------------------|--------------|--|

|                           | N1PWS<2:0>(1 | ,2)                                             | _               |                            | N1CK             | S<3:0>           |              |  |

| bit 7                     |              |                                                 |                 |                            |                  |                  | bit (        |  |

|                           |              |                                                 |                 |                            |                  |                  |              |  |

| Legend:                   |              |                                                 |                 |                            |                  |                  |              |  |

| R = Readab                | le bit       | W = Writable b                                  | bit             | U = Unimpler               | nented bit, read | d as '0'         |              |  |

| u = Bit is und            | changed      | x = Bit is unkn                                 | own             | -n/n = Value a             | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is se           | et           | '0' = Bit is clea                               | ired            |                            |                  |                  |              |  |

|                           |              |                                                 |                 |                            |                  |                  |              |  |

| bit 7-5                   | N1PWS<2:0    | >: NCO1 Output                                  | Pulse Width     | Select bits <sup>(1)</sup> |                  |                  |              |  |

|                           |              | 1 output is activ                               |                 |                            |                  |                  |              |  |

|                           |              | 1 output is activ                               |                 |                            |                  |                  |              |  |

|                           | 101 = NCO    | D1 output is active for 32 input clock periods  |                 |                            |                  |                  |              |  |

|                           | 100 = NCO    | 1 output is activ                               | e for 16 input  | clock periods              |                  |                  |              |  |

|                           | 011 = NCO    | ICO1 output is active for 8 input clock periods |                 |                            |                  |                  |              |  |

|                           | 010 = NCO    | 1 output is activ                               | e for 4 input c | lock periods               |                  |                  |              |  |

|                           | 001 = NCO    | 1 output is activ                               | e for 2 input c | lock periods               |                  |                  |              |  |

|                           | 000 = NCO    | 1 output is activ                               | e for 1 input c | lock period                |                  |                  |              |  |

| bit 4                     | Unimplemer   | nted: Read as '0                                | )'              |                            |                  |                  |              |  |

| bit 3-0                   | N1CKS<3:0>   | >: NCO1 Clock S                                 | Source Select   | bits                       |                  |                  |              |  |

|                           | 1011-1111    | = Reserved                                      |                 |                            |                  |                  |              |  |

|                           | 1010 = LC4   | Lout                                            |                 |                            |                  |                  |              |  |

|                           | 1001 = LC3   | 3_out                                           |                 |                            |                  |                  |              |  |

|                           | 1000 = LC2   | 2_out                                           |                 |                            |                  |                  |              |  |

|                           | 0111 = LC1   | I_out                                           |                 |                            |                  |                  |              |  |

|                           | 0110 = CLH   | KR                                              |                 |                            |                  |                  |              |  |

|                           | 0101 = Res   |                                                 |                 |                            |                  |                  |              |  |

|                           | 0100 = MFI   | INTOSC (32 kHz                                  | <u>z</u> )      |                            |                  |                  |              |  |

| 0011 = MFINTOSC (500 kHz) |              |                                                 |                 |                            |                  |                  |              |  |

|                           | 0010 = LFI   | NTOSC                                           |                 |                            |                  |                  |              |  |

|                           | 0001 = HFI   | NTOSC                                           |                 |                            |                  |                  |              |  |

|                           | 0000 = Fos   | ec.                                             |                 |                            |                  |                  |              |  |

## DEOIO

**Note 1:** N1PWS applies only when operating in Pulse Frequency mode.

| FIGURE 27-4:                 | SOFTWARE GATE MODE TIMING DIAGRAM (MODE = 00000)                                                                                                                                   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Rev. 10-0001658<br>500/2014                                                                                                                                                        |

| MODE                         | 0b00000                                                                                                                                                                            |

| TMRx_clk                     |                                                                                                                                                                                    |

| Instruction <sup>(1)</sup> - | BSF BSF                                                                                                                                                                            |

| ON                           |                                                                                                                                                                                    |

| PRx                          | 5                                                                                                                                                                                  |

| TMRx                         | $0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 1 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1$                |

| TMRx_postscaled              |                                                                                                                                                                                    |

| PWM Duty<br>Cycle            | 3                                                                                                                                                                                  |

| PWM Output                   |                                                                                                                                                                                    |

|                              | BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the CPU to<br>or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input. |

### 27.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the PRx value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

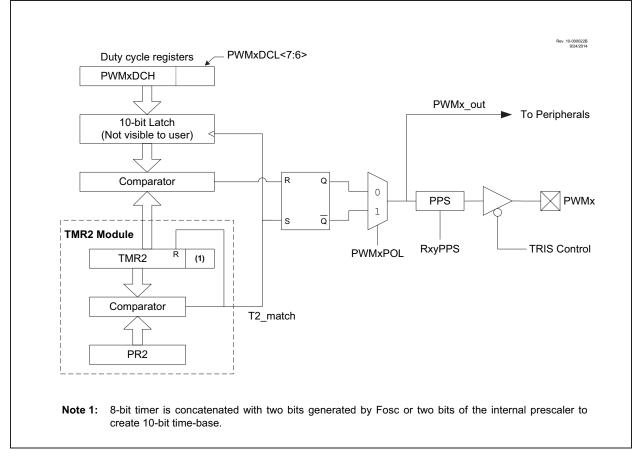

## 29.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 29-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = 0, the output will be the default state.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin

### FIGURE 29-2: SIMPLIFIED PWM BLOCK DIAGRAM

### **30.3 Selectable Input Sources**

The CWG generates the output waveforms from the input sources in Table 30-2.

### TABLE 30-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CWG input PPS pin | CWG1IN PPS  |

| CCP1              | CCP1_out    |

| CCP2              | CCP2_out    |

| PWM3              | PWM3_out    |

| PWM4              | PWM4_out    |

| PWM5              | PWM5_out    |

| PWM6              | PWM6_out    |

| NCO               | NCO1_out    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

| CLC4              | LC4_out     |

The input sources are selected using the CWG1ISM register.

## 30.4 Output Control

### 30.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

# 31.7 Register Definitions: CLC Control

| R/W-0/0         | U-0                                                                                        | R-0/0                                                                                                                                         | R/W-0/0         | R/W-0/0        | R/W-0/0         | R/W-0/0           | R/W-0/0     |  |

|-----------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-----------------|-------------------|-------------|--|

| LCxEN           |                                                                                            | LCxOUT                                                                                                                                        | LCxINTP         | LCxINTN        |                 | LCxMODE<2:0>      | •           |  |

| bit 7           |                                                                                            |                                                                                                                                               |                 |                |                 |                   | bit C       |  |

|                 |                                                                                            |                                                                                                                                               |                 |                |                 |                   |             |  |

| Legend:         |                                                                                            |                                                                                                                                               |                 |                |                 |                   |             |  |

| R = Readable    | e bit                                                                                      | W = Writable                                                                                                                                  | bit             | U = Unimpler   | nented bit, rea | ad as '0'         |             |  |

| u = Bit is unc  | hanged                                                                                     | x = Bit is unkr                                                                                                                               | nown            | -n/n = Value a | at POR and B    | OR/Value at all o | ther Resets |  |

| '1' = Bit is se | t                                                                                          | '0' = Bit is cle                                                                                                                              | ared            |                |                 |                   |             |  |

|                 |                                                                                            |                                                                                                                                               |                 |                |                 |                   |             |  |

| bit 7           |                                                                                            | igurable Logic                                                                                                                                |                 |                |                 |                   |             |  |

|                 |                                                                                            | rable logic cell is enabled and mixing input signals<br>rable logic cell is disabled and has logic zero output                                |                 |                |                 |                   |             |  |

| 1.1.0           | Ū.                                                                                         | •                                                                                                                                             |                 | nas logic zero | output          |                   |             |  |

| bit 6           | •                                                                                          | Unimplemented: Read as '0'                                                                                                                    |                 |                |                 |                   |             |  |

| bit 5           | LCxOUT: Configurable Logic Cell Data Output bit                                            |                                                                                                                                               |                 |                |                 |                   |             |  |

|                 |                                                                                            | gic cell output                                                                                                                               |                 | •              |                 |                   |             |  |

| bit 4           |                                                                                            | Configurable Logic Cell Positive Edge Going Interrupt Enable bit<br><sup>–</sup> will be set when a rising edge occurs on CLCxOUT             |                 |                |                 |                   |             |  |

|                 | 1 = CLCXIF v<br>0 = CLCXIF v                                                               |                                                                                                                                               | n a rising edge | e occurs on CL | CXOUT           |                   |             |  |

| bit 3           |                                                                                            |                                                                                                                                               | ic Cell Negativ | ve Edge Going  | Interrunt Ena   | hle hit           |             |  |

|                 |                                                                                            | <b>CxINTN:</b> Configurable Logic Cell Negative Edge Going Interrupt Enable bit<br>= CLCxIF will be set when a falling edge occurs on CLCxOUT |                 |                |                 |                   |             |  |

|                 | 0 = CLCxIFv                                                                                |                                                                                                                                               | r a rannig eag  |                |                 |                   |             |  |

| bit 2-0         | LCxMODE<2                                                                                  | ::0>: Configura                                                                                                                               | ble Logic Cell  | Functional Mo  | de bits         |                   |             |  |

|                 | 111 = Cell is                                                                              | 1-input transpa                                                                                                                               | arent latch wit | h S and R      |                 |                   |             |  |

|                 |                                                                                            | J-K flip-flop wi                                                                                                                              |                 |                |                 |                   |             |  |

|                 | 101 = Cell is 2-input D flip-flop with R<br>100 = Cell is 1-input D flip-flop with S and R |                                                                                                                                               |                 |                |                 |                   |             |  |

|                 | 100 = Cell is<br>011 = Cell is                                                             |                                                                                                                                               | lop with S and  | IR             |                 |                   |             |  |

|                 | 011 = Cell is                                                                              |                                                                                                                                               |                 |                |                 |                   |             |  |

|                 | 001 = Cell is                                                                              |                                                                                                                                               |                 |                |                 |                   |             |  |

|                 | 000 = Cell is                                                                              |                                                                                                                                               |                 |                |                 |                   |             |  |

### REGISTER 31-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

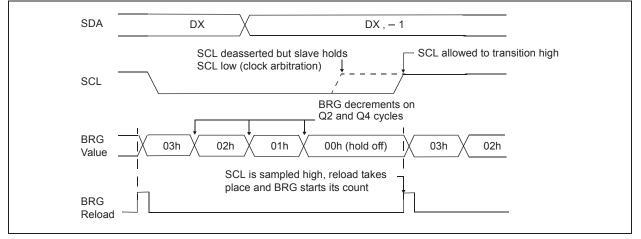

### 32.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 32-25).

### FIGURE 32-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

### 32.6.3 WCOL STATUS FLAG

If the user writes the SSP1BUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSP1BUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | writing to the lower five bits of SSP1CON2 |  |  |  |  |  |

|       | is disabled until the Start condition is   |  |  |  |  |  |

|       | complete.                                  |  |  |  |  |  |

# 33.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

### 33.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCxSTA and TXxSTA Control registers must be configured for Synchronous Slave Reception (see Section 33.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- The RXxIF interrupt flag must be cleared by reading RCxREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RXxIF interrupt flag bit of the PIR3 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

### 33.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCxSTA and TXxSTA Control registers must be configured for synchronous slave transmission (see Section 33.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXxIF interrupt flag must be cleared by writing the output data to the TXxREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXxIE bit of the PIE3 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXxIE of the PIE3 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXxREG will transfer to the TSR and the TXxIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXxREG is available to accept another character for transmission, which will clear the TXxIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# REGISTER 33-4: RCxREG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | RCxRE | G<7:0> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RCxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-2)

**Note 1:** RCxREG (including the 9<sup>th</sup> bit) is double buffered, and data is available while new data is being received.

# REGISTER 33-5: TXxREG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| TXxREG<7:0> |       |       |       |       |       |       |       |

| bit 7 bit C |       |       |       |       |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TXxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-1)

**Note 1:** TXxREG (including the 9th bit) is double buffered, and can be written when previous data has started shifting.

## **REGISTER 33-6:** SPxBRGL<sup>(1)</sup>: BAUD RATE GENERATOR REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| SPxBRG<7:0> |       |       |       |       |       |       |       |

| bit 7 bit 0 |       |       |       |       |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SPxBRG<7:0>: Lower eight bits of the Baud Rate Generator

**Note 1:** Writing to SP1BRG resets the BRG counter.

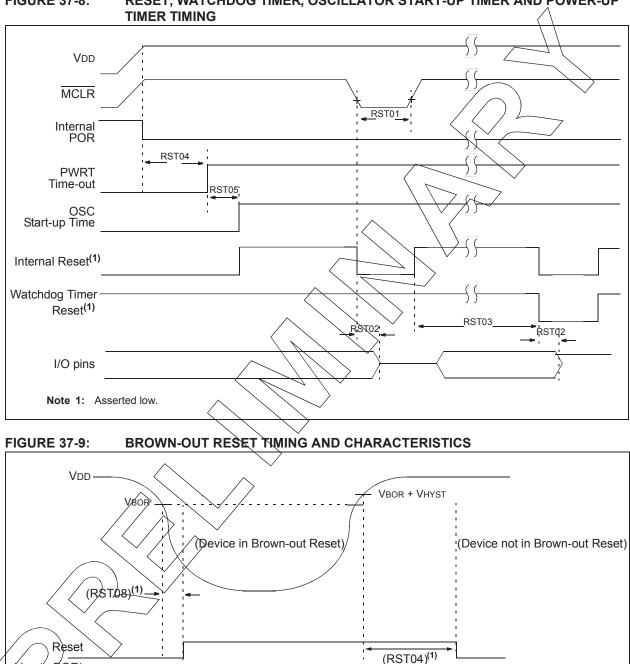

# **FIGURE 37-8:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP

(due to BOR)