Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 20-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15344t-i-gz |

DS40001889A-page 15

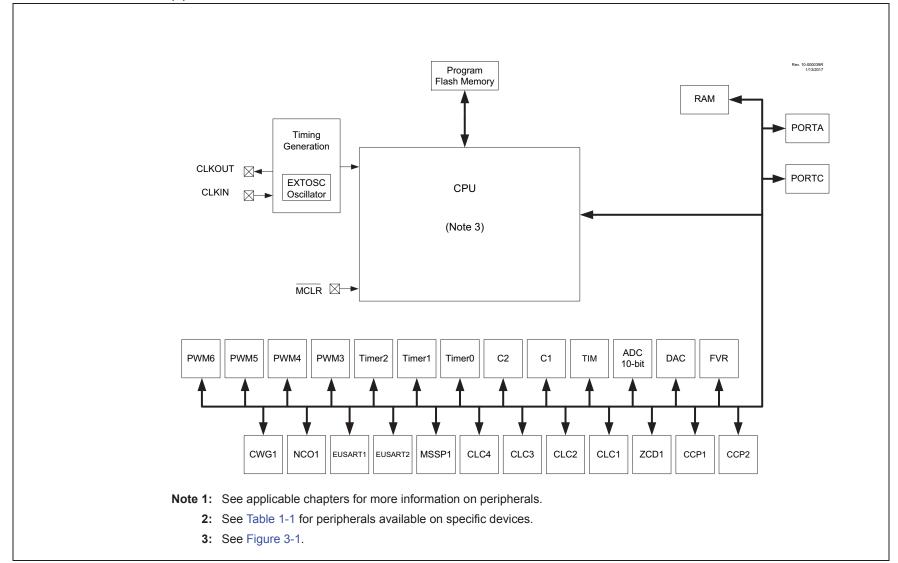

FIGURE 1-1: PIC16(L)F15324 BLOCK DIAGRAM

TABLE 1-2: PIC16(L)F15324 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                                                   | Function              | Input<br>Type    | Output Type | Description                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------|---------------------------------------------------------------------------------------------------|

| RA5/ANA5/T1CKI <sup>(1)</sup> /T2IN/CLCIN3 <sup>(1)</sup> /<br>CLKIN/OSC1/EIN/IOCA5                                                    | RA5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| OLINIVIOUS I/EIIVIOUS                                                                                                                  | ANA5                  | AN               | _           | ADC Channel A5 input.                                                                             |

|                                                                                                                                        | T1CKI <sup>(1)</sup>  | TTL/ST           | -           | Timer1 external digital clock input.                                                              |

|                                                                                                                                        | T2IN                  | TTL/ST           | _           | Timer2 external input.                                                                            |

|                                                                                                                                        | CLCIN3 <sup>(1)</sup> | TTL/ST           | _           | Configurable Logic Cell source input.                                                             |

|                                                                                                                                        | CLKIN                 | TTL/ST           | _           | External digital clock input.                                                                     |

|                                                                                                                                        | OSC1                  | XTAL             | _           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                       |

|                                                                                                                                        | EIN                   | TTL/ST           | _           | External digital clock input.                                                                     |

|                                                                                                                                        | IOCA5                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC0/ANC0/C2IN0+/SCL1 <sup>(1,4)</sup> /SCK1 <sup>(1)</sup> /TX2 <sup>(1)</sup> /CK2 <sup>(1)</sup> /IOCC0                              | RC0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| TAZI TICKZI TIOCCU                                                                                                                     | ANC0                  | AN               | _           | ADC Channel C0 input.                                                                             |

|                                                                                                                                        | C2IN0+                | AN               | _           | Comparator 2 positive input.                                                                      |

|                                                                                                                                        | SCL1 <sup>(1,4)</sup> | I <sup>2</sup> C | OD          | I <sup>2</sup> C, OD, MSSP1 I <sup>2</sup> C input/output.                                        |

|                                                                                                                                        | SCK1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK1 is a PPS remappable input and output). |

|                                                                                                                                        | TX2 <sup>(1)</sup>    | _                | CMOS        | EUSART2 asynchronous transmit.                                                                    |

|                                                                                                                                        | CK2 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART2 synchronous mode clock input/output.                                                      |

|                                                                                                                                        | IOCC0                 | TTL/ST           | -           | Interrupt-on-change input.                                                                        |

| RC1/ANC1/C1IN1-/C2IN1-/SDA1 <sup>(1,4)</sup> /<br>SDI1 <sup>(1)</sup> /RX2 <sup>(1)</sup> /DT2 <sup>(1)</sup> /CLCIN2 <sup>(1)</sup> / | RC1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| IOCC1                                                                                                                                  | ANC1                  | AN               | _           | ADC Channel C1 input.                                                                             |

|                                                                                                                                        | C1IN1-                | AN               | _           | Comparator 1 negative input.                                                                      |

|                                                                                                                                        | C2IN1-                | AN               | _           | Comparator 2 negative input.                                                                      |

|                                                                                                                                        | SDA1 <sup>(1,4)</sup> | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                  |

|                                                                                                                                        | SDI1 <sup>(1)</sup>   | TTL/ST           | _           | MSSP1 SPI serial data input.                                                                      |

|                                                                                                                                        | RX2 <sup>(1)</sup>    | TTL/ST           | _           | EUSART2 Asynchronous mode receiver data input.                                                    |

|                                                                                                                                        | DT2 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART2 Synchronous mode data input/output.                                                       |

|                                                                                                                                        | CLCIN2 <sup>(1)</sup> | TTL/ST           | _           | Configurable Logic Cell source input.                                                             |

|                                                                                                                                        | IOCC1                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC2/ANC2/C1IN2-/C2IN2-/IOCC2                                                                                                           | RC2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                                                                        | ANC2                  | AN               | _           | ADC Channel C2 input.                                                                             |

|                                                                                                                                        | C1IN2-                | AN               | _           | Comparator 1 negative input.                                                                      |

|                                                                                                                                        | C2IN2-                | AN               | _           | Comparator 2 negative input.                                                                      |

|                                                                                                                                        | IOCC2                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-3 for details on which PORT pins may be used for this signal.

- 2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

- 3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

- 4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address           | Name                                            | Bit 7  | Bit 6                                   | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------|-------------------------------------------------|--------|-----------------------------------------|-------|--------|--------|-------|-------|-------|-----------------------|----------------------------|

| Bank 20           | Bank 20                                         |        |                                         |       |        |        |       |       |       |                       |                            |

|                   | CPU CORE REGISTERS; see Table 4-3 for specifics |        |                                         |       |        |        |       |       |       |                       |                            |

| A0Ch<br>—<br>A18h | _                                               |        | Unimplemented — — —                     |       |        |        |       |       |       |                       | -                          |

| A19h              | RC2REG                                          |        |                                         |       | RC2REC | G<7:0> |       |       |       | 0000 0000             | 0000 0000                  |

| A1Ah              | TX2REG                                          |        |                                         |       | TX2REG | 6<7:0> |       |       |       | 0000 0000             | 0000 0000                  |

| A1Bh              | SP2BRGL                                         |        |                                         |       | SP2BRG | L<7:0> |       |       |       | 0000 0000             | 0000 0000                  |

| A1Ch              | SP2BRGH                                         |        |                                         |       | SP2BRG | H<7:0> |       |       |       | 0000 0000             | 0000 0000                  |

| A1Dh              | RC2STA                                          | SPEN   | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |       |        |        |       |       | RX9D  | 0000 0000             | 0000 0000                  |

| A1Eh              | TX2STA                                          | CSRC   | TX9                                     | TXEN  | SYNC   | SENDB  | BRGH  | TRMT  | TX9D  | 0000 0010             | 0000 0010                  |

| A1Fh              | BAUD2CON                                        | ABDOVF | RCIDL                                   | _     | SCKP   | BRG16  | _     | WUE   | ABDEN | 01-0 0-00             | 01-0 0-00                  |

$\textbf{Legend:} \qquad \textbf{x} \ = \text{unknown}, \textbf{u} \ = \text{unchanged}, \textbf{q} \ = \text{depends on condition}, \textbf{-} = \text{unimplemented}, \text{read as '0'}, \textbf{r} \ = \text{reserved}. \ Shaded \ locations \ unimplemented}, \text{read as '0'}.$

PIC16(L)F15324/44

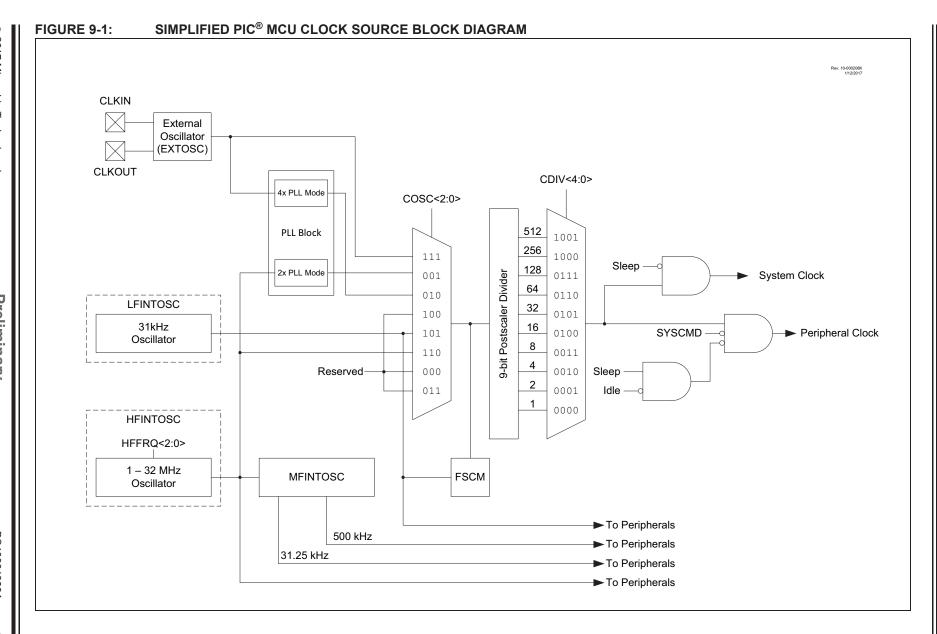

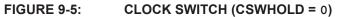

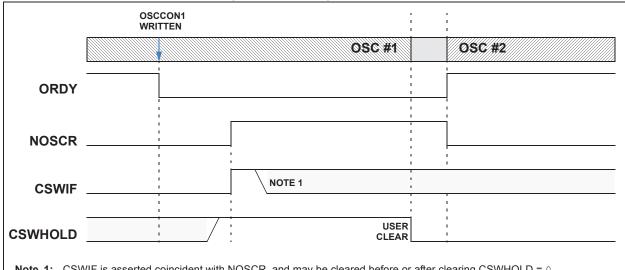

### 9.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register.

# 9.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source and the frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, and will be immediately ready. The device may enter Sleep while waiting for the switch as described in Section 9.3.3 "Clock Switch and Sleep".

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the new Oscillator's READY bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- set CSWHOLD = 0 so the switch can complete, or

- copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

#### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

**Note:** If the PLL fails to lock, the FSCM will trigger.

#### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

Note 1: CSWIF is asserted coincident with NOSCR; interrupt is serviced at OSC#2 speed.

2: The assertion of NOSCR is hidden from the user because it appears only for the duration of the switch.

#### FIGURE 9-6: CLOCK SWITCH (CSWHOLD = 1)

Note 1: CSWIF is asserted coincident with NOSCR, and may be cleared before or after clearing CSWHOLD = 0.

**Preliminary** © 2017 Microchip Technology Inc. DS40001889A-page 111

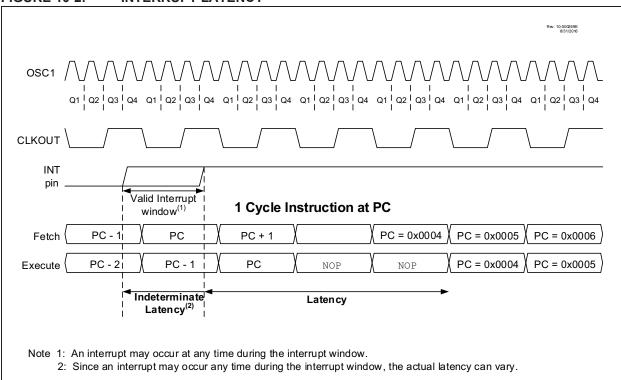

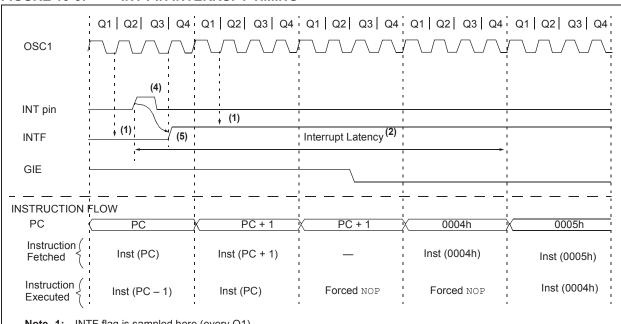

#### **FIGURE 10-3:** INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 Tcy. Synchronous latency = 3-4 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: For minimum width of INT pulse, refer to AC specifications in Section 37.0 "Electrical Specifications".

- 4: INTF may be set any time during the Q4-Q1 cycles.

**Preliminary** © 2017 Microchip Technology Inc. DS40001889A-page 123

# REGISTER 10-14: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| _     | _   | _   | _   | _   | _   | TMR2IF     | TMR1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHS = Hardware set

bit 7-2 **Unimplemented:** Read as '0' bit 1 **TRM2IF:** Timer2 Interrupt Flag bit

1 = The TMR2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be cleared

in software)

0 = No TMR2 event has occurred

bit 0 TRM1IF: Timer1 Overflow Interrupt Flag bit

1 = Timer1 overflow occurred (must be cleared in software)

0 = No Timer1 overflow occurred

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear

prior to enabling an interrupt.

TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0   | Register on Page |

|--------|--------|--------|--------|--------|-------|-------|--------|---------|------------------|

| INTCON | GIE    | PEIE   | _      | _      | _     | _     | _      | INTEDG  | 125              |

| PIE0   | 1      | 1      | TMR0IE | IOCIE  | 1     | _     | 1      | INTE    | 126              |

| PIE1   | OSFIE  | CSWIE  | I      | I      | 1     | _     | 1      | ADIE    | 127              |

| PIE2   | _      | ZCDIE  | _      | _      | -     | _     | C2IE   | C1IE    | 128              |

| PIE3   | RC2IE  | TX2IE  | RC1IE  | TX1IE  | _     | _     | BCL1IE | SSP1IE  | 129              |

| PIE4   | _      | _      | _      | _      | _     | _     | TMR2IE | TMR1IE  | 130              |

| PIE5   | CLC4IE | CLC3IE | CLC2IE | CLC1IE | _     | _     | _      | TMR1GIE | 131              |

| PIE6   | _      | _      | _      | _      | _     | _     | CCP2IE | CCP1IE  | 132              |

| PIE7   | I      | 1      | NVMIE  | NCO1IE | 1     | _     | 1      | CWG1IE  | 133              |

| PIR0   | 1      | 1      | TMR0IF | IOCIF  | 1     | _     | 1      | INTF    | 134              |

| PIR1   | OSFIF  | CSWIF  | _      | _      | _     | _     | _      | ADIF    | 135              |

| PIR2   | _      | ZCDIF  | _      | _      | -     | _     | C2IF   | C1IF    | 136              |

| PIR3   | RC2IF  | TX2IF  | RC1IF  | TX1IF  | _     | _     | BCL1IF | SSP1IF  | 137              |

| PIR4   | _      | -      | _      | -      | 1     | _     | TMR2IF | TMR1IF  | 138              |

| PIR5   | CLC4IF | CLC3IF | CLC2IF | CLC1IF |       | _     |        | TMR1GIF | 139              |

| PIR6   |        | -      |        |        | -     | _     | CCP2IF | CCP1IF  | 140              |

| PIR7   | _      | _      | NVMIF  | NCO1IF | _     | _     | _      | CWG1IF  | 141              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

# REGISTER 26-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u | R-x/x | U-0 | U-0   |

|---------|---------|---------|---------|------------|-------|-----|-------|

| GE      | GPOL    | GTM     | GSPM    | GGO/DONE   | GVAL  | _   | _     |

| bit 7   |         |         |         |            |       |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7   | GE: Timer1 Gate Enable bit                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If ON = 0</u> :                                                                                                                                             |

|         | This bit is ignored                                                                                                                                            |

|         | If ON = 1:                                                                                                                                                     |

|         | <ul><li>1 = Timer1 counting is controlled by the Timer1 gate function</li><li>0 = Timer1 is always counting</li></ul>                                          |

| bit 6   | GPOL: Timer1 Gate Polarity bit                                                                                                                                 |

| Dit 0   | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                                               |

|         | 0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                                                                 |

| bit 5   | GTM: Timer1 Gate Toggle Mode bit                                                                                                                               |

|         | 1 = Timer1 Gate Toggle mode is enabled                                                                                                                         |

|         | 0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared                                                                                        |

|         | Timer1 gate flip-flop toggles on every rising edge.                                                                                                            |

| bit 4   | GSPM: Timer1 Gate Single-Pulse Mode bit                                                                                                                        |

|         | 1 = Timer1 Gate Single-Pulse mode is enabled                                                                                                                   |

|         | 0 = Timer1 Gate Single-Pulse mode is disabled                                                                                                                  |

| bit 3   | GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                                                                                                      |

|         | 1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge                                                                                         |

|         | <ul> <li>Timer1 gate single-pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when GSPM is cleared</li> </ul> |

| bit 2   | GVAL: Timer1 Gate Value Status bit                                                                                                                             |

|         | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L Unaffected by Timer1 Gate Enable (GE)                                     |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                     |

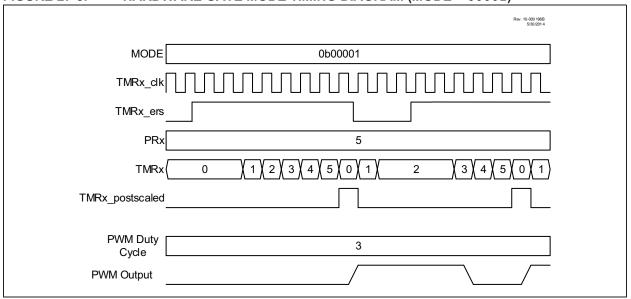

#### 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

FIGURE 27-5: HARDWARE GATE MODE TIMING DIAGRAM (MODE = 00001)

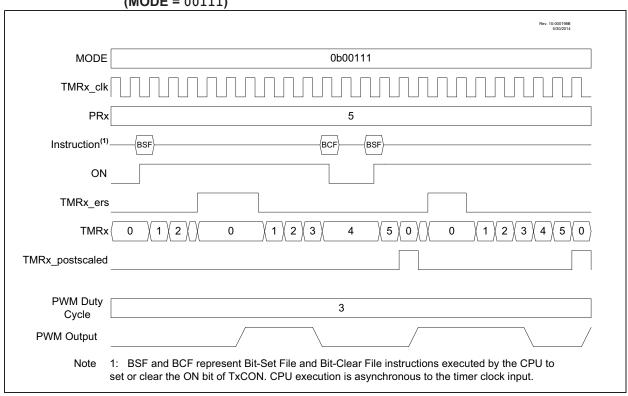

# 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

FIGURE 27-7: LEVEL-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00111)

#### 28.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See Section 15.0 "Peripheral Pin Select (PPS) Module" for more details.

The CCP output can also be used as an input for other peripherals.

Note:

Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 28.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note

Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, Tlmer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 28.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to Section 20.2.4 "Auto-Conversion Trigger" for more information.

Note:

Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring

#### 28.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

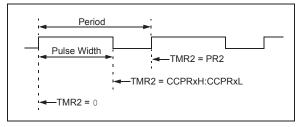

# 28.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 28-3 shows a typical waveform of the PWM signal.

#### 28.3.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- · T2CON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 28-4 shows a simplified block diagram of PWM operation.

Note:

The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

### FIGURE 28-3: CCP PWM OUTPUT SIGNAL

# TABLE 28-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

# TABLE 28-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 28.3.8 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

# 28.3.9 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

## 28.3.10 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# REGISTER 30-7: CWG1STR: CWG1 STEERING CONTROL REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|---------|---------|---------|---------|---------------------|---------------------|---------------------|---------------------|

| OVRD    | OVRC    | OVRB    | OVRA    | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7   |         |         |         |                     |                     |                     | bit 0               |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | OVRD: Steering Data D bit                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | OVRC: Steering Data C bit                                                                                                                            |

| bit 5 | OVRB: Steering Data B bit                                                                                                                            |

| bit 4 | OVRA: Steering Data A bit                                                                                                                            |

| bit 3 | STRD: Steering Enable D bit <sup>(2)</sup>                                                                                                           |

|       | $_1$ = CWG1D output has the CWG1_data waveform with polarity control from POLD bit $_0$ = CWG1D output is assigned the value of OVRD bit             |

| bit 2 | STRC: Steering Enable C bit <sup>(2)</sup>                                                                                                           |

|       | $_{\rm 1}$ = CWG1C output has the CWG1_data waveform with polarity control from POLC bit $_{\rm 0}$ = CWG1C output is assigned the value of OVRC bit |

| bit 1 | STRB: Steering Enable B bit <sup>(2)</sup>                                                                                                           |

|       | $_1$ = CWG1B output has the CWG1_data waveform with polarity control from POLB bit $_0$ = CWG1B output is assigned the value of OVRB bit             |

| bit 0 | STRA: Steering Enable A bit <sup>(2)</sup>                                                                                                           |

|       | $_1$ = CWG1A output has the CWG1_data waveform with polarity control from POLA bit $_0$ = CWG1A output is assigned the value of OVRA bit             |

|       |                                                                                                                                                      |

**Note 1:** The bits in this register apply only when MODE<2:0> = 00x.

**2:** This bit is effectively double-buffered when MODE<2:0> = 001.

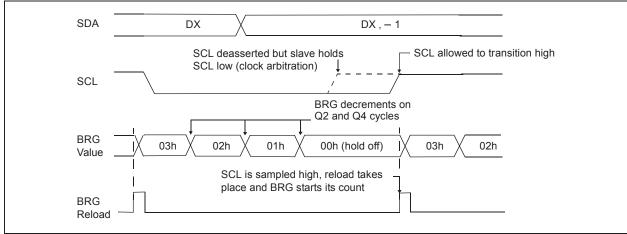

#### 32.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 32-25).

#### 32.6.3 WCOL STATUS FLAG

If the user writes the SSP1BUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSP1BUF was attempted while the module was not idle.

Note: Because queuing of events is not allowed, writing to the lower five bits of SSP1CON2 is disabled until the Start condition is complete.

#### REGISTER 33-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R-0/0 |  |  |  |

|---------------------|---------|---------|---------|---------|-------|-------|-------|--|--|--|

| SPEN <sup>(1)</sup> | RX9     | SREN    | CREN    | ADDEN   | FERR  | OERR  | RX9D  |  |  |  |

| bit 7 bit 0         |         |         |         |         |       |       |       |  |  |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 SPEN: Serial Port Enable bit<sup>(1)</sup>

1 = Serial port enabled

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-Bit Receive Enable bit

1 = Selects 9-bit reception0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Unused in this mode – value ignored

Synchronous mode - Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave

Unused in this mode - value ignored

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared

0 = Disables continuous receive

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection – enable interrupt and load of the receive buffer when the ninth bit in the receive buffer is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

<u>Asynchronous mode 8-bit (RX9 = 0)</u>: Unused in this mode – value ignored

bit 2 **FERR:** Framing Error bit

1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR:** Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** Ninth bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

**Note 1:** The EUSART module automatically changes the pin from tri-state to drive as needed. Configure the associated TRIS bits for TX/CK and RX/DT to 1.

# 37.0 ELECTRICAL SPECIFICATIONS

# 37.1 Absolute Maximum Ratings<sup>(†)</sup>

Ambient temperature under bias -40°C to +125°C Storage temperature ......-65°C to +150°C Voltage on pins with respect to Vss on VDD pin PIC16F15324/44 ...... -0.3V to +6.5V PIC16LF15324/44 -0.3V to +4.0V -0.3V to +9.0V on MCLR pin ..... ......0.3V to (VDD + 0.3V) on all other pins Maximum current on Vss pin<sup>(1)</sup>  $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ ..... 250 mA  $85^{\circ}C < TA \le +125^{\circ}C$  ..... on VDD pin for 28-Pin devices(1)  $-40^{\circ}C \le TA \le +85^{\circ}C$  $85^{\circ}C < TA \le +125^{\circ}C$  ..... on VDD pin for 40-Pin devices(1)  $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ 85°C < TA ≤ +125°C ..... ...... 120 mA on any standard I/O pin ..... Clamp current, IK (VPIN < 0 or VPIN > VDD)

Note 1: Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 37-6 to calculate device specifications.

2: Power dissipation is calculated as follows:

Total power dissipation<sup>(2)</sup>.....

PDIS = VDD x{IDO -  $\Sigma$ 10x1} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$  (VOI x IOL)

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

# 37.2 **Standard Operating Conditions** The standard operating conditions for any device are defined as: Operating Voltage: $V \mathsf{DDMIN} \leq V \mathsf{DD} \leq V \mathsf{DDMAX}$ Operating Temperature: $TA\_MIN \le TA \le TA\_MAX$ **VDD** — Operating Supply Voltage<sup>(1)</sup> PIC16LF15324/44 VDDMIN (Fosc ≤ 16 MHz) ..... VDDMIN (Fosc ≤ 32 MHz) ..... +2.5V VDDMAX..... .....+3.6V PIC16F15324/44 VDDMIN (Fosc ≤ 16 MHz) ..... VDDMIN (Fosc ≤ 32 MHz) ..... VDDMAX ..... TA — Operating Ambient Temperature Range **Industrial Temperature** TA MAX..... **Extended Temperature** TA\_MIN ..... Note 1: See Parameter Supply Voltage, DS Characteristics: Supply Voltage.

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |      |      |  |

|-------------------------|-------------|-----------|------|------|--|

| Dimension L             |             | MIN       | NOM  | MAX  |  |

| Number of Terminals     | N           | 20        |      |      |  |

| Pitch                   | е           | 0.50 BSC  |      |      |  |

| Overall Height          | Α           | 0.45      | 0.50 | 0.55 |  |

| Standoff                | A1          | 0.00      | 0.02 | 0.05 |  |

| Terminal Thickness      | A3          | 0.127 REF |      |      |  |

| Overall Width           | Е           | 4.00 BSC  |      |      |  |

| Exposed Pad Width       | E2          | 2.60      | 2.70 | 2.80 |  |

| Overall Length          | D           | 4.00 BSC  |      |      |  |

| Exposed Pad Length      | D2          | 2.60      | 2.70 | 2.80 |  |

| Terminal Width          | b           | 0.20      | 0.25 | 0.30 |  |

| Terminal Length         | L           | 0.30      | 0.40 | 0.50 |  |

| Terminal-to-Exposed-Pad | K           | 0.20      | -    | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2