# E·XFL

#### NXP USA Inc. - MKV46F256VLL15 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 150MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                |

| Number of I/O              | 74                                                                     |

| Program Memory Size        | 256КВ (256К х 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv46f256vll15 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol           | Description                                            | Min. | Тур. | Max. | Unit | Notes |

|------------------|--------------------------------------------------------|------|------|------|------|-------|

| V <sub>BG</sub>  | Bandgap voltage reference                              | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub> | Internal low power oscillator period — factory trimmed | 900  | 1000 | 1100 | μs   |       |

### Table 3. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

### 2.2.3 PORT Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

| Symbol                       | Description                                                  | Notes <sup>1</sup> | Min                                     | Тур                    | Max                                     | Unit | Test<br>Conditions                                                     |

|------------------------------|--------------------------------------------------------------|--------------------|-----------------------------------------|------------------------|-----------------------------------------|------|------------------------------------------------------------------------|

| V <sub>OH</sub> <sup>2</sup> | Output Voltage High                                          | Pin Group 1        | V <sub>DD</sub> - 0.5                   | —                      |                                         | V    | I <sub>OH</sub> = I <sub>OHmax</sub>                                   |

| V <sub>OL</sub>              | Output Voltage Low                                           | Pin Groups<br>1, 2 |                                         | _                      | 0.5                                     | V    | $I_{OL} = I_{OLmax}$                                                   |

| IIH                          | Digital Input Current High<br>pull-up enabled or<br>disabled | Pin Groups<br>1, 2 | _                                       | 0                      | +/- 2.5                                 | μA   | V <sub>IN</sub> = 2.4V<br>to 5.5V                                      |

| I <sub>IHC</sub>             | Comparator Input Current<br>High                             | Pin Group 3        | _                                       | 0                      | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                                     |

| I <sub>IHOSC</sub>           | Oscillator Input Current<br>High                             | Pin Group 3        | _                                       | 0                      | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                                     |

| IL                           | Digital Input Current Low<br>• pull-up enabled               | Pin Groups<br>1, 2 | TBD                                     | TBD                    | TBD                                     | μA   | $V_{IN} = 0V$                                                          |

|                              | pull-up disabled                                             |                    | TBD                                     | TBD                    | TBD                                     |      |                                                                        |

| R <sub>Pull-Up</sub>         | Internal Pull-Up<br>Resistance                               |                    | 20                                      | _                      | 50                                      | kΩ   | —                                                                      |

| I <sub>ILC</sub>             | Comparator Input Current<br>Low                              | Pin Group 3        |                                         | 0                      | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                                   |

| I <sub>ILOSC</sub>           | Oscillator Input Current<br>Low                              | Pin Group 3        | _                                       | 0                      | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                                   |

| V <sub>DAC</sub>             | DAC Output Voltage<br>Range                                  | Pin Group 5        | Typically<br>V <sub>SSA</sub> +<br>40mV | _                      | Typically<br>V <sub>DDA</sub> -<br>40mV | V    | $\begin{array}{c} R_{LD}=3\ k\Omega\\ II\ C_{LD}=400\\ pf \end{array}$ |

| I <sub>OZ</sub>              | Output Current <sup>1</sup><br>High Impedance State          | Pin Groups<br>1, 2 |                                         | 0                      | +/- 2.5                                 | μA   | —                                                                      |

| V <sub>HYS</sub>             | Schmitt Trigger Input<br>Hysteresis                          | Pin Groups<br>1, 2 |                                         | 0.06 x V <sub>DD</sub> |                                         | V    | -                                                                      |

| C <sub>IN</sub>              | Input Capacitance                                            |                    |                                         | 10                     | —                                       | pF   |                                                                        |

| C <sub>OUT</sub>             | Output Capacitance                                           |                    | _                                       | 10                     | —                                       | pF   | —                                                                      |

#### 1. Default Mode

• Pin Group 1: GPIO, TDI, TDO, TMS, TCK

### Table 6. Power consumption operating behaviors (All IDDs are Target values) (continued)

| Symbol                | Description                                                                                                                   | Min. | Тур.  | Max. | Unit | Notes                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|--------------------------------------------------------------------------------|

|                       |                                                                                                                               |      |       |      |      | and clocked at 5 MHz.                                                          |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks<br>disabled, code executing from flash, excludes<br>ADC IDDA                         |      |       |      |      | ADC/DAC<br>powered on<br>and clocked a                                         |

|                       | • @ 1.8V                                                                                                                      |      | 6.5   | 14   | mA   | 5 MHz. Core<br>frequency of 2                                                  |

|                       | • @ 3.0V                                                                                                                      | _    | 6.6   | 15   | mA   | MHz                                                                            |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks<br>disabled, code executing from flash, excludes<br>ADC IDDA<br>• @ 1.8V<br>• @ 3.0V |      |       |      |      | ADC/DAC<br>powered on<br>and clocked a<br>5 MHz. Core<br>frequency of 5<br>MHz |

|                       |                                                                                                                               | —    | 9.6   | 18   | mA   |                                                                                |

|                       |                                                                                                                               |      | 9.8   | 20   | mA   |                                                                                |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks<br>disabled, code executing from flash, excludes<br>ADC IDDA                         |      |       |      |      | ADC/DAC<br>powered on<br>and clocked a<br>5 MHz. Core                          |

|                       | • @ 1.8V                                                                                                                      | —    | 16.1  | 18   | mA   | frequency of                                                                   |

|                       | • @ 3.0V                                                                                                                      |      | 16.2  | 20   | mA   | 100 MHz.                                                                       |

| I <sub>DD_HSRUN</sub> | Run mode current — all peripheral clocks<br>disabled, code executing from flash, excludes<br>ADC IDDA                         |      |       |      |      | ADC/DAC<br>powered on<br>and clocked a                                         |

|                       | • @ 1.8V                                                                                                                      | —    | 25.3  | 50   | mA   | 5 MHz. Core<br>frequency of                                                    |

|                       | • @ 3.0V                                                                                                                      |      | 25.7  | 60   | mA   | 150 MHz.                                                                       |

| I <sub>DD_HSRUN</sub> | Run mode current — all peripheral clocks<br>enabled, code executing from flash,excludes<br>ADC IDDA                           |      |       |      |      | ADC/DAC<br>powered on<br>and clocked a                                         |

|                       | <ul> <li>@ 1.8V @ ambient</li> <li>@ 3.0V</li> </ul>                                                                          | —    | 33.7  | 90   | mA   | 5 MHz. Core<br>frequency of<br>150 MHz.                                        |

|                       | • @ 25°C                                                                                                                      | —    | 33.1  | 100  | mA   | Nanoedge                                                                       |

|                       | • @ 105°C                                                                                                                     |      | 39.6  | 120  | mA   | module at 75<br>MHz.                                                           |

| I <sub>DD_WAIT</sub>  | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled                                                    | _    | 8.6   |      | mA   |                                                                                |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled                                                     | _    | 0.574 | _    | mA   | CPU freq 4Mh                                                                   |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled                                                      | —    | 0.836 | _    | mA   | CPU freq 4Mh                                                                   |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V — all peripheral clocks disabled                                                    | —    | 0.285 | —    | mA   | 2Mhz bus<br>frequency                                                          |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                                                                    |      |       |      |      |                                                                                |

|                       |                                                                                                                               | _    | 0.366 | 2    |      |                                                                                |

Table continues on the next page...

| Symbol                 | Description                                                                       | Min. | Тур.  | Max. | Unit | Notes |

|------------------------|-----------------------------------------------------------------------------------|------|-------|------|------|-------|

|                        | <ul> <li>@ -40 to 25°C</li> </ul>                                                 | —    | 0.868 | TBD  | mA   |       |

|                        | • @ 70°C                                                                          | —    | 3.5   | TBD  | mA   |       |

|                        | • @ 105°C                                                                         |      |       |      | mA   |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 3.0 V                                         |      |       |      |      |       |

|                        | ● @ -40 to 25°C                                                                   | —    | 0.059 | TBD  | μA   |       |

|                        | • @ 70°C                                                                          | —    | _     | TBD  | μA   |       |

|                        | • @ 105°C                                                                         | —    | 0.717 | TBD  | μA   |       |

| I <sub>DD_VLLS3</sub>  | Very low-leakage stop mode 3 current at 3.0                                       |      |       |      |      |       |

|                        | V                                                                                 | —    | 0.124 | TBD  | mA   |       |

|                        | • @ -40 to 25°C                                                                   | —    | 3.8   | TBD  | mA   |       |

|                        | • @ 70°C                                                                          | —    | _     | TBD  | mA   |       |

|                        | • @ 105°C                                                                         |      |       |      |      |       |

| I <sub>DD_VLLS2</sub>  | Very low-leakage stop mode 2 current at 3.0<br>V                                  |      |       |      |      |       |

|                        |                                                                                   | —    | 0.122 | TBD  | mA   |       |

|                        | • @ -40 to 25°C                                                                   | —    | 3.7   | TBD  | mA   |       |

|                        | • @ 70°C                                                                          | —    | 4.1   | TBD  | mA   |       |

|                        | • @ 105°C                                                                         |      |       |      |      |       |

| I <sub>DD_VLLS1</sub>  | Very low-leakage stop mode 1 current at 3.0                                       |      |       |      |      |       |

|                        | V                                                                                 | —    | 749   | TBD  | nA   |       |

|                        | • @ -40 to 25°C                                                                   | —    | 2.2   | TBD  | μA   |       |

|                        | • @ 70°C                                                                          | —    | 9.9   | TBD  | μA   |       |

|                        | • @ 105°C                                                                         |      |       |      |      |       |

| IDD_VLLS0B             | Very low-leakage stop mode 0 current at 3.0<br>V with POR detect circuit enabled  |      |       |      |      |       |

|                        | • @ -40 to 25°C                                                                   |      | 470   | TBD  | nA   |       |

|                        | • @ 70°C                                                                          |      | 1.9   | TBD  | μA   |       |

|                        | • @ 105°C                                                                         | _    | 9.5   | TBD  | μΑ   |       |

| I <sub>DD_VLLS0A</sub> | Very low-leakage stop mode 0 current at 3.0<br>V with POR detect circuit disabled |      |       |      |      |       |

|                        | • @ -40 to 25°C                                                                   |      | 180   | TBD  | nA   |       |

|                        | • @ 70°C                                                                          |      | 1.6   | TBD  |      |       |

|                        | • @ 105°C                                                                         |      |       |      | μΑ   |       |

|                        |                                                                                   | _    | 9.1   | TBD  | μA   |       |

### Table 6. Power consumption operating behaviors (All IDDs are Target values) (continued)

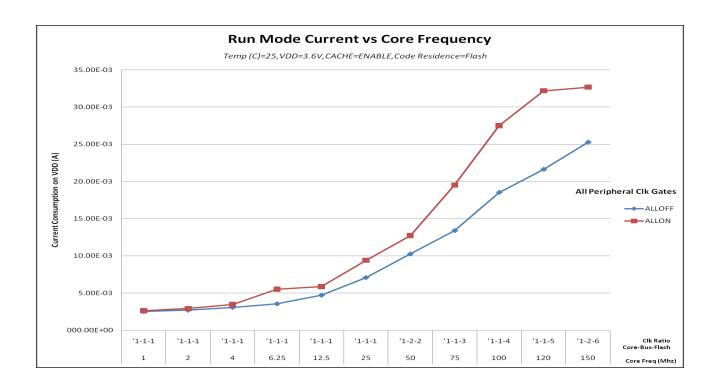

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 3. Run mode supply current vs. core frequency

### 2.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, and I<sup>2</sup>C signals.

| Symbol | Description                                                                        | Min. | Max. | Unit                | Notes |

|--------|------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path | 1.5  | _    | Bus clock<br>cycles | 1     |

|        | External RESET and NMI pin interrupt pulse width — Asynchronous path               | 100  | -    | ns                  | 2     |

|        | GPIO pin interrupt pulse width — Asynchronous path                                 | 16   | _    | ns                  | 2     |

|        | Port rise and fall time                                                            |      |      |                     | 3     |

|        | Fast slew rate                                                                     |      |      |                     |       |

|        | 1.71≤ VDD ≤ 2.7 V                                                                  | —    | 8    | ns                  |       |

|        | 2.7 ≤ VDD ≤ 3.6 V                                                                  | —    | 7    | ns                  |       |

|        | Port rise and fall time                                                            |      |      |                     |       |

|        | Slow slew rate                                                                     |      |      |                     |       |

|        | 1.71≤ VDD ≤ 2.7 V                                                                  | —    | 25   | ns                  |       |

|        | 2.7 ≤ VDD ≤ 3.6 V                                                                  | —    | 15   | ns                  |       |

Table 11. General switching specifications

1. The greater synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

3. For high drive pins with high drive enabled, load is 75pF; other pins load (low drive) is 25pF.

# 2.4 Thermal specifications

### 2.4.1 Thermal operating requirements Table 12. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| $T_J$          | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

| Board type        | Symbol            | Description                                                                                              | 100<br>LQFP | 64 LQFP | 48 LQFP | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|-------------|---------|---------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 62          | 64      | 81      | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 49          | 46      | 57      | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 52          | 52      | 68      | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 43          | 39      | 51      | °C/W |       |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 35          | 28      | 35      | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 17          | 15      | 25      | °C/W | 3     |

|                   | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 3           | 2       | 7       | °C/W | 4     |

### 2.4.2 Thermal attributes

| Board type        | Symbol            | Description                                                                                              | LQFP | 64 LQFP | 48 LQFP | Unit | NOTE |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|------|---------|---------|------|------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 62   | 64      | 81      | °C/W | 1    |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 49   | 46      | 57      | °C/W |      |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 52   | 52      | 68      | °C/W |      |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 43   | 39      | 51      | °C/W |      |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 35   | 28      | 35      | °C/W | 2    |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 17   | 15      | 25      | °C/W | 3    |

|                   | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 3    | 2       | 7       | °C/W | 4    |

#### Table 13. Thermal attributes

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions – Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions-Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions-Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, Test Method Standard, Microcircuits, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions-Natural Convection (Still Air).

#### Peripheral operating requirements and behaviors 3

## 3.1 Core modules

### 3.1.1 SWD Electricals

Table 14. SWD full voltage range electricals

| Symbol | Description                    | Min. | Max. | Unit |

|--------|--------------------------------|------|------|------|

|        | Operating voltage              | 1.71 | 3.6  | V    |

| J1     | SWD_CLK frequency of operation |      |      |      |

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Symbol                   | Description                                                                |                                                                           | Min.   | Тур. | Max.                                                          | Unit | Notes |

|--------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|--------|------|---------------------------------------------------------------|------|-------|

|                          |                                                                            | $2929 \times f_{fll_ref}$                                                 |        |      |                                                               |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter                                                          |                                                                           | _      | 180  | _                                                             | ps   |       |

|                          | <ul> <li>f<sub>DCO</sub> = 48 M</li> <li>f<sub>DCO</sub> = 98 M</li> </ul> |                                                                           | _      | 150  | _                                                             |      |       |

| t <sub>fll_acquire</sub> | FLL target frequer                                                         | cy acquisition time                                                       | _      | _    | 1                                                             | ms   | 6     |

|                          |                                                                            |                                                                           | PLL    |      |                                                               |      |       |

| f <sub>pll_ref</sub>     | PLL reference free                                                         | luency range                                                              | 8      | _    | 16                                                            | MHz  |       |

| f <sub>vcoclk_2x</sub>   | VCO output freque                                                          | ency                                                                      | 180    | _    | 360                                                           | MHz  |       |

| f <sub>vcoclk</sub>      | PLL output freque                                                          | ncy                                                                       | 90     | _    | 180                                                           | MHz  |       |

| f <sub>vcoclk_90</sub>   | PLL quadrature ou                                                          | Itput frequency                                                           | 90     | _    | 180                                                           | MHz  |       |

| I <sub>pll</sub>         |                                                                            | rent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz,<br>Hz, VDIV multiplier = 22) | _      | 2.8  | -                                                             | mA   | 7     |

| I <sub>pll</sub>         | PLL operating curv<br>• VCO @ 360<br>f <sub>pll_ref</sub> = 8 MH           | rent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz,<br>Hz, VDIV multiplier = 45) | -      | 4.7  | —                                                             | mA   | 7     |

| J <sub>cyc_pll</sub>     | PLL period jitter (F                                                       | RMS)                                                                      |        |      |                                                               |      | 8     |

|                          | • f <sub>vco</sub> = 48 MH                                                 | z                                                                         | _      | 120  |                                                               | ps   |       |

|                          | • f <sub>vco</sub> = 120 M                                                 | Hz                                                                        | _      | 75   | _                                                             | ps   |       |

| J <sub>acc_pll</sub>     | PLL accumulated                                                            | jitter over 1µs (RMS)                                                     |        |      |                                                               |      | 8     |

| _                        | • f <sub>vco</sub> = 48 MH                                                 | z                                                                         | _      | 1350 |                                                               | ps   |       |

|                          | • f <sub>vco</sub> = 120 M                                                 | Hz                                                                        | _      | 600  | _                                                             | ps   |       |

| D <sub>unl</sub>         | Lock exit frequence                                                        | y tolerance                                                               | ± 4.47 | _    | ± 5.97                                                        | %    |       |

| t <sub>pll_lock</sub>    | Lock detector dete                                                         | ection time                                                               | -      | —    | 150 × 10 <sup>-6</sup><br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S    | 9     |

### Table 18. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 8. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

### **3.3.2 Oscillator electrical specifications**

### 3.3.2.1 Oscillator DC electrical specifications Table 19. Oscillator DC electrical specifications

| Symbol         | Description                                                    | Min. | Тур. | Max. | Unit | Notes |

|----------------|----------------------------------------------------------------|------|------|------|------|-------|

| $V_{DD}$       | Supply voltage                                                 | 1.71 | —    | 3.6  | V    |       |

| IDDOSC         | Supply current — low-power mode (HGO=0)                        |      |      |      |      | 1     |

|                | • 32 kHz                                                       | —    | 500  | _    | nA   |       |

|                | • 4 MHz                                                        | —    | 200  | _    | μA   |       |

|                | • 8 MHz                                                        | —    | 300  | _    | μA   |       |

|                | • 16 MHz                                                       | —    | 950  | _    | μA   |       |

|                | • 24 MHz                                                       | —    | 1.2  | _    | mA   |       |

|                | • 32 MHz                                                       | _    | 1.5  | _    | mA   |       |

| IDDOSC         | Supply current — high gain mode (HGO=1)                        |      |      |      |      | 1     |

|                | • 4 MHz                                                        | _    | 400  | _    | μA   |       |

|                | • 8 MHz                                                        | _    | 500  | _    | μA   |       |

|                | • 16 MHz                                                       | —    | 2.5  | _    | mA   |       |

|                | • 24 MHz                                                       | —    | 3    | _    | mA   |       |

|                | • 32 MHz                                                       | —    | 4    | _    | mA   |       |

| C <sub>x</sub> | EXTAL load capacitance                                         |      | _    |      |      | 2, 3  |

| Cy             | XTAL load capacitance                                          | _    | _    | —    |      | 2, 3  |

| $R_F$          | Feedback resistor — low-frequency, low-power mode (HGO=0)      | —    | _    | _    | MΩ   | 2, 4  |

|                | Feedback resistor — low-frequency, high-gain mode (HGO=1)      | —    | 10   |      | MΩ   |       |

|                | Feedback resistor — high-frequency, low-<br>power mode (HGO=0) | —    | —    | _    | MΩ   |       |

|                | Feedback resistor — high-frequency, high-gain mode (HGO=1)     | _    | 1    | _    | MΩ   |       |

| $R_S$          | Series resistor — low-frequency, low-power mode (HGO=0)        | _    | _    | _    | kΩ   |       |

|                | Series resistor — low-frequency, high-gain mode (HGO=1)        | _    | 200  | —    | kΩ   |       |

|                | Series resistor — high-frequency, low-power<br>mode (HGO=0)    | —    | -    | —    | kΩ   |       |

|                | Series resistor — high-frequency, high-gain mode (HGO=1)       |      |      |      |      |       |

|                |                                                                | _    | 0    | _    | kΩ   |       |

Table continues on the next page...

| Characteristic                                         | Symbol             | Min               | Тур               | Max               | Unit             |

|--------------------------------------------------------|--------------------|-------------------|-------------------|-------------------|------------------|

| Input Voltage Range                                    | V <sub>ADIN</sub>  | V <sub>REFL</sub> |                   | V <sub>REFH</sub> | V                |

| External Reference                                     |                    | V <sub>SSA</sub>  |                   | V <sub>DDA</sub>  |                  |

| Internal Reference                                     |                    | ▼ SSA             |                   | ▼ DDA             |                  |

| Timing and Power                                       | 1                  |                   |                   |                   |                  |

| Conversion Time                                        | t <sub>ADC</sub>   |                   | 6                 |                   | ADC Clock Cycles |

| ADC Power-Up Time (from adc_pdn)                       | t <sub>ADPU</sub>  |                   | 13                |                   | ADC Clock Cycles |

| ADC RUN Current (per ADC block)                        | I <sub>ADRUN</sub> |                   |                   |                   | mA               |

| • at 600 kHz ADC Clock, LP mode                        |                    |                   | 1                 |                   |                  |

| • ≤ 8.33 MHz ADC Clock, 00 mode                        |                    |                   | 5.7               |                   |                  |

| • ≤ 12.5 MHz ADC Clock, 01 mode                        |                    |                   | 10.5              |                   |                  |

| • ≤ 16.67 MHz ADC Clock, 10 mode                       |                    |                   | 17.7              |                   |                  |

| <ul> <li>≤ 20 MHz ADC Clock, 11 mode</li> </ul>        |                    |                   | 22.6              |                   |                  |

| <ul> <li>≤ 25 MHz ADC Clock</li> </ul>                 |                    |                   | TBD               |                   |                  |

|                                                        |                    |                   |                   |                   |                  |

| ADC Powerdown Current (adc_pdn enabled)                | IADPWRDWN          |                   | 0.02              |                   | μΑ               |

| V <sub>REFH</sub> Current                              | I <sub>VREFH</sub> |                   | 0.001             |                   | μΑ               |

| Accuracy (DC or Absolute)                              |                    |                   | · ·               |                   |                  |

| Integral non-Linearity                                 | I <sub>NL</sub>    |                   | +/- 3             | +/- 5             | LSB              |

| Differential non-Linearity <sup>1</sup>                | DNL                |                   | +/- 0.6           | +/- 0.9           | LSB <sup>2</sup> |

| Monotonicity                                           | 1                  |                   |                   |                   |                  |

| Offset                                                 | VOFFSET            |                   |                   | +/- 17            | mV               |

| <ul><li>1x gain mode</li><li>2x gain mode</li></ul>    |                    |                   |                   | +/- 20            |                  |

| <ul> <li>2x gain mode</li> <li>4x gain mode</li> </ul> |                    |                   |                   | +/- 25            |                  |

| Gain Error                                             | E <sub>GAIN</sub>  |                   | 0.801 to<br>0.809 | 0.798 to<br>0.814 |                  |

| AC Specifications                                      | -1                 |                   | 4                 | · · · · · ·       |                  |

| Signal to Noise Ratio                                  | SNR                |                   | 59                |                   | dB               |

| Total Harmonic Distortion                              | THD                |                   | 64                |                   | dB               |

| Spurious Free Dynamic Range                            | SFDR               |                   | 65                |                   | dB               |

| Signal to Noise plus Distortion                        | SINAD              |                   | 59                |                   | dB               |

| Effective Number of Bits                               | ENOB               |                   | 9.5               |                   | bits             |

| ADC Inputs                                             |                    |                   |                   |                   |                  |

| Input Leakage Current                                  | I <sub>IN</sub>    |                   | 0                 | +/-2              | μA               |

| Input Injection Current                                | I <sub>INJ</sub>   |                   |                   | +/-3              | mA               |

| Input Capacitance                                      | C <sub>ADI</sub>   |                   | 4.8               |                   | pF               |

| Sampling Capacitor                                     |                    |                   |                   |                   |                  |

Table 25. 12-bit ADC electrical specifications (continued)

1.  $I_{NL}$  measured from  $V_{IN} = V_{REFL}$  to  $V_{IN} = V_{REFH}$ . 2. LSB = Least Significant Bit = 0.806 mV at 3.3 V VDDA, x1 Gain Setting

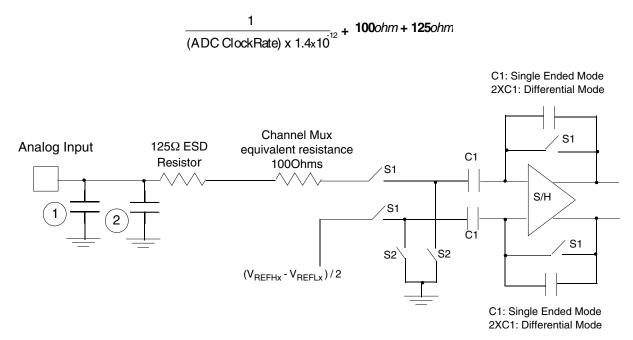

# 3.6.1.1 Equivalent circuit for ADC inputs

The following figure shows the ADC input circuit during sample and hold. S1 and S2 are always opened/closed at non-overlapping phases, and both S1 and S2 operate at the ADC clock frequency. The following equation gives equivalent input impedance when the input is selected.

- 1. Parasitic capacitance due to package, pin-to-pin and pin-to-package base coupling = 1.8pF

- 2. Parasitic capacitance due to the chip bond pad, ESD protection devices and signal routing = 2.04pF

- 3. Sampling capacitor at the sample and hold circuit. Capacitor C1 (4.8pF) is normally disconnected from the input, and is only connected to the input at sampling time.

- 4. S1 and S2 switch phases are non-overlapping and operate at the ADC clock frequency

Figure 13. Equivalent circuit for A/D loading

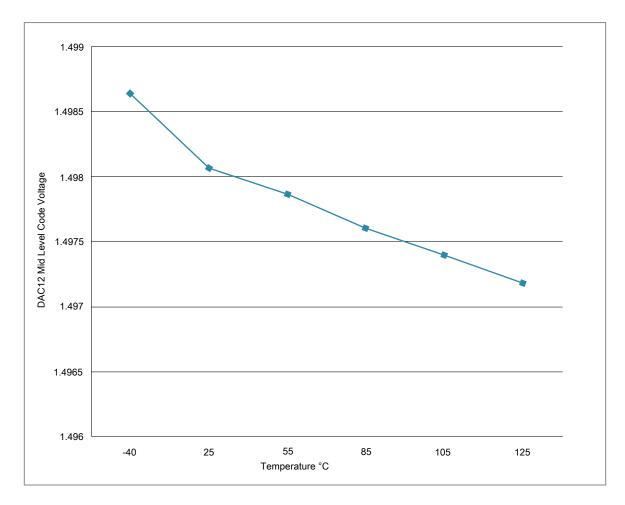

Figure 17. Offset at half scale vs. temperature

# 3.7 Timers

See General switching specifications.

# 3.8 Communication interfaces

#### Peripheral operating requirements and behaviors

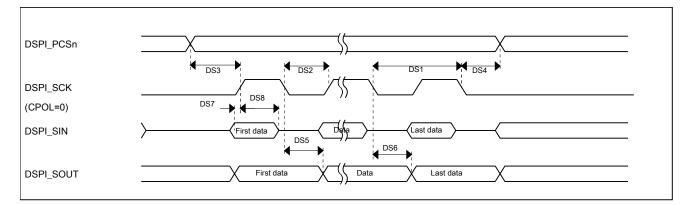

### Figure 18. DSPI classic SPI timing — master mode

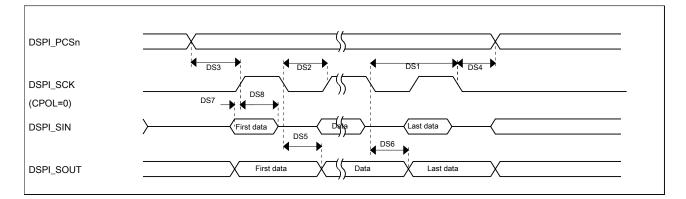

### Table 32. Slave mode DSPI timing for normal pads (limited voltage range)

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |

|      | Frequency of operation                   |                           | 12.5                      | MHz  |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 21                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | _                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | —                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | _                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 15                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | —                         | 15                        | ns   |

### Table 33. Slave mode DSPI timing for fast pads (limited voltage range)

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |

|      | Frequency of operation                   |                           | 25                        | MHz  |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 17                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | _                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | _                         | 11                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 11                        | ns   |

3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | _                             | 18.75                    | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 26                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -7.8                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 24                            | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | _                        | ns   |       |

### Table 37. Master mode DSPI timing open drain pads (full voltage range)

- 1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

- 2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

- 3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

Figure 20. DSPI classic SPI timing — master mode

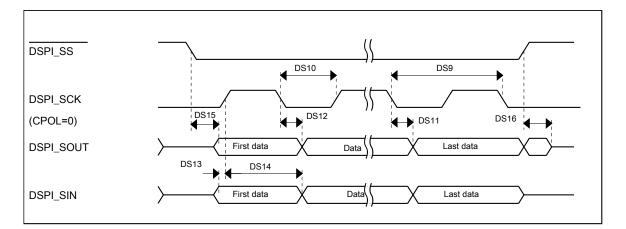

### Table 38. Slave mode DSPI timing for normal pads (full voltage range)

| Num  | Description                   | Min.                      | Max.                     | Unit |

|------|-------------------------------|---------------------------|--------------------------|------|

|      | Operating voltage             | 1.71                      | 3.6                      | V    |

|      | Frequency of operation        | _                         | 12.5                     | MHz  |

| DS9  | DSPI_SCK input cycle time     | 8 x t <sub>BUS</sub>      | —                        | ns   |

| DS10 | DSPI_SCK input high/low time  | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid   | —                         | 27.5                     | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid | 0                         | —                        | ns   |

Table continues on the next page...

Figure 21. DSPI classic SPI timing — slave mode

### 3.8.3 I<sup>2</sup>C

See General switching specifications.

### 3.8.4 UART

See General switching specifications.

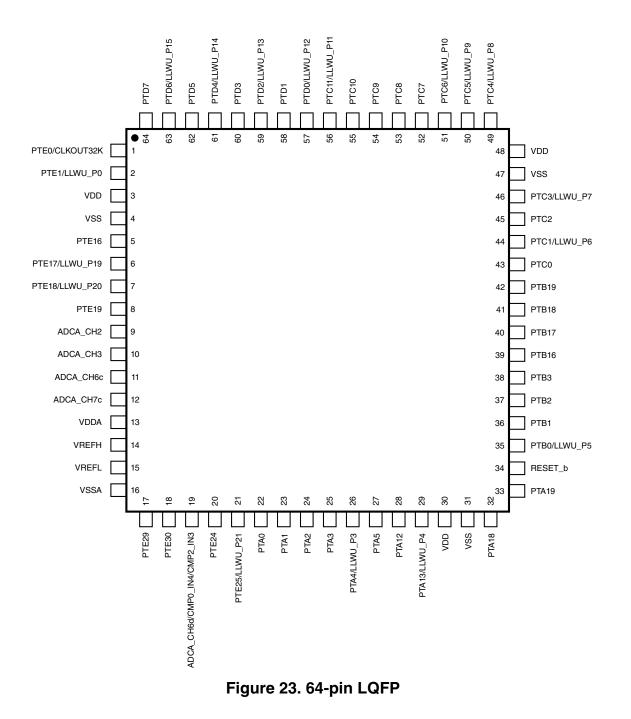

# 4 Dimensions

### 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to www.freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 48-pin LQFP                              | 98ASH00962A                   |

| 64-pin LQFP                              | 98ASS23234W                   |

| 100-pin LQFP                             | 98ASS23308W                   |

# 5 Pinout

# 5.1 KV4x Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

### NOTE

The 48-pin LQFP package for this product is not yet available. However, it is included in a Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

| 100<br>LQFP | 64<br>LQFP | 48<br>LQFP | Pin Name           | Default   | ALT0      | ALT1               | ALT2      | ALT3            | ALT4                | ALT5            | ALT6            | ALT7 |

|-------------|------------|------------|--------------------|-----------|-----------|--------------------|-----------|-----------------|---------------------|-----------------|-----------------|------|

| Ι           | 126        | B5         | PTC19              | DISABLED  |           | PTC19              |           | UART3_CTS_<br>b | ENET0_<br>1588_TMR3 | FLEXPWMB_<br>B3 |                 |      |

| _           | 134        | M10        | VSS                | DISABLED  | VSS       |                    |           |                 |                     |                 |                 |      |

| -           | 135        | F8         | VDD                | DISABLED  | VDD       |                    |           |                 |                     |                 |                 |      |

| _           | 137        | C9         | PTD8/<br>LLWU_P24  | DISABLED  |           | PTD8/<br>LLWU_P24  | I2C1_SCL  | UART5_RX        |                     |                 | FLEXPWMA_<br>A3 |      |

| Ι           | 138        | B9         | PTD9               | DISABLED  |           | PTD9               | I2C1_SDA  | UART5_TX        |                     |                 | FLEXPWMA_<br>B3 |      |

| -           | 139        | B3         | PTD10              | DISABLED  |           | PTD10              |           | UART5_RTS_<br>b |                     |                 | FLEXPWMA_<br>A2 |      |

| _           | 140        | B2         | PTD11/<br>LLWU_P25 | DISABLED  |           | PTD11/<br>LLWU_P25 | SPI2_PCS0 | UART5_CTS_<br>b |                     |                 | FLEXPWMA_<br>B2 |      |

| -           | 141        | B1         | PTD12              | DISABLED  |           | PTD12              | SPI2_SCK  | FTM3_FLT0       | XBAR0_IN5           | XBAR0_<br>OUT5  | FLEXPWMA_<br>A1 |      |

| -           | 142        | C3         | PTD13              | DISABLED  |           | PTD13              | SPI2_SOUT |                 | XBAR0_IN7           | XBAR0_<br>OUT7  | FLEXPWMA_<br>B1 |      |

| -           | 143        | C2         | PTD14              | DISABLED  |           | PTD14              | SPI2_SIN  |                 | XBAR0_IN11          | XBAR0_<br>OUT11 | FLEXPWMA_<br>A0 |      |

| -           | 144        | C1         | PTD15              | DISABLED  |           | PTD15              | SPI2_PCS1 |                 |                     |                 | FLEXPWMA_<br>B0 |      |

| 1           | 1          | —          | PTE0/<br>CLKOUT32K | ADCB_CH6f | ADCB_CH6f | PTE0/<br>CLKOUT32K |           | UART1_TX        | XBAR0_<br>OUT10     | XBAR0_IN11      |                 |      |

| 2           | 2          | -          | PTE1/<br>LLWU_P0   | ADCB_CH7f | ADCB_CH7f | PTE1/<br>LLWU_P0   |           | UART1_RX        | XBAR0_<br>OUT11     | XBAR0_IN7       |                 |      |

| 3           | —          | -          | PTE2/<br>LLWU_P1   | ADCB_CH6g | ADCB_CH6g | PTE2/<br>LLWU_P1   |           | UART1_CTS_<br>b |                     |                 |                 |      |

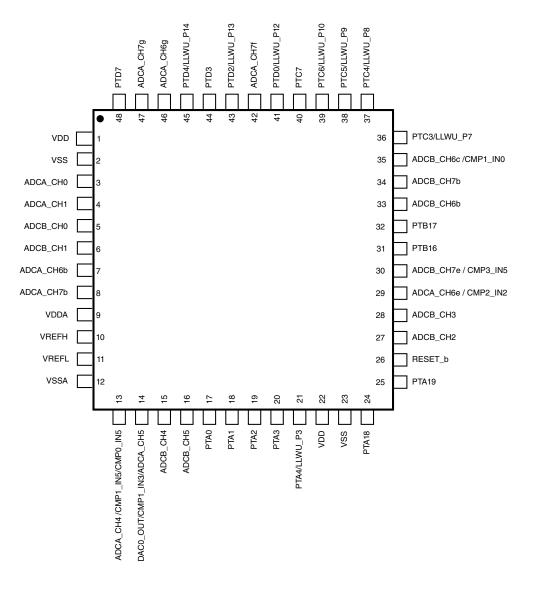

Figure 24. 48-pin LQFP

## 6 Ordering parts

| Field | Description                 | Values                                                                                  |

|-------|-----------------------------|-----------------------------------------------------------------------------------------|

|       |                             | <ul> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>LL = 100 LQFP (14 mm x 14 mm)</li> </ul> |

| CCC   | Maximum CPU frequency (MHz) | • 15 = 150 MHz                                                                          |

| N     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                          |

# 7.4 Example

This is an example part number:

MKV46F256VLL15

# 8 Terminology and guidelines

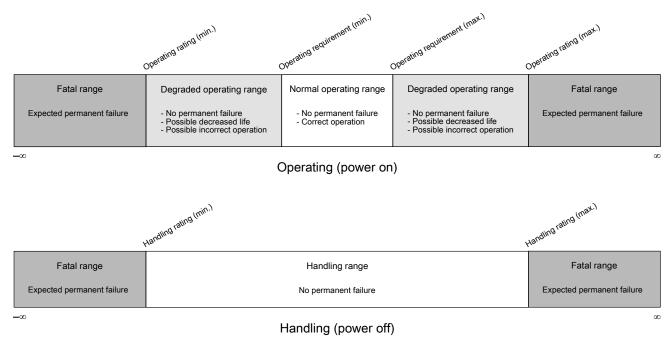

## 8.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 8.1.1 Example

This is an example of an operating requirement:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

# 8.2 Definition: Operating behavior

Unless otherwise specified, an *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

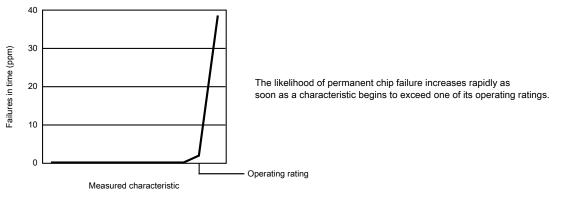

# 8.5 Result of exceeding a rating

# 8.6 Relationship between ratings and operating requirements

# 8.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                              |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>Obtaining package dimensions</li> </ul>                                                                                                                                                                                                                 |

|          |      | Pinout                                                                                                                                                                                                                                                           |

|          |      | <ul> <li>In table "Power consumption operating behaviors", removed the text "Maximum core fequency of 150 Mhz" from note for I<sub>DDA</sub>.</li> <li>In table "Typical device clock specifications", removed information about High Speed run mode.</li> </ul> |

Table 41. Revision history