Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                        |

| Core Processor             | ARM® Cortex®-M3                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 120MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT                            |

| Number of I/O              | 109                                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | 2K x 8                                                                                        |

| RAM Size                   | 40K x 8                                                                                       |

| /oltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                                   |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                                          |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 144-LQFP                                                                                      |

| Supplier Device Package    | 144-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1774fbd144-551                     |

**Table 3. Pin description** ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |            | Reset state[1] | Type <u>[2]</u> | Description                                                                                                                                                                          |

|--------|-------------|---------------|---------------|-------------|------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[5]  | 166         | C12           | B11           | 115         | [3]        | l;             | I/O             | P0[5] — General purpose digital input/output pin.                                                                                                                                    |

|        |             |               |               |             |            | PU             | I/O             | <b>I2S_RX_WS</b> — $I^2$ S Receive word select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $\ell$ S-bus specification.                |

|        |             |               |               |             |            |                | 0               | CAN_TD2 — CAN2 transmitter output.                                                                                                                                                   |

|        |             |               |               |             |            |                | I               | T2_CAP1 — Capture input for Timer 2, channel 1.                                                                                                                                      |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | 0               | LCD_VD[1] — LCD data.                                                                                                                                                                |

| P0[6]  | 164         | D13           | D11           | 113         | [3]        | l;             | I/O             | P0[6] — General purpose digital input/output pin.                                                                                                                                    |

|        |             |               |               |             |            | PU             | I/O             | <b>I2S_RX_SDA</b> — I <sup>2</sup> S Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the I <sup>2</sup> S-bus specification. |

|        |             |               |               |             |            |                | I/O             | SSP1_SSEL — Slave Select for SSP1.                                                                                                                                                   |

|        |             |               |               |             |            |                | 0               | T2_MAT0 — Match output for Timer 2, channel 0.                                                                                                                                       |

|        |             |               |               |             |            |                | 0               | <b>U1_RTS</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1.                                                     |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | 0               | LCD_VD[8] — LCD data.                                                                                                                                                                |

| P0[7]  | 162         | C13           | B12           | 112         | <u>[4]</u> | I; IA          | I/O             | P0[7] — General purpose digital input/output pin.                                                                                                                                    |

|        |             |               |               |             |            |                | I/O             | <b>I2S_TX_SCK</b> — I <sup>2</sup> S transmit clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the I <sup>2</sup> S-bus specification.  |

|        |             |               |               |             |            |                | I/O             | SSP1_SCK — Serial Clock for SSP1.                                                                                                                                                    |

|        |             |               |               |             |            |                | 0               | T2_MAT1 — Match output for Timer 2, channel 1.                                                                                                                                       |

|        |             |               |               |             |            |                | I               | RTC_EV0 — Event input 0 to Event Monitor/Recorder.                                                                                                                                   |

|        |             |               |               |             |            |                | -               | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                |                 | R — Function reserved.                                                                                                                                                               |

|        |             |               |               |             |            |                | 0               | LCD_VD[9] — LCD data.                                                                                                                                                                |

**Table 3. Pin description** ...continued Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |     | Reset state[1] | Type[2] | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------------|---------------|---------------|-------------|-----|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1[16] | 180         | D10           | B8            | 125         | [3] | I;<br>PU       | I/O     | P1[16] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                         |

|        |             |               |               |             |     | PU             | 0       | ENET_MDC — Ethernet MIIM clock.                                                                                                                                                                                                                                                                                                                                                                            |

|        |             |               |               |             |     |                | 0       | I2S_TX_MCLK — I2S transmit master clock.                                                                                                                                                                                                                                                                                                                                                                   |

| P1[17] | 178         | A9            | C9            | 123         | [3] | I;<br>PU       | I/O     | P1[17] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                         |

|        |             |               |               |             |     | PU             | I/O     | ENET_MDIO — Ethernet MIIM data input and output.                                                                                                                                                                                                                                                                                                                                                           |

|        |             |               |               |             |     |                | 0       | I2S_RX_MCLK — I2S receive master clock.                                                                                                                                                                                                                                                                                                                                                                    |

| P1[18] | 66          | P7            | L5            | 46          | [3] | l;             | I/O     | P1[18] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                         |

|        |             |               |               |             |     | PU             | О       | USB_UP_LED1 — It is LOW when the device is configured (non-control endpoints enabled), or when the host is enabled and has detected a device on the bus. It is HIGH when the device is not configured, or when host is enabled and has not detected a device on the bus, or during global suspend. It transitions between LOW and HIGH (flashes) when the host is enabled and detects activity on the bus. |

|        |             |               |               |             |     |                | 0       | PWM1[1] — Pulse Width Modulator 1, channel 1 output.                                                                                                                                                                                                                                                                                                                                                       |

|        |             |               |               |             |     |                | I       | T1_CAP0 — Capture input for Timer 1, channel 0.                                                                                                                                                                                                                                                                                                                                                            |

|        |             |               |               |             |     |                | -       | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                     |

|        |             |               |               |             |     |                | I/O     | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                                                                                                                                                                                                                                                  |

| P1[19] | 68          | U6            | P5            | 47          | [3] | I;             | I/O     | P1[19] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                         |

|        |             |               |               |             |     | PU             | 0       | USB_TX_E1 — Transmit Enable signal for USB port 1 (OTG transceiver).                                                                                                                                                                                                                                                                                                                                       |

|        |             |               |               |             |     |                | 0       | USB_PPWR1 — Port Power enable signal for USB port 1.                                                                                                                                                                                                                                                                                                                                                       |

|        |             |               |               |             |     |                | I       | T1_CAP1 — Capture input for Timer 1, channel 1.                                                                                                                                                                                                                                                                                                                                                            |

|        |             |               |               |             |     |                | 0       | MC_0A — Motor control PWM channel 0, output A.                                                                                                                                                                                                                                                                                                                                                             |

|        |             |               |               |             |     |                | I/O     | SSP1_SCK — Serial clock for SSP1.                                                                                                                                                                                                                                                                                                                                                                          |

|        |             |               |               |             |     |                | 0       | U2_OE — RS-485/EIA-485 output enable signal for UART2.                                                                                                                                                                                                                                                                                                                                                     |

| P1[20] | 70          | U7            | K6            | 49          | [3] | I;             | I/O     | P1[20] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                         |

|        |             |               |               |             |     | PU             | 0       | USB_TX_DP1 — D+ transmit data for USB port 1 (OTG transceiver).                                                                                                                                                                                                                                                                                                                                            |

|        |             |               |               |             |     |                | 0       | PWM1[2] — Pulse Width Modulator 1, channel 2 output.                                                                                                                                                                                                                                                                                                                                                       |

|        |             |               |               |             |     |                | I       | QEI_PHA — Quadrature Encoder Interface PHA input.                                                                                                                                                                                                                                                                                                                                                          |

|        |             |               |               |             |     |                | I       | MC_FB0 — Motor control PWM channel 0 feedback input.                                                                                                                                                                                                                                                                                                                                                       |

|        |             |               |               |             |     |                | I/O     | SSP0_SCK — Serial clock for SSP0.                                                                                                                                                                                                                                                                                                                                                                          |

|        |             |               |               |             |     |                | 0       | LCD_VD[6] — LCD data.                                                                                                                                                                                                                                                                                                                                                                                      |

|        |             |               |               |             |     |                | 0       | LCD_VD[10] — LCD data.                                                                                                                                                                                                                                                                                                                                                                                     |

**Table 3. Pin description** ...continued Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |                                 | Reset state[1] | Type[2] | Description                                                                                                                          |

|--------|-------------|---------------|---------------|-------------|---------------------------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| P2[5]  | 140         | F16           | F12           | 97          | [3]                             | I;             | I/O     | P2[5] — General purpose digital input/output pin.                                                                                    |

|        |             |               |               |             |                                 | PU             | 0       | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                                                                                 |

|        |             |               |               |             |                                 |                | 0       | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

|        |             |               |               |             |                                 |                | 0       | T2_MAT0 — Match output for Timer 2, channel 0.                                                                                       |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | 0       | TRACEDATA[0] — Trace data, bit 0.                                                                                                    |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | 0       | <b>LCD_LP</b> — Line synchronization pulse (STN). Horizontal synchronization pulse (TFT).                                            |

| P2[6]  | 138         | E17           | F13           | 96          | [3]                             | l;             | I/O     | P2[6] — General purpose digital input/output pin.                                                                                    |

|        |             |               |               |             |                                 | PU             | I       | <b>PWM1_CAP0</b> — Capture input for PWM1, channel 0.                                                                                |

|        |             |               |               |             |                                 |                | I       | U1_RI — Ring Indicator input for UART1.                                                                                              |

|        |             |               |               |             |                                 |                | I       | T2_CAP0 — Capture input for Timer 2, channel 0.                                                                                      |

|        |             |               |               |             |                                 |                | 0       | U2_OE — RS-485/EIA-485 output enable signal for UART2.                                                                               |

|        |             |               |               |             |                                 |                | 0       | TRACECLK — Trace clock.                                                                                                              |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[0] — LCD data.                                                                                                                |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[4] — LCD data.                                                                                                                |

| P2[7]  | 136         | G16           | G11           | 95          | [3]                             | l;             | I/O     | P2[7] — General purpose digital input/output pin.                                                                                    |

|        |             |               |               |             |                                 | PU             | I       | CAN_RD2 — CAN2 receiver input.                                                                                                       |

|        |             |               |               |             |                                 |                | Ο       | <b>U1_RTS</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1.     |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[1] — LCD data.                                                                                                                |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[5] — LCD data.                                                                                                                |

| P2[8]  | 134         | H15           | G14           | 93          | [3]                             | l;             | I/O     | P2[8] — General purpose digital input/output pin.                                                                                    |

|        |             |               |               |             |                                 | PU             | 0       | CAN_TD2 — CAN2 transmitter output.                                                                                                   |

|        |             |               |               |             |                                 |                | 0       | U2_TXD — Transmitter output for UART2.                                                                                               |

|        |             |               |               |             |                                 |                | I       | U1_CTS — Clear to Send input for UART1.                                                                                              |

|        |             |               |               | 0           | ENET_MDC — Ethernet MIIM clock. |                |         |                                                                                                                                      |

|        |             |               |               |             |                                 |                | -       | R — Function reserved.                                                                                                               |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[2] — LCD data.                                                                                                                |

|        |             |               |               |             |                                 |                | 0       | LCD_VD[6] — LCD data.                                                                                                                |

**Table 3. Pin description** ...continued Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |     | Reset state[1] | Type <u>[2]</u> | Description                                                                                                                          |

|--------|-------------|---------------|---------------|-------------|-----|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P3[17] | 143         | F15           | -             | -           | [3] | l;             | I/O             | P3[17] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[17] — External memory data line 17.                                                                                            |

|        |             |               |               |             |     |                | 0               | PWM0[2] — Pulse Width Modulator 0, output 2.                                                                                         |

|        |             |               |               |             |     |                | I               | U1_RXD — Receiver input for UART1.                                                                                                   |

| P3[18] | 151         | C15           | -             | -           | [3] | l;             | I/O             | P3[18] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[18] — External memory data line 18.                                                                                            |

|        |             |               |               |             |     |                | 0               | PWM0[3] — Pulse Width Modulator 0, output 3.                                                                                         |

|        |             |               |               |             |     |                | I               | U1_CTS — Clear to Send input for UART1.                                                                                              |

| P3[19] | 161         | B14           | -             | -           | [3] | l;             | I/O             | P3[19] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[19] — External memory data line 19.                                                                                            |

|        |             |               |               |             |     |                | О               | PWM0[4] — Pulse Width Modulator 0, output 4.                                                                                         |

|        |             |               |               |             |     |                | I               | U1_DCD — Data Carrier Detect input for UART1.                                                                                        |

| P3[20] | 167         | A13           | -             | -           | [3] | l;             | I/O             | P3[20] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[20] — External memory data line 20.                                                                                            |

|        |             |               |               |             |     |                | Ο               | PWM0[5] — Pulse Width Modulator 0, output 5.                                                                                         |

|        |             |               |               |             |     |                | I               | U1_DSR — Data Set Ready input for UART1.                                                                                             |

| P3[21] | 175         | C10           | -             | -           | [3] | l;             | I/O             | P3[21] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[21] — External memory data line 21.                                                                                            |

|        |             |               |               |             |     |                | Ο               | PWM0[6] — Pulse Width Modulator 0, output 6.                                                                                         |

|        |             |               |               |             |     |                | 0               | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

| P3[22] | 195         | C6            | -             | -           | [3] | l;             | I/O             | P3[22] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[22] — External memory data line 22.                                                                                            |

|        |             |               |               |             |     |                | I               | PWM0_CAP0 — Capture input for PWM0, channel 0.                                                                                       |

|        |             |               |               |             |     |                | I               | U1_RI — Ring Indicator input for UART1.                                                                                              |

| P3[23] | 65          | T6            | M4            | 45          | [3] | I;             | I/O             | P3[23] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[23] — External memory data line 23.                                                                                            |

|        |             |               |               |             |     |                | I               | PWM1_CAP0 — Capture input for PWM1, channel 0.                                                                                       |

|        |             |               |               |             |     |                | I               | T0_CAP0 — Capture input for Timer 0, channel 0.                                                                                      |

| P3[24] | 58          | R5            | N3            | 40          | [3] | I;             | I/O             | P3[24] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |     | PU             | I/O             | EMC_D[24] — External memory data line 24.                                                                                            |

|        |             |               |               |             |     |                | 0               | PWM1[1] — Pulse Width Modulator 1, output 1.                                                                                         |

|        |             |               |               |             |     |                | I               | T0_CAP1 — Capture input for Timer 0, channel 1.                                                                                      |

**Table 3. Pin description** ...continued Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol             | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |     | Reset state[1] | Type <u>[2]</u> | Description                                                                                                                                                                                |

|--------------------|-------------|---------------|---------------|-------------|-----|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3[25]             | 56          | U2            | МЗ            | 39          | [3] | I;             | I/O             | P3[25] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[25] — External memory data line 25.                                                                                                                                                  |

|                    |             |               |               |             |     |                | 0               | PWM1[2] — Pulse Width Modulator 1, output 2.                                                                                                                                               |

|                    |             |               |               |             |     |                | О               | T0_MAT0 — Match output for Timer 0, channel 0.                                                                                                                                             |

| P3[26]             | 55          | Т3            | K7            | 38          | [3] | l;             | I/O             | P3[26] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[26] — External memory data line 26.                                                                                                                                                  |

|                    |             |               |               |             |     |                | О               | PWM1[3] — Pulse Width Modulator 1, output 3.                                                                                                                                               |

|                    |             |               |               |             |     |                | О               | T0_MAT1 — Match output for Timer 0, channel 1.                                                                                                                                             |

|                    |             |               |               |             |     |                | I               | <b>STCLK</b> — System tick timer clock input. The maximum STCLK frequency is 1/4 of the ARM processor clock frequency CCLK.                                                                |

| P3[27]             | 203         | A1            | -             | -           | [3] | l;             | I/O             | P3[27] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[27] — External memory data line 27.                                                                                                                                                  |

|                    |             |               |               |             |     |                | 0               | PWM1[4] — Pulse Width Modulator 1, output 4.                                                                                                                                               |

|                    |             |               |               |             |     |                | I               | T1_CAP0 — Capture input for Timer 1, channel 0.                                                                                                                                            |

| P3[28]             | 5           | D2            | -             | -           | [3] | l;             | I/O             | P3[28] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[28] — External memory data line 28.                                                                                                                                                  |

|                    |             |               |               |             |     |                | 0               | PWM1[5] — Pulse Width Modulator 1, output 5.                                                                                                                                               |

|                    |             |               |               |             |     |                | I               | T1_CAP1 — Capture input for Timer 1, channel 1.                                                                                                                                            |

| P3[29]             | 11          | F3            | -             | -           | [3] | l;             | I/O             | P3[29] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[29] — External memory data line 29.                                                                                                                                                  |

|                    |             |               |               |             |     |                | 0               | PWM1[6] — Pulse Width Modulator 1, output 6.                                                                                                                                               |

|                    |             |               |               |             |     |                | 0               | T1_MAT0 — Match output for Timer 1, channel 0.                                                                                                                                             |

| P3[30]             | 19          | НЗ            | -             | -           | [3] | l;             | I/O             | P3[30] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[30] — External memory data line 30.                                                                                                                                                  |

|                    |             |               |               |             |     |                | 0               | <b>U1_RTS</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1.                                                           |

|                    |             |               |               |             |     |                | 0               | T1_MAT1 — Match output for Timer 1, channel 1.                                                                                                                                             |

| P3[31]             | 25          | J3            | -             | -           | [3] | I;             | I/O             | P3[31] — General purpose digital input/output pin.                                                                                                                                         |

|                    |             |               |               |             |     | PU             | I/O             | EMC_D[31] — External memory data line 31.                                                                                                                                                  |

|                    |             |               |               |             |     |                | -               | R — Function reserved.                                                                                                                                                                     |

|                    |             |               |               |             |     |                | 0               | T1_MAT2 — Match output for Timer 1, channel 2.                                                                                                                                             |

| P4[0] to<br>P4[31] |             |               |               |             |     |                | I/O             | <b>Port 4:</b> Port 4 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 4 pins depends upon the pin function selected via the pin connect block. |

| P4[0]              | 75          | U9            | L6            | 52          | [3] | I;             | I/O             | P4[0] — General purpose digital input/output pin.                                                                                                                                          |

|                    |             |               |               |             |     | PU             | I/O             | EMC_A[0] — External memory address line 0.                                                                                                                                                 |

**Table 3. Pin description** ...continued Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol               | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |              | Reset state[1] | Type[ <u>2]</u> | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------|---------------|---------------|-------------|--------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5[3]                | 141         | G14           | G10           | 98          | [11]         | ı              | I/O             | P5[3] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                        |

|                      |             |               |               |             |              |                | -               | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                   |

|                      |             |               |               |             |              |                | -               | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                   |

|                      |             |               |               |             |              |                | -               | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                   |

|                      |             |               |               |             |              |                | I               | U4_RXD — Receiver input for USART4.                                                                                                                                                                                                                                                                                                                                      |

|                      |             |               |               |             |              |                | I/O             | <b>I2C0_SCL</b> — I <sup>2</sup> C0 clock input/output (this pin uses a specialized I <sup>2</sup> C pad that supports I <sup>2</sup> C Fast Mode Plus).                                                                                                                                                                                                                 |

| P5[4]                | 206         | C3            | C4            | 143         | [3]          | I;             | I/O             | P5[4] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                        |

|                      |             |               |               |             |              | PU             | 0               | U0_OE — RS-485/EIA-485 output enable signal for UART0.                                                                                                                                                                                                                                                                                                                   |

|                      |             |               |               |             |              |                | -               | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                   |

|                      |             |               |               |             |              |                | 0               | T3_MAT3 — Match output for Timer 3, channel 3.                                                                                                                                                                                                                                                                                                                           |

|                      |             |               |               |             |              |                | 0               | <b>U4_TXD</b> — Transmitter output for USART4 (input/output in smart card mode).                                                                                                                                                                                                                                                                                         |

| JTAG_TDO<br>(SWO)    | 2           | D3            | B1            | 1           | [3]          | 0              | 0               | Test Data Out for JTAG interface. Also used as Serial wire trace output.                                                                                                                                                                                                                                                                                                 |

| JTAG_TDI             | 4           | C2            | C3            | 3           | [3]          | I;<br>PU       | I               | Test Data In for JTAG interface.                                                                                                                                                                                                                                                                                                                                         |

| JTAG_TMS<br>(SWDIO)  | 6           | E3            | C2            | 4           | [3]          | I;<br>PU       | I               | Test Mode Select for JTAG interface. Also used as Serial wire debug data input/output.                                                                                                                                                                                                                                                                                   |

| JTAG_TRST            | 8           | D1            | D4            | 5           | [3]          | I;<br>PU       | I               | Test Reset for JTAG interface.                                                                                                                                                                                                                                                                                                                                           |

| JTAG_TCK<br>(SWDCLK) | 10          | E2            | D2            | 7           | [3]          | i              | I               | Test Clock for JTAG interface. This clock must be slower than 1/6 of the CPU clock (CCLK) for the JTAG interface to operate. Also used as serial wire clock.                                                                                                                                                                                                             |

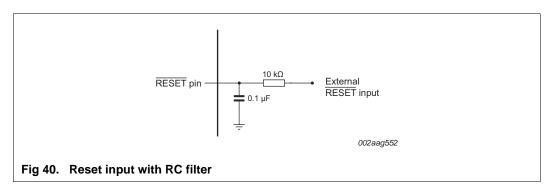

| RESET                | 35          | M2            | J1            | 24          | [12]         | I;<br>PU       | I               | External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin also serves as the debug select input. LOW level selects the JTAG boundary scan. HIGH level selects the ARM SWD debug mode. |

| RSTOUT               | 29          | K3            | H2            | 20          | [3]          | ОН             | 0               | Reset status output. A LOW output on this pin indicates that the device is in the reset state for any reason. This reflects the RESET input pin and all internal reset sources.                                                                                                                                                                                          |

| RTC_ALARM            | 37          | N1            | H5            | 26          | [13]         | OL             | 0               | RTC controlled output. This pin has a low drive strength and is powered by VBAT. It is driven HIGH when an RTC alarm is generated.                                                                                                                                                                                                                                       |

| RTCX1                | 34          | K2            | J2            | 23          | [14]<br>[15] | -              | I               | Input to the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                                                                                                                                                                              |

| RTCX2                | 36          | L2            | J3            | 25          | [14]<br>[15] | -              | 0               | Output from the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                                                                                                                                                                           |

| USB_D-2              | 52          | U1            | N2            | 37          | [9]          | -              | I/O             | USB port 2 bidirectional D– line.                                                                                                                                                                                                                                                                                                                                        |

Table 7. External memory controller pin configuration

| Part          | Data bus pins |             | Control pins                                     |                                                                                 |  |  |  |  |

|---------------|---------------|-------------|--------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

|               |               | pins        | SRAM                                             | SDRAM                                                                           |  |  |  |  |

| LPC1788FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1788FET208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0],<br>EMC_CLK[1:0], EMC_CKE[3:0],<br>EMC_DQM[3:0] |  |  |  |  |

| LPC1788FET180 | EMC_D[15:0]   | EMC_A[19:0] | EMC_BLS[1:0],<br>EMC_CS[1:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[1:0],<br>EMC_CLK[1:0], EMC_CKE[1:0],<br>EMC_DQM[1:0] |  |  |  |  |

| LPC1788FBD144 | EMC_D[7:0]    | EMC_A[15:0] | EMC_BLS[3:2],<br>EMC_CS[1:0],<br>EMC_OE, EMC_WE  | not available                                                                   |  |  |  |  |

| LPC1787FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS_[3:0],<br>EMC_OE, EMC_WE | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1786FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1785FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1778FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1778FET208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1778FET180 | EMC_D[15:0]   | EMC_A[19:0] | EMC_BLS[1:0],<br>EMC_CS[1:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[1:0],<br>EMC_CLK[1:0], EMC_CKE[1:0],<br>EMC_DQM[1:0] |  |  |  |  |

| LPC1778FBD144 | EMC_D[7:0]    | EMC_A[15:0] | EMC_CS[1:0],<br>EMC_OE, EMC_WE                   | not available                                                                   |  |  |  |  |

| LPC1777FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0],<br>EMC_CLK[1:0], EMC_CKE[3:0],<br>EMC_DQM[3:0] |  |  |  |  |

| LPC1776FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1776FET180 | EMC_D[15:0]   | EMC_A[19:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[1:0], EMC_CLK[1:0], EMC_CKE[1:0], EMC_DQM[1:0]       |  |  |  |  |

| LPC1774FBD208 | EMC_D[31:0]   | EMC_A[25:0] | EMC_BLS[3:0],<br>EMC_CS[3:0],<br>EMC_OE, EMC_WE  | EMC_RAS, EMC_CAS, EMC_DYCS[3:0], EMC_CLK[1:0], EMC_CKE[3:0], EMC_DQM[3:0]       |  |  |  |  |

| LPC1774FBD144 | EMC_D[7:0]    | EMC_A[15:0] | EMC_CS[1:0],<br>EMC_OE, EMC_WE                   | not available                                                                   |  |  |  |  |

### 32-bit ARM Cortex-M3 microcontroller

- Physical interface:

- Attachment of external PHY chip through standard MII or RMII interface.

- PHY register access is available via the MIIM interface.

### 7.15 USB interface

**Remark:** The USB Device/Host/OTG controller is available on parts LPC1788/87/86/85 and LPC1778/77/76. The USB Device-only controller is available on parts LPC1774.

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

Details on typical USB interfacing solutions can be found in Section 14.1.

#### 7.15.1 USB device controller

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of a register interface, serial interface engine, endpoint buffer memory, and a DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. When enabled, the DMA controller transfers data between the endpoint buffer and the USB RAM.

### 7.15.1.1 Features

- Fully compliant with USB 2.0 Specification (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- Supports SoftConnect and GoodLink features.

- While USB is in the Suspend mode, the LPC178x/7x can enter one of the reduced power modes and wake up on USB activity.

- Supports DMA transfers with all on-chip SRAM blocks on all non-control endpoints.

- Allows dynamic switching between CPU-controlled and DMA modes.

- Double buffer implementation for Bulk and Isochronous endpoints.

#### 7.15.2 USB host controller

The host controller enables full- and low-speed data exchange with USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies with the Open Host Controller Interface (OHCI) specification.

### 7.15.2.1 Features

OHCI compliant.

LPC178X\_7X

### 32-bit ARM Cortex-M3 microcontroller

### 7.19.1 Features

- 10-bit DAC.

- Resistor string architecture.

- Buffered output.

- Power-down mode.

- Selectable output drive.

- Dedicated conversion timer.

- DMA support.

### **7.20 UARTs**

Remark: USART4 is not available on part LPC1774FBD144.

The LPC178x/7x contain five UARTs. In addition to standard transmit and receive data lines, UART1 also provides a full modem control handshake interface and support for RS-485/9-bit mode allowing both software address detection and automatic address detection using 9-bit mode.

The UARTs include a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 7.20.1 Features

- Maximum UART data bit rate of 7.5 MBit/s.

- 16 B Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Auto-baud capability.

- Fractional divider for baud rate control, auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- Support for RS-485/9-bit/EIA-485 mode and multiprocessor addressing.

- All UARTs have DMA support for both transmit and receive.

- UART1 equipped with standard modem interface signals. This module also provides full support for hardware flow control (auto-CTS/RTS).

- USART4 includes an IrDA mode to support infrared communication.

- USART4 supports synchronous mode and a smart card mode conforming to ISO7816-3.

### 7.21 SSP serial I/O controller

The LPC178x/7x contain three SSP controllers. The SSP controller is capable of operation on a SPI, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus

### 32-bit ARM Cortex-M3 microcontroller

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

# 7.25 General purpose 32-bit timers/external event counters

The LPC178x/7x include four 32-bit timer/counters.

The timer/counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts, generate timed DMA requests, or perform other actions at specified timer values, based on four match registers. Each timer/counter also includes two capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

### **7.25.1** Features

- A 32-bit timer/counter with a programmable 32-bit prescaler.

- Counter or timer operation.

- Two 32-bit capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event may also generate an interrupt.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

# 7.26 Pulse Width Modulator (PWM)

The LPC178x/7x contain two standard PWMs.

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC178x/7x. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

### 32-bit ARM Cortex-M3 microcontroller

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- Periodic interrupts can be generated from increments of any field of the time registers.

- Backup registers (20 bytes) powered by VBAT.

- RTC power supply is isolated from the rest of the chip.

# 7.32 Event monitor/recorder

The event monitor/recorder allows recording of tampering events in sealed product enclosures. Sensors report any attempt to open the enclosure, or to tamper with the device in any other way. The event monitor/recorder stores records of such events when the device is powered only by the backup battery.

### 7.32.1 Features

- Supports three digital event inputs in the VBAT power domain.