Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                                      |

| Speed                      | 120MHz                                                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 141                                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                                   |

| EEPROM Size                | 4K x 8                                                                                                  |

| RAM Size                   | 80K x 8                                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                                             |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                                                    |

| Oscillator Type            | Internal                                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                       |

| Mounting Type              | Surface Mount                                                                                           |

| Package / Case             | 180-TFBGA                                                                                               |

| Supplier Device Package    | 180-TFBGA (12x12)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1776fet180-551                               |

|                            |                                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. Ordering information

# Table 1.Ordering information

| Type number   | Package  | Package                                                                                     |          |  |  |  |  |  |  |  |

|---------------|----------|---------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

|               | Name     | Description                                                                                 | Version  |  |  |  |  |  |  |  |

| LPC1788       |          |                                                                                             | <b>I</b> |  |  |  |  |  |  |  |

| LPC1788FBD208 | LQFP208  | LQFP208 plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm |          |  |  |  |  |  |  |  |

| LPC1788FET208 | TFBGA208 | plastic thin fine-pitch ball grid array package; 208 balls; body 15 ´ 15 ´ 0.7 mm           | SOT950-1 |  |  |  |  |  |  |  |

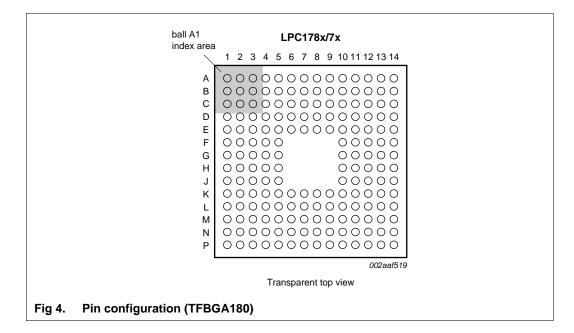

| LPC1788FET180 | TFBGA180 | thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm                   | SOT570-3 |  |  |  |  |  |  |  |

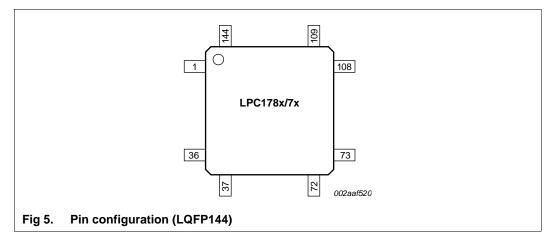

| LPC1788FBD144 | LQFP144  | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |  |  |  |  |  |  |  |

| LPC1787       |          |                                                                                             | I        |  |  |  |  |  |  |  |

| LPC1787FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1786       |          |                                                                                             |          |  |  |  |  |  |  |  |

| LPC1786FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1785       |          |                                                                                             |          |  |  |  |  |  |  |  |

| LPC1785FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1778       |          |                                                                                             |          |  |  |  |  |  |  |  |

| LPC1778FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body 28 $\times$ 28 $\times$ 1.4 mm       | SOT459-1 |  |  |  |  |  |  |  |

| LPC1778FET208 | TFBGA208 | plastic thin fine-pitch ball grid array package; 208 balls; body 15 ´ 15 ´ 0.7 mm           | SOT950-1 |  |  |  |  |  |  |  |

| LPC1778FET180 | TFBGA180 | thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm                   | SOT570-3 |  |  |  |  |  |  |  |

| LPC1778FBD144 | LQFP144  | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |  |  |  |  |  |  |  |

| LPC1777       |          |                                                                                             | I        |  |  |  |  |  |  |  |

| LPC1777FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1776       |          |                                                                                             | I        |  |  |  |  |  |  |  |

| LPC1776FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1776FET180 | TFBGA180 | thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm                   | SOT570-3 |  |  |  |  |  |  |  |

| LPC1774       |          |                                                                                             |          |  |  |  |  |  |  |  |

| LPC1774FBD208 | LQFP208  | plastic low profile quad flat package; 208 leads; body $28 \times 28 \times 1.4$ mm         | SOT459-1 |  |  |  |  |  |  |  |

| LPC1774FBD144 | LQFP144  | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm         | SOT486-1 |  |  |  |  |  |  |  |

#### 32-bit ARM Cortex-M3 microcontroller

# 6.2 Pin description

I/O pins on the LPC178x/7x are 5 V tolerant and have input hysteresis unless otherwise indicated in the table below. Crystal pins, power pins, and reference voltage pins are not 5 V tolerant. In addition, when pins are selected to be ADC inputs, they are no longer 5 V tolerant and the input voltage must be limited to the voltage at the ADC positive reference pin (VREFP).

All port pins Pn[m] are multiplexed, and the multiplexed functions appear in <u>Table 3</u> in the order defined by the FUNC bits of the corresponding IOCON register up to the highest used function number. Each port pin can support up to eight multiplexed functions. IOCON register FUNC values which are reserved are noted as 'R' in the pin configuration table.

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |            | Reset state[1] | Type <sup>[2]</sup> | Description                                                                                                                                                                                  |

|--------|-------------|---------------|---------------|-------------|------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[8]  | 160         | A15           | C12           | 111         | <u>[4]</u> | I; IA          | I/O                 | P0[8] — General purpose digital input/output pin.                                                                                                                                            |

|        |             |               |               |             |            |                | I/O                 | <b>I2S_TX_WS</b> — I <sup>2</sup> S Transmit word select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.               |

|        |             |               |               |             |            |                | I/O                 | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                                    |

|        |             |               |               |             |            |                | 0                   | T2_MAT2 — Match output for Timer 2, channel 2.                                                                                                                                               |

|        |             |               |               |             |            |                | I                   | RTC_EV1 — Event input 1 to Event Monitor/Recorder.                                                                                                                                           |

|        |             |               |               |             |            |                | -                   | R — Function reserved.                                                                                                                                                                       |

|        |             |               |               |             |            |                | -                   | R — Function reserved.                                                                                                                                                                       |

|        |             |               |               |             |            |                | 0                   | LCD_VD[16] — LCD data.                                                                                                                                                                       |

| P0[9]  | 158         | C14           | A13           | 109         | [4]        | I; IA          | I/O                 | P0[9] — General purpose digital input/output pin.                                                                                                                                            |

|        |             |               |               |             |            |                | I/O                 | <b>I2S_TX_SDA</b> — I <sup>2</sup> S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |             |               |               |             |            |                | I/O                 | SSP1_MOSI — Master Out Slave In for SSP1.                                                                                                                                                    |

|        |             |               |               |             |            |                | 0                   | T2_MAT3 — Match output for Timer 2, channel 3.                                                                                                                                               |

|        |             |               |               |             |            |                | I                   | RTC_EV2 — Event input 2 to Event Monitor/Recorder.                                                                                                                                           |

|        |             |               |               |             |            |                | -                   | R — Function reserved.                                                                                                                                                                       |

|        |             |               |               |             |            |                | -                   | R — Function reserved.                                                                                                                                                                       |

|        |             |               |               |             |            |                | 0                   | LCD_VD[17] — LCD data.                                                                                                                                                                       |

| P0[10] | 98          | T15           | L10           | 69          | [3]        | I;             | I/O                 | P0[10] — General purpose digital input/output pin.                                                                                                                                           |

|        |             |               |               |             |            | PU             | 0                   | U2_TXD — Transmitter output for UART2.                                                                                                                                                       |

|        |             |               |               |             |            |                | I/O                 | <b>I2C2_SDA</b> — I <sup>2</sup> C2 data input/output (this pin does not use a specialized I2C pad).                                                                                         |

|        |             |               |               |             |            |                | 0                   | T3_MAT0 — Match output for Timer 3, channel 0.                                                                                                                                               |

| P0[11] | 100         | R14           | P12           | 70          | [3]        | l;             | I/O                 | <b>P0[11]</b> — General purpose digital input/output pin.                                                                                                                                    |

|        |             |               |               |             |            | PU             | 1                   | U2_RXD — Receiver input for UART2.                                                                                                                                                           |

|        |             |               |               |             |            |                | I/O                 | <b>I2C2_SCL</b> — I <sup>2</sup> C2 clock input/output (this pin does not use a specialized I2C pad).                                                                                        |

|        |             |               |               |             |            |                | 0                   | T3_MAT1 — Match output for Timer 3, channel 1.                                                                                                                                               |

| P0[12] | 41          | R1            | J4            | 29          | [5]        | l;             | I/O                 | P0[12] — General purpose digital input/output pin.                                                                                                                                           |

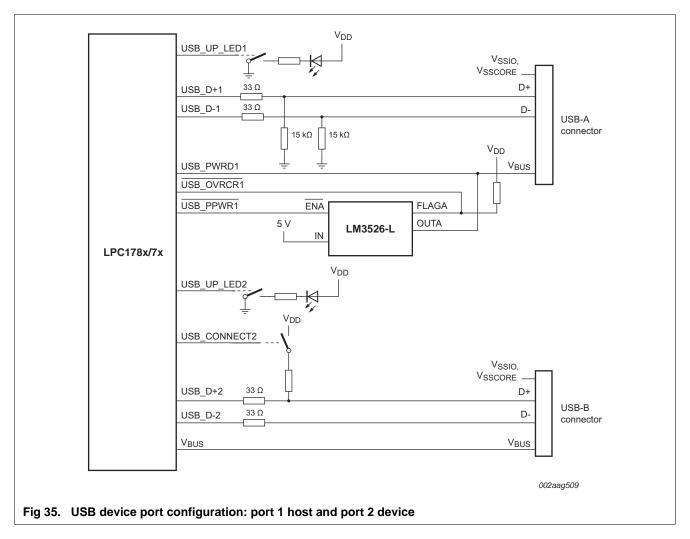

|        |             |               |               |             |            | PU             | 0                   | <b>USB_PPWR2</b> — Port Power enable signal for USB port 2.                                                                                                                                  |

|        |             |               |               |             |            |                | I/O                 | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                                    |

|        |             |               |               |             |            |                | I                   | <b>ADC0_IN[6]</b> — A/D converter 0, input 6. When configured as an ADC input, the digital function of the pin must be disabled.                                                             |

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |            | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                                                          |

|--------|-------------|---------------|---------------|-------------|------------|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P3[17] | 143         | F15           | -             | -           | [3]        | l;<br>PU                   | I/O                 | <b>P3[17]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[17] — External memory data line 17.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[2]</b> — Pulse Width Modulator 0, output 2.                                                                                  |

|        |             |               |               |             |            |                            | I                   | U1_RXD — Receiver input for UART1.                                                                                                   |

| P3[18] | 151         | C15           | -             | -           | [3]        | l;<br>PU                   | I/O                 | <b>P3[18]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | <b>EMC_D[18]</b> — External memory data line 18.                                                                                     |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[3]</b> — Pulse Width Modulator 0, output 3.                                                                                  |

|        |             |               |               |             |            |                            | I                   | <b>U1_CTS</b> — Clear to Send input for UART1.                                                                                       |

| P3[19] | 161         | B14           | -             | -           | <u>[3]</u> | l;                         | I/O                 | <b>P3[19]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[19] — External memory data line 19.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[4]</b> — Pulse Width Modulator 0, output 4.                                                                                  |

|        |             |               |               |             |            |                            | I                   | <b>U1_DCD</b> — Data Carrier Detect input for UART1.                                                                                 |

| P3[20] | 167         | A13           | -             | -           | [3]        | l;                         | I/O                 | P3[20] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[20] — External memory data line 20.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | PWM0[5] — Pulse Width Modulator 0, output 5.                                                                                         |

|        |             |               |               |             |            |                            | I                   | U1_DSR — Data Set Ready input for UART1.                                                                                             |

| P3[21] | 175         | C10           | -             | -           | [3]        | l;                         | I/O                 | P3[21] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[21] — External memory data line 21.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | PWM0[6] — Pulse Width Modulator 0, output 6.                                                                                         |

|        |             |               |               |             |            |                            | 0                   | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

| P3[22] | 195         | C6            | -             | -           | [3]        | I;                         | I/O                 | P3[22] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[22] — External memory data line 22.                                                                                            |

|        |             |               |               |             |            |                            | I                   | <b>PWM0_CAP0</b> — Capture input for PWM0, channel 0.                                                                                |

|        |             |               |               |             |            |                            | I                   | <b>U1_RI</b> — Ring Indicator input for UART1.                                                                                       |

| P3[23] | 65          | T6            | M4            | 45          | [3]        | I;                         | I/O                 | P3[23] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[23] — External memory data line 23.                                                                                            |

|        |             |               |               |             |            |                            | I                   | <b>PWM1_CAP0</b> — Capture input for PWM1, channel 0.                                                                                |

|        |             |               |               |             |            |                            | I                   | T0_CAP0 — Capture input for Timer 0, channel 0.                                                                                      |

| P3[24] | 58          | R5            | N3            | 40          | [3]        | I;                         | I/O                 | P3[24] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[24] — External memory data line 24.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM1[1]</b> — Pulse Width Modulator 1, output 1.                                                                                  |

|        |             |               |               |             |            |                            | I                   | T0_CAP1 — Capture input for Timer 0, channel 1.                                                                                      |

28 of 126

### 32-bit ARM Cortex-M3 microcontroller

#### Table 5. Pin allocation table TFBGA180

Not all functions are available on all parts. See <u>Table 2</u> and <u>Table 7</u> (EMC pins).

| Ball | Symbol                    | Ball | Symbol | Ball | Symbol             | Ball | Symbol          |

|------|---------------------------|------|--------|------|--------------------|------|-----------------|

| 13   | P2[6]                     | 14   | P4[27] |      | -                  |      | -               |

| Row  | G                         |      |        | I    |                    |      |                 |

| 1    | V <sub>DD(REG)(3V3)</sub> | 2    | VREFP  | 3    | P3[7]              | 4    | P3[15]          |

| 5    | P3[3]                     | 6    | -      | 7    | -                  | 8    | -               |

| 9    | -                         | 10   | P5[3]  | 11   | P2[7]              | 12   | P4[10]          |

| 13   | V <sub>SS</sub>           | 14   | P2[8]  |      | -                  |      | -               |

| Row  | Н                         | I    |        | L    |                    |      | 1               |

| 1    | P5[1]                     | 2    | RSTOUT | 3    | V <sub>SSREG</sub> | 4    | V <sub>SS</sub> |

| 5    | RTC_ALARM                 | 6    | -      | 7    | -                  | 8    | -               |

| 9    | -                         | 10   | P4[5]  | 11   | P2[9]              | 12   | P4[9]           |

| 13   | P0[15]                    | 14   | P0[16] |      | -                  |      | -               |

NXP Semiconductors

32-bit ARM Cortex-M3 microcontroller

PC178x/7x

of 126 reserved.

43

Product data

sheet

Rev.

сı Сī

26 April 2016

#### 32-bit ARM Cortex-M3 microcontroller

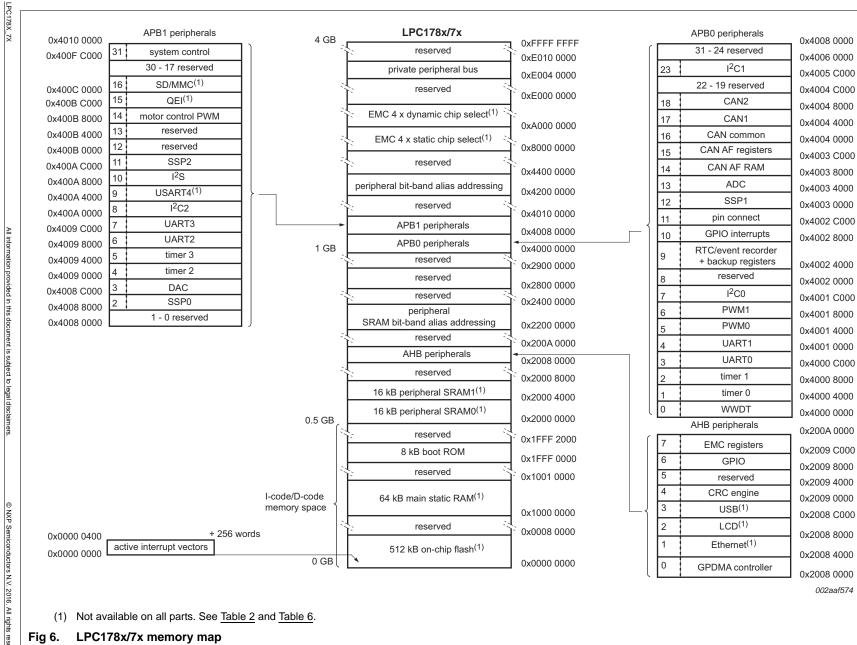

- GPIO registers are accessed through the AHB multilayer bus so that the fastest possible I/O timing can be achieved.

- Mask registers allow treating sets of port bits as a group, leaving other bits unchanged.

- All GPIO registers are byte and half-word addressable.

- Entire port value can be written in one instruction.

- Support for Cortex-M3 bit banding.

- Support for use with the GPDMA controller.

Additionally, any pin on Port 0 and Port 2 providing a digital function can be programmed to generate an interrupt on a rising edge, a falling edge, or both. The edge detection is asynchronous, so it may operate when clocks are not present such as during Power-down mode. Each enabled interrupt can be used to wake up the chip from Power-down mode.

## 7.17.1 Features

- Bit level set and clear registers allow a single instruction to set or clear any number of bits in one port.

- Direction control of individual bits.

- All I/O default to inputs after reset.

- Pull-up/pull-down resistor configuration and open-drain configuration can be programmed through the pin connect block for each GPIO pin.

### 7.18 12-bit ADC

The LPC178x/7x contain one ADC. It is a single 12-bit successive approximation ADC with eight channels and DMA support.

### 7.18.1 Features

- 12-bit successive approximation ADC.

- Input multiplexing among eight pins.

- Power-down mode.

- Measurement range V<sub>SS</sub> to VREFP.

- 12-bit conversion rate: up to 400 kHz.

- Individual channels can be selected for conversion.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- DMA support.

# 7.19 10-bit DAC

The LPC178x/7x contain one DAC. The DAC allows to generate a variable analog output. The maximum output value of the DAC is VREFP.

#### 32-bit ARM Cortex-M3 microcontroller

# 7.23 I<sup>2</sup>S-bus serial I/O controllers

The LPC178x/7x contain one I<sup>2</sup>S-bus interface. The I<sup>2</sup>S-bus provides a standard communication interface for digital audio applications.

The I<sup>2</sup>S-bus specification defines a 3-wire serial bus using one data line, one clock line, and one word select signal. The basic I<sup>2</sup>S connection has one master, which is always the master, and one slave. The I<sup>2</sup>S interface on the LPC178x/7x provides a separate transmit and receive channel, each of which can operate as either a master or a slave.

### 7.23.1 Features

- The interface has separate input/output channels each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 48 kHz (16, 22.05, 32, 44.1, 48) kHz.

- Configurable word select period in master mode (separately for I<sup>2</sup>S input and output).

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive.

- Generates interrupt requests when buffer levels cross a programmable boundary.

- Two DMA requests, controlled by programmable buffer levels. These are connected to the GPDMA block.

- Controls include reset, stop and mute options separately for I<sup>2</sup>S input and I<sup>2</sup>S output.

### 7.24 CAN controller and acceptance filters

The LPC178x/7x contain one CAN controller with two channels.

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router between two of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

### 7.24.1 Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

LPC178X 7X

PWM to immediately release all motor drive outputs. At the same time, the motor control PWM is highly configurable for other generalized timing, counting, capture, and compare applications.

The maximum PWM speed is determined by the PWM resolution (n) and the operating frequency f: PWM speed =  $f/2^n$  (see <u>Table 8</u>).

| PWM resolution | PWM speed |  |  |  |  |

|----------------|-----------|--|--|--|--|

| 6 bit          | 1.875 MHz |  |  |  |  |

| 8 bit          | 0.468 MHz |  |  |  |  |

| 10 bit         | 0.117 MHz |  |  |  |  |

Table 8. PWM speed at operating frequency 120 MHz

# 7.28 Quadrature Encoder Interface (QEI)

Remark: The QEI is available on parts LPC1788/87/86 and LPC1778/77/76

A quadrature encoder, also known as a 2-channel incremental encoder, converts angular displacement into two pulse signals. By monitoring both the number of pulses and the relative phase of the two signals, the user can track the position, direction of rotation, and velocity. In addition, a third channel, or index signal, can be used to reset the position counter. The quadrature encoder interface decodes the digital pulses from a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, the QEI can capture the velocity of the encoder wheel.

### 7.28.1 Features

- Tracks encoder position.

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

- Uses 32-bit registers for position and velocity.

- Three position compare registers with interrupts.

- Index counter for revolution counting.

- Index compare register with interrupts.

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement.

- Digital filter with programmable delays for encoder input signals.

- Can accept decoded signal inputs (clk and direction).

- Connected to APB.

# 7.29 ARM Cortex-M3 system tick timer

The ARM Cortex-M3 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval. In the LPC178x/7x, this timer can be clocked from the internal AHB clock or from a device pin.

#### 7.33.1.3 RTC oscillator

The RTC oscillator provides a 1 Hz clock to the RTC and a 32 kHz clock output that can be output on the CLKOUT pin in order to allow trimming the RTC oscillator without interference from a probe.

#### 7.33.1.4 Watchdog oscillator

The Watchdog Timer has a dedicated watchdog oscillator that provides a 500 kHz clock to the Watchdog Timer. The watchdog oscillator is always running if the Watchdog Timer is enabled. The Watchdog oscillator clock can be output on the CLKOUT pin in order to allow observe its frequency.

In order to allow Watchdog Timer operation with minimum power consumption, which can be important in reduced power modes, the Watchdog oscillator frequency is not tightly controlled. The Watchdog oscillator frequency will vary over temperature and power supply within a particular part, and may vary by processing across different parts. This variation should be taken into account when determining Watchdog reload values.

Within a particular part, temperature and power supply variations can produce up to a  $\pm$ 17 % frequency variation. Frequency variation between devices under the same operating conditions can be up to  $\pm$ 30 %.

### 7.33.2 Main PLL (PLL0) and Alternate PLL (PLL1)

PLL0 (also called the Main PLL) and PLL1 (also called the Alternate PLL) are functionally identical but have somewhat different input possibilities and output connections. These possibilities are shown in Figure 7. The Main PLL can receive its input from either the IRC or the main oscillator and can potentially be used to provide the clocks to nearly everything on the device. The Alternate PLL receives its input only from the main oscillator and is intended to be used as an alternate source of clocking to the USB. The USB has timing needs that may not always be filled by the Main PLL.

Both PLLs are disabled and powered off on reset. If the Alternate PLL is left disabled, the USB clock can be supplied by PLL0 if everything is set up to provide 48 MHz to the USB clock through that route. The source for each clock must be selected via the CLKSEL registers and can be further reduced by clock dividers as needed.

PLL0 accepts an input clock frequency from either the IRC or the main oscillator. If only the Main PLL is used, then its output frequency must be an integer multiple of all other clocks needed in the system. PLL1 takes its input only from the main oscillator, requiring an external crystal in the range of 10 to 25 MHz. In each PLL, the Current Controlled Oscillator (CCO) operates in the range of 156 MHz to 320 MHz, so there are additional dividers to bring the output down to the desired frequencies. The minimum output divider value is 2, insuring that the output of the PLLs have a 50 % duty cycle.

If the USB is used, the possibilities for the CPU clock and other clocks will be limited by the requirements that the frequency be precise and very low jitter, and that the PLL0 output must be a multiple of 48 MHz. Even multiples of 48 MHz that are within the operating range of the PLL are 192 MHz and 288 MHz. Also, only the main oscillator in conjunction with the PLL can meet the precision and jitter specifications for USB. It is due to these limitations that the Alternate PLL is provided.

On the wake-up of Power-down mode, if the IRC was used before entering Power-down mode, it will take IRC 60  $\mu$ s to start-up. After this, four IRC cycles will expire before the code execution can then be resumed if the code was running from SRAM. In the meantime, the flash wake-up timer then counts 12 MHz IRC clock cycles to make the 100  $\mu$ s flash start-up time. When it times out, access to the flash will be allowed. Users need to reconfigure the PLL and clock dividers accordingly.

#### 7.33.4.4 Deep power-down mode

In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

To optimize power conservation, the user has the additional option of turning off or retaining power to the 32 kHz oscillator. It is also possible to use external circuitry to turn off power to the on-chip regulator via the  $V_{DD(REG)(3V3)}$  pins and/or the I/O power via the  $V_{DD(3V3)}$  pins after entering Deep Power-down mode. Power must be restored before device operation can be restarted.

The LPC178x/7x can wake up from Deep power-down mode via the  $\overline{\text{RESET}}$  pin or an alarm match event of the RTC.

#### 7.33.4.5 Wake-up Interrupt Controller (WIC)

The WIC allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep-sleep, Power-down, and Deep power-down modes.

The WIC works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep-sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The WIC eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

### 7.33.5 Peripheral power control

A power control for peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

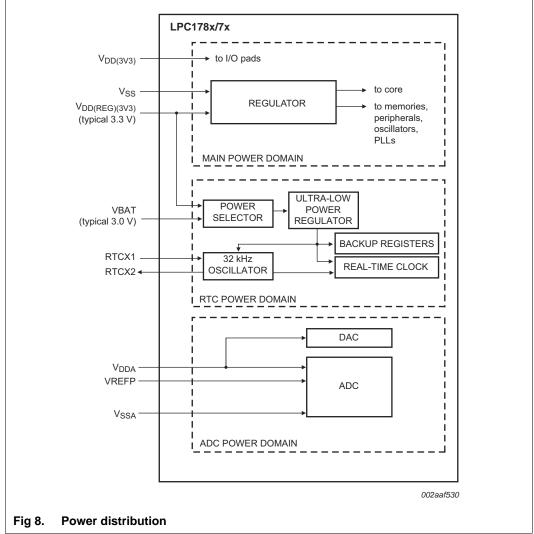

### 7.33.6 Power domains

The LPC178x/7x provide two independent power domains that allow the bulk of the device to have power removed while maintaining operation of the RTC and the backup registers.

On the LPC178x/7x, I/O pads are powered by  $V_{DD(3V3)}$ , while  $V_{DD(REG)(3V3)}$  powers the on-chip voltage regulator which in turn provides power to the CPU and most of the peripherals.

Depending on the LPC178x/7x application, a design can use two power options to manage power consumption.

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(REG)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

The second option uses two power supplies; a 3.3 V supply for the I/O pads ( $V_{DD(3V3)}$ ) and a dedicated 3.3 V supply for the CPU ( $V_{DD(REG)(3V3)}$ ). Having the on-chip voltage regulator powered independently from the I/O pad ring enables shutting down of the I/O pad power supply "on the fly" while the CPU and peripherals stay active.

The VBAT pin supplies power only to the RTC domain. The RTC operates at very low power, which can be supplied by an external battery. The device core power ( $V_{DD(REG)(3V3)}$ ) is used to operate the RTC whenever  $V_{DD(REG)(3V3)}$  is present. There is no power drain from the RTC battery when  $V_{DD(REG)(3V3)}$  is at nominal levels and  $V_{DD(REG)(3V3)} > V_{BAT}$ .

#### 32-bit ARM Cortex-M3 microcontroller

# 9. Thermal characteristics

The average chip junction temperature,  $T_{j}\,(^{\circ}C),$  can be calculated using the following equation:

$$T_j = T_{amb} + (P_D \times R_{th(j-a)}) \tag{1}$$

- T<sub>amb</sub> = ambient temperature (°C),

- R<sub>th(i-a)</sub> = the package junction-to-ambient thermal resistance (°C/W)

- P<sub>D</sub> = sum of internal and I/O power dissipation

#### Table 10. Thermal characteristics

$V_{DD}$  = 3.0 V to 3.6 V;  $T_{amb}$  = -40 °C to +85 °C unless otherwise specified;

| Symbol              | Parameter                       | Min | Тур | Мах | Unit |

|---------------------|---------------------------------|-----|-----|-----|------|

| T <sub>j(max)</sub> | maximum junction<br>temperature | -   | -   | 125 | °C   |

#### Table 11. Thermal resistance (LQFP packages)

$T_{amb} = -40$  °C to +85 °C unless otherwise specified.

| Symbol | Conditions                          | Thermal resistance in °C/W ±15 % |         |  |  |  |

|--------|-------------------------------------|----------------------------------|---------|--|--|--|

|        |                                     | LQFP208                          | LQFP144 |  |  |  |

| өја    | JEDEC (4.5 in × 4 in)               |                                  |         |  |  |  |

|        | 0 m/s                               | 27.4                             | 31.5    |  |  |  |

|        | 1 m/s                               | 25.7                             | 28.1    |  |  |  |

|        | 2.5 m/s                             | 24.4                             | 26.2    |  |  |  |

|        | Single-layer (4.5 in $\times$ 3 in) |                                  |         |  |  |  |

|        | 0 m/s                               | 35.4                             | 43.2    |  |  |  |

|        | 1 m/s                               | 31.2                             | 35.7    |  |  |  |

|        | 2.5 m/s                             | 29.2                             | 32.8    |  |  |  |

| өјс    | -                                   | 8.8                              | 7.8     |  |  |  |

| θjb    | -                                   | 15.4                             | 13.8    |  |  |  |

# Table 12. Thermal resistance value (TFBGA packages)

$T_{amb} = -40$  °C to +85 °C unless otherwise specified.

| Symbol | Conditions                     | Thermal resistance in °C/W ±15 % |          |  |  |  |

|--------|--------------------------------|----------------------------------|----------|--|--|--|

|        |                                | TFBGA208                         | TFBGA180 |  |  |  |

| өја    | JEDEC (4.5 in × 4 in)          |                                  |          |  |  |  |

|        | 0 m/s                          | 41                               | 45.5     |  |  |  |

|        | 1 m/s                          | 35                               | 38.3     |  |  |  |

|        | 2.5 m/s                        | 31                               | 33.8     |  |  |  |

|        | 8-layer (4.5 in $\times$ 3 in) |                                  |          |  |  |  |

|        | 0 m/s                          | 34.9                             | 38       |  |  |  |

|        | 1 m/s                          | 30.9                             | 33.5     |  |  |  |

|        | 2.5 m/s                        | 28                               | 29.8     |  |  |  |

| өјс    | -                              | 8.3                              | 8.9      |  |  |  |

| θjb    | -                              | 13.6                             | 12       |  |  |  |

LPC178X\_7X

### 32-bit ARM Cortex-M3 microcontroller

# 10. Static characteristics

#### Table 13. Static characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                               | Parameter                        | Conditions                                                                                                                          |               | Min | Typ[1] | Max              | Unit |

|--------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|--------|------------------|------|

| Supply pins                          |                                  |                                                                                                                                     |               |     |        |                  |      |

| V <sub>DD(3V3)</sub>                 | supply voltage (3.3 V)           | external rail                                                                                                                       | [2]           | 2.4 | 3.3    | 3.6              | V    |

| V <sub>DD(REG)(3V3)</sub>            | regulator supply voltage (3.3 V) |                                                                                                                                     |               | 2.4 | 3.3    | 3.6              | V    |

| V <sub>DDA</sub>                     | analog 3.3 V pad supply voltage  |                                                                                                                                     | [3]           | 2.7 | 3.3    | 3.6              | V    |

| V <sub>i(VBAT)</sub>                 | input voltage on pin<br>VBAT     |                                                                                                                                     | <u>[4]</u>    | 2.1 | 3.0    | 3.6              | V    |

| V <sub>i(VREFP)</sub>                | input voltage on pin<br>VREFP    |                                                                                                                                     | [3]           | 2.7 | 3.3    | V <sub>DDA</sub> | V    |

| I <sub>DD(REG)(3V3)</sub><br>(3.3 V) |                                  | active mode; code<br>while(1){}<br>executed from flash; all<br>peripherals disabled<br>PCLK = CCLK/4                                |               |     |        |                  |      |

|                                      |                                  | CCLK = 12 MHz; PLL<br>disabled                                                                                                      | <u>[5][6]</u> | -   | 7      | -                | mA   |

|                                      |                                  | CCLK = 120 MHz; PLL<br>enabled                                                                                                      | <u>[5][7]</u> | -   | 51     | -                | mA   |

|                                      |                                  | active mode; code                                                                                                                   |               |     |        |                  |      |

|                                      |                                  | while(1){}                                                                                                                          |               |     |        |                  |      |

|                                      |                                  | executed from flash; all<br>peripherals enabled;<br>PCLK = CCLK/4                                                                   |               |     |        |                  |      |

|                                      |                                  | CCLK = 12 MHz; PLL<br>disabled                                                                                                      | [5][6]        |     | 14     |                  |      |

|                                      |                                  | CCLK = 120 MHz; PLL<br>enabled                                                                                                      | [5][7]        |     | 100    |                  | mA   |

|                                      |                                  | Sleep mode                                                                                                                          | [5][8]        | -   | 5      | -                | mA   |

|                                      |                                  | Deep-sleep mode                                                                                                                     | [5][9]        |     | 550    | -                | μA   |

|                                      |                                  | Power-down mode                                                                                                                     | [5][9]        | -   | 280    | -                | μA   |

| I <sub>BAT</sub>                     | battery supply current           | RTC running;<br>part powered down;<br>$V_{DD(REG)(3V3)} = 0 V;$<br>$V_{i(VBAT)} = 3.0 V;$<br>$V_{DD(3V3)} = 0 V.$                   | [10]          | -   | 1      | _                | μΑ   |

|                                      |                                  | $\begin{array}{c} v_{DD(3V3)} = 0 \ V. \\ \hline part powered; \\ V_{DD(REG)(3V3)} = 3.3 \ V; \\ V_{i(VBAT)} = 3.0 \ V \end{array}$ | [11]          |     | <10    |                  | nA   |

### 32-bit ARM Cortex-M3 microcontroller

# 11.2 External memory interface

#### Table 17. Dynamic characteristics: Static external memory interface

$C_L = 30 \text{ pF}, T_{amb} = -40 \text{ °C to } 85 \text{ °C}, V_{DD(3V3)} = 3.0 \text{ V to } 3.6 \text{ V}.$  Values guaranteed by design.

| Symbol                | Parameter <sup>[1]</sup>           | Conditions <sup>[1]</sup> |               | Min                                                                                                          | Тур                                                                                                           | Max                                                                                   | Unit |

|-----------------------|------------------------------------|---------------------------|---------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|

| Read cyc              | le parameters <sup>[2]</sup>       |                           |               |                                                                                                              |                                                                                                               |                                                                                       |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time       | RD <sub>1</sub>           |               | 2.7                                                                                                          | 3.5                                                                                                           | 4.7                                                                                   | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time              | RD <sub>2</sub>           | [3]           | $2.7 + T_{cy(clk)} \times WAITOEN$                                                                           | $3.4 + T_{cy(clk)} \times WAITOEN$                                                                            | $4.6 + T_{cy(clk)} \times WAITOEN$                                                    | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time             | RD <sub>3</sub> ; PB = 1  | [3]           | 2.8                                                                                                          | 3.8                                                                                                           | 5.1                                                                                   | ns   |

| t <sub>oeloeh</sub>   | OE LOW to OE HIGH<br>time          | RD <sub>4</sub>           | [3]           | $\begin{array}{l} (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} - 2.26 \end{array}$                        | $\begin{array}{l} (\text{WAITRD}-\\ \text{WAITOEN + 1)} \times \\ \text{T}_{\text{cy(clk)}}-2.83 \end{array}$ | $\begin{array}{l} (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} - 3.7 \end{array}$  | ns   |

| t <sub>am</sub>       | memory access time                 | RD <sub>5</sub>           | <u>[3][4]</u> | $\begin{array}{l} (\text{WAITRD}-\\ \text{WAITOEN + 1)} \times \\ \text{T}_{\text{cy(clk)}}-8.6 \end{array}$ | $\begin{array}{l} (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} - 11.9 \end{array}$                         | $\begin{array}{l} (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} - 18.0 \end{array}$ | ns   |

| t <sub>h(D)</sub>     | data input hold time               | RD <sub>6</sub>           | [3][5]        | -4.1                                                                                                         | -5.8                                                                                                          | -                                                                                     | ns   |

| tCSHBLSH              | CS HIGH to BLS HIGH time           | PB = 1                    |               | 2.8                                                                                                          | 3.7                                                                                                           | 5.1                                                                                   | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time            |                           | [3]           | 2.7                                                                                                          | 3.5                                                                                                           | 4.6                                                                                   | ns   |

| t <sub>OEHANV</sub>   | OE HIGH to address<br>invalid time |                           | [3]           | 0.1                                                                                                          | 0.1                                                                                                           | 0.16                                                                                  | ns   |

| t <sub>deact</sub>    | deactivation time                  | RD <sub>7</sub>           | [3]           | -                                                                                                            | -3.4                                                                                                          | -4.7                                                                                  | ns   |

| Write cyc             | le parameters <sup>[2]</sup>       |                           |               | 1                                                                                                            |                                                                                                               |                                                                                       |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time       | WR <sub>1</sub>           |               | 2.7                                                                                                          | 3.5                                                                                                           | 4.7                                                                                   | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time          | WR <sub>2</sub>           |               | 2.8                                                                                                          | 3.9                                                                                                           | 5.1                                                                                   | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time              | WR <sub>3</sub> ; PB =1   | [3]           | $2.7 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                                                  | $3.5 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                                                   | $4.6 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                           | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time             | WR <sub>4</sub> ; PB = 1  | [3]           | 2.8                                                                                                          | 3.9                                                                                                           | 5.1                                                                                   | ns   |

| t <sub>WELWEH</sub>   | WE LOW to WE HIGH time             | WR <sub>5</sub> ; PB =1   | [3]           | $\begin{array}{l} (WAITWR-\\ WAITWEN+1)\times\\ T_{cy(clk)}-2.3 \end{array}$                                 | $\begin{array}{l} (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} - 2.8 \end{array}$                          | $\begin{array}{l} (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} - 3.8 \end{array}$  | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time           | PB = 1                    | [3]           |                                                                                                              | $\begin{array}{l} (\text{WAITWR}-\\ \text{WAITWEN + 3)}\times\\ \text{T}_{\text{cy(clk)}}-3.4 \end{array}$    | $\begin{array}{c} (WAITWR-\\ WAITWEN + 3) \times \\ T_{cy(clk)} - 4.9 \end{array}$    | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time       | WR <sub>6</sub> ; PB =1   | [3]           | $2.5 + T_{cy(clk)}$                                                                                          | $3.3 + T_{cy(clk)}$                                                                                           | $4.3 + T_{cy(clk)}$                                                                   | ns   |

| t <sub>WEHEOW</sub>   | WE HIGH to end of write time       | WR <sub>7</sub> ; PB = 1  | [3][6]        | $T_{cy(clk)} - 2.7$                                                                                          | T <sub>cy(clk)</sub> – 3.4                                                                                    | $T_{cy(clk)} - 4.6$                                                                   | ns   |

| t <sub>BLSHDNV</sub>  | BLS HIGH to data invalid time      | PB = 1                    |               | 2.7                                                                                                          | 3.6                                                                                                           | 4.8                                                                                   | ns   |

| t <sub>WEHANV</sub>   | WE HIGH to address invalid time    | PB = 1                    | [3]           | $2.4 + T_{cy(clk)}$                                                                                          | $3.0 + T_{cy(clk)}$                                                                                           | $3.9 + T_{cy(clk)}$                                                                   | ns   |

LPC178X\_7X

#### 32-bit ARM Cortex-M3 microcontroller

# 11.7 I<sup>2</sup>C-bus

### Table 27. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

| $T_{amb} = -40$ | °C t | o +85 | °C.[2] |

|-----------------|------|-------|--------|

|-----------------|------|-------|--------|

| Symbol              | Parameter                    |                | Conditions                  | Min                   | Max | Unit |

|---------------------|------------------------------|----------------|-----------------------------|-----------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock<br>frequency       |                | Standard-mode               | 0                     | 100 | kHz  |

|                     |                              |                | Fast-mode                   | 0                     | 400 | kHz  |

|                     |                              |                | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time                    | [4][5][6][7]   | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                              |                | Standard-mode               |                       |     |      |

|                     |                              |                | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                              |                | Fast-mode Plus              | -                     | 120 | ns   |

| t <sub>LOW</sub>    | LOW period of the SCL clock  |                | Standard-mode               | 4.7                   | -   | μS   |

|                     |                              |                | Fast-mode                   | 1.3                   | -   | μS   |

|                     |                              |                | Fast-mode Plus              | 0.5                   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock |                | Standard-mode               | 4.0                   | -   | μS   |

|                     |                              |                | Fast-mode                   | 0.6                   | -   | μS   |

|                     |                              |                | Fast-mode Plus              | 0.26                  | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time               | [3][4][8]      | Standard-mode               | 0                     | -   | μS   |

|                     |                              |                | Fast-mode                   | 0                     | -   | μS   |

|                     |                              |                | Fast-mode Plus              | 0                     | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up<br>time          | <u>[9][10]</u> | Standard-mode               | 250                   | -   | ns   |

|                     |                              |                | Fast-mode                   | 100                   | -   | ns   |

|                     |                              |                | Fast-mode Plus              | 50                    | -   | ns   |

[1] See the I<sup>2</sup>C-bus specification UM10204 for details.

[2] Parameters are valid over operating temperature range unless otherwise specified.

- [3] tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [5]  $C_b$  = total capacitance of one bus line in pF.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum  $t_{HD;DAT}$  could be 3.45  $\mu$ s and 0.9  $\mu$ s for Standard-mode and Fast-mode but must be less than the maximum of  $t_{VD;DAT}$  or  $t_{VD;ACK}$  by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT}$  = 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

### 32-bit ARM Cortex-M3 microcontroller

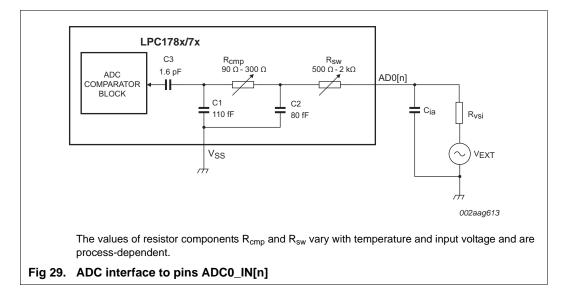

#### Table 32. ADC interface components

| Component        | Range                        | Description                                                                                                |

|------------------|------------------------------|------------------------------------------------------------------------------------------------------------|

| R <sub>cmp</sub> | 90 Ω to 300 Ω                | Switch-on resistance for the comparator input switch. Varies with temperature, input voltage, and process. |

| R <sub>sw</sub>  | 500 $\Omega$ to 2 k $\Omega$ | Switch-on resistance for channel selection switch. Varies with temperature, input voltage, and process.    |

| C1               | 110 fF                       | Parasitic capacitance from the ADC block level.                                                            |

| C2               | 80 fF                        | Parasitic capacitance from the ADC block level.                                                            |

| C3               | 1.6 pF                       | Sampling capacitor.                                                                                        |

# **13. DAC electrical characteristics**

#### Table 33. 10-bit DAC electrical characteristics

$V_{DDA} = 2.7 \text{ V to } 3.6 \text{ V}; T_{amb} = -40 \text{ °C to } +85 \text{ °C unless otherwise specified}$

| Symbol              | Parameter                    | Min | Тур  | Max | Unit |  |

|---------------------|------------------------------|-----|------|-----|------|--|

| E <sub>D</sub>      | differential linearity error | -   | ±1   | -   | LSB  |  |

| E <sub>L(adj)</sub> | integral non-linearity       | -   | ±1.5 | -   | LSB  |  |

| E <sub>O</sub>      | offset error                 | -   | 0.6  | -   | %    |  |

| E <sub>G</sub>      | gain error                   | -   | 0.6  | -   | %    |  |

| CL                  | load capacitance             | -   | -    | 200 | pF   |  |

| RL                  | load resistance              | 1   | -    | -   | kΩ   |  |

100 of 126

#### 32-bit ARM Cortex-M3 microcontroller

# 14.2 Crystal oscillator XTAL input and component selection

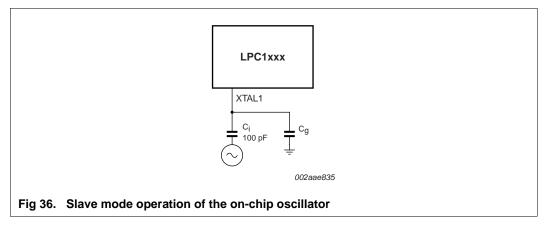

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

LPC178X 7X

105 of 126

#### 32-bit ARM Cortex-M3 microcontroller

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (<u>Figure 36</u>), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

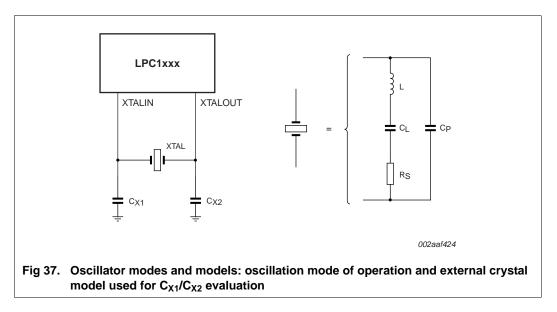

External components and models used in oscillation mode are shown in Figure 37 and in Table 34 and Table 35. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in Figure 37 represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

Table 34. Recommended values for  $C_{\chi_1}/C_{\chi_2}$  in oscillation mode (crystal and external components parameters): low frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> |       | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> /C <sub>X2</sub> |  |

|----------------------------------------------------|-------|-----------------------------------------------------|--------------------------------------------------------------|--|

| 1 MHz to 5 MHz                                     | 10 pF | < 300 Ω                                             | 18 pF, 18 pF                                                 |  |

|                                                    | 20 pF | < 300 Ω                                             | 39 pF, 39 pF                                                 |  |

|                                                    | 30 pF | < 300 Ω                                             | 57 pF, 57 pF                                                 |  |

© NXP Semiconductors N.V. 2016. All rights reserved.

# 32-bit ARM Cortex-M3 microcontroller

| Document ID      | Release date                                                                                                                                                                                                                                    | Data sheet status              | Change notice        | Supersedes     |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------|----------------|--|--|

| LPC178X_7X v.4.1 | 20121115                                                                                                                                                                                                                                        | Product data sheet             | -                    | LPC178X_7X v.4 |  |  |

| Modifications:   | <ul> <li>LCD timing characteristics updated in Table 27 "Dynamic characteristics: LCD" and<br/>Figure 26 added.</li> </ul>                                                                                                                      |                                |                      |                |  |  |

|                  | <ul> <li>Removed table note "The peak current is limited to 25 times the corresponding maximum<br/>current." in Table 9.</li> </ul>                                                                                                             |                                |                      |                |  |  |

|                  | <ul> <li>Removed deep power-down spec Table 13 and associated table note.</li> </ul>                                                                                                                                                            |                                |                      |                |  |  |

|                  | <ul> <li>Updated min value for t<sub>WEHEOW</sub> Table 15.</li> </ul>                                                                                                                                                                          |                                |                      |                |  |  |

|                  | <ul> <li>Removed F</li> </ul>                                                                                                                                                                                                                   | g 21 Internal RC oscillator fr | equency versus tempe | erature.       |  |  |

|                  | <ul> <li>Updated 12-bit and 8-bit values for E<sub>T</sub> Table 29.</li> </ul>                                                                                                                                                                 |                                |                      |                |  |  |

|                  | <ul> <li>Changed data</li> </ul>                                                                                                                                                                                                                | ta sheet status to Product.    |                      |                |  |  |

| LPC178X_7X v.4   | 20120501                                                                                                                                                                                                                                        | Preliminary data sheet         | -                    | LPC178X_7X v.3 |  |  |