Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M3Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, EBI/EMI, Ethernet, I*C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTGPripheralsBrown-out Detect/Reset, DMA, I*S, Motor Control PWM, POR, PWM, WDTNumber of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size06K x 8Voltage - Suppl (vccr/vd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature4.0°C ~ 85°C (TA)Mounting Type180-TFBGA (12x12)Purchase UBLhttps://www.exfl.com/product-detail/nxp-semiconductors/lpc1778fet180-S51 | Decans                     |                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, EBI/EMI, Ethernet, I²C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTGPeripheralsBrown-out Detect/Reset, DMA, I²S, Motor Control PWM, POR, PWM, WDTNumber of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                             | Product Status             | Active                                                                                                  |

| Speed120MHzConnectivityCANbus, EBI/EMI, Ethernet, I²C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTGPeripheralsBrown-out Detect/Reset, DMA, I²S, Motor Control PWM, POR, PWM, WDTNumber of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                       | Core Processor             | ARM® Cortex®-M3                                                                                         |

| ConnectivityCANbus, EBI/EMI, Ethernet, I²C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTGPeripheralsBrown-out Detect/Reset, DMA, I²S, Motor Control PWM, POR, PWM, WDTNumber of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                                                        | Core Size                  | 32-Bit Single-Core                                                                                      |

| PeripheralsBrown-out Detect/Reset, DMA, I²S, Motor Control PWM, POR, PWM, WDTNumber of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                                                                                                                                       | Speed                      | 120MHz                                                                                                  |

| Number of I/O141Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                    | Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Program Memory Size512KB (512K x 8)Program Memory TypeFLASHFLPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdu)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                    | Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                         |

| Program Memory TypeFLASHEEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                       | Number of I/O              | 141                                                                                                     |

| EEPROM Size4K x 8RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                               | Program Memory Size        | 512KB (512K x 8)                                                                                        |

| RAM Size96K x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                | Program Memory Type        | FLASH                                                                                                   |

| Voltage - Supply (Vcc/Vdb)2.4V ~ 3.6VData ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                               | EEPROM Size                | 4K x 8                                                                                                  |

| Data ConvertersA/D 8x12b; D/A 1x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                                                                    | RAM Size                   | 96K × 8                                                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                                             |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12×12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Data Converters            | A/D 8x12b; D/A 1x10b                                                                                    |

| Mounting TypeSurface MountPackage / Case180-TFBGASupplier Device Package180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Oscillator Type            | Internal                                                                                                |

| Package / Case     180-TFBGA       Supplier Device Package     180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 85°C (TA)                                                                                       |

| Supplier Device Package 180-TFBGA (12x12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | Surface Mount                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Package / Case             | 180-TFBGA                                                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1778fet180-551                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Supplier Device Package    | 180-TFBGA (12x12)                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1778fet180-551                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, USB, Ethernet, and the General Purpose DMA controller. This interconnect provides communication with no arbitration delays unless two masters attempt to access the same slave at the same time.

- Split APB bus allows for higher throughput with fewer stalls between the CPU and DMA. A single level of write buffering allows the CPU to continue without waiting for completion of APB writes if the APB was not already busy.

- ◆ Cortex-M3 system tick timer, including an external clock input option.

- Standard JTAG test/debug interface as well as Serial Wire Debug and Serial WireTrace Port options.

- ◆ Embedded Trace Macrocell (ETM) module supports real-time trace.

- Boundary scan for simplified board testing.

- ◆ Non-maskable Interrupt (NMI) input.

- Memory:

- ♦ Up to 512 kB on-chip flash program memory with In-System Programming (ISP) and In-Application Programming (IAP) capabilities. The combination of an enhanced flash memory accelerator and location of the flash memory on the CPU local code/data bus provides high code performance from flash.

- Up to 96 kB on-chip SRAM includes:

64 kB of main SRAM on the CPU with local code/data bus for high-performance CPU access.

Two 16 kB peripheral SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for DMA memory as well as for general purpose instruction and data storage.

- ◆ Up to 4032 byte on-chip EEPROM.

- LCD controller, supporting both Super-Twisted Nematic (STN) and Thin-Film Transistors (TFT) displays.

- Dedicated DMA controller.

- ◆ Selectable display resolution (up to 1024 × 768 pixels).

- Supports up to 24-bit true-color mode.

- External Memory Controller (EMC) provides support for asynchronous static memory devices such as RAM, ROM and flash, as well as dynamic memories such as single data rate SDRAM with an SDRAM clock of up to 80 MHz.

- Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with the SSP, I2S, UART, CRC engine, Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, GPIO, and for memory-to-memory transfers.

- Serial interfaces:

- Ethernet MAC with MII/RMII interface and associated DMA controller. These functions reside on an independent AHB.

- USB 2.0 full-speed dual-port device/host/OTG controller with on-chip PHY and associated DMA controller.

- Five UARTs with fractional baud rate generation, internal FIFO, DMA support, and RS-485/EIA-485 support. One UART (UART1) has full modem control I/O, and one UART (USART4) supports IrDA, synchronous mode, and a smart card mode conforming to ISO7816-3.

- Three SSP controllers with FIFO and multi-protocol capabilities. The SSP controllers can be used with the GPDMA.

LPC178X 7X

- The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in Deep-sleep, Power-down, and Deep power-down modes.

- Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, PORT0/2 pin interrupt, and NMI).

- Brownout detect with separate threshold for interrupt and forced reset.

- ◆ On-chip Power-On Reset (POR).

- Clock generation:

- Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock, CPU clock, USB clock, or the watchdog timer clock.

- On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

- 12 MHz Internal RC oscillator (IRC) trimmed to 1% accuracy that can optionally be used as a system clock.

- An on-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator or the internal RC oscillator.

- ♦ A second, dedicated PLL may be used for USB interface in order to allow added flexibility for the Main PLL settings.

- Versatile pin function selection feature allows many possibilities for using on-chip peripheral functions.

- Unique device serial number for identification purposes.

- Single 3.3 V power supply (2.4 V to 3.6 V). Temperature range of -40 °C to 85 °C.

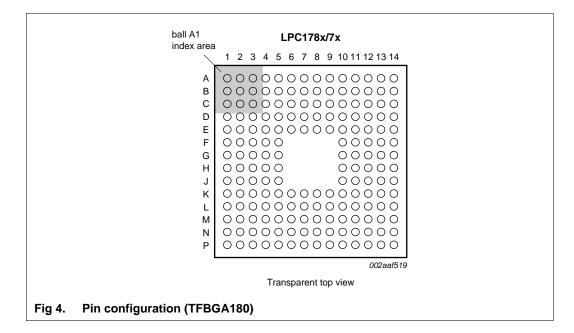

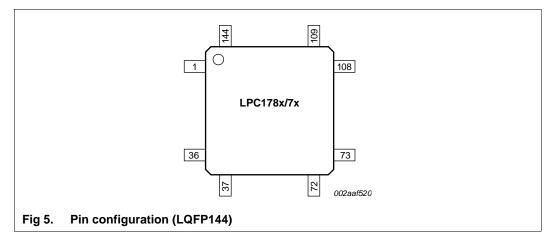

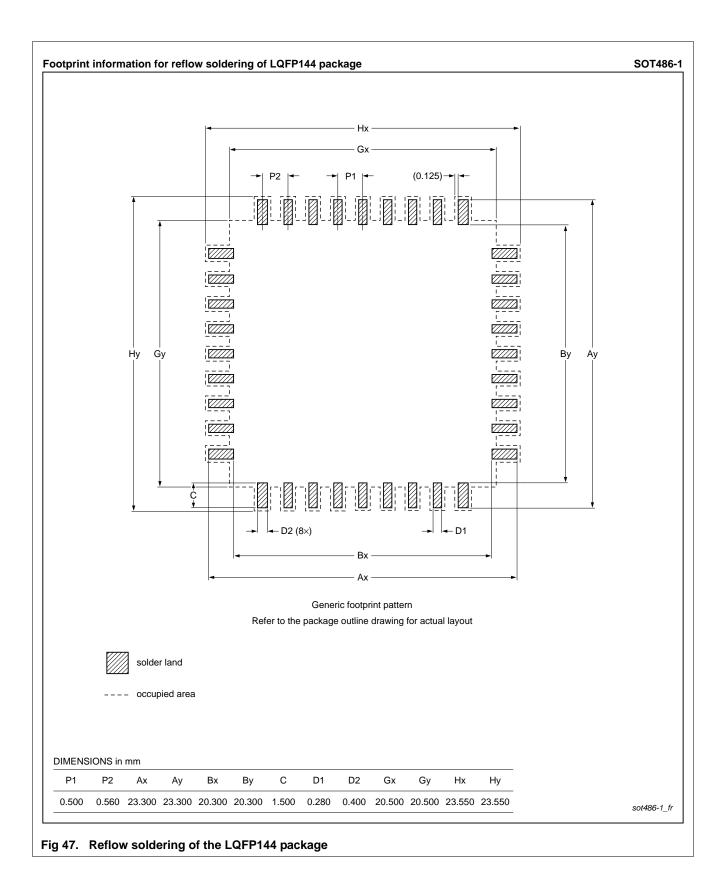

- Available as LQFP208, TFBGA208, TFBGA180, and LQFP144 package.

## 3. Applications

- Communications:

- ◆ Point-of-sale terminals, web servers, multi-protocol bridges

- Industrial/Medical:

- Automation controllers, application control, robotics control, HVAC, PLC, inverters, circuit breakers, medical scanning, security monitoring, motor drive, video intercom

- Consumer/Appliance:

- Audio, MP3 decoders, alarm systems, displays, printers, scanners, small appliances, fitness equipment

- Automotive:

- ◆ After-market, car alarms, GPS/fleet monitors

LPC178X 7X

### 32-bit ARM Cortex-M3 microcontroller

#### Table 2. LPC178x/7x ordering options

All parts include two CAN channels, three SSP interfaces, three I<sup>2</sup>C interfaces, one I<sup>2</sup>S interface, DAC, and an 8-channel 12-bit ADC.

| Type number   | Device order<br>part number | Flash<br>(kB) | Main SRAM<br>(kB) | Peripheral<br>SRAM (kB) | Total SRAM<br>(kB) | EEPROM<br>(byte) | Ethernet | USB   | UART         | EMC bus<br>width (bit) [1] | GPIO | LCD | QEI | SD/<br>MMC |

|---------------|-----------------------------|---------------|-------------------|-------------------------|--------------------|------------------|----------|-------|--------------|----------------------------|------|-----|-----|------------|

| LPC178x       |                             |               |                   |                         |                    |                  |          |       |              |                            |      |     |     |            |

| LPC1788FBD208 | LPC1788FBD208/CP3E          | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Y   | Y   | Y          |

| LPC1788FET208 | LPC1788FET208,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Y   | Y   | Y          |

| LPC1788FET180 | LPC1788FET180,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 16                         | 141  | Y   | Y   | Y          |

| LPC1788FBD144 | LPC1788FBD144,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 8                          | 109  | Y   | Y   | Y          |

| LPC1787FBD208 | LPC1787FBD208,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Ν        | H/O/D | 5            | 32                         | 165  | Y   | Y   | Y          |

| LPC1786FBD208 | LPC1786FBD208,551           | 256           | 64                | 16                      | 80                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Y   | Y   | Y          |

| LPC1785FBD208 | LPC1785FBD208K              | 256           | 64                | 16                      | 80                 | 4032             | Ν        | H/O/D | 5            | 32                         | 165  | Y   | Ν   | Y          |

| LPC177x       |                             |               |                   |                         |                    |                  |          |       |              |                            |      |     |     |            |

| LPC1778FBD208 | LPC1778FBD208,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Ν   | Y   | Y          |

| LPC1778FET208 | LPC1778FET208,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Ν   | Y   | Y          |

| LPC1778FET180 | LPC1778FET180,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 16                         | 141  | Ν   | Y   | Y          |

| LPC1778FBD144 | LPC1778FBD144,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Y        | H/O/D | 5            | 8                          | 109  | Ν   | Y   | Y          |

| LPC1777FBD208 | LPC1777FBD208,551           | 512           | 64                | 16 	imes 2              | 96                 | 4032             | Ν        | H/O/D | 5            | 32                         | 165  | Ν   | Y   | Y          |

| LPC1776FBD208 | LPC1776FBD208,551           | 256           | 64                | 16                      | 80                 | 4032             | Y        | H/O/D | 5            | 32                         | 165  | Ν   | Y   | Y          |

| LPC1776FET180 | LPC1776FET180,551           | 256           | 64                | 16                      | 80                 | 4032             | Y        | H/O/D | 5            | 16                         | 141  | Ν   | Y   | Y          |

| LPC1774FBD208 | LPC1774FBD208,551           | 128           | 32                | 8                       | 40                 | 2048             | Ν        | D     | 5            | 32                         | 165  | Ν   | Ν   | Ν          |

| LPC1774FBD144 | LPC1774FBD144,551           | 128           | 32                | 8                       | 40                 | 2048             | Ν        | D     | 4 <u>[2]</u> | 8                          | 109  | Ν   | Ν   | Ν          |

[1] Maximum data bus width of the External Memory Controller (EMC) depends on package size. Smaller widths may be used.

[2] USART4 not available.

Product data sheet

#### 32-bit ARM Cortex-M3 microcontroller

## 6.2 Pin description

I/O pins on the LPC178x/7x are 5 V tolerant and have input hysteresis unless otherwise indicated in the table below. Crystal pins, power pins, and reference voltage pins are not 5 V tolerant. In addition, when pins are selected to be ADC inputs, they are no longer 5 V tolerant and the input voltage must be limited to the voltage at the ADC positive reference pin (VREFP).

All port pins Pn[m] are multiplexed, and the multiplexed functions appear in <u>Table 3</u> in the order defined by the FUNC bits of the corresponding IOCON register up to the highest used function number. Each port pin can support up to eight multiplexed functions. IOCON register FUNC values which are reserved are noted as 'R' in the pin configuration table.

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |     | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                                                   |

|--------|-------------|---------------|---------------|-------------|-----|----------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| P1[8]  | 190         | C7            | B6            | 132         | [3] | l;                         | I/O                 | P1[8] — General purpose digital input/output pin.                                                                             |

|        |             |               |               |             |     | PU                         | I                   | <b>ENET_CRS (ENET_CRS_DV)</b> — Ethernet Carrier Sense (MII interface) or Ethernet Carrier Sense/Data Valid (RMII interface). |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                                                                        |

|        |             |               |               |             |     |                            | 0                   | T3_MAT1 — Match output for Timer 3, channel 1.                                                                                |

|        |             |               |               |             |     |                            | I/O                 | SSP2_SSEL — Slave Select for SSP2.                                                                                            |

| P1[9]  | 188         | A6            | D7            | 131         | [3] | I;                         | I/O                 | P1[9] — General purpose digital input/output pin.                                                                             |

|        |             |               |               |             |     | PU                         | I                   | ENET_RXD0 — Ethernet receive data 0 (RMII/MII interface).                                                                     |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                                                                        |

|        |             |               |               |             |     |                            | 0                   | T3_MAT0 — Match output for Timer 3, channel 0.                                                                                |

| P1[10] | 186         | C8            | A7            | 129         | [3] | I;                         | I/O                 | P1[10] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | ENET_RXD1 — Ethernet receive data 1 (RMII/MII interface).                                                                     |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                                                                        |

|        |             |               |               |             |     |                            | I                   | T3_CAP0 — Capture input for Timer 3, channel 0.                                                                               |

| P1[11] | 163         | A14           | A12           | -           | [3] | I;                         | I/O                 | P1[11] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | ENET_RXD2 — Ethernet Receive Data 2 (MII interface).                                                                          |

|        |             |               |               |             |     |                            | I/O                 | <b>SD_DAT[2]</b> — Data line 2 for SD card interface.                                                                         |

|        |             |               |               |             |     |                            | 0                   | PWM0[6] — Pulse Width Modulator 0, output 6.                                                                                  |

| P1[12] | 157         | A16           | A14           | -           | [3] | I;                         | I/O                 | P1[12] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | ENET_RXD3 — Ethernet Receive Data (MII interface).                                                                            |

|        |             |               |               |             |     |                            | I/O                 | <b>SD_DAT[3]</b> — Data line 3 for SD card interface.                                                                         |

|        |             |               |               |             |     |                            | I                   | <b>PWM0_CAP0</b> — Capture input for PWM0, channel 0.                                                                         |

| P1[13] | 147         | D16           | D14           | -           | [3] | I;                         | I/O                 | P1[13] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (MII interface).                                                              |

| P1[14] | 184         | A7            | D8            | 128         | [3] | I;                         | I/O                 | P1[14] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | <b>ENET_RX_ER</b> — Ethernet receive error (RMII/MII interface).                                                              |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                                                                        |

|        |             |               |               |             |     |                            | I                   | T2_CAP0 — Capture input for Timer 2, channel 0.                                                                               |

| P1[15] | 182         | A8            | A8            | 126         | [3] | I;                         | I/O                 | P1[15] — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |     | PU                         | I                   | <b>ENET_RX_CLK (ENET_REF_CLK)</b> — Ethernet Receive Clock (MII interface) or Ethernet Reference Clock (RMII interface).      |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                                                                        |

|        |             |               |               |             |     |                            | I/O                 | <b>I2C2_SDA</b> — I <sup>2</sup> C2 data input/output (this pin does not use a specialized I2C pad).                          |

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |     | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                   |

|--------|-------------|---------------|---------------|-------------|-----|----------------------------|---------------------|-------------------------------------------------------------------------------|

| P1[25] | 80          | T10           | L7            | 56          | [3] | I;                         | I/O                 | P1[25] — General purpose digital input/output pin.                            |

|        |             |               |               |             |     | PU                         | 0                   | <b>USB_LS1</b> — Low Speed status for USB port 1 (OTG transceiver).           |

|        |             |               |               |             |     |                            | 0                   | <b>USB_HSTEN1</b> — Host Enabled status for USB port 1.                       |

|        |             |               |               |             |     |                            | 0                   | T1_MAT1 — Match output for Timer 1, channel 1.                                |

|        |             |               |               |             |     |                            | 0                   | MC_1A — Motor control PWM channel 1, output A.                                |

|        |             |               |               |             |     |                            | 0                   | CLKOUT — Selectable clock output.                                             |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[11] — LCD data.                                                        |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[15] — LCD data.                                                        |

| P1[26] | 82          | R10           | P8            | 57          | [3] | l;                         | I/O                 | P1[26] — General purpose digital input/output pin.                            |

|        |             |               |               |             |     | PU                         | 0                   | <b>USB_SSPND1</b> — USB port 1 Bus Suspend status (OTG transceiver).          |

|        |             |               |               |             |     |                            | 0                   | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                          |

|        |             |               |               |             |     |                            | I                   | T0_CAP0 — Capture input for Timer 0, channel 0.                               |

|        |             |               |               |             |     |                            | 0                   | MC_1B — Motor control PWM channel 1, output B.                                |

|        |             |               |               |             |     |                            | I/O                 | SSP1_SSEL — Slave Select for SSP1.                                            |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[12] — LCD data.                                                        |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[20] — LCD data.                                                        |

| P1[27] | 88          | T12           | M9            | 61          | [3] | I;                         | I/O                 | P1[27] — General purpose digital input/output pin.                            |

|        |             |               |               |             |     | PU                         | I                   | <b>USB_INT1</b> — USB port 1 OTG transceiver interrupt (OTG transceiver).     |

|        |             |               |               |             |     |                            | I                   | USB_OVRCR1 — USB port 1 Over-Current status.                                  |

|        |             |               |               |             |     |                            | I                   | T0_CAP1 — Capture input for Timer 0, channel 1.                               |

|        |             |               |               |             |     |                            | 0                   | CLKOUT — Selectable clock output.                                             |

|        |             |               |               |             |     |                            | -                   | R — Function reserved.                                                        |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[13] — LCD data.                                                        |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[21] — LCD data.                                                        |

| P1[28] | 90          | T13           | P10           | 63          | [3] | l;                         | I/O                 | P1[28] — General purpose digital input/output pin.                            |

|        |             |               |               |             |     | PU                         | I/O                 | <b>USB_SCL1</b> — USB port 1 I <sup>2</sup> C serial clock (OTG transceiver). |

|        |             |               |               |             |     |                            | I                   | <b>PWM1_CAP0</b> — Capture input for PWM1, channel 0.                         |

|        |             |               |               |             |     |                            | 0                   | <b>T0_MAT0</b> — Match output for Timer 0, channel 0.                         |

|        |             |               |               |             |     |                            | 0                   | MC_2A — Motor control PWM channel 2, output A.                                |

|        |             |               |               |             |     |                            | I/O                 | SSP0_SSEL — Slave Select for SSP0.                                            |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[14] — LCD data.                                                        |

|        |             |               |               |             |     |                            | 0                   | LCD_VD[22] — LCD data.                                                        |

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |             | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                                                                                                   |

|--------|-------------|---------------|---------------|-------------|-------------|----------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2[9]  | 132         | H16           | H11           | 92          | [3]         | I;                         | I/O                 | P2[9] — General purpose digital input/output pin.                                                                                                                             |

|        |             |               |               |             |             | PU                         | 0                   | <b>USB_CONNECT1</b> — USB1 SoftConnect control. Signal used to switch an external 1.5 k $\Omega$ resistor under the software control. Used with the SoftConnect USB feature.  |

|        |             |               |               |             |             |                            | I                   | U2_RXD — Receiver input for UART2.                                                                                                                                            |

|        |             |               |               |             |             |                            | I                   | U4_RXD — Receiver input for USART4.                                                                                                                                           |

|        |             |               |               |             |             |                            | I/O                 | ENET_MDIO — Ethernet MIIM data input and output.                                                                                                                              |

|        |             |               |               |             |             |                            | -                   | R — Function reserved.                                                                                                                                                        |

|        |             |               |               |             |             |                            | I                   | LCD_VD[3] — LCD data.                                                                                                                                                         |

|        |             |               |               |             |             |                            | I                   | LCD_VD[7] — LCD data.                                                                                                                                                         |

| P2[10] | 110         | N15           | M13           | 76          | <u>[10]</u> | l;<br>PU                   | I/O                 | <b>P2[10]</b> — General purpose digital input/output pin. This pin includes a 10 ns input .                                                                                   |

|        |             |               |               |             |             |                            |                     | A LOW on this pin while $\overline{\text{RESET}}$ is LOW forces the on-chip boot loader to take over control of the part after a reset and go into ISP mode.                  |

|        |             |               |               |             |             |                            | I                   | EINT0 — External interrupt 0 input.                                                                                                                                           |

|        |             |               |               |             |             |                            | I                   | NMI — Non-maskable interrupt input.                                                                                                                                           |

| P2[11] | 108         | T17           | M12           | 75          | [10]        | l;<br>PU                   | I/O                 | <b>P2[11]</b> — General purpose digital input/output pin. This pin includes a 10 ns input glitch filter.                                                                      |

|        |             |               |               |             |             |                            | I                   | EINT1 — External interrupt 1 input.                                                                                                                                           |

|        |             |               |               |             |             |                            | I/O                 | <b>SD_DAT[1]</b> — Data line 1 for SD card interface.                                                                                                                         |

|        |             |               |               |             |             |                            | I/O                 | <b>I2S_TX_SCK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> S-bus specification.     |

|        |             |               |               |             |             |                            | -                   | R — Function reserved.                                                                                                                                                        |

|        |             |               |               |             |             |                            | -                   | R — Function reserved.                                                                                                                                                        |

|        |             |               |               |             |             |                            | -                   | R — Function reserved.                                                                                                                                                        |

|        |             |               |               |             |             |                            | 0                   | LCD_CLKIN — LCD clock.                                                                                                                                                        |

| P2[12] | 106         | N14           | N14           | 73          | <u>[10]</u> | l;<br>PU                   | I/O                 | <b>P2[12]</b> — General purpose digital input/output pin. This pin includes a 10 ns input glitch filter.                                                                      |

|        |             |               |               |             |             |                            | I                   | EINT2 — External interrupt 2 input.                                                                                                                                           |

|        |             |               |               |             |             |                            | I/O                 | <b>SD_DAT[2]</b> — Data line 2 for SD card interface.                                                                                                                         |

|        |             |               |               |             |             |                            | I/O                 | <b>I2S_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |             |               |               |             |             |                            | 0                   | LCD_VD[4] — LCD data.                                                                                                                                                         |

|        |             |               |               |             |             |                            | 0                   | LCD_VD[3] — LCD data.                                                                                                                                                         |

|        |             |               |               |             |             |                            | 0                   | LCD_VD[8] — LCD data.                                                                                                                                                         |

|        |             |               |               |             |             |                            | 0                   | LCD_VD[18] — LCD data.                                                                                                                                                        |

LPC178X\_7X

© NXP Semiconductors N.V. 2016. All rights reserved.

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 |            | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                                                          |

|--------|-------------|---------------|---------------|-------------|------------|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P3[17] | 143         | F15           | -             | -           | [3]        | l;<br>PU                   | I/O                 | <b>P3[17]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[17] — External memory data line 17.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[2]</b> — Pulse Width Modulator 0, output 2.                                                                                  |

|        |             |               |               |             |            |                            | I                   | U1_RXD — Receiver input for UART1.                                                                                                   |

| P3[18] | 151         | C15           | -             | -           | [3]        | l;<br>PU                   | I/O                 | <b>P3[18]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | <b>EMC_D[18]</b> — External memory data line 18.                                                                                     |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[3]</b> — Pulse Width Modulator 0, output 3.                                                                                  |

|        |             |               |               |             |            |                            | I                   | <b>U1_CTS</b> — Clear to Send input for UART1.                                                                                       |

| P3[19] | 161         | B14           | -             | -           | <u>[3]</u> | l;                         | I/O                 | <b>P3[19]</b> — General purpose digital input/output pin.                                                                            |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[19] — External memory data line 19.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM0[4]</b> — Pulse Width Modulator 0, output 4.                                                                                  |

|        |             |               |               |             |            |                            | I                   | <b>U1_DCD</b> — Data Carrier Detect input for UART1.                                                                                 |

| P3[20] | 167         | A13           | -             | -           | [3]        | l;                         | I/O                 | P3[20] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | <b>EMC_D[20]</b> — External memory data line 20.                                                                                     |

|        |             |               |               |             |            |                            | 0                   | PWM0[5] — Pulse Width Modulator 0, output 5.                                                                                         |

|        |             |               |               |             |            |                            | I                   | U1_DSR — Data Set Ready input for UART1.                                                                                             |

| P3[21] | 175         | C10           | -             | -           | [3]        | l;                         | I/O                 | P3[21] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[21] — External memory data line 21.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | PWM0[6] — Pulse Width Modulator 0, output 6.                                                                                         |

|        |             |               |               |             |            |                            | 0                   | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

| P3[22] | 195         | C6            | -             | -           | [3]        | I;                         | I/O                 | P3[22] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[22] — External memory data line 22.                                                                                            |

|        |             |               |               |             |            |                            | I                   | <b>PWM0_CAP0</b> — Capture input for PWM0, channel 0.                                                                                |

|        |             |               |               |             |            |                            | I                   | <b>U1_RI</b> — Ring Indicator input for UART1.                                                                                       |

| P3[23] | 65          | T6            | M4            | 45          | [3]        | I;                         | I/O                 | P3[23] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[23] — External memory data line 23.                                                                                            |

|        |             |               |               |             |            |                            | I                   | <b>PWM1_CAP0</b> — Capture input for PWM1, channel 0.                                                                                |

|        |             |               |               |             |            |                            | I                   | T0_CAP0 — Capture input for Timer 0, channel 0.                                                                                      |

| P3[24] | 58          | R5            | N3            | 40          | [3]        | I;                         | I/O                 | P3[24] — General purpose digital input/output pin.                                                                                   |

|        |             |               |               |             |            | PU                         | I/O                 | EMC_D[24] — External memory data line 24.                                                                                            |

|        |             |               |               |             |            |                            | 0                   | <b>PWM1[1]</b> — Pulse Width Modulator 1, output 1.                                                                                  |

|        |             |               |               |             |            |                            | I                   | T0_CAP1 — Capture input for Timer 0, channel 1.                                                                                      |

28 of 126

### 32-bit ARM Cortex-M3 microcontroller

#### Table 3. Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and <u>Table 7</u> (EMC pins).

| Symbol                     | Pin LQFP208       | Ball TFBGA208                                                          | Ball TFBGA180                                           | Pin LQFP144                              |              | Reset state[1] | Type <sup>[2]</sup> | Description                                                                                                                                                                                                                                                                      |

|----------------------------|-------------------|------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------|--------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

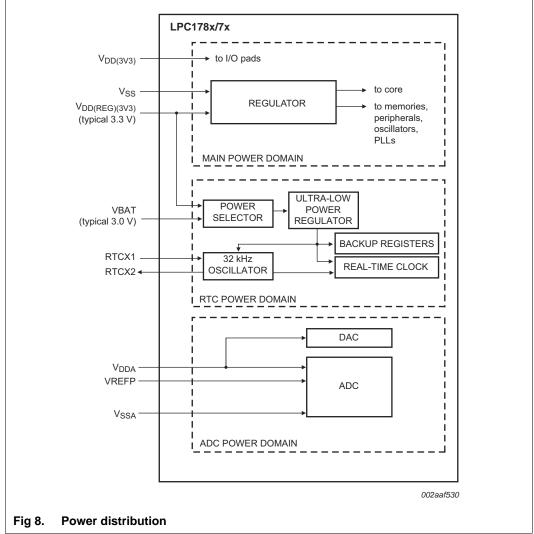

| VBAT                       | 38                | M3                                                                     | K1                                                      | 27                                       |              | -              | I                   | RTC power supply: 3.0 V on this pin supplies power to the RTC.                                                                                                                                                                                                                   |

| V <sub>DD(REG)</sub> (3V3) | 26,<br>86,<br>174 | H4,<br>P11,<br>D11                                                     | G1,<br>N9,<br>E9                                        | 18,<br>60,<br>121                        |              | -              | S                   | 3.3 V regulator supply voltage: This is the power supply for the on-chip voltage regulator that supplies internal logic.                                                                                                                                                         |

| V <sub>DDA</sub>           | 20                | G4                                                                     | F2                                                      | 14                                       |              | -              | S                   | Analog 3.3 V pad supply voltage: This can be connected to the same supply as $V_{DD(3V3)}$ but should be isolated to minimize noise and error. This voltage is used to power the ADC and DAC. Note: This pin should be tied to 3.3 V if the ADC and DAC are not used.            |

| V <sub>DD(3V3)</sub>       | 125,<br>146,      | G3,<br>P6,<br>P8,<br>U13,<br>P17,<br>K16,<br>C17,<br>B13,<br>C9,<br>D7 | E2,<br>L4,<br>K8,<br>L11,<br>J14,<br>E12,<br>E10,<br>C5 | 41,<br>62,<br>77,<br>102,<br>114,<br>138 |              | -              | S                   | 3.3 V supply voltage: This is the power supply voltage for I/O other than pins in the VBAT domain.                                                                                                                                                                               |

| VREFP                      | 24                | К1                                                                     | G2                                                      | 17                                       |              | -              | S                   | ADC positive reference voltage: This should be the same voltage as $V_{DDA}$ , but should be isolated to minimize noise and error. The voltage level on this pin is used as a reference for ADC and DAC. Note: This pin should be tied to 3.3 V if the ADC and DAC are not used. |

| V <sub>SS</sub>            | 133,              | E15,<br>A12,                                                           | H4,<br>P4,<br>L9,<br>L13,<br>G13,<br>D13,<br>C11,<br>B4 | 44,<br>65,<br>79,<br>103,<br>117,<br>139 |              | -              | G                   | Ground: 0 V reference for digital IO pins.                                                                                                                                                                                                                                       |

| V <sub>SSREG</sub>         | 32,<br>84,<br>172 | D12,<br>K4,<br>P10                                                     | H3,<br>L8,<br>A10                                       | 22,<br>59,<br>119                        |              | -              | G                   | Ground: 0 V reference for internal logic.                                                                                                                                                                                                                                        |

| V <sub>SSA</sub>           | 22                | J2                                                                     | F3                                                      | 15                                       |              | -              | G                   | Analog ground: 0 V power supply and reference for the ADC and DAC. This should be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                                                             |

| XTAL1                      | 44                | M4                                                                     | L2                                                      | 31                                       | [14]<br>[16] | -              | I                   | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                                                                                           |

| XTAL2                      | 46                | N4                                                                     | K4                                                      | 33                                       | [14]<br>[16] | -              | 0                   | Output from the oscillator amplifier.                                                                                                                                                                                                                                            |

during a given data transfer. The SSP supports full duplex transfers, with frames of 4 bits to 16 bits of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

### 7.21.1 Features

- Maximum SSP speed of 33 Mbit/s (master) or 10 Mbit/s (slave).

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses.

- Synchronous serial communication.

- Master or slave operation.

- 8-frame FIFOs for both transmit and receive.

- 4-bit to 16-bit frame.

- DMA transfers supported by GPDMA.

### 7.22 I<sup>2</sup>C-bus serial I/O controllers

The LPC178x/7x contain three  $I^2C$ -bus controllers.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock Line (SCL) and a Serial Data Line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

### 7.22.1 Features

- All I<sup>2</sup>C-bus controllers can use standard GPIO pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus). The I<sup>2</sup>C0-bus interface uses special open-drain pins with bit rates of up to 400 kbit/s.

- The I<sup>2</sup>C-bus interface supports Fast-mode Plus with bit rates up to 1 Mbit/s for I2C0 using pins P5[2] and P5[3].

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- Both I<sup>2</sup>C-bus controllers support multiple address recognition and a bus monitor mode.

LPC178X 7X

The alternate PLL accepts an input clock frequency from the main oscillator in the range of 10 MHz to 25 MHz only. When used as the USB clock, the input frequency is multiplied up to a multiple of 48 MHz (192 MHz or 288 MHz as described above).

### 7.33.3 Wake-up timer

The LPC178x/7x begin operation at power-up and when awakened from Power-down mode by using the 12 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the main oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

When the main oscillator is initially activated, the wake-up timer allows software to ensure that the main oscillator is fully functional before the processor uses it as a clock source and starts to execute instructions. This is important at power on, all types of reset, and whenever any of the aforementioned functions are turned off for any reason. Since the oscillator and other functions are turned off during Power-down mode, any wake-up of the processor from Power-down mode makes use of the wake-up Timer.

The wake-up timer monitors the crystal oscillator to check whether it is safe to begin code execution. When power is applied to the chip, or when some event caused the chip to exit Power-down mode, some time is required for the oscillator to produce a signal of sufficient amplitude to drive the clock logic. The amount of time depends on many factors, including the rate of  $V_{DD(3V3)}$  ramp (in the case of power on), the type of crystal and its electrical characteristics (if a quartz crystal is used), as well as any other external circuitry (e.g., capacitors), and the characteristics of the oscillator itself under the existing ambient conditions.

### 7.33.4 Power control

The LPC178x/7x support a variety of power control features. There are four special modes of processor power reduction: Sleep mode, Deep-sleep mode, Power-down mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, the peripheral power control allows shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Each of the peripherals has its own clock divider which provides even better power control.

The integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep-sleep, Power-down, and Deep power-down modes.

The LPC178x/7x also implement a separate power domain to allow turning off power to the bulk of the device while maintaining operation of the RTC and a small set of registers for storing data during any of the power-down modes.

#### 7.33.4.1 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence other than re-enabling the clock to the ARM core.

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(REG)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

The second option uses two power supplies; a 3.3 V supply for the I/O pads ( $V_{DD(3V3)}$ ) and a dedicated 3.3 V supply for the CPU ( $V_{DD(REG)(3V3)}$ ). Having the on-chip voltage regulator powered independently from the I/O pad ring enables shutting down of the I/O pad power supply "on the fly" while the CPU and peripherals stay active.

The VBAT pin supplies power only to the RTC domain. The RTC operates at very low power, which can be supplied by an external battery. The device core power ( $V_{DD(REG)(3V3)}$ ) is used to operate the RTC whenever  $V_{DD(REG)(3V3)}$  is present. There is no power drain from the RTC battery when  $V_{DD(REG)(3V3)}$  is at nominal levels and  $V_{DD(REG)(3V3)} > V_{BAT}$ .

### 32-bit ARM Cortex-M3 microcontroller

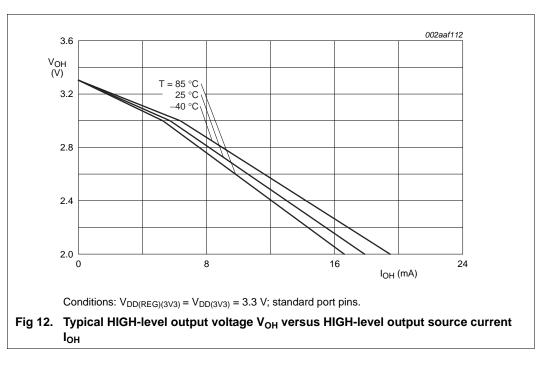

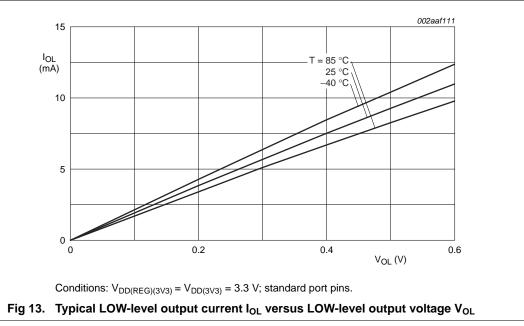

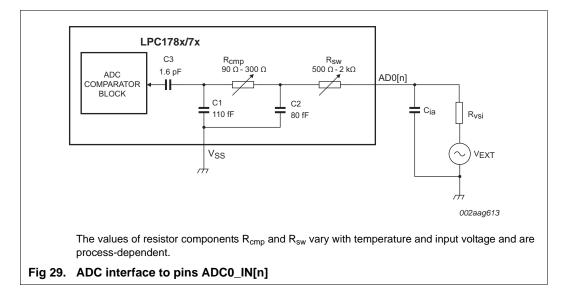

# 10.3 Electrical pin characteristics

#### 32-bit ARM Cortex-M3 microcontroller

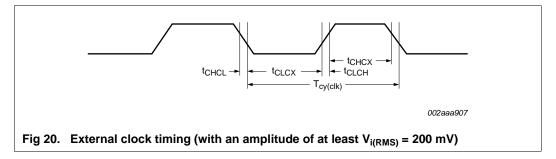

## 11.3 External clock

#### Table 23. Dynamic characteristic: external clock (see Figure 36)

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; V_{DD(3V3)} \text{ over specified ranges.}$

| Symbol               | Parameter            | Min                     | Тур  | Max  | Unit |

|----------------------|----------------------|-------------------------|------|------|------|

| f <sub>osc</sub>     | oscillator frequency | 1                       | 12   | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     | 40                      | 83.3 | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      | $T_{cy(clk)} 	imes 0.4$ | -    | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       | $T_{cy(clk)} 	imes 0.4$ | -    | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      | -                       | -    | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      | -                       | -    | 5    | ns   |

### 11.4 Internal oscillators

#### Table 24. Dynamic characteristic: internal oscillators

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}.[1]$

| Symbol               | Parameter                        | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|----------------------------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | 11.88 | 12             | 12.12 | MHz  |

| f <sub>i(RTC)</sub>  | RTC input frequency              | -     | 32.768         | -     | kHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

## 11.5 I/O pins

#### Table 25. Dynamic characteristic: I/O pins<sup>[1]</sup>

$C_L = 10 \text{ pF}, T_{amb} = -40 \text{ °C to } +85 \text{ °C}; V_{DD(3V3)} = 3.0 \text{ V to } 3.6 \text{ V}.$

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |