Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                    |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | SCI                                                                        |

| Peripherals                | LCD, PWM, WDT                                                              |

| Number of I/O              | 55                                                                         |

| Program Memory Size        | 60KB (60K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38327wv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ltem                                                                                                                                        | Page | Revision (                                                                                                                                                       | See Ma                         | nual for                     | r Details                    | 5)                               |                              |             |            |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|------------------------------|----------------------------------|------------------------------|-------------|------------|

| 8.3.4 Pin States                                                                                                                            | 211  | Table and                                                                                                                                                        | notes ar                       | nended                       |                              |                                  |                              |             |            |

| Table 8.7 Port 3 Pin                                                                                                                        |      | Pins                                                                                                                                                             | Reset                          | Sleep                        | Subsleep                     | Standby                          | Watch                        | Subactive   | Active     |

| States                                                                                                                                      |      | P3 <sub>7</sub> /AEVL<br>P3 <sub>6</sub> /AEVH<br>P3 <sub>5</sub> /TXD <sub>31</sub><br>P3 <sub>4</sub> /RXD <sub>31</sub><br>P3 <sub>9</sub> /SCK <sub>31</sub> | High-<br>impedance             | Retains<br>previous<br>state | Retains<br>previous<br>state | High-<br>impedance <sup>*1</sup> | Retains<br>previous<br>state | Functional  | Functional |

|                                                                                                                                             |      | P3 <sub>2</sub> /RESO <sup>*2</sup>                                                                                                                              | RESO<br>output                 | -                            |                              |                                  |                              |             |            |

|                                                                                                                                             |      | P32*4                                                                                                                                                            | Pull-up<br>MOS on              | _                            |                              |                                  |                              |             |            |

|                                                                                                                                             |      | P32 <sup>*3</sup><br>P31/UD <sup>*2</sup><br>P31/UD/EXCL <sup>*3*4</sup><br>P30/PWM                                                                              | High-<br>impedance             | _                            |                              |                                  |                              |             |            |

|                                                                                                                                             |      | 3. Appl                                                                                                                                                          | lies to H8/38<br>lies to the m | 27R Group<br>ask ROM ve      | and H8/382<br>ersion of the  | • •                              | roup and H                   | 18/38427 Gr |            |

| 8.12.1 The                                                                                                                                  | 236  | Description                                                                                                                                                      | amend                          | ed                           |                              |                                  |                              |             |            |

| Management of the<br>Un-Use Terminal                                                                                                        |      | If an unused pin is an output pin, handle it in one of the                                                                                                       |                                |                              |                              |                                  |                              |             | ;          |

|                                                                                                                                             |      |                                                                                                                                                                  | g ways:                        |                              |                              |                                  |                              |             |            |

|                                                                                                                                             |      | <ul> <li>Set the output of the unused pin to high and pull it up to<br/>Vcc with an external resistor of approximately 100 kΩ.</li> </ul>                        |                                |                              |                              |                                  |                              |             |            |

|                                                                                                                                             |      | — Set                                                                                                                                                            | the outp                       | out of th                    | e unuse                      | d pin to l<br>or of appi         | ow and                       | pull it d   | own to     |

| C.2 Block Diagrams<br>of Port 3                                                                                                             | 593  | Figure title                                                                                                                                                     | amende                         | ed                           |                              |                                  |                              |             | <u> </u>   |

| Figure C.2 (e-2)<br>Port 3 Block Diagram<br>(Pin P3 <sub>2</sub> in the Mask<br>ROM Version of the<br>H8/38327 Group and<br>H8/38427 Group) |      |                                                                                                                                                                  |                                |                              |                              |                                  |                              |             |            |

| Figure C.2 (e-3)<br>Port 3 Block Diagram<br>(Pin P $_2$ in the F-ZTAT<br>Version of the<br>H8/38327 Group and<br>H8/38427 Group)            | 594  | Newly add                                                                                                                                                        | ed                             |                              |                              |                                  |                              |             |            |

Rev. 6.00 Aug 04, 2006 page viii of xxxiv

| Secti            | on 5    | Power-Down Modes                                                      | 121      |

|------------------|---------|-----------------------------------------------------------------------|----------|

| 5.1              |         | ew                                                                    |          |

|                  | 5.1.1   | System Control Registers                                              | 124      |

| 5.2              | Sleep I | Mode                                                                  | 128      |

|                  | 5.2.1   | Transition to Sleep Mode                                              | 128      |

|                  | 5.2.2   | Clearing Sleep Mode                                                   | 129      |

|                  | 5.2.3   | Clock Frequency in Sleep (Medium-Speed) Mode                          | 129      |

| 5.3              | Standb  | by Mode                                                               | 129      |

|                  | 5.3.1   | Transition to Standby Mode                                            | 129      |

|                  | 5.3.2   | Clearing Standby Mode                                                 | 130      |

|                  | 5.3.3   | Oscillator Settling Time after Standby Mode is Cleared                | 131      |

|                  | 5.3.4   | Standby Mode Transition and Pin States                                | 131      |

|                  | 5.3.5   | Notes on External Input Signal Changes before/after Standby Mode      | 132      |

| 5.4              | Watch   | Mode                                                                  | 134      |

|                  | 5.4.1   | Transition to Watch Mode                                              | 134      |

|                  | 5.4.2   | Clearing Watch Mode                                                   | 134      |

|                  | 5.4.3   | Oscillator Settling Time after Watch Mode is Cleared                  | 134      |

|                  | 5.4.4   | Notes on External Input Signal Changes before/after Watch Mode        | 135      |

| 5.5              | Subsle  | ep Mode                                                               | 135      |

|                  | 5.5.1   | Transition to Subsleep Mode                                           | 135      |

|                  | 5.5.2   | Clearing Subsleep Mode                                                | 135      |

| 5.6              | Subact  | ive Mode                                                              | 136      |

|                  | 5.6.1   | Transition to Subactive Mode                                          | 136      |

|                  | 5.6.2   | Clearing Subactive Mode                                               | 136      |

|                  | 5.6.3   | Operating Frequency in Subactive Mode                                 | 136      |

| 5.7              | Active  | (Medium-Speed) Mode                                                   | 137      |

|                  | 5.7.1   | Transition to Active (Medium-Speed) Mode                              | 137      |

|                  | 5.7.2   | Clearing Active (Medium-Speed) Mode                                   | 137      |

|                  | 5.7.3   | Operating Frequency in Active (Medium-Speed) Mode                     | 137      |

| 5.8              | Direct  | Transfer                                                              | 138      |

|                  | 5.8.1   | Overview of Direct Transfer                                           | 138      |

|                  | 5.8.2   | Direct Transition Times                                               | 139      |

|                  | 5.8.3   | Notes on External Input Signal Changes before/after Direct Transition |          |

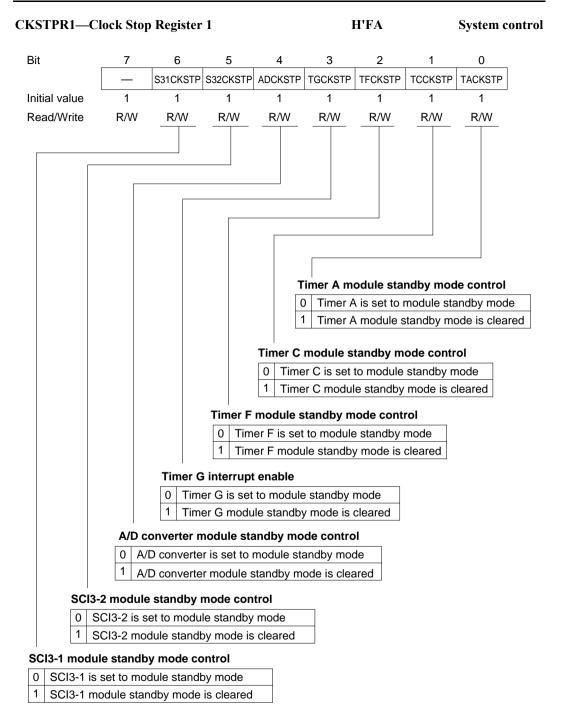

| 5.9              | Modul   | e Standby Mode                                                        | 142      |

|                  | 5.9.1   | Setting Module Standby Mode                                           | 142      |

|                  | 5.9.2   | Clearing Module Standby Mode                                          | 142      |

|                  | 5.9.3   | Usage Note                                                            | 144      |

| а . <sup>.</sup> | ~       |                                                                       | <b>.</b> |

|                  |         | ROM                                                                   |          |

| 6.1              | Overvi  | ew                                                                    | 145      |

Rev. 6.00 Aug 04, 2006 page xiii of xxxiv

### 2.5.5 Bit Manipulations

Table 2.8 describes the bit-manipulation instructions. Figure 2.7 shows their object code formats.

| Table 2.8Bit-Manipulation Instructions |

|----------------------------------------|

|----------------------------------------|

| Instruction | Size* | Function                                                                                                                                                                                            |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSET        | В     | $1 \rightarrow (\text{sbit-No.} \text{ of } \text{scale})$                                                                                                                                          |

|             |       | Sets a specified bit in a general register or memory to 1. The bit number is specified by 3-bit immediate data or the lower three bits of a general register.                                       |

| BCLR        | В     | $0 \rightarrow (\text{sbit-No.> of })$                                                                                                                                                              |

|             |       | Clears a specified bit in a general register or memory to 0. The bit number is specified by 3-bit immediate data or the lower three bits of a general register.                                     |

| BNOT        | В     | ~ ( <bit-no.> of <ead>) <math>\rightarrow</math> (<bit-no.> of <ead>)</ead></bit-no.></ead></bit-no.>                                                                                               |

|             |       | Inverts a specified bit in a general register or memory. The bit<br>number is specified by 3-bit immediate data or the lower three bits<br>of a general register.                                   |

| BTST        | В     | ~ ( <bit-no.> of <ead>) <math>\rightarrow</math> Z</ead></bit-no.>                                                                                                                                  |

|             |       | Tests a specified bit in a general register or memory and sets or clears the Z flag accordingly. The bit number is specified by 3-bit immediate data or the lower three bits of a general register. |

| BAND        | В     | $C \land (<\!bit-No.\!> of <\!EAd\!>) \rightarrow C$                                                                                                                                                |

|             |       | ANDs the C flag with a specified bit in a general register or memory, and stores the result in the C flag.                                                                                          |

| BIAND       | В     | $C \land [\text{~( of )}] \to C$                                                                                                                                                                    |

|             |       | ANDs the C flag with the inverse of a specified bit in a general register or memory, and stores the result in the C flag.                                                                           |

|             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                |

| BOR         | В     | $C \lor ( of ) \to C$                                                                                                                                                                               |

|             |       | ORs the C flag with a specified bit in a general register or memory, and stores the result in the C flag.                                                                                           |

| BIOR        | В     | $C \lor [\sim (<\!bit-No.\!> of <\!EAd\!>)] \to C$                                                                                                                                                  |

|             |       | ORs the C flag with the inverse of a specified bit in a general register or memory, and stores the result in the C flag.                                                                            |

|             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                |

| Instruction             | Size*              | Function                                                                                                                  |

|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| BXOR                    | В                  | $C \oplus (<\!bit-\!No.\!> of <\!\mathsf{EAd\!\!>) \!\rightarrow C}$                                                      |

|                         |                    | XORs the C flag with a specified bit in a general register or<br>memory, and stores the result in the C flag.             |

| BIXOR                   | В                  | $C \oplus \ [\text{-( of )]} \rightarrow C$                                                                               |

|                         |                    | XORs the C flag with the inverse of a specified bit in a general register or memory, and stores the result in the C flag. |

|                         |                    | The bit number is specified by 3-bit immediate data.                                                                      |

| BLD                     | В                  | ( <bit-no.> of <ead>) <math>\rightarrow</math> C</ead></bit-no.>                                                          |

|                         |                    | Copies a specified bit in a general register or memory to the C flag.                                                     |

| BILD                    | В                  | ~ ( <bit-no.> of <ead>) <math>\rightarrow</math> C</ead></bit-no.>                                                        |

|                         |                    | Copies the inverse of a specified bit in a general register or<br>memory to the C flag.                                   |

|                         |                    | The bit number is specified by 3-bit immediate data.                                                                      |

| BST                     | В                  | $C \rightarrow (\text{sbit-No.> of } \text{})$                                                                            |

|                         |                    | Copies the C flag to a specified bit in a general register or memory.                                                     |

| BIST                    | В                  | ~ C $\rightarrow$ ( <bit-no.> of <ead>)</ead></bit-no.>                                                                   |

|                         |                    | Copies the inverse of the C flag to a specified bit in a general register or memory.                                      |

|                         |                    | The bit number is specified by 3-bit immediate data.                                                                      |

| Note: * Size<br>B: Byte | e: Operand si<br>e | ze                                                                                                                        |

Certain precautions are required in bit manipulation. See section 2.9.2, Notes on Bit Manipulation, for details.

### 5. Port Mode Register 2 (PMR2)

| Bit           | 7    | 6 | 5   | 4 | 3 | 2   | 1   | 0   | _ |

|---------------|------|---|-----|---|---|-----|-----|-----|---|

|               | EXCL | — | —   | _ | _ | _   | _   | _   |   |

| Initial value | 0    | 1 | 0   | 1 | 1 | 0   | 0   | 0   | - |

| Read/Write    | R/W  | R | R/W | R | R | R/W | R/W | R/W |   |

PMR2 is an 8-bit read/write register that controls external clock input to pin P31.

Upon reset, PMR2 is initialized to H'58. The information on this register applies to the H8/38327 Group and H8/38427 Group.

**Bit 7:** P3<sub>1</sub>/UD/EXCL pin function switch (EXCL)

This bit selects whether pin  $P3_1/UD/EXCL$  is used as  $P3_1/UD$  or as EXCL. When the pin is used as EXCL an external clock should be input to it. See section 4, Clock Pulse Generators, for a connection example.

| Bit 7 | <b>-</b>                                 |                 |

|-------|------------------------------------------|-----------------|

| EXCL  | Description                              |                 |

| 0     | Functions as P3 <sub>1</sub> /UD I/O pin | (initial value) |

| 1     | Functions as EXCL input pin              |                 |

Bit 6: Reserved bit

Bit 6 is a reserved bit. It is always read as 1 and cannot be modified.

Bit 5: Reserved bit

Bit 5 is a readable/writable reserved bit.

### Bits 4 and 3: Reserved bits

Bits 4 and 3 are reserved bits. They are always read as 1 and cannot be modified.

Bits 2 to 0: Reserved bits

Bits 2 to 0 are readable/writable reserved bits.

#### **Bit 5:** Parity enable (PE)

Bit 5 selects whether a parity bit is to be added during transmission and checked during reception in asynchronous mode. In synchronous mode parity bit addition and checking is not performed, irrespective of the bit 5 setting.

| Bit 5     |                                                                                                                                                                          |                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| PE        | Description                                                                                                                                                              |                 |

| 0         | Parity bit addition and checking disabled <sup>*2</sup>                                                                                                                  | (initial value) |

| 1         | Parity bit addition and checking enabled <sup>*1*2</sup>                                                                                                                 |                 |

| Notes: 1. | . When PE is set to 1, even or odd parity, as designated by bit PM, is a data before it is sent, and the received parity bit is checked against th designated by bit PM. |                 |

| 2.        | . For the case where 5-bit data is selected, see table 10.11.                                                                                                            |                 |

Bit 4: Parity mode (PM)

Bit 4 selects whether even or odd parity is to be used for parity addition and checking. The PM bit setting is only valid in asynchronous mode when bit PE is set to 1, enabling parity bit addition and checking. The PM bit setting is invalid in synchronous mode, and in asynchronous mode if parity bit addition and checking is disabled.

| Bit 4    |                                                                                                                                                                                                                                                                                                                        |            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| РМ       | Description                                                                                                                                                                                                                                                                                                            |            |

| 0        | Even parity <sup>*1</sup> (initi                                                                                                                                                                                                                                                                                       | ial value) |

| 1        | Odd parity <sup>*2</sup>                                                                                                                                                                                                                                                                                               |            |

| Notes: 7 | <ol> <li>When even parity is selected, a parity bit is added in transmission so that the to<br/>number of 1 bits in the transmit data plus the parity bit is an even number; in re<br/>a check is carried out to confirm that the number of 1 bits in the receive data pl<br/>parity bit is an even number.</li> </ol> | eception,  |

| 2        | 2. When odd parity is selected, a parity bit is added in transmission so that the tot                                                                                                                                                                                                                                  | tal        |

2. When odd parity is selected, a parity bit is added in transmission so that the total number of 1 bits in the transmit data plus the parity bit is an odd number; in reception, a check is carried out to confirm that the number of 1 bits in the receive data plus the parity bit is an odd number.

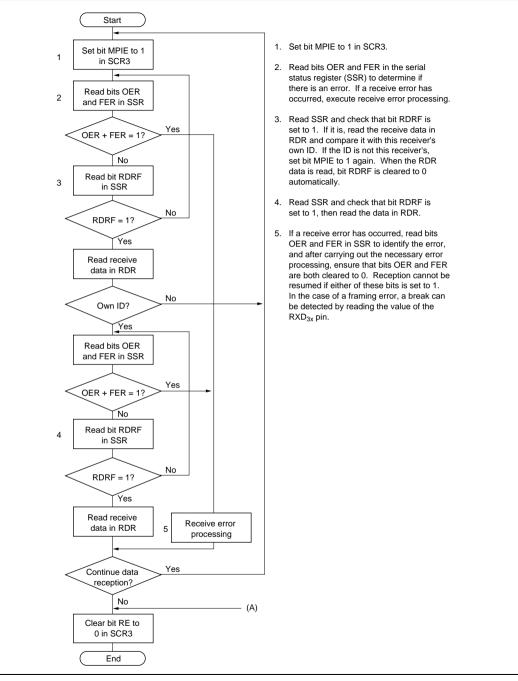

#### Figure 10.19 Example of Multiprocessor Data Reception Flowchart

Bit 7: Clock select (CKS)

Bit 7 sets the A/D conversion speed.

| φ = 5 MHz |

|-----------|

| 12.4 µs   |

| _         |

|           |

Note: \* For information on conversion time settings for which operation is guaranteed, see section 15, Electrical Characteristics.

Bit 6: External trigger select (TRGE)

Bit 6 enables or disables the start of A/D conversion by external trigger input.

| Bit 6<br>TRGE |   | Description                                                                                                                             |

|---------------|---|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0             |   | Disables start of A/D conversion by external trigger (initial value)                                                                    |

| 1             |   | Enables start of A/D conversion by rising or falling edge of external trigger at pin ADTRG*                                             |

| Note:         | * | The external trigger (ADTRG) edge is selected by bit IEG4 of IEGR. See 1. IRQ edge select register (IEGR) in section 3.3.2 for details. |

Bits 5 and 4: Reserved bits

Bits 5 and 4 are reserved; they are always read as 1, and cannot be modified.

Bits 3 to 0: Channel select (CH3 to CH0)

Bits 3 to 0 select the analog input channel.

The channel selection should be made while bit ADSF is cleared to 0.

Bit 4: Expansion signal select (SGX)

Bit 4 selects whether the SEG<sub>32</sub>/CL<sub>1</sub>, SEG<sub>31</sub>/CL<sub>2</sub>, SEG<sub>30</sub>/DO, and SEG<sub>29</sub>/M pins are used as segment pins (SEG<sub>32</sub> to SEG<sub>29</sub>) or as segment external expansion pins (CL<sub>1</sub>, CL<sub>2</sub>, DO, and M).

In the H8/38327 Group and H8/38427 Group this bit should be left at its initial value and not written to. Changing the value of this bit may prevent the SEG/COM signal from operating normally.

| Bit 4<br>SGX |   | Description                                    |                                                 |

|--------------|---|------------------------------------------------|-------------------------------------------------|

| 0            |   | Pins SEG <sub>32</sub> to SEG <sub>29</sub> *  | (initial value)                                 |

| 1            |   | Pins CL <sub>1</sub> , CL <sub>2</sub> , DO, M |                                                 |

| Note:        | * | These pins function as ports whe               | en the setting of SGS3 to SGS0 is 0000 or 0001. |

Bits 3 to 0: Segment driver select 3 to 0 (SGS3 to SGS0)

Bits 3 to 0 select the segment drivers to be used. The SGX = 0 setting is selected on the H8/38327 and H8/38427.

|              |               |               |               |               | i uni                                     |                                           |                                          |                                         |                 |

|--------------|---------------|---------------|---------------|---------------|-------------------------------------------|-------------------------------------------|------------------------------------------|-----------------------------------------|-----------------|

| Bit 4<br>SGX | Bit 3<br>SGS3 | Bit 2<br>SGS2 | Bit 1<br>SGS1 | Bit 0<br>SGS0 | SEG <sub>32</sub> to<br>SEG <sub>25</sub> | SEG <sub>24</sub> to<br>SEG <sub>17</sub> | SEG <sub>16</sub> to<br>SEG <sub>9</sub> | SEG <sub>8</sub> to<br>SEG <sub>1</sub> | Notes           |

| 0            | 0             | 0             | 0             | 0             | Port                                      | Port                                      | Port                                     | Port                                    | (initial value) |

|              | 0             | 0             | 0             | 1             | Port                                      | Port                                      | Port                                     | Port                                    |                 |

|              | 0             | 0             | 1             | *             | SEG                                       | Port                                      | Port                                     | Port                                    |                 |

|              | 0             | 1             | 0             | *             | SEG                                       | SEG                                       | Port                                     | Port                                    |                 |

|              | 0             | 1             | 1             | *             | SEG                                       | SEG                                       | SEG                                      | Port                                    |                 |

|              | 1             | *             | *             | *             | SEG                                       | SEG                                       | SEG                                      | SEG                                     |                 |

| 1            | 0             | 0             | 0             | 0             | Port <sup>*1</sup>                        | Port                                      | Port                                     | Port                                    |                 |

|              | *             | *             | *             | *             | Setting pro                               | ohibited                                  |                                          |                                         |                 |

| -            |               |               |               |               |                                           |                                           |                                          |                                         |                 |

#### Function of Pins SEG<sub>32</sub> to SEG<sub>1</sub>

\*: Don't care

Note: 1. SEG<sub>32</sub> to SEG<sub>29</sub> are external expansion pins.

# Renesas

|                                   |                  | Applicable                      |     | Values               | 5    |                  |                                  | Reference         |

|-----------------------------------|------------------|---------------------------------|-----|----------------------|------|------------------|----------------------------------|-------------------|

| Item                              | Symbol           |                                 | Min | Тур                  | Мах  | Unit             | Test Condition                   | Figure            |

| Oscillation<br>stabilization time | t <sub>rc</sub>  | X <sub>1</sub> , X <sub>2</sub> | _   | _                    | 2.0  | S                |                                  |                   |

| External clock high width         | t <sub>CPH</sub> | OSC <sub>1</sub>                | 25  | _                    | _    | ns               | $V_{CC}$ = 4.5 V to 5.5 V        | Figure 15.1<br>*2 |

|                                   |                  |                                 | 40  | _                    | _    | _                | V <sub>CC</sub> = 2.7 V to 5.5 V | Figure 15.1       |

|                                   |                  |                                 | 100 | _                    | _    | _                | V <sub>CC</sub> = 1.8 V to 5.5 V | _                 |

|                                   |                  | X <sub>1</sub>                  | _   | 15.26<br>or<br>13.02 | —    | μs               |                                  | -                 |

| External clock low width          | t <sub>CPL</sub> | OSC <sub>1</sub>                | 25  | _                    | _    | ns               | $V_{\rm CC}$ = 4.5 V to 5.5 V    | Figure 15.1<br>*2 |

|                                   |                  |                                 | 40  |                      | _    | _                | V <sub>CC</sub> = 2.7 V to 5.5 V | Figure 15.1       |

|                                   |                  |                                 | 100 | _                    | _    | _                | $V_{\rm CC}$ = 1.8 V to 5.5 V    | -                 |

|                                   |                  | X <sub>1</sub>                  | _   | 15.26<br>or<br>13.02 | _    | μs               |                                  | -                 |

| External clock rise time          | t <sub>CPr</sub> | OSC <sub>1</sub>                | _   | _                    | 6    | ns               | $V_{\rm CC}$ = 4.5 V to 5.5 V    | Figure 15.1<br>*2 |

|                                   |                  |                                 | _   |                      | 10   | _                | V <sub>CC</sub> = 2.7 V to 5.5 V | Figure 15.1       |

|                                   |                  |                                 | _   |                      | 25   | _                | V <sub>CC</sub> = 1.8 V to 5.5 V | -                 |

|                                   |                  | X <sub>1</sub>                  | _   |                      | 55.0 | ns               |                                  | -                 |

| External clock fall time          | t <sub>CPf</sub> | OSC <sub>1</sub>                | _   | _                    | 6    | ns               | $V_{\rm CC}$ = 4.5 V to 5.5 V    | Figure 15.1<br>*2 |

|                                   |                  |                                 | _   | _                    | 10   | _                | V <sub>CC</sub> = 2.7 V to 5.5 V | Figure 15.1       |

|                                   |                  |                                 | _   | _                    | 25   | _                | V <sub>CC</sub> = 1.8 V to 5.5 V | _                 |

|                                   |                  | X <sub>1</sub>                  | _   | _                    | 55.0 | ns               |                                  | -                 |

| $Pin\ \overline{RES}\ low\ width$ | t <sub>REL</sub> | RES                             | 10  | _                    | _    | t <sub>cyc</sub> |                                  | Figure 15.2       |

### 15.5 H8/3827S Group Absolute Maximum Ratings

Table 15.15 lists the absolute maximum ratings.

| Table 15.15 A | bsolute Maximum | Ratings |

|---------------|-----------------|---------|

|---------------|-----------------|---------|

| ltem                                  |                               | Symbol           | Value                                         | Unit | Notes |

|---------------------------------------|-------------------------------|------------------|-----------------------------------------------|------|-------|

| Power supply vo                       | Itage                         | V <sub>CC</sub>  | –0.3 to +4.3                                  | V    | *1    |

| Analog power su                       | ipply voltage                 | AV <sub>CC</sub> | –0.3 to +4.3                                  | V    |       |

| Input voltage Ports other than Port B |                               | V <sub>in</sub>  | –0.3 to V <sub>CC</sub> +0.3                  | V    |       |

|                                       | –0.3 to AV <sub>CC</sub> +0.3 | V                |                                               |      |       |

| Operating tempe                       | erature                       | T <sub>opr</sub> | –20 to +75 (Regular specifications)           | °C   |       |

|                                       |                               |                  | -40 to +85 (wide-range specifications)        | -    |       |

|                                       |                               |                  | +75 (products shipped as chips) <sup>*2</sup> |      |       |

| Storage tempera                       | iture                         | T <sub>stg</sub> | –55 to +125                                   | °C   |       |

Notes: 1. Permanent damage may occur to the chip if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

2. Power may be applied when the temperature is between –20 and –75°C.

# Renesas

|                                              |                    |                 |     | Value | S   |      |                                                               |                                                      |

|----------------------------------------------|--------------------|-----------------|-----|-------|-----|------|---------------------------------------------------------------|------------------------------------------------------|

| ltem                                         | Symbol             | Applicable Pins | Min | Тур   | Мах | Unit | <b>Test Condition</b>                                         | Notes                                                |

| Sleep<br>mode<br>current<br>consump-<br>tion | I <sub>SLEEP</sub> | V <sub>CC</sub> | _   | 0.5   | _   | mA   | V <sub>CC</sub> = 2.7 V,<br>f <sub>OSC</sub> = 2 MHz          | *1 *3 *4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ. |

|                                              |                    |                 | _   | 0.8   | _   |      |                                                               | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      |                                                               | Approx.<br>max. value<br>= 1.1 ×<br>Typ.             |

|                                              |                    |                 | _   | 0.7   | _   |      | V <sub>CC</sub> = 5 V,                                        | *1 *3 *4                                             |

|                                              |                    |                 |     |       |     |      | f <sub>OSC</sub> = 2 MHz                                      | Approx.<br>max. value<br>= 1.1 ×<br>Typ.             |

|                                              |                    |                 | —   | 1.2   | —   |      |                                                               | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      |                                                               | Approx.<br>max. value<br>= 1.1 ×<br>Typ.             |

|                                              |                    |                 | _   | 1.1   | _   |      | V <sub>CC</sub> = 5 V,<br>f <sub>OSC</sub> = 4 MHz            | *1*3*4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ.   |

|                                              |                    |                 | _   | 1.6   | _   |      |                                                               | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      |                                                               |                                                      |

|                                              |                    |                 | _   | 1.9   | 5.0 |      | V <sub>CC</sub> = 5 V,                                        | *1 *3 *4                                             |

|                                              |                    |                 | —   | 2.6   | 5.0 |      | f <sub>OSC</sub> = 10 MHz                                     | *2 *3 *4                                             |

| Subactive                                    | leun               | V <sub>CC</sub> | _   | 12    | _   | μA   | V <sub>CC</sub> = 2.7 V,                                      | *1 *3 *4                                             |

| mode<br>current                              | 1308               | •00             |     | 12    |     | μ, τ | LCD on,<br>32-kHz crystal                                     | Reference<br>value                                   |

| consump-<br>tion                             |                    |                 | _   | 15    | _   |      | resonator used<br>(φ <sub>SUB</sub> = φ <sub>W</sub> /8)      | *2 *3 *4<br>Reference<br>value                       |

|                                              |                    |                 | _   | 18    | 50  |      | V <sub>CC</sub> = 2.7 V,                                      | *1 *3 *4                                             |

|                                              |                    |                 | _   | 30    | 50  | _    | LCD on,                                                       | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      | 32-kHz crystal<br>resonator used<br>$(\phi_{SUB} = \phi_W/2)$ |                                                      |

### 15.8.3 AC Characteristics

Table 15.24 lists the control signal timing and table 15.25 lists the serial interface timing.

### Table 15.24 Control Signal Timing

$V_{CC} = 2.7 \text{ V}$  to 5.5 V,  $AV_{CC} = 2.7 \text{ V}$  to 5.5 V,  $V_{SS} = AV_{SS} = 0.0 \text{ V}$ , unless otherwise specified

|                                         |                     | Applicable                                |             | Values            | 6             |                                         |                                                              | Reference                       |  |

|-----------------------------------------|---------------------|-------------------------------------------|-------------|-------------------|---------------|-----------------------------------------|--------------------------------------------------------------|---------------------------------|--|

| Item                                    | Symbol              | Pins                                      | Min Typ Max |                   | Unit          | Test Condition                          | Figure                                                       |                                 |  |

| System clock                            | fosc                | OSC <sub>1</sub> ,                        | 2.0         | _                 | 16.0          | MHz                                     |                                                              | *3                              |  |

| oscillation<br>frequency                |                     | OSC <sub>2</sub>                          | 2.0         | _                 | 16.0          | _                                       | $V_{CC}$ = 4.5 to 5.5 V                                      | *4                              |  |

| nequency                                |                     |                                           | 2.0         | _                 | 10.0          | _                                       | $V_{CC}$ = 2.7 to 5.5 V                                      | -                               |  |

| OSC clock ( $\phi_{OSC}$ ) cycle time   | t <sub>osc</sub>    | OSC <sub>1</sub> ,<br>OSC <sub>2</sub>    | 62.5        | _                 | 500<br>(1000) | ns                                      |                                                              | Figure<br>15.1 <sup>*2 *3</sup> |  |

|                                         |                     |                                           | 62.5        | _                 | 500<br>(1000) | _                                       | $V_{\rm CC}$ = 4.5 to 5.5 V                                  | Figure<br>15.1 <sup>*2 *4</sup> |  |

|                                         |                     |                                           | 100         | _                 | 500<br>(1000) | _                                       | $V_{\rm CC}$ = 2.7 to 5.5 V                                  | -                               |  |

| System clock (                          | t <sub>cyc</sub>    |                                           | 2           | _                 | 128           | tosc                                    |                                                              |                                 |  |

| cycle time                              |                     |                                           | _           | _                 | 128           | μs                                      | -                                                            |                                 |  |

| Subclock oscillation<br>frequency       | f₩                  | X <sub>1</sub> , X <sub>2</sub> ,<br>EXCL | _           | 32.768<br>or 38.4 | _             | kHz                                     |                                                              |                                 |  |

| Watch clock ( $\phi_W$ ) cycle time     | tw                  | X <sub>1</sub> , X <sub>2</sub> ,<br>EXCL | _           | 30.5 or<br>26.0   | _             | μs                                      |                                                              | Figure<br>15.1                  |  |

| Subclock ( $\phi_{SUB}$ )<br>cycle time | t <sub>subcyc</sub> |                                           | 2           | —                 | 4             | tw                                      |                                                              | *1                              |  |

| Instruction cycle time                  |                     |                                           | 2           | —                 | —             | t <sub>cyc</sub><br>t <sub>subcyc</sub> |                                                              |                                 |  |

| Oscillation stabilization time          | t <sub>rc</sub>     | OSC <sub>1</sub> ,<br>OSC <sub>2</sub>    | —           | 20                | 45            | μs                                      | Ceramic resonator $(V_{CC} = 3.0 \text{ to } 5.5 \text{ V})$ | Figure<br>15.10                 |  |

|                                         |                     |                                           | —           | 80                | —             | _                                       | Ceramic resonator other than above                           | _                               |  |

|                                         |                     |                                           | _           | 0.8               | 2             | ms                                      | Crystal resonator                                            | -                               |  |

|                                         |                     |                                           | _           | —                 | 50            | _                                       | Other than above                                             |                                 |  |

|                                         | t <sub>rc</sub>     | X <sub>1</sub> , X <sub>2</sub>           |             | _                 | 2.0           | S                                       |                                                              |                                 |  |

|                    |              | perand Size<br>cx: 8/16                                                                         |   |    |     |             | sing<br>Ler |           |            |       | s)     |   |   |   |    |     |                   |               |

|--------------------|--------------|-------------------------------------------------------------------------------------------------|---|----|-----|-------------|-------------|-----------|------------|-------|--------|---|---|---|----|-----|-------------------|---------------|

|                    | Operand Size |                                                                                                 |   | c  | @Rn | @(d:16, Rn) | @-Rn/@Rn+   | @aa: 8/16 | @(d:8, PC) | ) @aa | mplied | - |   |   |    | Cod |                   | No. of States |

| Mnemonic           | -            | Operation                                                                                       | # | Rn | ø   | ø           | ø           | ø         | ø          | 0     | 5      | I | н | Ν | Z  | ۷   | С                 |               |

| BTST #xx:3, Rd     | В            | $(\#xx:3 \text{ of } Rd8) \rightarrow Z$                                                        |   | 2  |     |             |             |           |            |       |        | - | - | _ | \$ | _   | -                 | 2             |

| BTST #xx:3, @Rd    | В            | $(\overline{\texttt{#xx:3 of @Rd16}}) \rightarrow Z$                                            |   |    | 4   |             |             |           |            |       |        | - | - | — | \$ | _   | -                 | 6             |

| BTST #xx:3, @aa:8  | В            | $(\#xx:3 \text{ of } @aa:8) \rightarrow Z$                                                      |   |    |     |             |             | 4         |            |       |        | _ | — | _ | \$ | _   | —                 | 6             |

| BTST Rn, Rd        | В            | (Rn8 of Rd8) $\rightarrow$ Z                                                                    |   | 2  |     |             |             |           |            |       |        | - | - | — | ↕  | _   |                   | 2             |

| BTST Rn, @Rd       | В            | $(\overline{\text{Rn8 of } @\text{Rd16}}) \rightarrow \text{Z}$                                 |   |    | 4   |             |             |           |            |       |        | _ | _ | _ | ↕  | _   | _                 | 6             |

| BTST Rn, @aa:8     | В            | $(\overline{\text{Rn8}} \ \overline{\text{of}} \ \overline{\text{@aa:8}}) \rightarrow \text{Z}$ |   |    |     |             |             | 4         |            |       |        | _ | — | _ | ↕  | _   | _                 | 6             |

| BLD #xx:3, Rd      | В            | (#xx:3 of Rd8) $\rightarrow$ C                                                                  |   | 2  |     |             |             |           |            |       |        | - | — | — | —  | _   | $\updownarrow$    | 2             |

| BLD #xx:3, @Rd     | В            | (#xx:3 of @Rd16) $\rightarrow$ C                                                                |   |    | 4   |             |             |           |            |       |        | _ | _ | _ | _  | _   | $\updownarrow$    | 6             |

| BLD #xx:3, @aa:8   | В            | (#xx:3 of @aa:8) $\rightarrow$ C                                                                |   |    |     |             |             | 4         |            |       |        | - | — | — | —  | _   | $\updownarrow$    | 6             |

| BILD #xx:3, Rd     | В            | $(\overline{\#xx:3} \text{ of } \overline{Rd8}) \to C$                                          |   | 2  |     |             |             |           |            |       |        | _ | — | — | —  | —   | $\updownarrow$    | 2             |

| BILD #xx:3, @Rd    | В            | $(\overline{\#xx:3} \text{ of } \overline{@Rd16}) \rightarrow C$                                |   |    | 4   |             |             |           |            |       |        | _ | _ | _ | _  | _   | $\updownarrow$    | 6             |

| BILD #xx:3, @aa:8  | В            | $(\overline{\#xx:3} \text{ of } \overline{@aa:8}) \rightarrow C$                                |   |    |     |             |             | 4         |            |       |        | _ | _ | _ | —  | _   | $\updownarrow$    | 6             |

| BST #xx:3, Rd      | В            | $C \rightarrow (\#xx:3 \text{ of } Rd8)$                                                        |   | 2  |     |             |             |           |            |       |        | _ | — | — | —  | —   |                   | 2             |

| BST #xx:3, @Rd     | В            | $C \rightarrow (\#xx:3 \text{ of } @Rd16)$                                                      |   |    | 4   |             |             |           |            |       |        | _ | — | — | —  | _   | —                 | 8             |

| BST #xx:3, @aa:8   | в            | $C \rightarrow (\#xx:3 \text{ of } @aa:8)$                                                      |   |    |     |             |             | 4         |            |       |        | — | — | — | —  | _   |                   | 8             |

| BIST #xx:3, Rd     | В            | $\overline{C} \rightarrow$ (#xx:3 of Rd8)                                                       |   | 2  |     |             |             |           |            |       |        | _ | _ | _ | _  | —   |                   | 2             |

| BIST #xx:3, @Rd    | В            | $\overline{C} \rightarrow$ (#xx:3 of @Rd16)                                                     |   |    | 4   |             |             |           |            |       |        | — | — | _ | _  | _   |                   | 8             |

| BIST #xx:3, @aa:8  | В            | $\overline{C} \rightarrow$ (#xx:3 of @aa:8)                                                     |   |    |     |             |             | 4         |            |       |        | _ | _ | _ | _  | _   | —                 | 8             |

| BAND #xx:3, Rd     | В            | $C {\wedge} (\#xx{:}3 \text{ of } Rd8) \to C$                                                   |   | 2  |     |             |             |           |            |       |        | _ | — | — | —  | —   | $\updownarrow$    | 2             |

| BAND #xx:3, @Rd    | В            | $C {\wedge} (\#xx:3 \text{ of } @ Rd16) \to C$                                                  |   |    | 4   |             |             |           |            |       |        | _ | — | _ | _  | _   | $\updownarrow$    | 6             |

| BAND #xx:3, @aa:8  | В            | $C {\scriptstyle \land} (\#xx:3 \text{ of } @aa:8) \rightarrow C$                               |   |    |     |             |             | 4         |            |       |        | — | — | — | —  | _   | $\updownarrow$    | 6             |

| BIAND #xx:3, Rd    | В            | $C {\wedge} (\overline{\#xx:3} \ \overline{of} \ \overline{Rd8}) \to C$                         |   | 2  |     |             |             |           |            |       |        | _ | — | — | —  | —   | $\updownarrow$    | 2             |

| BIAND #xx:3, @Rd   | В            | $C {\wedge} (\overline{\#xx:3} \ \overline{of} \ \overline{@  Rd16}) \to C$                     |   |    | 4   |             |             |           |            |       |        | — | — | — | —  | —   | $\updownarrow$    | 6             |

| BIAND #xx:3, @aa:8 | В            | $C {\wedge} (\overline{\#xx:3} \ \overline{of} \ \overline{@aa:8}) \to C$                       |   |    |     |             |             | 4         |            |       |        | — | — | — | _  | —   | $\updownarrow$    | 6             |

| BOR #xx:3, Rd      | В            | $C{\scriptstyle\lor}(\text{\#xx:3 of Rd8})\rightarrow C$                                        |   | 2  |     |             |             |           |            |       |        | _ | _ | _ | _  | —   | $\leftrightarrow$ | 2             |

| BOR #xx:3, @Rd     | в            | $C{\scriptstyle\lor}(\#xx{:}3\text{ of }@Rd16)\rightarrow C$                                    |   |    | 4   |             |             |           |            |       |        | _ | _ | _ | _  | _   | $\updownarrow$    | 6             |

| BOR #xx:3, @aa:8   | в            | $C \lor (\#xx:3 \text{ of } @aa:8) \rightarrow C$                                               |   |    |     |             |             | 4         |            |       |        | _ | _ | _ | _  | _   | $\updownarrow$    | 6             |

| BIOR #xx:3, Rd     | в            | $C{\scriptstyle\lor}(\overline{\#xx:3}\ \overline{of}\ \overline{Rd8})\rightarrow C$            |   | 2  |     |             |             |           |            |       |        | _ | _ | _ |    | —   | $\updownarrow$    | 2             |

| BIOR #xx:3, @Rd    | в            | $C {\scriptstyle \lor} (\overline{\#xx:3} \ \overline{of} \ \overline{@Rd16}) \rightarrow C$    |   |    | 4   |             |             |           |            |       |        | — | _ | _ | _  | —   | $\updownarrow$    | 6             |

I/O ports

H'E3

| Bit                                   | 7          | 6                  | 5                 | 4                  | 3                 | 2                  | 1                  | 0                 |

|---------------------------------------|------------|--------------------|-------------------|--------------------|-------------------|--------------------|--------------------|-------------------|

|                                       | PUCR67     | PUCR6 <sub>6</sub> | PUCR65            | PUCR6 <sub>4</sub> | PUCR63            | PUCR6 <sub>2</sub> | PUCR6 <sub>1</sub> | PUCR60            |

| Initial value                         | 0          | 0                  | 0                 | 0                  | 0                 | 0                  | 0                  | 0                 |

| Read/Write                            | R/W        | R/W                | R/W               | R/W                | R/W               | R/W                | R/W                | R/W               |

|                                       |            |                    |                   |                    |                   |                    |                    |                   |

|                                       |            | Port               | 6 input pu        | III-up MO          | S control         |                    |                    |                   |

|                                       |            | 0 1                | nput pull-u       | p MOS is           | off               |                    |                    |                   |

|                                       |            | 1 I                | nput pull-u       | p MOS is           | on                |                    |                    |                   |

|                                       |            | Note:              | When the          | e PCR6 sp          | pecification      | n is 0. (Inp       | ut port spe        | ecification)      |

|                                       |            |                    |                   |                    |                   |                    |                    |                   |

| PCR1—Port Control Register 1 H'E4 I/O |            |                    |                   |                    |                   |                    |                    |                   |

| Bit                                   | 7          | 6                  | 5                 | 4                  | 3                 | 2                  | 1                  | 0                 |

|                                       | PCR17      | PCR1 <sub>6</sub>  | PCR1 <sub>5</sub> | PCR1 <sub>4</sub>  | PCR1 <sub>3</sub> | PCR1 <sub>2</sub>  | PCR1 <sub>1</sub>  | PCR1 <sub>0</sub> |

| Initial value                         | 0          | 0                  | 0                 | 0                  | 0                 | 0                  | 0                  | 0                 |

| Read/Write                            | W          | W                  | W                 | W                  | W                 | W                  | W                  | W                 |

|                                       |            |                    |                   | Б                  | ort 1 inpu        | t/output c         | alact              |                   |

|                                       |            |                    |                   |                    |                   | -                  | elect              |                   |

|                                       |            |                    |                   | 1                  |                   |                    |                    |                   |

|                                       |            |                    |                   |                    |                   |                    |                    |                   |

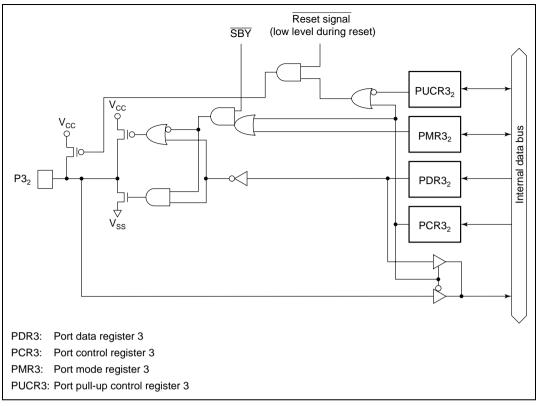

| PCR3—Port Co                          | ontrol Reg | gister 3           |                   |                    | H'H               | 26                 |                    | I/O por           |

|                                       |            |                    |                   |                    |                   |                    |                    |                   |

| Bit                                   | 7          | 6                  | 5                 | 4                  | 3                 | 2                  | 1                  | 0                 |

|                                       | PCR37      | PCR3 <sub>6</sub>  | PCR3 <sub>5</sub> | PCR3 <sub>4</sub>  | PCR3 <sub>3</sub> | PCR3 <sub>2</sub>  | PCR3 <sub>1</sub>  | PCR30             |

| Initial value                         | 0          | 0                  | 0                 | 0                  | 0                 | 0                  | 0                  | 0                 |

| Read/Write                            | W          | W                  | W                 | W                  | W                 | W                  | W                  | W                 |

|                                       |            |                    |                   | Р                  | ort 3 inpu        | t/output s         | elect              |                   |

|                                       |            |                    |                   | (                  |                   | •                  |                    |                   |

|                                       |            |                    |                   | 1                  | I Output          | pin                |                    |                   |

|                                       |            |                    |                   |                    | -                 | -                  |                    |                   |

PUCR6—Port Pull-Up Control Register 6

#### IWPR—Wakeup Interrupt Request Register

System control

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| IWPF7  | IWPF6  | IWPF5  | IWPF4  | IWPF3  | IWPF2  | IWPF1  | IWPF0  |

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/(W)* |

|        | 0      | 0 0    | 0 0 0  |        |        |        |        |

#### Wakeup interrupt request register

| 0 | [Clearing condition]<br>When IWPFn = 1, it is cleared by writing 0                                                    |

|---|-----------------------------------------------------------------------------------------------------------------------|

| 1 | [Setting condition] When pin $\overline{WKPn}$ is designated for wakeup input and a falling edge is input at that pin |

(n = 7 to 0)

Note: \* All bits can only be written with 0, for flag clearing.

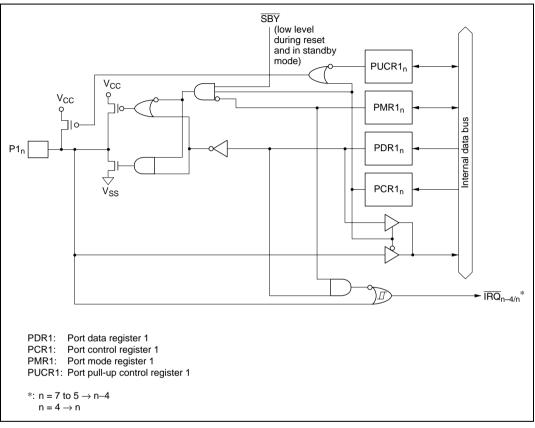

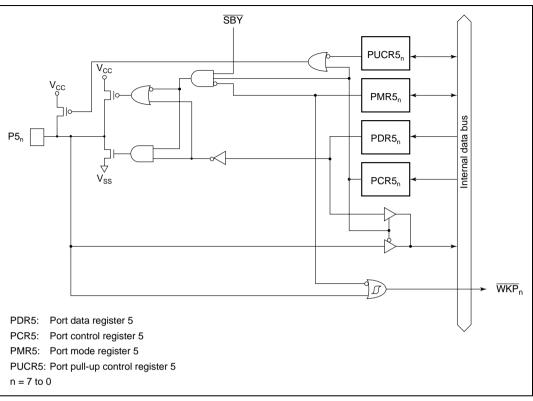

# Appendix C I/O Port Block Diagrams

# C.1 Block Diagrams of Port 1

Figure C.1 (a) Port 1 Block Diagram (Pins P1<sub>7</sub> to P1<sub>4</sub>)

Figure C.2 (e-3) Port 3 Block Diagram (Pin P3<sub>2</sub> in the F-ZTAT Version of the H8/38327 Group and H8/38427 Group)

# C.4 Block Diagram of Port 5

Figure C.4 Port 5 Block Diagram