#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                       |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 8MHz                                                                          |

| Connectivity               | SCI                                                                           |

| Peripherals                | LCD, PWM, WDT                                                                 |

| Number of I/O              | 55                                                                            |

| Program Memory Size        | 60KB (60K x 8)                                                                |

| Program Memory Type        | ОТР                                                                           |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-BQFP                                                                       |

| Supplier Device Package    | 80-QFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6473827rhv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4 Addressing Modes

### 2.4.1 Addressing Modes

The H8/300L CPU supports the eight addressing modes listed in table 2.1. Each instruction uses a subset of these addressing modes.

### Table 2.1Addressing Modes

| No. | Address Modes                                                                 | Symbol          |

|-----|-------------------------------------------------------------------------------|-----------------|

| 1   | Register direct                                                               | Rn              |

| 2   | Register indirect                                                             | @Rn             |

| 3   | Register indirect with displacement                                           | @(d:16, Rn)     |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @Rn+<br>@-Rn    |

| 5   | Absolute address                                                              | @aa:8 or @aa:16 |

| 6   | Immediate                                                                     | #xx:8 or #xx:16 |

| 7   | Program-counter relative                                                      | @(d:8, PC)      |

| 8   | Memory indirect                                                               | @@aa:8          |

1. **Register Direct—Rn:** The register field of the instruction specifies an 8- or 16-bit general register containing the operand.

Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits  $\times$  8 bits), and DIVXU (16 bits  $\div$  8 bits) instructions have 16-bit operands.

- 2. Register Indirect—@Rn: The register field of the instruction specifies a 16-bit general register containing the address of the operand in memory.

- 3. Register Indirect with Displacement—@(d:16, Rn): The instruction has a second word (bytes 3 and 4) containing a displacement which is added to the contents of the specified general register to obtain the operand address in memory.

This mode is used only in MOV instructions. For the MOV.W instruction, the resulting address must be even.

### 3.3.5 Interrupt Operations

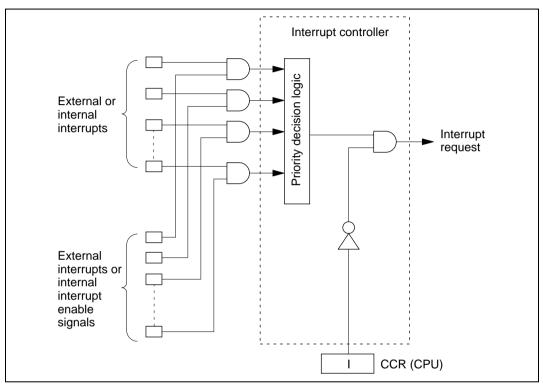

Interrupts are controlled by an interrupt controller. Figure 3.2 shows a block diagram of the interrupt controller. Figure 3.3 shows the flow up to interrupt acceptance.

Figure 3.2 Block Diagram of Interrupt Controller

Interrupt operation is described as follows.

- When an interrupt condition is met while the interrupt enable register bit is set to 1, an interrupt request signal is sent to the interrupt controller.

- When the interrupt controller receives an interrupt request, it sets the interrupt request flag.

- From among the interrupts with interrupt request flags set to 1, the interrupt controller selects the interrupt request with the highest priority and holds the others pending. (Refer to table 3.2 for a list of interrupt priorities.)

- The interrupt controller checks the I bit of CCR. If the I bit is 0, the selected interrupt request is accepted; if the I bit is 1, the interrupt request is held pending.

# Renesas

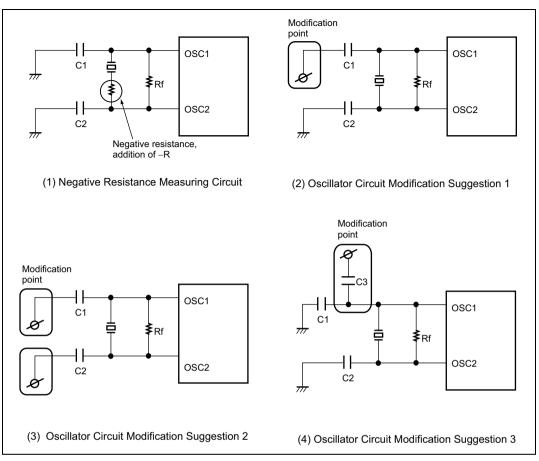

Figure 4.11 Negative Resistance Measurement and Circuit Modification Suggestions

### 4.5.1 Definition of Oscillation Stabilization Wait Time

Figure 4.12 shows the oscillation waveform (OSC<sub>2</sub>), system clock ( $\phi$ ), and microcomputer operating mode when a transition is made from standby mode, watch mode, or subactive mode, to active (high-speed/medium-speed) mode, with an oscillator element connected to the system clock oscillator.

As shown in figure 4.12, as the system clock oscillator is halted in standby mode, watch mode, and subactive mode, when a transition is made to active (high-speed/medium-speed) mode, the sum of the following two times (oscillation stabilization time and wait time) is required.

# Renesas

### Bit 4—Program Setup (PSU)

This bit is to prepare for changing to program mode. Set this bit to 1 before setting the P bit to 1 in FLMCR1 (do not set SWE, ESU, EV, PV, E, and P bits at the same time).

| Bit 4<br>PSU | Description                                                                                            |                 |

|--------------|--------------------------------------------------------------------------------------------------------|-----------------|

| 0            | The program setup state is cancelled                                                                   | (initial value) |

| 1            | The flash memory changes to the program setup state. Set this bit to setting the P bit to 1 in FLMCR1. | 1 before        |

### Bit 3—Erase-Verify (EV)

This bit is to set changing to or cancelling erase-verify mode (do not set SWE, ESU, PSU, PV, E, and P bits at the same time).

| Bit 3 |                                               |                 |

|-------|-----------------------------------------------|-----------------|

| EV    | Description                                   |                 |

| 0     | Erase-verify mode is cancelled                | (initial value) |

| 1     | The flash memory changes to erase-verify mode |                 |

### Bit 2—Program-Verify (PV)

This bit is to set changing to or cancelling program-verify mode (do not set SWE, ESU, PSU, EV, E, and P bits at the same time).

#### Bit 2 PV

| PV | Description                                     |                 |

|----|-------------------------------------------------|-----------------|

| 0  | Program-verify mode is cancelled                | (initial value) |

| 1  | The flash memory changes to program-verify mode |                 |

### Bit 1—Erase (E)

This bit is to set changing to or cancelling erase mode (do not set SWE, ESU, PSU, EV, PV, and P bits at the same time).

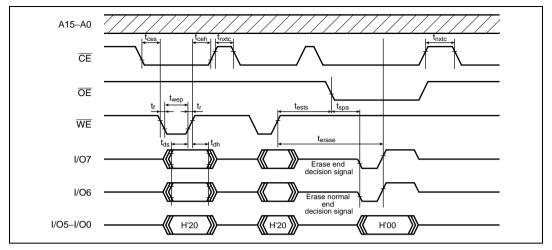

Figure 6.18 Auto-Erase Mode Timing Waveforms

### 6.10.6 Status Read Mode

- 1. Status read mode is provided to identify the kind of abnormal end. Use this mode when an abnormal end occurs in auto-program mode or auto-erase mode.

- 2. The return code is retained until a command write other than a status read mode command write is executed.

- 3. Table 6.20 shows the AC characteristics and 6.21 shows the return codes.

### 1. Port Data Register 1 (PDR1)

| Bit           | 7   | 6               | 5               | 4   | 3    | 2   | 1               | 0   |

|---------------|-----|-----------------|-----------------|-----|------|-----|-----------------|-----|

|               | P17 | P1 <sub>6</sub> | P1 <sub>5</sub> | P14 | P1 3 | P12 | P1 <sub>1</sub> | P10 |

| Initial value | 0   | 0               | 0               | 0   | 0    | 0   | 0               | 0   |

| Read/Write    | R/W | R/W             | R/W             | R/W | R/W  | R/W | R/W             | R/W |

PDR1 is an 8-bit register that stores data for port 1 pins  $P1_7$  to  $P1_0$ . If port 1 is read while PCR1 bits are set to 1, the values stored in PDR1 are read, regardless of the actual pin states. If port 1 is read while PCR1 bits are cleared to 0, the pin states are read.

Upon reset, PDR1 is initialized to H'00.

### 2. Port Control Register 1 (PCR1)

| Bit           | 7     | 6                 | 5                 | 4                 | 3                 | 2                 | 1                 | 0     |

|---------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

|               | PCR17 | PCR1 <sub>6</sub> | PCR1 <sub>5</sub> | PCR1 <sub>4</sub> | PCR1 <sub>3</sub> | PCR1 <sub>2</sub> | PCR1 <sub>1</sub> | PCR10 |

| Initial value | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0     |

| Read/Write    | W     | W                 | W                 | W                 | W                 | W                 | W                 | W     |

PCR1 is an 8-bit register for controlling whether each of the port 1 pins  $P1_7$  to  $P1_0$  functions as an input pin or output pin. Setting a PCR1 bit to 1 makes the corresponding pin an output pin, while clearing the bit to 0 makes the pin an input pin. The settings in PCR1 and in PDR1 are valid only when the corresponding pin is designated in PMR1 as a general I/O pin.

Upon reset, PCR1 is initialized to H'00.

PCR1 is a write-only register, which is always read as all 1s.

Bit 3: P1<sub>3</sub>/TMIG pin function switch (TMIG)

This bit selects whether pin P1<sub>3</sub>/TMIG is used as P1<sub>3</sub> or as TMIG.

| Bit 3<br>TMIG | Description                          |                 |

|---------------|--------------------------------------|-----------------|

| 0             | Functions as P1 <sub>3</sub> I/O pin | (initial value) |

| 1             | Functions as TMIG input pin          |                 |

**Bit 2:** P1<sub>2</sub>/TMOFH pin function switch (TMOFH)

This bit selects whether pin P1<sub>2</sub>/TMOFH is used as P1<sub>2</sub> or as TMOFH.

| Bit 2<br>TMOFH | Description                          |                 |

|----------------|--------------------------------------|-----------------|

| 0              | Functions as P1 <sub>2</sub> I/O pin | (initial value) |

| 1              | Functions as TMOFH output pin        |                 |

**Bit 1:** P1<sub>1</sub>/TMOFL pin function switch (TMOFL)

This bit selects whether pin  $P1_1/TMOFL$  is used as  $P1_1$  or as TMOFL.

| Bit 1<br>TMOFL | Description                          |                 |

|----------------|--------------------------------------|-----------------|

| 0              | Functions as P1 <sub>1</sub> I/O pin | (initial value) |

| 1              | Functions as TMOFL output pin        |                 |

**Bit 0:** P1<sub>0</sub>/TMOW pin function switch (TMOW)

This bit selects whether pin  $P1_0/TMOW$  is used as  $P1_0$  or as TMOW.

| Bit 0 |                                      |                 |

|-------|--------------------------------------|-----------------|

| TMOW  | Description                          |                 |

| 0     | Functions as P1 <sub>0</sub> I/O pin | (initial value) |

| 1     | Functions as TMOW output pin         |                 |

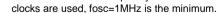

### 8.3.3 Pin Functions

Table 8.6 shows the port 3 pin functions.

### Table 8.6Port 3 Pin Functions

| Pin                                | Pin Functions and                                                                                       | d Selection Met                                                    | hod                                            |           |                     |                                |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|-----------|---------------------|--------------------------------|--|--|

| P37/AEVL                           | The pin function de                                                                                     | The pin function depends on bit SO1 in PMR3 and bit PCR37 in PCR3. |                                                |           |                     |                                |  |  |

|                                    | AEVL                                                                                                    |                                                                    | 0                                              |           |                     | 1                              |  |  |

|                                    | PCR37                                                                                                   | 0                                                                  |                                                | 1         |                     | *                              |  |  |

|                                    | Pin function                                                                                            | P37 input p                                                        | in P37 ou                                      | ıtput pin | A                   | EVL input pin                  |  |  |

| P3 <sub>6</sub> /AEVH              | The pin function de                                                                                     | epends on bit AE                                                   | VH in PMR3 a                                   | nd bit P( | CR3 <sub>6</sub> in | PCR3.                          |  |  |

|                                    | AEVH                                                                                                    |                                                                    | 0                                              |           |                     | 1                              |  |  |

|                                    | PCR36                                                                                                   | 0                                                                  |                                                | 1         |                     | *                              |  |  |

|                                    | Pin function                                                                                            | P3 <sub>6</sub> input p                                            | in P3 <sub>6</sub> ou                          | ıtput pin | AE                  | EVH input pin                  |  |  |

| P3 <sub>5</sub> /TXD <sub>31</sub> | The pin function de<br>PCR3₅ in PCR3.                                                                   | epends on bit TE                                                   | 31 in SCR3-1, b                                | oit SPC3  | 1 in SP             | CR, and bit                    |  |  |

|                                    | SPC31                                                                                                   | 0                                                                  |                                                |           |                     | 1                              |  |  |

|                                    | TE <sub>31</sub>                                                                                        | 0                                                                  |                                                |           |                     | 1                              |  |  |

|                                    | PCR3₅                                                                                                   | 0 1                                                                |                                                | 1         |                     | *                              |  |  |

|                                    | Pin function                                                                                            | $P3_5$ input pin $P3_5$ out                                        |                                                | ıtput pin | TX                  | TXD <sub>31</sub> output pin   |  |  |

| P3 <sub>4</sub> /RXD <sub>31</sub> | The pin function depends on bit RE <sub>31</sub> in SCR3-1 and bit PCR3 <sub>4</sub> in PCR3.           |                                                                    |                                                |           |                     |                                |  |  |

|                                    | RE <sub>31</sub>                                                                                        | 0                                                                  |                                                |           |                     | 1                              |  |  |

|                                    | PCR3 <sub>4</sub>                                                                                       | 0                                                                  | 0 1                                            |           | *                   |                                |  |  |

|                                    | Pin function                                                                                            | P3₄ input p                                                        | P3 <sub>4</sub> input pin P3 <sub>4</sub> outp |           | R۷                  | RXD <sub>31</sub> input pin    |  |  |

| P3 <sub>3</sub> /SCK <sub>31</sub> | The pin function depends on bits CKE311, CKE310, and SMR31 in SCR3-1 and bit PCR3 <sub>3</sub> in PCR3. |                                                                    |                                                |           |                     |                                |  |  |

|                                    | CKE311                                                                                                  |                                                                    | 0                                              |           |                     | 1                              |  |  |

|                                    | CKE310                                                                                                  |                                                                    | 0                                              |           | 1                   | *                              |  |  |

|                                    | COM3 <sub>1</sub>                                                                                       |                                                                    | 0                                              |           | *                   | *                              |  |  |

|                                    | PCR3 <sub>3</sub>                                                                                       | 0                                                                  | 1                                              | *         |                     | *                              |  |  |

|                                    | Pin function                                                                                            | P3 <sub>3</sub> input pin                                          | P33 output pir                                 | -         | output<br>in        | SCK <sub>31</sub> input<br>pin |  |  |

### 8.5.2 Register Configuration and Description

Table 8.11 shows the port 5 register configuration.

### Table 8.11 Port 5 Registers

| Name                            | Abbr. | R/W | Initial Value | Address |

|---------------------------------|-------|-----|---------------|---------|

| Port data register 5            | PDR5  | R/W | H'00          | H'FFD8  |

| Port control register 5         | PCR5  | W   | H'00          | H'FFE8  |

| Port pull-up control register 5 | PUCR5 | R/W | H'00          | H'FFE2  |

| Port mode register 5            | PMR5  | R/W | H'00          | H'FFCC  |

### 1. Port Data Register 5 (PDR5)

| Bit           | 7   | 6               | 5               | 4   | 3   | 2               | 1   | 0   |

|---------------|-----|-----------------|-----------------|-----|-----|-----------------|-----|-----|

|               | P57 | P5 <sub>6</sub> | P5 <sub>5</sub> | P54 | P53 | P5 <sub>2</sub> | P51 | P50 |

| Initial value | 0   | 0               | 0               | 0   | 0   | 0               | 0   | 0   |

| Read/Write    | R/W | R/W             | R/W             | R/W | R/W | R/W             | R/W | R/W |

PDR5 is an 8-bit register that stores data for port 5 pins  $P5_7$  to  $P5_0$ . If port 5 is read while PCR5 bits are set to 1, the values stored in PDR5 are read, regardless of the actual pin states. If port 5 is read while PCR5 bits are cleared to 0, the pin states are read.

Upon reset, PDR5 is initialized to H'00.

### 2. Port Control Register 5 (PCR5)

| Bit           | 7     | 6                 | 5     | 4                 | 3     | 2                 | 1     | 0     |

|---------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|-------|

|               | PCR57 | PCR5 <sub>6</sub> | PCR55 | PCR5 <sub>4</sub> | PCR53 | PCR5 <sub>2</sub> | PCR51 | PCR50 |

| Initial value | 0     | 0                 | 0     | 0                 | 0     | 0                 | 0     | 0     |

| Read/Write    | W     | W                 | W     | W                 | W     | W                 | W     | W     |

PCR5 is an 8-bit register for controlling whether each of the port 5 pins  $P5_7$  to  $P5_0$  functions as an input pin or output pin. Setting a PCR5 bit to 1 makes the corresponding pin an output pin, while clearing the bit to 0 makes the pin an input pin. PCR5 and PDR5 settings are valid when the corresponding pins are designated for general-purpose input/output by PMR5 and bits SGS3 to SGS0 in LPCR.

Upon reset, PCR5 is initialized to H'00.

### 9.4.5 Application Notes

The following types of contention and operation can occur when timer F is used.

### 1. 16-bit Timer Mode

In toggle output, TMOFH pin output is toggled when all 16 bits match and a compare match signal is generated. If a TCRF write by a MOV instruction and generation of the compare match signal occur simultaneously, TOLH data is output to the TMOFH pin as a result of the TCRF write. TMOFL pin output is unstable in 16-bit mode, and should not be used; the TMOFL pin should be used as a port pin.

If an OCRFL write and compare match signal generation occur simultaneously, the compare match signal is invalid. However, if the written data and the counter value match, a compare match signal will be generated at that point. As the compare match signal is output in synchronization with the TCFL clock, a compare match will not result in compare match signal generation if the clock is stopped.

Compare match flag CMFH is set when all 16 bits match and a compare match signal is generated. Compare match flag CMFL is set if the setting conditions for the lower 8 bits are satisfied.

When TCF overflows, OVFH is set. OVFL is set if the setting conditions are satisfied when the lower 8 bits overflow. If a TCFL write and overflow signal output occur simultaneously, the overflow signal is not output.

### 2. 8-bit Timer Mode

a. TCFH, OCRFH

In toggle output, TMOFH pin output is toggled when a compare match occurs. If a TCRF write by a MOV instruction and generation of the compare match signal occur simultaneously, TOLH data is output to the TMOFH pin as a result of the TCRF write.

If an OCRFH write and compare match signal generation occur simultaneously, the compare match signal is invalid. However, if the written data and the counter value match, a compare match signal will be generated at that point. The compare match signal is output in synchronization with the TCFH clock.

If a TCFH write and overflow signal output occur simultaneously, the overflow signal is not output.

b. TCFL, OCRFL

In toggle output, TMOFL pin output is toggled when a compare match occurs. If a TCRF write by a MOV instruction and generation of the compare match signal occur simultaneously, TOLL data is output to the TMOFL pin as a result of the TCRF write.

### 3. Pin Configuration

Table 9.11 shows the timer G pin configuration.

### Table 9.11Pin Configuration

| Name                | Abbr. | I/O   | Function                |

|---------------------|-------|-------|-------------------------|

| Input capture input | TMIG  | Input | Input capture input pin |

### 4. Register Configuration

Table 9.12 shows the register configuration of timer G.

### Table 9.12 Timer G Registers

| Name                      | Abbr.   | R/W | Initial Value | Address |

|---------------------------|---------|-----|---------------|---------|

| Timer control register G  | TMG     | R/W | H'00          | H'FFBC  |

| Timer counter G           | TCG     | _   | H'00          | _       |

| Input capture register GF | ICRGF   | R   | H'00          | H'FFBD  |

| Input capture register GR | ICRGR   | R   | H'00          | H'FFBE  |

| Clock stop register 1     | CKSTPR1 | R/W | H'FF          | H'FFFA  |

| Input capture<br>input signal |  |

|-------------------------------|--|

| Sampling clock                |  |

| Noise canceler<br>output      |  |

| Input capture<br>signal R     |  |

Figure 9.12 Input Capture Input Timing (with Noise Cancellation Function)

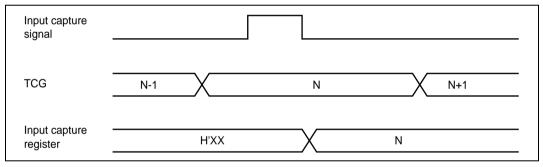

### 4. Timing of Input Capture by Input Capture Input

Figure 9.13 shows the timing of input capture by input capture input

Figure 9.13 Timing of Input Capture by Input Capture Input

### Bit 4: Channel select (CH2)

Bit 4 selects whether ECH and ECL are used as a single-channel 16-bit event counter or as two independent 8-bit event counter channels. When CH2 is cleared to 0, ECH and ECL function as a 16-bit event counter which is incremented each time an event clock is input to the AEVL pin as asynchronous event input. In this case, the overflow signal from ECL is selected as the ECH input clock. When CH2 is set to 1, ECH and ECL function as independent 8-bit event counters which are incremented each time an event clock is input to the AEVL pin, respectively, as asynchronous event input.

| Bit 4<br>CH2 | Description                                                                            |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 0            | ECH and ECL are used together as a single-channel 16-bit event counter (initial value) |  |  |  |  |

| 1            | ECH and ECL are used as two independent 8-bit event counter channels                   |  |  |  |  |

### Bit 3: Count-up enable H (CUEH)

Bit 3 enables event clock input to ECH. When 1 is written to this bit, event clock input is enabled and increments the counter. When 0 is written to this bit, event clock input is disabled and the ECH value is held. The AEVH pin or the ECL overflow signal can be selected as the event clock source by bit CH2.

| Bit 3<br>CUEH | Description                       |                 |

|---------------|-----------------------------------|-----------------|

| 0             | ECH event clock input is disabled | (initial value) |

|               | ECH value is held                 |                 |

| 1             | ECH event clock input is enabled  |                 |

|               |                                   |                 |

Bit 2: Count-up enable L (CUEL)

Bit 3 enables event clock input to ECL. When 1 is written to this bit, event clock input is enabled and increments the counter. When 0 is written to this bit, event clock input is disabled and the ECL value is held.

| Bit 2<br>CUEL | Description                                            |                 |

|---------------|--------------------------------------------------------|-----------------|

| 0             | ECL event clock input is disabled<br>ECL value is held | (initial value) |

| 1             | ECL event clock input is enabled                       |                 |

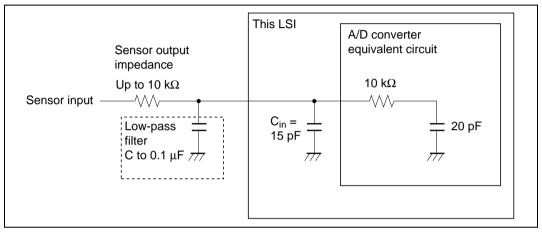

### 12.6.3 Influences on Absolute Precision

Adding capacitance results in coupling with GND, and therefore noise in GND may adversely affect absolute precision. Be sure to make the connection to an electrically stable GND.

Care is also required to ensure that filter circuits do not interfere with digital signals or act as antennas on the mounting board.

Figure 12.6 Analog Input Circuit Example

### **15.2.2 DC Characteristics**

Table 15.2 lists the DC characteristics.

### Table 15.2 DC Characteristics

$V_{CC} = 1.8 \text{ V}$  to 5.5 V,  $AV_{CC} = 1.8 \text{ V}$  to 5.5 V,  $V_{SS} = AV_{SS} = 0.0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}^{*4}$  (including subactive mode) unless otherwise indicated.

|            |                 |                                                                                                                                                                                                                                                                                                      |                     | Valu | es                    |      |                               |       |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----------------------|------|-------------------------------|-------|

| Item       | Symbol          | Applicable Pins                                                                                                                                                                                                                                                                                      | Min                 | Тур  | Max                   | Unit | Test Condition                | Notes |

| Input high | V <sub>IH</sub> | RES,                                                                                                                                                                                                                                                                                                 | 0.8 V <sub>CC</sub> | _    | Vcc + 0.3             | V    | $V_{\rm CC}$ = 4.0 V to 5.5 V |       |

| voltage    |                 | $\label{eq:wkp_0} \begin{array}{l} WKP_0 \text{ to } WKP_7, \\ \overline{IRQ}_0 \text{ to } \overline{IRQ}_4, \\ AEVL, AEVH, \\ TMIC, TMIF, \\ TMIG \\ SCK_{31}, SCK_{32}, \\ \overline{ADTRG} \end{array}$                                                                                          | 0.9 V <sub>CC</sub> | _    | V <sub>CC</sub> + 0.3 | _    | Except the above              |       |

|            |                 | RXD <sub>31</sub> , RXD <sub>32</sub> ,<br>UD                                                                                                                                                                                                                                                        | 0.7 V <sub>CC</sub> |      | V <sub>CC</sub> + 0.3 | V    | $V_{CC}$ = 4.0 V to 5.5 V     | -     |

|            |                 |                                                                                                                                                                                                                                                                                                      | 0.8 V <sub>CC</sub> |      | V <sub>CC</sub> + 0.3 |      | Except the above              | _     |

|            |                 | OSC <sub>1</sub>                                                                                                                                                                                                                                                                                     | 0.8 V <sub>CC</sub> | _    | V <sub>CC</sub> + 0.3 | V    | $V_{CC}$ = 4.0 V to 5.5 V     | -     |

|            |                 |                                                                                                                                                                                                                                                                                                      | 0.9 V <sub>CC</sub> |      | V <sub>CC</sub> + 0.3 | _    | Except the above              | -     |

|            |                 | X <sub>1</sub>                                                                                                                                                                                                                                                                                       | 0.9 V <sub>CC</sub> |      | V <sub>CC</sub> + 0.3 | V    | $V_{\rm CC}$ = 1.8 V to 5.5 V | -     |

|            |                 | P1 <sub>0</sub> to P1 <sub>7</sub> ,                                                                                                                                                                                                                                                                 | 0.7 V <sub>CC</sub> |      | V <sub>CC</sub> + 0.3 | V    | $V_{\rm CC}$ = 4.0 V to 5.5 V | -     |

|            |                 | $\begin{array}{l} {\sf P3}_0 \mbox{ to } {\sf P3}_7, \\ {\sf P4}_0 \mbox{ to } {\sf P4}_3, \\ {\sf P5}_0 \mbox{ to } {\sf P5}_7, \\ {\sf P6}_0 \mbox{ to } {\sf P5}_7, \\ {\sf P7}_0 \mbox{ to } {\sf P6}_7, \\ {\sf P8}_0 \mbox{ to } {\sf P8}_7, \\ {\sf PA}_0 \mbox{ to } {\sf PA}_3 \end{array}$ | 0.8 V <sub>CC</sub> | _    | V <sub>CC</sub> + 0.3 | _    | Except the above              |       |

|            |                 | PB <sub>0</sub> to PB <sub>7</sub>                                                                                                                                                                                                                                                                   | 0.7 V <sub>CC</sub> | _    | $AV_{CC}$ + 0.3       | _    | $V_{\rm CC}$ = 4.0 V to 5.5 V | _     |

|            |                 |                                                                                                                                                                                                                                                                                                      | 0.8 V <sub>CC</sub> | _    | $AV_{CC}$ + 0.3       |      | Except the above              |       |

Note: Connect the TEST pin to V<sub>SS</sub>.

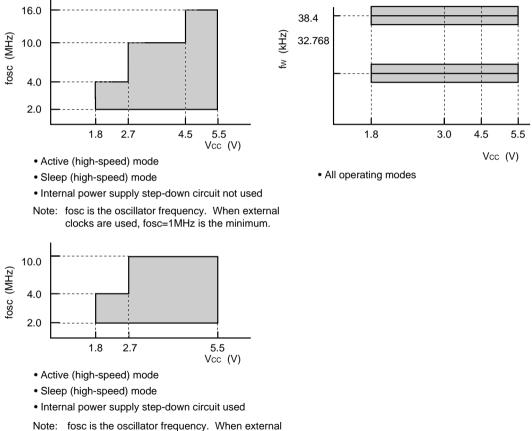

# 15.4 H8/3827R Group Electrical Characteristics (Wide-Range Specification)

### 15.4.1 Power Supply Voltage and Operating Range

The power supply voltage and operating range are indicated by the shaded region in the figures.

### 1. Power Supply Voltage and Oscillator Frequency Range

# Renesas

|                        |                 |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                      | Valu                  | es                  |                     |                                                               |                           |   |

|------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|---------------------|---------------------------------------------------------------|---------------------------|---|

| Item                   | Symbol          | Applicable Pins                                                                                                                                                                                                                                                                                                                            | Min                                                                                                                                                                                                                                                                                  | Тур                   | Max                 | Unit                | Test Condition                                                | Notes                     |   |

| Input low              | V <sub>IL</sub> | RES,                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                 | _                     | 0.2 V <sub>CC</sub> | V                   | $V_{CC}$ = 4.0 V to 5.5 V                                     |                           |   |

| voltage                |                 |                                                                                                                                                                                                                                                                                                                                            | $\label{eq:WKP_0} \begin{array}{l} \mbox{WKP}_0 \mbox{ to } \mbox{WKP}_7, \\ \hline \mbox{IRQ}_0 \mbox{ to } \mbox{IRQ}_4, \\ \mbox{AEVL}, \mbox{ AEVH}, \\ \mbox{TMIC}, \mbox{TMIF}, \\ \hline \mbox{TMIG} \\ \mbox{SCK}_{31}, \mbox{SCK}_{32}, \\ \hline \mbox{ADTRG} \end{array}$ | -0.3                  | _                   | 0.1 V <sub>CC</sub> | _                                                             | Except the above          | - |

|                        |                 | RXD <sub>31</sub> , RXD <sub>32</sub> ,                                                                                                                                                                                                                                                                                                    | -0.3                                                                                                                                                                                                                                                                                 | —                     | 0.3 V <sub>CC</sub> | V                   | $V_{CC}$ = 4.0 V to 5.5 V                                     | -                         |   |

|                        |                 | UD                                                                                                                                                                                                                                                                                                                                         | -0.3                                                                                                                                                                                                                                                                                 | _                     | $0.2 V_{CC}$        |                     | Except the above                                              |                           |   |

|                        |                 | OSC <sub>1</sub>                                                                                                                                                                                                                                                                                                                           | -0.3                                                                                                                                                                                                                                                                                 | _                     | 0.2                 |                     | When internal step-<br>down circuit is<br>used.               |                           |   |

|                        |                 |                                                                                                                                                                                                                                                                                                                                            | -0.3                                                                                                                                                                                                                                                                                 | —                     | 0.2 V <sub>CC</sub> | V                   | $V_{\rm CC}$ = 4.0 V to 5.5 V                                 | -                         |   |

|                        |                 |                                                                                                                                                                                                                                                                                                                                            | -0.3                                                                                                                                                                                                                                                                                 | —                     | 0.1 V <sub>CC</sub> | _                   | Except the above                                              | -                         |   |

|                        |                 | X <sub>1</sub>                                                                                                                                                                                                                                                                                                                             | -0.3                                                                                                                                                                                                                                                                                 | —                     | 0.1 V <sub>CC</sub> | V                   | $V_{\rm CC}$ = 1.8 V to 5.5 V                                 | -                         |   |

|                        |                 | P1 <sub>0</sub> to P1 <sub>7</sub> ,                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                 | —                     | 0.3 V <sub>CC</sub> | V                   | $V_{CC}$ = 4.0 V to 5.5 V                                     | -                         |   |

|                        |                 | $\begin{array}{c} {\sf P3}_0 \mbox{ to } {\sf P3}_7, \\ {\sf P4}_0 \mbox{ to } {\sf P4}_3, \\ {\sf P5}_0 \mbox{ to } {\sf P5}_7, \\ {\sf P6}_0 \mbox{ to } {\sf P6}_7, \\ {\sf P7}_0 \mbox{ to } {\sf P7}_7, \\ {\sf P8}_0 \mbox{ to } {\sf P8}_7, \\ {\sf P4}_0 \mbox{ to } {\sf P4}_3, \\ {\sf PB}_0 \mbox{ to } {\sf P8}_7 \end{array}$ | -0.3                                                                                                                                                                                                                                                                                 | _                     | 0.2 V <sub>CC</sub> |                     | Except the above                                              |                           |   |

| Output high<br>voltage | $V_{OH}$        | $P1_0$ to $P1_7$ ,<br>$P3_0$ to $P3_7$ ,                                                                                                                                                                                                                                                                                                   | V <sub>CC</sub> – 1.0                                                                                                                                                                                                                                                                | _                     | _                   | V                   | $V_{CC}$ = 4.0 V to 5.5 V<br>-I <sub>OH</sub> = 1.0 mA        |                           |   |

|                        |                 | $P4_0$ to $P4_2$ ,<br>$P5_0$ to $P5_7$ ,<br>$P6_0$ to $P6_7$ ,                                                                                                                                                                                                                                                                             | V <sub>CC</sub> - 0.5                                                                                                                                                                                                                                                                | —                     | _                   |                     | V <sub>CC</sub> = 4.0 V to 5.5 V<br>-I <sub>OH</sub> = 0.5 mA | -                         |   |

|                        |                 | F                                                                                                                                                                                                                                                                                                                                          | $P_{0}^{0}$ to $P_{7}^{0}$ ,<br>$P_{1}^{0}$ to $P_{7}^{0}$ ,<br>$P_{1}^{0}$ to $P_{1}^{0}$ ,<br>$P_{1}^{0}$ to $P_{1}^{0}$ ,<br>$P_{2}^{0}$ to $P_{3}^{0}$                                                                                                                           | V <sub>CC</sub> - 0.3 | _                   | _                   | _                                                             | -I <sub>OH</sub> = 0.1 mA | - |

|                                              |                    |                 |     | Value | S   |      |                                                                            |                                                      |

|----------------------------------------------|--------------------|-----------------|-----|-------|-----|------|----------------------------------------------------------------------------|------------------------------------------------------|

| ltem                                         | Symbol             | Applicable Pins | Min | Тур   | Мах | Unit | <b>Test Condition</b>                                                      | Notes                                                |

| Sleep<br>mode<br>current<br>consump-<br>tion | I <sub>SLEEP</sub> | V <sub>CC</sub> | _   | 0.5   | _   | mA   | V <sub>CC</sub> = 2.7 V,<br>f <sub>OSC</sub> = 2 MHz                       | *1 *3 *4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ. |

|                                              |                    |                 | _   | 0.8   | _   |      |                                                                            | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      |                                                                            | Approx.<br>max. value<br>= 1.1 ×<br>Typ.             |

|                                              |                    |                 | _   | 0.7   | _   |      | V <sub>CC</sub> = 5 V,                                                     | *1 *3 *4                                             |

|                                              |                    |                 |     |       |     |      | f <sub>OSC</sub> = 2 MHz                                                   | Approx.<br>max. value<br>= 1.1 ×<br>Typ.             |

|                                              |                    |                 | —   | 1.2   | —   |      |                                                                            | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      | Approx.<br>max. value<br>= 1.1 ×<br>Typ.                                   |                                                      |

|                                              |                    |                 | _   | 1.1   | _   |      | V <sub>CC</sub> = 5 V,<br>f <sub>OSC</sub> = 4 MHz                         | *1*3*4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ.   |

|                                              |                    |                 | _   | 1.6   | _   |      |                                                                            | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      |                                                                            |                                                      |

|                                              |                    |                 | _   | 1.9   | 5.0 |      | V <sub>CC</sub> = 5 V,                                                     | *1 *3 *4                                             |

|                                              |                    |                 | —   | 2.6   | 5.0 |      | f <sub>OSC</sub> = 10 MHz                                                  | *2 *3 *4                                             |

| Subactive                                    | leun               | V <sub>CC</sub> | _   | 12    | _   | μA   | V <sub>CC</sub> = 2.7 V,                                                   | *1 *3 *4                                             |

| mode<br>current                              | 1308               | •00             |     | 12    |     | μ, τ | LCD on,<br>32-kHz crystal                                                  | Reference<br>value                                   |

| consump-<br>tion                             |                    |                 | _   | 15    | _   |      | <sup>-</sup> resonator used<br>(φ <sub>SUB</sub> = φ <sub>W</sub> /8)      | *2 *3 *4<br>Reference<br>value                       |

|                                              |                    |                 | _   | 18    | 50  |      | V <sub>CC</sub> = 2.7 V,                                                   | *1 *3 *4                                             |

|                                              |                    |                 | _   | 30    | 50  | _    | LCD on,                                                                    | *2 *3 *4                                             |

|                                              |                    |                 |     |       |     |      | 32-kHz crystal<br>resonator used<br>(φ <sub>SUB</sub> = φ <sub>W</sub> /2) |                                                      |

### LPCR—LCD Port Control Register

### H'C0

### LCD controller/driver

| Bit           | 7    | 6    | 5   | 4   | 3    | 2    | 1    | 0    |

|---------------|------|------|-----|-----|------|------|------|------|

|               | DTS1 | DTS0 | CMX | SGX | SGS3 | SGS2 | SGS1 | SGS0 |

| Initial value | 0    | 0    | 0   | 0   | 0    | 0    | 0    | 0    |

| Read/Write    | R/W  | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

|               |      |      |     |     |      |      |      |      |

| Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |                                           |                                           | F                                         | function of                               | Pins SEG <sub>3</sub>                     | 32 to SEG1                               |                             |                                         |             |

|-------|-------|-------|-------|-------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------|-----------------------------|-----------------------------------------|-------------|

| SGX   | SGS3  | SGS2  | SGS1  | SGS0  | SEG <sub>32</sub><br>to SEG <sub>29</sub> | SEG <sub>28</sub><br>to SEG <sub>25</sub> | SEG <sub>24</sub><br>to SEG <sub>21</sub> | SEG <sub>20</sub><br>to SEG <sub>17</sub> | SEG <sub>16</sub><br>to SEG <sub>13</sub> | SEG <sub>12</sub><br>to SEG <sub>9</sub> | SEG <sub>8</sub><br>to SEG₅ | SEG <sub>4</sub><br>to SEG <sub>1</sub> | Notes       |

| 0     | 0     | 0     | 0     | 0     | Port                                      | Port                                      | Port                                      | Port                                      | Port                                      | Port                                     | Port                        | Port                                    | (Initial va |

|       | 0     | 0     | 0     | 1     | Port                                      | Port                                      | Port                                      | Port                                      | Port                                      | Port                                     | Port                        | Port                                    |             |

|       | 0     | 0     | 1     | *     | SEG                                       | SEG                                       | Port                                      | Port                                      | Port                                      | Port                                     | Port                        | Port                                    | 1           |

|       | 0     | 1     | 0     | *     | SEG                                       | SEG                                       | SEG                                       | SEG                                       | Port                                      | Port                                     | Port                        | Port                                    | 1           |

|       | 0     | 1     | 1     | *     | SEG                                       | SEG                                       | SEG                                       | SEG                                       | SEG                                       | SEG                                      | Port                        | Port                                    | 1           |

|       | 1     | *     | *     | *     | SEG                                       | SEG                                       | SEG                                       | SEG                                       | SEG                                       | SEG                                      | SEG                         | SEG                                     | 1           |

| 1     | 0     | 0     | 0     | 0     | Port*                                     | Port                                      | Port                                      | Port                                      | Port                                      | Port                                     | Port                        | Port                                    |             |

|       | *     | *     | *     | *     |                                           |                                           | U                                         | se prohibit                               | ed                                        |                                          |                             |                                         |             |

| Bit 4 | Bit 4 Description                              |                 |  |  |  |  |

|-------|------------------------------------------------|-----------------|--|--|--|--|

| SGX   | Description                                    |                 |  |  |  |  |

| 0     | Pins SEG <sub>32</sub> to SEG <sub>29</sub> *  | (Initial value) |  |  |  |  |

| 1     | Pins CL <sub>1</sub> , CL <sub>2</sub> , DO, M |                 |  |  |  |  |

|       |                                                |                 |  |  |  |  |

Note: \* These pins function as ports when the setting of SGS3 to SGS0 is 0000 or 0001. In the case of the H8/38327 Group and H8/38427 Group the initial values of these bits must not be changed.

#### Duty select, common function select

| Bit 7 | Bit 6 | Bit 5      | Durte Curala | D. D.                                | Notes                                                                                         |

|-------|-------|------------|--------------|--------------------------------------|-----------------------------------------------------------------------------------------------|

| DTS1  | DTS0  | CMX        | Duty Cycle   | Common Drivers                       | Notes                                                                                         |

| 0     | 0     | 0          | Static       | COM <sub>1</sub>                     |                                                                                               |

|       |       | 1          | Static       | COM <sub>4</sub> to COM <sub>1</sub> | COM <sub>4</sub> to COM <sub>2</sub> output the same waveform as COM <sub>1</sub>             |

| 0     | 1     | 0          | 1/2 duty     | COM <sub>2</sub> to COM <sub>1</sub> |                                                                                               |

|       |       | 1          | 1/2 duty     | COM <sub>4</sub> to COM <sub>1</sub> | $COM_4$ outputs the same waveform as $COM_3$ and $COM_2$ outputs the same waveform as $COM_1$ |

| 1     | 0     | 0          | 1/3 duty     | COM <sub>3</sub> to COM <sub>1</sub> |                                                                                               |

|       |       | 1          | 1/3 duty     | COM <sub>4</sub> to COM <sub>1</sub> | COM <sub>4</sub> outputs a non-selected waveform                                              |

| 1     | 1     | 0          | 1/4 dutv     | COM <sub>4</sub> to COM <sub>1</sub> | _                                                                                             |

|       |       | 1 1/4 duty |              |                                      |                                                                                               |

Figure C.2 (f-1) Port 3 Block Diagram (Pin P3<sub>1</sub>, H8/3827R Group and H8/3827S Group)