Welcome to E-XFL.COM

Understanding Embedded - Microcontroller, Microprocessor, FPGA Modules

Embedded - Microcontroller, Microprocessor, and FPGA Modules are fundamental components in modern electronic systems, offering a wide range of functionalities and capabilities. Microcontrollers are compact integrated circuits designed to execute specific control tasks within an embedded system. They typically include a processor, memory, and input/output peripherals on a single chip. Microprocessors, on the other hand, are more powerful processing units used in complex computing tasks, often requiring external memory and peripherals. FPGAs (Field Programmable Gate Arrays) are highly flexible devices that can be configured by the user to perform specific logic functions, making them invaluable in applications requiring customization and adaptability.

Applications of Embedded - Microcontroller,

| Product Status |  |

|----------------|--|

Details

| Product Status        | Not For New Designs                                                   |

|-----------------------|-----------------------------------------------------------------------|

| Module/Board Type     | FPGA, USB Core                                                        |

| Core Processor        | Spartan-3A DSP                                                        |

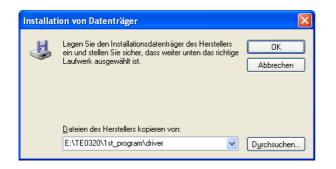

| Co-Processor          | Cypress EZ-USB FX2LP                                                  |

| Speed                 | 100MHz                                                                |

| Flash Size            | 4MB                                                                   |

| RAM Size              | 128MB                                                                 |

| Connector Type        | B2B                                                                   |

| Size / Dimension      | 2.7" x 1.9" (68mm x 48mm)                                             |

| Operating Temperature | -40°C ~ 85°C                                                          |

| Purchase URL          | https://www.e-xfl.com/product-detail/trenz-electronic/te0320-00-ev02i |

|                       |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 Block Diagram                       |    |

|---------------------------------------|----|

| 2 Module options                      | 5  |

| 3 Specifications                      | 6  |

| 4 Board Dimensions                    | 7  |

| 5 Power Supply                        | 8  |

| 5.1 Power Supply Range                | 8  |

| 5.2 Power Supply Sources              |    |

| 5.3 On-Board Power Rails              | 9  |

| 5.4 Power Supervision                 | 12 |

| 5.4.1 Power-on Reset                  | 12 |

| 5.4.2 Power Fail                      | 13 |

| 6 Inputs and Outputs                  | 14 |

| 6.1 Board-to-Board Connectors         |    |

| 6.2 USB Interface                     | 16 |

| 6.2.1 USB Connector                   |    |

| 6.2.2 USB Pins                        |    |

| 6.3 JTAG Interface                    |    |

| 6.3.1 JTAG connector J2               |    |

| 6.3.2 JTAG lines at B2B connector JM4 | 20 |

| 6.4 I2C bus                           |    |

| 6.5 SPI bus.                          |    |

| 6.5.1 SPI bus for configuration       |    |

| 6.5.2 SPI bus for operation           |    |

| 6.6 LEDs                              |    |

| 6.6.1 System LED D1                   |    |

| 6.6.2 User LEDs D[5:8]                |    |

| 6.7 Push-Buttons S[3:4]               |    |

| 6.8 Switches.                         |    |

| 6.8.1 DIP Slide Switches S1[A:D]      |    |

| 6.8.2 Slide Switch S2.                |    |

| 6.8.3 DIP Slide Switches S5[A:H]      |    |

| 6.9 Voltage Reference VREF0.          |    |

| 7 Timing                              |    |

| 7.1 Main Clock Oscillator             |    |

| 7.2 24 MHz Clock Oscillator           |    |

| 7.3 Interface Clock (IFCLK)           |    |

| 7.4 Digital Clock Manager (DCM)       |    |

| 7.5 Watchdog                          |    |

| 8 Memories                            |    |

| 8.1 DDR SDRAM                         |    |

| 8.2 SPI Flash                         |    |

| 8.3 Serial EEPROM                     |    |

| 9 System Requirements                 |    |

| 9.1 Power Supply Requirements         |    |

| 9.2 Hardware Design Requirements      |    |

| 9.3 USB Requirements                  |    |

| 9.4 JTAG Requirements                 |    |

| 9.4.1 Software Requirements           |    |

| 9.5 Operating System Support.         |    |

|                                       |    |

## **5 Power Supply**

### 5.1 Power Supply Range

The power supply range of TE0320 is 4.0 V to 7.0 V.

### 5.2 Power Supply Sources

TE0320 can be power supplied in two ways:

- through USB connector J1,

- through B2B connector JM5 (pins 1 to 4).

The power supply source is determined by assembly option. See Figure 5.

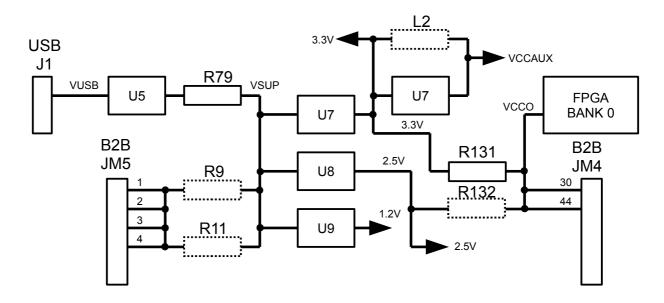

#### Figure 5: Power supply options diagram

If resistors R9 and R11 are populated and R12 is <u>not</u> populated, then TE0320 is power supplied through JM5 (B2B connector).

Figure 6: assembly combination for power supply through JM5.

If resistors R9 and R11 are <u>not</u> populated and R12 is populated, then TE0320 is power supplied through J1 (USB bus).

#### Figure 10: assembly option for VCCAUX = off (bottom view).

Pins 30 and 44 of JM4 are power supply **inputs** in this case.

(b) if resistor R131 is <u>not</u> populated and R132 <u>is</u> populated, VCCCIO0 power rail is set to power rail 2.5V (nominal voltage = 2.5 V).

Figure 11: assembly option for VCCAUX = 2.5 V (bottom view).

Pins 30 and 44 of JM4 are power supply **outputs** in this case.

(c) if resistor R131 <u>is</u> populated and R132 is <u>not</u> populated, VCCCIO0 power rail is set to power rail 3.3V (nominal voltage = 3.3 V). This is the default.

Figure 12: assembly option for VCCCIO0 = 3.3 V (bottom view).

Pins 30 and 44 of JM4 are power supply **outputs** in this case.

Assembly option where both R131 and R132 are populated is not allowed.

1.2 V, 2.5 V and 3.3 V voltage rails are provided by corresponding step-down regulator DC/DC converters, each one capable of providing up to 3 A of output current. These three regulators are synchronized to switch with 120° phase lag, to improve EMC, and to reduce input ripple. The synchronization circuit can be omitted in cost sensitive applications (please contact Trenz Electronic).

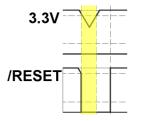

start. When the rail voltage drops below the threshold voltage, the /RESET line becomes active (low) again.

Figure 14: Reset assertion on power drop with fixed delay time of 200 ms.

#### 5.4.2 Power Fail

TE0320 integrates a power-fail comparator which can be used for low-battery detection, power-fail warning, or for monitoring Vsup power rail.

An additional power-fail circuit can be used, to monitor the input voltage. At 4.4V, a power-fail signal (/PFO) is sent to the FPGA. Should you wish or need another threshold voltage, please contact Trenz Electronic.

#### 6.3.2 JTAG lines at B2B connector JM4

JTAG signal lines are also available at B2B connector JM4. See Table 40 for additional information on these signals.

#### 6.4 I2C bus

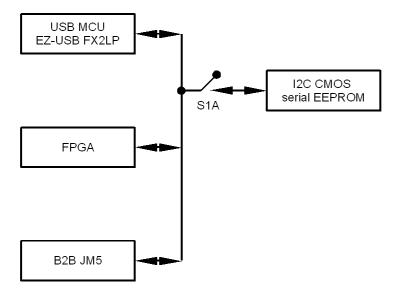

TE0320 has a flexible I2C bus on-board as outlined in Figure 28.

#### Figure 28: I2C bus topology.

The I2C signals on the TE0320 are listed and described in Table 5.

| name | definition   | description                                                                               |

|------|--------------|-------------------------------------------------------------------------------------------|

| SDA  | serial data  | This is a bidirectional pin used to transfer addresses and data into and out of a device. |

| SCL  | serial clock | This signal is used to synchronize the data transfer to and from a device.                |

#### Table 5: I2C signals summary.

The I2C bus is typically used by the USB microcontroller to write USB firmware to the serial EEPROM. In this case,

- the I2C port of the FPGA must be set in slave mode (SCL pin as input),

- the device attached to the I2C port of B2B JM5 connector must be set to slave mode.

The USB microcontroller can operate just in I2C master mode (default operation). If the user wants to set another device attached to the I2C bus as master device, the USB microcontroller shall three-state (Z = high impedance) its SCL and SDA pins.

If the FPGA is set to I2C master mode, it can write to or read from serial EEPROM (always slave mode) and B2B connector JM5 (attached device set to slave mode).

If the device attached to the I2C port of B2B JM5 connector is set to master mode, it can write to or read from serial EEPROM (always slave mode) and FPGA I2C port (set to slave mode).

Possible I2C operation modes are summarized in Table 6.

| name   | definition            | description                                                                                                                                                                                                        |

|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_Q  | serial data<br>output | This output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of SPI_/C.                                                                                         |

| SPI_D  | serial data input     | This input signal is used to transfer data serially into the device. It receives instructions, addresses, and the data to be programmed. Values are latched on the rising edge of SPI_/C                           |

| SPI_/C | serial clock          | This input signal provides the timing of the serial interface. Instructions, addresses, or data present at SPI_D are latched on the rising edge of SPI_/C. Data on SPI_Q changes after the falling edge of SPI_/C. |

|        |                       | When this input signal is <b>high</b> , the device is <b>disabled</b> and SPI_Q is at high impedance (Z).                                                                                                          |

| SPI_/S | chip select           | When this input signal is <b>low</b> , the device is <b>enabled</b> .                                                                                                                                              |

|        |                       | After power-up, a falling edge on SPI_/S is required prior to the start of any instruction to the Flash memory.                                                                                                    |

#### Table 7: SPI signals summary.

SPI signal pin-out of the TE0320 is summarized in Table 8.

| name   | FPGA ball | JM5 pin |

|--------|-----------|---------|

| SPI_Q  | AF24      | 18      |

| SPI_D  | AB15      | 12      |

| SPI_/C | AE24      | 22      |

| SPI_/S | AA7       | 20      |

Table 8: SPI pin-out summary.

SPI pins on B2B connector JM5 cannot be used as GPIOs (general purpose I/Os).

The SPI bus can be used during configuration and operation in a plurality of ways as summarized respectively in Table 9 and Table 10. Any other usage of the SPI bus is neither supported nor recommended.

#### 6.5.1 SPI bus for configuration

The SPI bus is used for configuration in two ways by default:

(d) EZ-USB ► Flash

the USB microcontroller (master) writes the PROM file (containing the FPGA configuration bitstream) to the SPI serial Flash memory (slave)

(e) FPGA - Flash

the FPGA (master) configures itself in Master SPI mode from the SPI serial Flash memory (slave).

In case (a), the FPGA shall be turned off to release its shared SPI pins.

In case (b), the USB microcontroller shall three-state (Z = high impedance) its shared SPI pins.

Figure 30: DONE LED D1 (bottom side).

### 6.6.2 User LEDs D[5:8]

TE0320 is provided with 4 user LEDs. A LED is lit when the corresponding signal listed in Table 11 is set high (logical 1).

| LED | signal | FPGA ball | FPGA pin            | bank |

|-----|--------|-----------|---------------------|------|

| D5  | UL1    | R20       | IO_L22N_1           | 1    |

| D6  | UL2    | V23       | IO_L21P_1           | 1    |

| D7  | UL3    | R19       | IO_L22P_1           | 1    |

| D8  | UL4    | U24       | IO_L23N_1<br>VREF_1 | 1    |

Table 11: user LEDs signal details..

### 6.7 Push-Buttons S[3:4]

TE0320 is provided with 2 user buttons. A signal listed in Table 12 is set low (logical 0) when a push button is pressed, and vice-versa.

| switch | signal | FPGA ball | FPGA pin  | bank | default<br>input | input<br>when<br>pressed |

|--------|--------|-----------|-----------|------|------------------|--------------------------|

| S3     | PB1    | U23       | IO_L23P_1 | 1    | logical 1        | logical 0                |

| S4     | PB2    | R22       | IO_L25N_1 | 1    | logical 1        | logical 0                |

Table 12: user push-buttons signal details.

S4 - PB2 S3 - PB1

Figure 31: push buttons PB1 and PB2.

full power operation.

Figure 35: S2 on position FX2 PON (FX2\_PS\_EN = high).

When the EZ-USB FX2LP USB microcontroller resets signal FX2\_PS\_EN (low), the following components are switched off:

- FPGA core logic (1.2V)

- DDR SDRAM (2.5V)

- FPGA bank 3 (2.5V)

- VREF (2.5V)

- VCCCIO0 (2.5V) FPGA bank 0

This setting can be useful for dynamic **low power** operation.

Figure 36: S2 on position FX2 PON (FX2\_PS\_EN = low).

#### 6.8.2.3 Alternate Assembly Options for Slide Switch S2

Slide switch S2 can be replaced by one resistors in the following cases:

- cost sensitive applications

- applications where just one position of S2 is required

- application where switching of S2 is not allowed.

Assembly option when resistor R17 <u>not</u> populated and R19 populated is equivalent to slide switch S2 permanently set to PON.

Figure 37: assembly option: S2 = PON.

## 7 Timing

## 7.1 Main Clock Oscillator

The module has a main SMD clock oscillator providing a clock source for the FPGA as detailed in Table 3.

| signal  | FPGA pin           | FPGA ball | FPGA bank |

|---------|--------------------|-----------|-----------|

| MAINCLK | IO_L27N_2<br>GCLK1 | AA14      | 2         |

Table 16: Main clock signal details.

Standard frequency is 100 MHz. Should you wish or need another main clock oscillator frequency, please contact Trenz Electronic. The lower the main clock frequency, the lower the module power consumption. Moreover, as the main clock is preferably used as DDR SDRAM clock, a lower clock frequency makes easier for the development tools to meet the timing requirements (particularly for DDR SDRAM).

## 7.2 24 MHz Clock Oscillator

The module has a 24 MHz SMD clock oscillator providing a clock source for both the EZ-USB FX2LP USB microcontroller (XTALIN) and the FPGA as detailed in Table 17.

| signal | FPGA pin           | FPGA ball | FPGA bank |

|--------|--------------------|-----------|-----------|

| 24MHZ1 | IO_L28N_2<br>GCLK3 | AE14      | 2         |

Table 17: 24 MHz clock signal details.

## 7.3 Interface Clock (IFCLK)

The IFCLK line synchronizes the communication between the EZ-USB FX2LP USB microcontroller and the FPGA as detailed in Table 18.

| signal | FPGA pin                     | FPGA ball | FPGA bank |

|--------|------------------------------|-----------|-----------|

| IFCLK  | IO_L31N_1<br>TRDY1<br>RHCLK3 | P25       | 1         |

Table 18: Interface clock signal details.

# 7.4 Digital Clock Manager (DCM)

The DCMs of the FPGA can be used to synthesize arbitrary clock frequencies from any on-board clock network, differential clock input pair or single-ended clock input. For further reference, please read Xilinx DS485:Digital Clock Manager (DCM) Module and the DCM chapter in Xilinx UG331: Spartan-3 Generation FPGA User Guide.

## 7.5 Watchdog

TE0320 has a watchdog timer that is periodically triggered by a positive or negative transition of the watchdog input (WDI) signal. When the supervising system fails to retrigger the watchdog circuit within the time-out interval (min 1.1

### 8 Memories

The TE0300 has three on-board memories:

- DDR SDRAM

- SPI Flash

- serial EEPROM

#### 8.1 DDR SDRAM

TE0320 modules have two 512Mb DDR SDRAM components each with a 16-bit data-bus connected in parallel to FPGA bank 3 as a virtual 512Mb DDR SDRAM component with a 32-bit data-bus. Memory available in industrial and commercial temperature grade.

### 8.2 SPI Flash

TE0320 has an STMicroelectronics M25P32/64/128 (32/64/128-Mbit), low voltage, serial Flash memory with 75 MHz SPI bus interface for configuration and operating storage accessible through USB or SPI. Default module configuration contain 32 Mbit Flash chip M25P32, others available by request.

### 8.3 Serial EEPROM

TE0300 modules have a Micron Technology 24LC128 128 kbit I2C CMOS Serial EEPROM for EZ-USB FX2 firmware, vendor ID and device ID storage accessible through the EZ-USB FX2 microcontroller.

40/82

| Step 1. Select Storage Ta                                                                                                                                                                                                                   | gei                                                     | Step 2.                                                           | Add                                       | Storage Device(s)                                                                   |          | Step 3,                 |             | Enter Data                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------|----------|-------------------------|-------------|---------------------------------------------------------------------|

| Storage Device Type :                                                                                                                                                                                                                       |                                                         | PROM Family                                                       |                                           | Platform Flash                                                                      |          | General File Detail     |             | Value                                                               |

| Xilinx Flash/PROM                                                                                                                                                                                                                           |                                                         | Device (bits)                                                     |                                           | xcf01s [1 M] 🗸                                                                      |          | Checksum Fill<br>Value  | FF          |                                                                     |

| Spartan3AN<br>SPI Flash                                                                                                                                                                                                                     |                                                         | Add Storage                                                       |                                           | Remove Storage Device                                                               |          | Output File Name        | fpga        |                                                                     |

| Configure Single FPGA                                                                                                                                                                                                                       |                                                         | Add Scorage                                                       | Device                                    | Remove Scorage Device                                                               |          | Output File<br>Location | C:/Daten    | Į                                                                   |

| <ul> <li>Configure Single FPGA</li> <li>Configure MultiBoot FPGA</li> </ul>                                                                                                                                                                 |                                                         |                                                                   |                                           |                                                                                     |          | Flash/PROM Fi           | le Property | Value                                                               |

| Configure from Paralleled PROMs<br>Generic Parallel PROM                                                                                                                                                                                    |                                                         |                                                                   |                                           |                                                                                     |          | File Format             |             | BIN (Swap Bits ON)                                                  |

| denence Parallel PROM                                                                                                                                                                                                                       |                                                         |                                                                   |                                           |                                                                                     |          | Enable Revisioning      |             | MCS<br>EXO                                                          |

|                                                                                                                                                                                                                                             |                                                         |                                                                   |                                           |                                                                                     |          | Number Of Revisio       | ns          | TEK                                                                 |

|                                                                                                                                                                                                                                             |                                                         |                                                                   |                                           |                                                                                     |          | Enable Compressio       | n           | HEX (Swap Bits ON)<br>HEX (Swap Bits OFF                            |

|                                                                                                                                                                                                                                             |                                                         | V Auto Select                                                     | PROM                                      |                                                                                     |          |                         |             | BIN (Swap Bits ON)<br>BIN (Swap Bits OFF<br>UFP ('C' format)<br>ISC |

| escription:                                                                                                                                                                                                                                 |                                                         |                                                                   |                                           |                                                                                     |          |                         |             |                                                                     |

| In this step, you will enter information to assist in s<br>• Checksum Fill Value: When data is insu<br>• Output File Name: This allows you to sp<br>• Output File Location: This allows you to<br>• File Format: PROM likes can be energian | ficient to fill th<br>ecify the base<br>specify the dir | e entire memory of<br>name of the file to<br>rectory in which the | f a PROM, t<br>which your<br>e file named | ne value specified here is us<br>PROM data will be written<br>above will be created | ed to ca |                         |             |                                                                     |

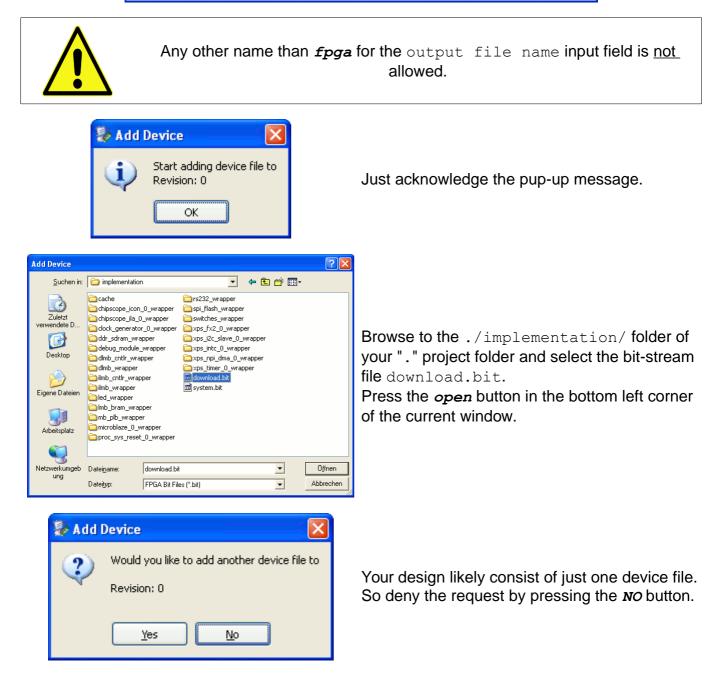

# You should see the following message in the main panel: generate succeeded.

|                                            |              |                |              |                |                        |             |                                                                                | -     |

|--------------------------------------------|--------------|----------------|--------------|----------------|------------------------|-------------|--------------------------------------------------------------------------------|-------|

| 🐉 ISE iMPACT - [PROM File Formatter: X     | ilinx F      | lash/P         | ROM          | ]              |                        |             |                                                                                |       |

| 🐼 File Edit View Operations Output D       | ebu <u>a</u> | <u>Wi</u> ndov | v <u>H</u> e | lp             |                        |             | -                                                                              | Ξ×    |

| ê 🗋 ờ 🛃 ê 🐲 - ê 🕾 🗉 ê 🔑 🌾                  |              |                |              |                |                        |             |                                                                                |       |

| iMPACT Flows ↔                             |              |                |              |                |                        |             |                                                                                | ^     |

| Boundary Scan                              |              |                |              |                | 0×0000_0000            |             |                                                                                |       |

| 🔄 🚍 SlaveSerial                            |              |                |              |                |                        |             |                                                                                |       |

| 😭 Direct SPI<br>                           |              |                |              |                |                        |             |                                                                                |       |

| Create PROM File (PROM File Formatter)     |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        | xcf08p      |                                                                                |       |

|                                            |              |                |              |                |                        | Actoop      | xc3sd1800a                                                                     |       |

|                                            |              |                |              |                |                        |             | download.bit                                                                   |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            | 1.1.1        |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              | -              | _            | download.bit   |                        |             |                                                                                |       |

|                                            |              | R O I          | Bitstream    |                |                        |             |                                                                                |       |

| IMPACT Processes ↔ □                       |              |                | eam          |                |                        |             |                                                                                |       |

| Available Operations are:<br>Generate File | 1.1.1.1      | PROM / FLASH   |              |                |                        |             |                                                                                |       |

|                                            |              | -              |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        | *           |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                |                        |             | Generate Succeeded                                                             |       |

|                                            |              |                |              |                | 0×000F_FFFF            |             |                                                                                |       |

|                                            |              |                |              |                |                        |             |                                                                                | ~     |

|                                            | -            |                |              | PROM File Form | natter: Xilinx Flash/I | PROM        |                                                                                |       |

| Console                                    |              |                |              |                |                        |             | ······································                                         | 38×   |

| Writing file "C:\Daten\fpga.s              |              |                |              |                |                        |             |                                                                                | ^     |

| Writing file "C:\Daten\fpga.c              |              |                |              |                |                        |             |                                                                                |       |

| // *** BATCH CMD : setCurrent              | Desig        | n -v           | ersi         | on O           |                        |             |                                                                                | ~     |

|                                            |              |                |              |                |                        |             |                                                                                | >     |

| Console Errors Warnings                    |              |                |              |                |                        |             |                                                                                |       |

|                                            |              |                |              |                | PROM                   | File Genera | ation Target Xilinx PROM 8,197,280 Bits used File: fpga in Location: C:\Daten/ | 51 FL |

|                                            |              |                |              |                |                        |             |                                                                                |       |

You might now want to save your Xilinx iMPACT project settings for future use.

In the folder corresponding to the path you chose as the output file location, you should find the fpga.bin PROM file.

#### 10.2.4.3 FWU file from the PROM file

Once you have got your fpga.bin PROM file, you can proceed and generate your FWU (= FirmWare Upgrade) file. The FWU file is a ZIP archive containing 3 files:

- Bootload.ini TE0320 booting settings (see paragraph 10.2.4.3.1 Bootload.ini file)

- fpga.bin FPGA configuration PROM file

### 10.3 Configuration Using Indirect SPI Configuration Mode

Similar to the traditional configuration memories, SPI serial Flash memories must be loaded with the configuration data. SPI serial Flash memories have a single interface for programming, but there are multiple methods to deliver the data to this interface. This section discusses the hardware setup, the PROM file generation flow and the software flow for ISP (indirect in-system programming) of a Trenz Electronic TE0320 SPI serial Flash configuration PROM through the JTAG interface of a Xilinx Spartan-3A DSP FPGA using Xilinx iMPACT 11.5.

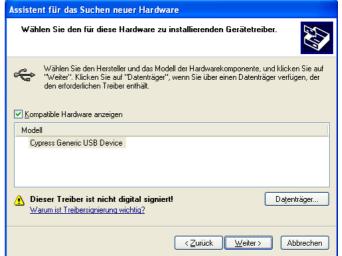

To write the SPI Flash memory, perform the following steps:

- (a) disable the master reset S1D (do not care about all other switches at write time);

- (b) connect the Xilinx platform cable to JTAG connector J2 as described in paragraph 6.3.1 JTAG connector J2;

- (c) generate or locate the FPGA bit-stream file you want to store on the memory;

- (d) prepare an SPI PROM file using the ISE iMPACT graphical software from the FPGA bit-stream file;

- (e) use the ISE iMPACT graphical software to in-system program the SPI PROM.

In order to have the module to configure from its SPI Flash memory next time it is (re)booted, ensure one of following DIP switch settings:

| switch | S1A<br>(EEPROM serial data) | S1B<br>(M2) | S1C<br>(M1) | S1D<br>(/MR master reset) | S2<br>(PS_EN)    |

|--------|-----------------------------|-------------|-------------|---------------------------|------------------|

| state  | 0 = ON                      | 0 = ON      | 0 = ON      | 1 = OFF                   | X = do note care |

| state  | 1 = OFF                     | 0 = ON      | 0 = ON      | 1 = OFF                   | FX2 PON          |

Table 31: S1 settings for booting from SPI Flash memory.

For your convenience, a reference video is available on the TrenzElectronic's Channel at YouTube.

For further reference, please read Xilinx XAPP974: Indirect Programming of SPI Serial Flash PROMs with Spartan-3A FPGAs.

## **11 Recommended Design Tools Settings**

### 11.1 DONE LED

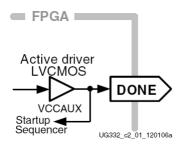

When the configuration process successfully completes, the FPGA either actively drives the DONE pin High (*DriveDone*) or allows the DONE pin to float High using either an internal or external pull-up resistor, controlled by the *DonePin* bitstream generator option. To have DONE LED D1 lit after successful FPGA configuration, DriveDone and DonePin bitstream generator options for the DONE pin have to be set to have DONE actively driving its line (see Figure 52 and Table 32).

#### Figure 52: DriveDone and DonePin set to have DONE actively driving its line.

DriveDone defines whether the DONE pin is an active driver or an open-drain output.

DonePin defines whether or not the DONE pin has an internal pull-up resistor.

| bitstream generator (BitGen) option | Setting  |

|-------------------------------------|----------|

| DriveDone                           | Yes      |

| DonePin                             | Pullnone |

Table 32: DriveDone and DonePin settings for having DONE actively driving its line.

See Xilinx UG332: Spartan-3 Generation Configuration User Guide (paragraph "DONE Pin") for additional information on these signals.

This options are set graphically in Xilinx ISE Software Project Navigator by selecting the following:

- Generate Programming File > Process Properties > Startup Options > Drive Done Pin High > check the box

- Generate Programming File > Process Properties > Configuration Options > Configuration Pin Done > float

| Xilinx ISE Project Navigator option | setting            |

|-------------------------------------|--------------------|

| Drive Done Pin High                 | $\sqrt{(checked)}$ |

| Configuration Pin Done              | Float              |

Table 33: Xilinx ISE Project Navigator settings for having DONE actively driving its line.

Consult *ISE Help* about the Process Properties of the Generate Programming File process in the Processes pane for additional information on these properties.

#### 12.2 Reference Design Summary for Xilinx Spartan-3A DSP 3400

platgen -p xc3sd3400afg676-4 -lang vhdl -lp x:/xxx/projects\_EDK/ system.mhs Release 11.5 - platgen Xilinx EDK 11.5 Build EDK LS5.70 (nt) Copyright (c) 1995-2009 Xilinx, Inc. All rights reserved. \_\_\_\_\_ Command Line: platgen -p xc3sd3400afg676-4 -lang vhdl -lp Running post-placement packing ... Design Summary: Number of errors: 0 Number of warnings: 1272 Logic Utilization: Number of Slice Flip Flops: 6,442 out of 47,744 13% Number of 4 input LUTs: 8,290 out of 47,744 17% Logic Distribution: Number of occupied Slices: 7,889 out of 23,872 338 Number of Slices containing only related logic: 7,889 out of 7,889 0% 7,889 100% Number of Slices containing unrelated logic: 0 out of \*See NOTES below for an explanation of the effects of unrelated logic. Total Number of 4 input LUTs: 8,662 out of 47,744 18% Number used as logic: 6,212 372 Number used as a route-thru: Number used for Dual Port RAMs: 1,892 (Two LUTs used per Dual Port RAM) Number used as Shift registers: 186 The Slice Logic Distribution report is not meaningful if the design is over-mapped for a non-slice resource or if Placement fails. Number of bonded IOBs: 119 out of 469 25% IOB Flip Flops: 39 IOB Master Pads: 2 2 IOB Slave Pads: Number of ODDR2s used: 44 Number of DDR ALIGNMENT = NONE 44 Number of DDR ALIGNMENT = C0 0 Number of DDR ALIGNMENT = C1 0 Number of BUFGMUXs: 24 20% 5 out of 8 12% 1 100% Number of DCMs: 1 out of 1 out of 3 out of Number of BSCANs: Number of DSP48As: 126 2% 30 out of 23% Number of RAMB16BWERs: 126 Number of BSCAN\_SPARTAN3As: 1 out of 1 100% Number of RPM macros: 1 Average Fanout of Non-Clock Nets: 3.56 \_\_\_\_\_

Initializing temperature to 85.000 Celsius. (default - Range: 0.000 to 85.000 Celsius) Initializing voltage to 1.140 Volts. (default - Range: 1.140 to 1.260 Volts)

Device speed data version: "PRODUCTION 1.33 2010-02-13".

Design Summary Report:

| Number of External IOBs                                                                                                                       | 119 out of 469 25%                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of External Input IOBs                                                                                                                 | 30                                                                                                                                                                                                                                                                                                                                 |

| Number of External Input IBUFs                                                                                                                | 30                                                                                                                                                                                                                                                                                                                                 |

| Number of LOCed External Input IBUFs                                                                                                          | 30 out of 30 100%                                                                                                                                                                                                                                                                                                                  |

| Number of External Output IOBs                                                                                                                | 43                                                                                                                                                                                                                                                                                                                                 |

| Number of External Output DIFFMs                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                  |

| Number of LOCed External Output DIFFMs                                                                                                        | s 2 out of 2 100%                                                                                                                                                                                                                                                                                                                  |

| Number of External Output DIFFSs                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                  |

| Number of LOCed External Output DIFFSs                                                                                                        | 5 2 out of 2 100%                                                                                                                                                                                                                                                                                                                  |

| Number of External Output IOBs                                                                                                                | 39                                                                                                                                                                                                                                                                                                                                 |

| Number of LOCed External Output IOBs                                                                                                          | 39 out of 39 100%                                                                                                                                                                                                                                                                                                                  |

| Number of External Bidir IOBs                                                                                                                 | 46                                                                                                                                                                                                                                                                                                                                 |

| Number of External Bidir IOBs                                                                                                                 | 46                                                                                                                                                                                                                                                                                                                                 |

| Number of LOCed External Bidir IOBs                                                                                                           | 46 out of 46 100%                                                                                                                                                                                                                                                                                                                  |

| Number of BUFGMUXs5Number of DCMs1Number of DSP48As3Number of RAMB16BWERs30Number of Slices7889Number of SLICEMs1156Number of LOCed Slices125 | 1       out of 1       100%         5       out of 24       20%         1       out of 8       12%         3       out of 126       2%         0       out of 126       23%         9       out of 23872       33%         6       out of 11936       9%         5       out of 7889       1%         3       out of 1156       7% |

Overall effort level (-ol): High Router effort level (-rl): High

\_\_\_\_\_

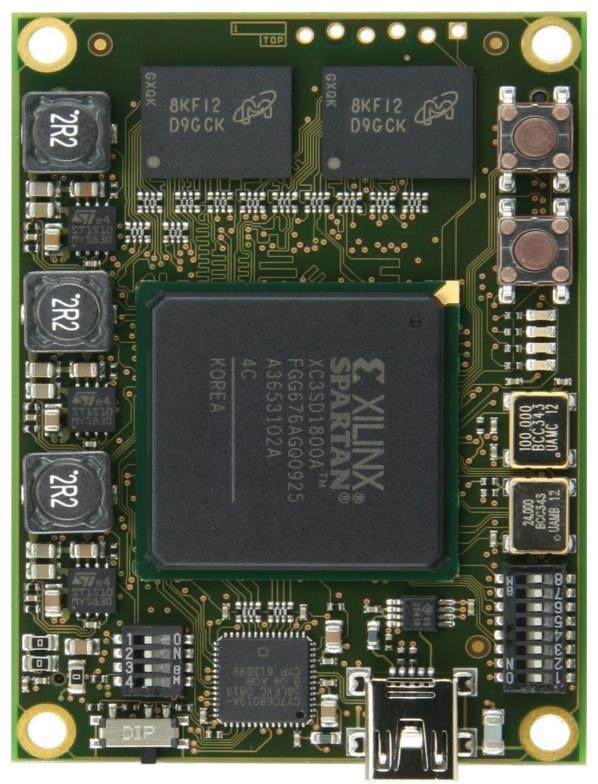

## 14.1 Top View

Figure 53: TE0320 high resolution top view.

## **17 Related Materials and References**

The following documents provide supplementary information useful with this user manual.

### 17.1 Data Sheets

- Xilinx DS485: Digital Clock Manager (DCM) Module Data Sheet This is the data sheet for the Digital Clock Manager (DCM) Module core. www.xilinx.com/support/documentation/ip\_documentation/dcm\_module.pdf

- Xilinx DS610: Spartan-3A DSP FPGA Family: Complete Data Sheet The Spartan®-3A DSP family of Field-Programmable Gate Arrays (FPGAs) solves the design challenges in most high-volume, cost-sensitive, highperformance DSP applications.

www.xilinx.com/support/documentation/data\_sheets/ds610.pdf

### 17.2 User Guides

- Xilinx UG331: Spartan-3 Generation FPGA User Guide Functional description of the Spartan®-3 generation FPGA architecture and how to use it. Includes the Spartan-3A, Spartan-3AN, Spartan-3A DSP, Spartan-3E, and Spartan-3 platforms.

www.xilinx.com/support/documentation/user\_guides/ug331.pdf

- Xilinx UG332: Spartan-3 Generation Configuration User Guide Describes the configuration features of the Spartan®-3 Generation FPGAs. Includes the Spartan-3A, Spartan-3AN, Spartan-3A DSP, Spartan-3E, and Spartan-3 FPGA families.

www.xilinx.com/support/documentation/user\_guides/ug332.pdf

EZ-USB® Technical Reference Manual (TRM) www.cypress.com/?rID=14667

### 17.3 Tutorials

- (Xilinx) ISE (10.1) In-Depth Tutorial Chapter 7: iMPACT Tutorial www.xilinx.com/direct/ise10\_tutorials/ise10tut.pdf

- Xilinx UG695: ISE In-Depth Tutorial Chapter 7: iMPACT Tutorial http://www.xilinx.com/support/documentation/sw\_manuals/xilinx11/ise11tut.pdf

### **17.4 Application Notes**

- Xilinx XAPP104: A Quick JTAG ISP Checklist Most Xilinx CPLDs, PROMs, and FPGAs have an IEEE Standard 1149.1 (JTAG) port. Xilinx devices with a JTAG port are in-system programmable (ISP) through the JTAG port. The ISP feature is beneficial for fast prototype development. This application note describes a short list of considerations needed to get the best performance from your ISP designs. www.xilinx.com/support/documentation/application\_notes/xapp104.pdf

- Xilinx XAPP974: Indirect Programming of SPI Serial Flash PROMs with Spartan-3A FPGAs

### 18.4 Signal Integrity Considerations

Traces of differential signals pairs are NOT routed symmetrically (as symmetric pairs).

Traces of differential signals pairs are NOT routed with equal length. For applications where traces length has to be matched or timing differences have to be compensated, Table 42 and Table 43 list the trace length of I/O signal lines measured from FPGA balls to B2B connector pins.

Traces of differential signals pairs are routed with a differential impedance between the two traces of 60 ohm.

Pairs of pins that form a differential I/O pair appear colored together in the table. An electronic version of these pin-out tables are available for download from the Trenz Electronic support area of the web site.