# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 150MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, QSPI, SDHC, SPI, UART/USART, USB             |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                         |

| Number of I/O              | 120                                                                     |

| Program Memory Size        | 2MB (2M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1M x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 16b SAR; D/A 2x6b, 1x12b                                            |

| Oscillator Type            | External, Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 169-LFBGA                                                               |

| Supplier Device Package    | 169-MAPBGA (9x9)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk27fn2m0avmi15 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Security

- Hardware random-number generator

- Memory Mapped Crypto Acceleration Unit(MMCAU): DES, 3-DES, AES, SHA-1, SHA-256 and MD5 accelerator

- Cyclic Redundancy Check (CRC)

#### **Target Applications**

- Wearables

- Low-end graphic display system

- Cost-optimized multi-standard wireless smart home hubs

- Home Automation devices

- Consumer accessories

- Independent V<sub>BAT</sub> (RTC): 1.71 V–3.6 V

- I/O Voltage range (V<sub>DD</sub>): 1.71 V–3.6 V

#### **Communication interfaces**

- Two USB controllers:Crystal-less Full-/low-speed + transceiver Host and Device; High-/Full-/low-speed + PHY Host and Device

- Secure Digital Host Controller (SDHC)

- Two I2S modules, four I2C modules and five Low-Power UART modules

- Four SPI modules (SPI3 supports more than 40 Mbps)

- 32-ch Programmable module (FlexIO) to emulate various serial, parallel or custom interfaces

### Ordering Information 1

| Part Number     | Embedded Memory |      | Package Type | Maximum number of |

|-----------------|-----------------|------|--------------|-------------------|

|                 | Flash           | SRAM |              | I\O's             |

| MK27FN2M0AVMI15 | 2 MB            | 1 MB | 169 MAPBGA   | 120               |

1. To confirm current availability of orderable part numbers, go to http://www.nxp.com and perform a part number search.

### **Device Revision Number**

| Device Mask Set Number | SIM_SDID[REVID] | JTAG ID Register[PRN] |

|------------------------|-----------------|-----------------------|

| 3N96T                  | 0011            | 0011                  |

### **Related Resources**

| Туре                | Description                                                                                                      | Resource                                    |

|---------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Fact Sheet          | The Fact Sheet gives overview of the product key features and its uses.                                          | K2x Fact Sheet                              |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device. | K27P169M150SF5RM <sup>1</sup>               |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                       | This document                               |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.         | KINETIS_K_3N96T <sup>1</sup>                |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                             | MAPBGA 169-pin:<br>98ASA00628D <sup>1</sup> |

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

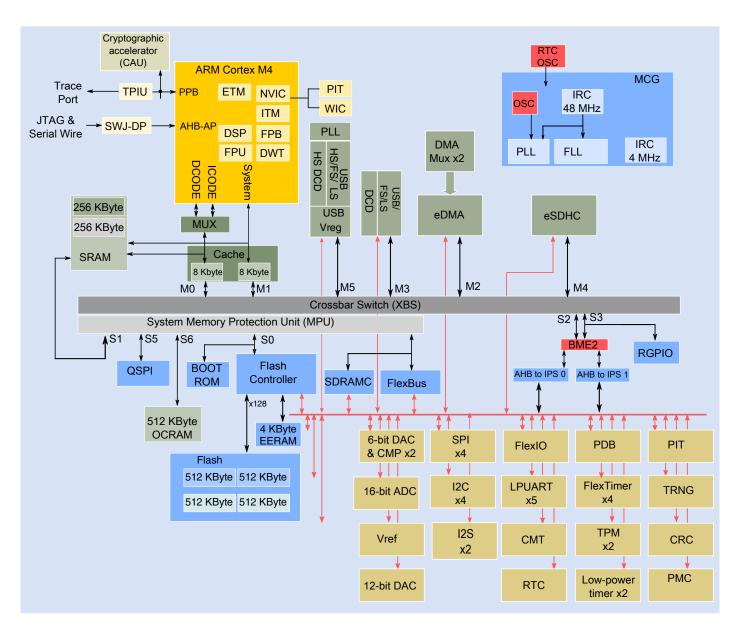

Figure 1. K27F Block Diagram

#### General

- All I/O pins are internally clamped to V<sub>SS</sub> through an ESD protection diode. There is no diode connection to V<sub>DD</sub> or V<sub>DDIO\_E</sub>. If V<sub>IN</sub> is less than -0.3V, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(-0.3-V<sub>IN</sub>)/II<sub>ICIO</sub>I. The actual resistor value should be an order of magnitude higher to tolerate transient voltages.

- 2. Open drain outputs must be pulled to VDD.

## 2.2.2 HVD, LVD and POR operating requirements Table 2. V<sub>DD</sub> supply HVD, LVD and POR operating requirements

| Symbol             | Description                                                                   | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------------------------|------|------|------|------|-------|

| V <sub>HVDH</sub>  | High Voltage Detect (High Trip Point)                                         | _    | 3.72 | —    | V    |       |

| V <sub>HVDL</sub>  | High Voltage Detect (Low Trip Point)                                          | —    | 3.46 | —    | V    |       |

| V <sub>POR</sub>   | Falling VDD POR detect voltage                                                | 0.8  | 1.1  | 1.5  | V    |       |

| $V_{LVDH}$         | Falling low-voltage detect threshold — high range (LVDV=01)                   | 2.48 | 2.56 | 2.64 | V    |       |

| V <sub>LVW1H</sub> | Low-voltage warning thresholds — high range                                   | 2.62 | 2.70 | 2.78 | V    | 1     |

| V <sub>LVW2H</sub> | Level 1 falling (LVWV=00)                                                     | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | Level 2 falling (LVWV=01)                                                     | 2.82 | 2.90 | 2.98 | V    |       |

| V <sub>LVW4H</sub> | <ul><li>Level 3 falling (LVWV=10)</li><li>Level 4 falling (LVWV=11)</li></ul> | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range                     |      | 60   | _    | mV   |       |

| $V_{LVDL}$         | Falling low-voltage detect threshold — low range (LVDV=00)                    | 1.54 | 1.60 | 1.66 | V    |       |

| V <sub>LVW1L</sub> | Low-voltage warning thresholds — low range                                    | 1.74 | 1.80 | 1.86 | V    | 1     |

| V <sub>LVW2L</sub> | Level 1 falling (LVWV=00)                                                     | 1.84 | 1.90 | 1.96 | v    |       |

| V <sub>LVW3L</sub> | Level 2 falling (LVWV=01)                                                     | 1.94 | 2.00 | 2.06 | V    |       |

| V <sub>LVW4L</sub> | Level 3 falling (LVWV=10)                                                     | 2.04 | 2.10 | 2.16 | V    |       |

|                    | Level 4 falling (LVWV=11)                                                     | -    |      |      |      |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis —<br>low range                   | _    | 40   | -    | mV   |       |

| $V_{BG}$           | Bandgap voltage reference                                                     | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed                        | 900  | 1000 | 1100 | μs   |       |

1. Rising threshold is the sum of falling threshold and hysteresis voltage

| Symbol                 | Description                                                                                              | Min. | Тур. | Max. | Unit | Notes |

|------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                        | • @ 85°C                                                                                                 | _    | 4.1  | 10.7 |      |       |

|                        | • @ 105°C                                                                                                | _    | 6.9  | 16.9 |      |       |

| I <sub>DD_PSTOP2</sub> | Stop mode current with partial stop 2 clocking option - core and system disabled / 10.5 MHz bus at 3.0 V |      |      |      | _    | 3     |

|                        | • @ 25°C<br>• @ 70°C                                                                                     | _    | 6.6  | 19.8 | mA   |       |

|                        | • @ 85°C                                                                                                 | _    | 12.4 | 33.1 |      |       |

|                        | • @ 105°C                                                                                                | _    | 15.9 | 41.5 |      |       |

|                        |                                                                                                          | _    | 19.0 | 46.6 |      |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current at 3.0 V — all                                                          |      |      |      |      | 6     |

| 55-11.11               | peripheral clocks disabled<br>• @ 25°C                                                                   | _    | 0.9  | 2.7  | mA   |       |

|                        | • @ 70°C                                                                                                 | _    | 2.5  | 6.7  |      |       |

|                        | • @ 85°C                                                                                                 | _    | 3.8  | 9.9  |      |       |

|                        | • @ 105°C                                                                                                | _    | 6.5  | 16.0 |      |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current at 3.0 V — all peripheral clocks enabled                                |      |      |      |      | 6     |

|                        | • @ 25°C                                                                                                 | _    | 1.4  | 4.2  | mA   |       |

|                        | • @ 70°C<br>• @ 85°C                                                                                     | _    | 3.0  | 8.0  |      |       |

|                        | • @ 105°C                                                                                                | _    | 4.3  | 11.2 |      |       |

|                        |                                                                                                          | _    | 7.0  | 17.2 |      |       |

| IDD_STOP               | Stop mode current at 3.0 V                                                                               |      |      |      |      |       |

|                        | • @ 25°C                                                                                                 | _    | 1.0  | 2.8  | mA   |       |

|                        | • @ 70°C                                                                                                 | _    | 3.9  | 9.9  |      |       |

|                        | • @ 85°C                                                                                                 | _    | 6.0  | 15.0 |      |       |

|                        | • @ 105°C                                                                                                | _    | 10.0 | 24.4 |      |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 3.0 V                                                                |      |      |      |      |       |

| •עע_ענץ                | • @ 25°C                                                                                                 | _    | 0.5  | 1.4  | mA   |       |

|                        | • @ 70°C                                                                                                 |      |      |      |      |       |

|                        | • @ 85°C                                                                                                 |      | 2.4  | 5.8  |      |       |

|                        | • @ 105°C                                                                                                | _    | 3.7  | 8.7  |      |       |

|                        |                                                                                                          |      | 6.3  | 14.1 |      |       |

| I <sub>DD_LLS3</sub>   | Low leakage stop mode current at 3.0 V                                                                   |      |      |      |      |       |

|                        | • @ 25°C                                                                                                 | _    | 19.5 | 30.0 | μA   |       |

Table 6. Power consumption operating behaviors (through VDD) (continued)

| Symbol               | Description                                                     | Min. | Тур.  | Max.  | Unit | Notes |

|----------------------|-----------------------------------------------------------------|------|-------|-------|------|-------|

|                      | • @ 70°C                                                        | —    | 0.595 | 0.750 |      |       |

|                      | <ul> <li>@ 85°C</li> <li>@ 105°C</li> </ul>                     | _    | 0.989 | 1.30  |      |       |

|                      |                                                                 |      | 2.2   | 2.8   |      |       |

| I <sub>DD_VBAT</sub> | Average current when CPU is not accessing RTC registers @ 1.8 V |      |       |       |      | 9     |

|                      | • @ 25°C                                                        | _    | 0.436 | 0.489 | μA   |       |

|                      | • @ 70°C                                                        | —    | 0.724 | 0.897 |      |       |

|                      | • @ 85°C                                                        | _    | 1.1   | 1.4   |      |       |

|                      | • @ 105°C                                                       |      | 2.0   | 2.6   |      |       |

Table 6. Power consumption operating behaviors (through VDD) (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device.

- 2. 120 MHz core and system clock, 60 MHz bus and FlexBus clock, and 24 MHz flash clock. MCG configured for PEE mode.

- 3. MCG configured for PEE mode.

- 4. 150 MHz core and system clock, 50 MHz bus and FlexBus clock, and 25 MHz flash clock. MCG configured for PEE mode.

- 5. 25 MHz core and system clock, 25 MHz bus and FlexBus clock, and 25 MHz flash clock. MCG configured for FEI mode.

- 6. 4 MHz core, system, FlexBus, and bus clock and 1 MHz flash clock. MCG configured for BLPE mode using an 8MHz external reference clock. Code executing from flash.

- 7. MCG configured for BLPE mode using an 8MHz external reference clock.

- 8. By default, this mode has only 32 KB of SRAM enabled.

- 9. Includes 32 kHz oscillator current and RTC operation.

Below table list the current consumption adders for different SRAM configurations from the LLS2/VLLS2 (TYP) IDD values using a 32 KB SRAM retention referenced in Table 6.

Table 7. LLS2/VLLS2 additional Typical IDD current consumption Adders

|       | RAM array retained | @ 25°C | @ 85°C | @ 105°C | Unit |

|-------|--------------------|--------|--------|---------|------|

| LLS2  | RAM2: 32 KB        | 0.5    | 10.8   | 21.3    | μA   |

|       | RAM3: 32 KB        | 0.5    | 11.0   | 21.5    | μA   |

|       | RAM4: 32 KB        | 0.4    | 10.7   | 21.0    | μA   |

|       | RAM5: 128 KB       | 1.4    | 28.1   | 57.6    | μA   |

|       | RAM6: 64 KB        | 0.6    | 15.2   | 30.5    | μA   |

|       | RAM7: 192 KB       | 2.1    | 41.1   | 85.1    | μA   |

|       | RAM8: 256 KB       | 2.8    | 53.0   | 109.9   | μA   |

|       | RAM9: 256 KB       | 2.3    | 53.5   | 110.9   | μA   |

| VLLS2 | RAM2: 32 KB        | 0.5    | 9.1    | 19.7    | μA   |

|       | RAM3: 32 KB        | 0.5    | 8.5    | 18.0    | μA   |

|       | RAM4: 32 KB        | 0.5    | 8.1    | 16.8    | μA   |

| Symbol           | Description                                                                                                                                                                                                           | Temperature (°C) |     |     |     |     | Unit |    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-----|------|----|

|                  |                                                                                                                                                                                                                       | -40              | 25  | 50  | 70  | 85  | 105  |    |

|                  | data at 115200 baud rate. Includes selected clock source power consumption.                                                                                                                                           | 66               | 66  | 66  | 66  | 66  | 66   |    |

|                  | MCGIRCLK (4 MHz internal reference clock)                                                                                                                                                                             | 214              | 234 | 246 | 254 | 260 | 268  |    |

|                  | OSCERCLK (4 MHz external crystal)                                                                                                                                                                                     |                  |     |     |     |     |      |    |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set and device is placed in VLPx, LLS, or VLLSx mode.                                                                                                                                  | 45               | 45  | 45  | 45  | 45  | 45   | μA |

| I <sub>ADC</sub> | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode.<br>ADC is configured for low power mode using the internal clock and continuous conversions. | 366              | 366 | 366 | 366 | 366 | 366  | μΑ |

Table 8. Low power mode peripheral adders — typical value (continued)

# 2.2.6 Electromagnetic Compatibility (EMC) specifications

EMC measurements to IC-level IEC standards are available from NXP on request.

# 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions.

- 1. Go to nxp.com

- 2. Perform a keyword search for "EMC design."

# 2.2.8 Capacitance attributes

### Table 9. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

# 2.3 Switching specifications

| Symbol | Description                                                                                                 | Min. | Max. | Unit | Notes |

|--------|-------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled) — Asynchronous path | 50   | _    | ns   | 3     |

|        | External RESET_b input pulse width (digital glitch filter disabled)                                         | 100  | -    | ns   |       |

|        | Port rise and fall time (high drive strength)                                                               |      |      |      | 4, 5  |

|        | Slew enabled                                                                                                | _    | 34   | ns   |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                                                                                | _    | 16   | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 |      |      |      |       |

|        | Slew disabled                                                                                               | _    | 10   | ns   |       |

|        | • $1.71 \le V_{DD} \le 2.7 \text{ V}$                                                                       | _    | 8    | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6 V$                                                                                |      |      |      |       |

|        | Port rise and fall time (low drive strength)                                                                |      |      |      | 6, 7  |

|        | Slew enabled                                                                                                | _    | 34   | ns   |       |

|        | • $1.71 \le V_{DD} \le 2.7 \text{ V}$                                                                       | _    | 16   | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6 \text{ V}$                                                                        |      |      |      |       |

|        | Slew disabled                                                                                               |      | 7    | ns   |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7 V                                                                            |      | 5    | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6 \text{ V}$                                                                        |      | 0    |      |       |

|        | Port rise and fall time (high drive strength)                                                               |      |      |      | 5, 8  |

|        | Slew enabled                                                                                                | _    | 34   | ns   |       |

|        | • $1.71 \le V_{DDIO_E} \le 2.7 \text{ V}$                                                                   |      | 16   | ns   |       |

|        | • $2.7 \le V_{DDIO_E} \le 3.6 \text{ V}$                                                                    |      |      |      |       |

|        | Slew disabled                                                                                               | _    | 7    | ns   |       |

|        | • $1.71 \le V_{DDIO_E} \le 2.7 \text{ V}$                                                                   | _    | 5    | ns   |       |

|        | • $2.7 \le V_{DDIO_E} \le 3.6 \text{ V}$                                                                    |      | 5    |      |       |

|        | Port rise and fall time (low drive strength)                                                                |      |      |      | 7, 8  |

|        | Slew enabled                                                                                                | _    | 34   | ns   |       |

|        | • $1.71 \le V_{DDIO_E} \le 2.7 \text{ V}$                                                                   | _    | 16   | ns   |       |

|        | • $2.7 \le V_{DDIO_E} \le 3.6 \text{ V}$                                                                    |      |      |      |       |

|        | Slew disabled                                                                                               |      | 7    | ns   |       |

|        | • $1.71 \le V_{DDIO_E} \le 2.7 \text{ V}$                                                                   |      | 5    | ns   |       |

|        | <ul> <li>2.7 ≤ V<sub>DDIO</sub> E ≤ 3. 6V</li> </ul>                                                        |      | 5    |      |       |

### Table 11. General switching specifications (continued)

1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry in run modes.

2. The greater synchronous and asynchronous timing must be met.

3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

4. PTB0, PTB1, PTC3, PTC4, PTD4, PTD5, PTD6, and PTD7.

#### General

- 5. 75 pF load.

- 6. Ports A, B, C, and D.

- 7. 25 pF load.

- 8. Port E pins only.

# 2.4 Thermal specifications

# 2.4.1 Thermal operating requirements

### Table 12. Thermal operating requirements (for V-Temp range)

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed the maximum. The simplest method to determine  $T_J$  is:

$T_J = T_A + R\theta_{JA} \ x$  chip power dissipation

# 2.4.2 Thermal attributes

### Table 13. Thermal attributes

| Board type        | Symbol            | Description                                                                                           | 169<br>MAPBGA | Unit | Notes |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------|---------------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                          | 56.8          | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                          | 27.1          | °C/W | 1     |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                      | 41            | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                      | 22.4          | °C/W | 1     |

| —                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                 | 10.4          | °C/W | 2     |

| —                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                  | 7.1           | °C/W | 3     |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization parameter,<br>junction to package top outside center<br>(natural convection) | 0.2           | °C/W | 4     |

- 1. Determined according to JEDEC Standard JESD51-2, *Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air)* with the single layer board horizontal. Board meets JESD51-9 specification.

- Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions – Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

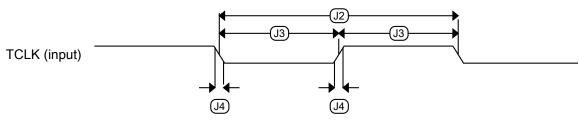

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

| J4     | TCLK rise and fall times                           | —    | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | —    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 2.0  | —    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 30.6 | ns   |

| J8     | TCLK low to boundary scan output high-Z            | _    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1.0  | —    | ns   |

| J11    | TCLK low to TDO data valid                         | _    | 19.0 | ns   |

| J12    | TCLK low to TDO high-Z                             |      | 17.0 | ns   |

| J13    | TRST assert time                                   | 100  | —    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    | —    | ns   |

Table 16. JTAG full voltage range electricals (continued)

Figure 6. Test clock input timing

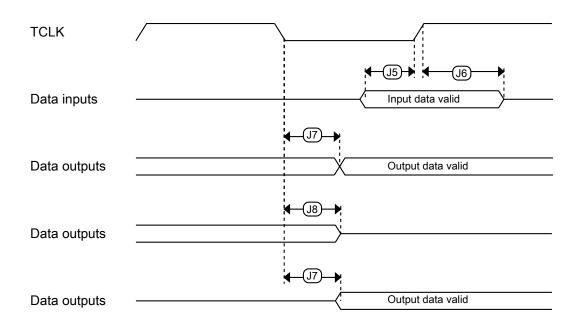

### Figure 7. Boundary scan (JTAG) timing

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              | • 24 MHz                                                                                               |      | 1.5             | —    | mA   |       |

|                              | • 32 MHz                                                                                               |      |                 |      |      |       |

| IDDOSC                       | Supply current — high gain mode (HGO=1)                                                                |      |                 |      |      | 1     |

|                              | • 32 kHz                                                                                               | —    | 7.5             | _    | μA   |       |

|                              | • 4 MHz                                                                                                |      | 500             | —    | μA   |       |

|                              | • 8 MHz (RANGE=01)                                                                                     |      | 650             | _    | μA   |       |

|                              | • 16 MHz                                                                                               |      | 2.5             | _    | mA   |       |

|                              | • 24 MHz                                                                                               |      | 3.25            | _    | mA   |       |

|                              | • 32 MHz                                                                                               | _    | 4               | _    | mA   |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 |      |                 |      |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  |      |                 |      |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | —    | —               | —    | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | —    | 10              | _    | MΩ   |       |

|                              | Feedback resistor — high-frequency, low-power mode (HGO=0)                                             | _    |                 |      | MΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | _    | 1               |      | MΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power<br>mode (HGO=0)                                             | —    |                 |      | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | _    | 200             |      | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               |      |                 |      | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | _    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | —    | V    |       |

| Table 19. | Oscillator | <b>DC</b> electrical s | pecifications ( | (continued) |

|-----------|------------|------------------------|-----------------|-------------|

|-----------|------------|------------------------|-----------------|-------------|

1.  $V_{DD}$ =3.3 V, Temperature =25 °C, Internal capacitance = 20 pf 2. See crystal or resonator manufacturer's recommendation

The following table lists the QuadSPI delay chain read/write settings. Refer the device reference manual for register and bit descriptions.

| Mode       |                          |                           | Notes                    |                         |                                     |

|------------|--------------------------|---------------------------|--------------------------|-------------------------|-------------------------------------|

|            | QuadSPI_MCR[DQ<br>S_EN]  | QuadSPI_SOCCR[<br>SOCCFG] | QuadSPI_MCR[SC<br>LKCFG] | QuadSPI_FLSHCR[<br>TDH] |                                     |

| SDR        | Yes                      | 3Fh                       | 5                        | No                      | Delay of 63<br>buffer and 64<br>mux |

| DDR        | Yes                      | 3Fh                       | 1                        | 2                       | Delay of 63<br>buffer and 64<br>mux |

| Hyperflash | RDS driven from<br>Flash | 0h                        | No                       | 2                       | Delay of 1 mux                      |

Table 23. QuadSPI delay chain read/write settings

## SDR mode

Figure 10. QuadSPI input timing (SDR mode) diagram

# NOTE

- The below timing values are with default settings for sampling registers like QuadSPI\_SMPR.

- A negative time indicates the actual capture edge inside the device is earlier than clock appearing at pad.

- The below timing are for a load of 15 pf (1.8 V) and 35 pf (3 V) or output pads

#### Peripheral operating requirements and behaviors

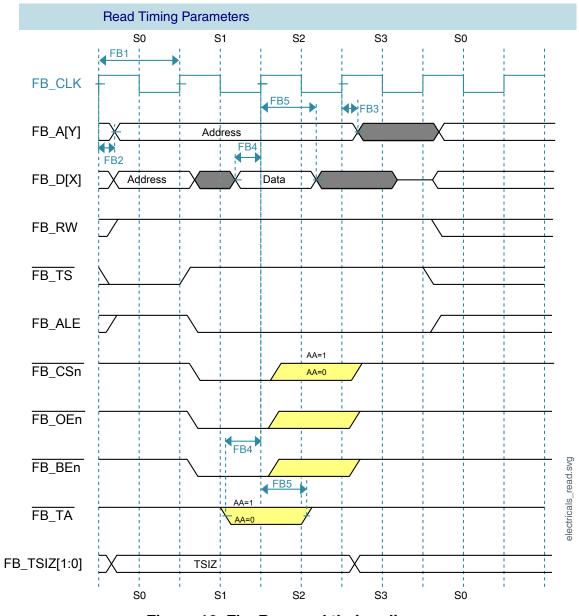

Figure 16. FlexBus read timing diagram

3. D7 and D8 are for write cycles only.

| NUM             | Characteristic <sup>1</sup>          | Symbol              | Min    | Max  | Unit |

|-----------------|--------------------------------------|---------------------|--------|------|------|

|                 | Operating voltage                    | 2.7                 | 3.6    | V    |      |

|                 | Frequency of operation               | —                   | CLKOUT | MHz  |      |

| D0              | Clock period                         | 1/CLKOUT            | —      | ns   | 2    |

| D1              | CLKOUT high to SDRAM address valid   | t <sub>CHDAV</sub>  | -      | 11.1 | ns   |

| D2              | CLKOUT high to SDRAM control valid   | t <sub>CHDCV</sub>  |        | 11.1 | ns   |

| D3              | CLKOUT high to SDRAM address invalid | t <sub>CHDAI</sub>  | 1.0    | -    | ns   |

| D4              | CLKOUT high to SDRAM control invalid | t <sub>CHDCI</sub>  | 1.0    | -    | ns   |

| D5              | SDRAM data valid to CLKOUT high      | t <sub>DDVCH</sub>  | 11.3   | -    | ns   |

| D6              | CLKOUT high to SDRAM data invalid    | t <sub>CHDDI</sub>  | 1.0    | -    | ns   |

| D7 <sup>3</sup> | CLKOUT high to SDRAM data valid      | t <sub>CHDDVW</sub> | -      | 11.1 | ns   |

| D8 <sup>3</sup> | CLKOUT high to SDRAM data invalid    | t <sub>CHDDIW</sub> | 1.0    | -    | ns   |

### Table 37. SDRAM Timing (Limited voltage range)

1. All timing specifications are based on taking into account, a 25 pF load on the SDRAM output pins.

2. CLKOUT is same as FB\_CLK, maximum frequency can be 75 MHz

3. D7 and D8 are for write cycles only.

Following figure shows an SDRAM write cycle.

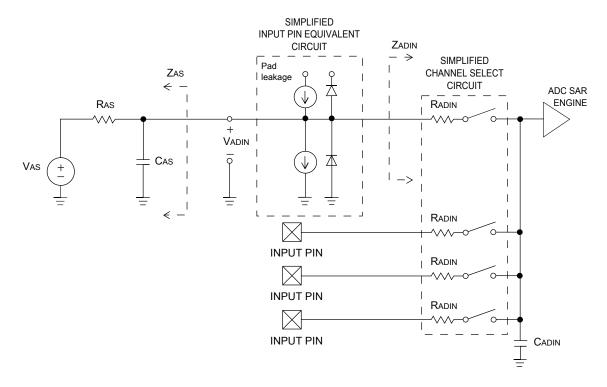

| Symbol            | Description                               | Conditions                                                                                    | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                            | Absolute                                                                                      | 1.71             | _                 | 3.6              | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                            | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> )                                | -100             | 0                 | +100             | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to $V_{SS}$ ( $V_{SS} - V_{SSA}$ )                                                      | -100             | 0                 | +100             | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high                |                                                                                               | 1.13             | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    |       |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                                               | V <sub>SSA</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    |       |

| V <sub>ADIN</sub> | Input voltage                             | 16-bit differential mode                                                                      | VREFL            |                   | 31/32 ×<br>VREFH | V    |       |

|                   |                                           | All other modes                                                                               | VREFL            | —                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input                                     | 16-bit mode                                                                                   | _                | 8                 | 10               | pF   |       |

|                   | capacitance                               | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>                                         | —                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                                               | _                | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance<br>(external) | 13-bit / 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz                                            | _                | _                 | 5                | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | ≤ 13-bit mode                                                                                 | 1.0              |                   | 18.0             | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | 16-bit mode                                                                                   | 2.0              | _                 | 12.0             | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion                            | ≤ 13-bit modes                                                                                |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                                                     | 20.000           | —                 | 818.330          | kS/s |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time                              |                  |                   |                  |      |       |

| C <sub>rate</sub> | ADC conversion                            | 16-bit mode                                                                                   |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 37.037           | —                 | 461.467          | kS/s |       |

### 3.4.1.1 16-bit ADC operating conditions Table 38. 16-bit ADC operating conditions

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 20. ADC input impedance equivalency diagram

# 3.4.1.2 16-bit ADC electrical characteristics

|                      |                        |                                      |              | DDA,              |                        | 33A/             |                         |

|----------------------|------------------------|--------------------------------------|--------------|-------------------|------------------------|------------------|-------------------------|

| Symbol               | Description            | Conditions <sup>1</sup>              | Min.         | Typ. <sup>2</sup> | Max.                   | Unit             | Notes                   |

| I <sub>DDA_ADC</sub> | Supply current         |                                      | 0.215        | —                 | 1.7                    | mA               | 3                       |

|                      | ADC asynchronous       | • ADLPC = 1, ADHSC = 0               | 1.2          | 2.4               | 3.9                    | MHz              | t <sub>ADACK</sub> = 1/ |

|                      | clock source           | • ADLPC = 1, ADHSC = 1               | 2.4          | 4.0               | 6.1                    | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub>   |                        | • ADLPC = 0, ADHSC = 0               | 3.0          | 5.2               | 7.3                    | MHz              |                         |

|                      |                        | • ADLPC = 0, ADHSC = 1               | 4.4          | 6.2               | 9.5                    | MHz              |                         |

|                      | Sample Time            | See Reference Manual chapter         | for sample t | imes              |                        |                  |                         |

| TUE                  | Total unadjusted       | 12-bit modes                         | _            | ±4                | ±6.8                   | LSB <sup>4</sup> | 5                       |

|                      | error                  | <ul> <li>&lt;12-bit modes</li> </ul> | —            | ±1.4              | ±2.1                   |                  |                         |

| DNL                  | Differential non-      | 12-bit modes                         | _            | ±0.7              | -1.1 to                | LSB <sup>4</sup> | 5                       |

|                      | linearity              | <ul> <li>&lt;12-bit modes</li> </ul> | _            | ±0.2              | +1.9<br>-0.3 to<br>0.5 |                  |                         |

| INL                  | Integral non-linearity | 12-bit modes                         | —            | ±1.0              | –2.7 to<br>+1.9        | LSB <sup>4</sup> | 5                       |

| Table 39. | 16-bit ADC | characteristics | (V <sub>REFH</sub> = | $V_{DDA}$ , | V <sub>REFL</sub> = | V <sub>SSA</sub> ) |

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

## 3.4.2 CMP and 6-bit DAC electrical specifications Table 40. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  |      | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | _                     | _    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | —    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | —    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     | —    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | —                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          |                       |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> |                       |      | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   |                       | 7    | —               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  | _    | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  |      | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB =  $V_{reference}/64$

# 3.6.2 USB Full Speed Transceiver and High Speed PHY specifications

This section describes the USB0 port Full Speed/Low Speed transceiver and USB1 port USB-PHY High Speed Phy parameters. The high speed phy is capable of full and low speed as well.

The USB0 (FS/LS Transceiver) and USB1 ((USB HS/FS/LS) meet the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 Specification with the amendments below.

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

- On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification

- Revision 2.0 version 1.1a July 27, 2012

- Battery Charging Specification (available from USB-IF)

- Revision 1.2 (including errata and ECNs through March 15, 2012), March 15, 2012

USB1\_VBUS pin is a detector function which is 5v tolerant and complies with the above specifications without needing any external voltage division components.

# 3.6.3 USB DCD electrical specifications

### Table 46. USB DCD electrical specifications

| Symbol                                         | Description                                                 | Min. | Тур. | Max. | Unit |

|------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| V <sub>DP_SRC</sub> ,<br>V <sub>DM_SRC</sub>   | USB_DP and USB_DM source voltages (up to 250 $\mu\text{A})$ | 0.5  | —    | 0.7  | V    |

| V <sub>LGC</sub>                               | Threshold voltage for logic high                            | 0.8  | —    | 2.0  | V    |

| I <sub>DP_SRC</sub>                            | USB_DP source current                                       | 7    | 10   | 13   | μA   |

| I <sub>DM_SINK</sub> ,<br>I <sub>DP_SINK</sub> | USB_DM and USB_DP sink currents                             | 50   | 100  | 150  | μA   |

| Symbol               | Description                                        | Min.  | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------|-------|------|------|------|

| R <sub>DM_DWN</sub>  | D- pulldown resistance for data pin contact detect | 14.25 | —    | 24.8 | kΩ   |

| V <sub>DAT_REF</sub> | Data detect voltage                                | 0.25  | 0.33 | 0.4  | V    |

Table 46.USB DCD electrical specifications<br/>(continued)

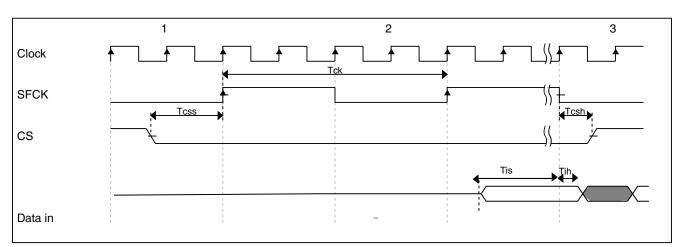

# 3.6.4 DSPI switching specifications (limited voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                                 | Min.                          | Max.                      | Unit | Notes |

|-----|---------------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                           | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation                      | —                             | 30                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time                  | 2 x t <sub>BUS</sub>          | —                         | ns   |       |

| DS2 | DSPI_SCK output high/low time               | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay           | (t <sub>BUS</sub> x 2) –<br>2 | —                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCS <i>n</i> invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | —                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid                 | _                             | 15.0                      | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid               | 1.0                           | —                         | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup            | 15.8                          | —                         | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold             | 0                             | —                         | ns   |       |

Table 47. Master mode DSPI timing (limited voltage range)

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

| Characteristic                                                                                     | Symbol                | Standard Mode    |                   | Fast Mode                          |                  | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                | _                 | 0.6                                | —                | μs   |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | _                 | 1.25                               | —                | μs   |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | _                 | 0.6                                | —                | μs   |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | —                 | 0.6                                | —                | μs   |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 01               | 3.45 <sup>2</sup> | 0 <sup>3</sup>                     | 0.9 <sup>1</sup> | μs   |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>4</sup> | —                 | 100 <sup>2, 5</sup>                | —                | ns   |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | —                | 1000              | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>5</sup> | 300              | ns   |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | —                | μs   |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | _                 | 1.3                                | —                | μs   |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |

| Table 55. | I <sup>2</sup> C timing | (continued) |

|-----------|-------------------------|-------------|

|-----------|-------------------------|-------------|

- 1. The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

- 2. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 3. Input signal Slew = 10 ns and Output Load = 50 pF

- 4. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 5. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement  $t_{SU; DAT} \ge 250$  ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line  $t_{rmax} + t_{SU; DAT} = 1000 + 250 = 1250$  ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 6.  $C_b$  = total capacitance of the one bus line in pF.

| Table 56. | I <sup>2</sup> C 1 | Mbps | timing |

|-----------|--------------------|------|--------|

|-----------|--------------------|------|--------|

|                                                                                              | -                     | -                                    |                |      |

|----------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|----------------|------|

| Characteristic                                                                               | Symbol                | Minimum                              | Maximum        | Unit |

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                    | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                                 |                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                  | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                                 | _              | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                                 | —              | μs   |

| Data hold time for $I_2C$ bus devices                                                        | t <sub>HD</sub> ; DAT | 0                                    | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                   | _              | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub> , <sup>2</sup> | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup>   | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                                 | —              | μs   |

| Rev. No. | Date    | Substantial Changes |

|----------|---------|---------------------|

| 0        | 08/2017 | Initial release     |

## Table 66. Revision History