Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 120MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 95                                                                                   |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 128K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 53x16b; D/A 2x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LBGA                                                                             |

| Supplier Device Package    | 144-MAPBGA (13x13)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk61fn1m0caa12r              |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Terminology and guidelines

| Field | Description                 | Values                                                    |

|-------|-----------------------------|-----------------------------------------------------------|

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul> |

| PP    | Package identifier          | • AA = 143 WLCSP                                          |

| CC    | Maximum CPU frequency (MHz) | • 12 = 120 MHz                                            |

| Ν     | Packaging type              | • R = Tape and reel                                       |

# 2.4 Example

This is an example part number:

MK61FN1M0CAA12

# **3** Terminology and guidelines

# 3.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |  |  |  |  |  |  |

|                       | <ul> <li>Operating ratings apply during operation of the chip.</li> <li>Handling ratings apply when the chip is not powered.</li> </ul>                                                                                             |  |  |  |  |  |  |

|                       | <b>NOTE:</b> The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                  |  |  |  |  |  |  |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                       |  |  |  |  |  |  |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |  |  |  |  |  |  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |  |  |  |  |  |  |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |  |  |  |  |  |  |

|                       | NOTE: Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                       |  |  |  |  |  |  |

reminology and guidelines

# 3.2 Examples

### Operating rating:

| Symbol          | Description                  | Min.     | Max. | Unit |

|-----------------|------------------------------|----------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 JAM | 1.2  | V    |

|                 | •                            |          |      | •    |

## **Operating requirement:**

| Operating requ  | irement:                     |      | 9    |      |

|-----------------|------------------------------|------|------|------|

| Symbol          | Description                  | Min. | Max. | Unit |

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

|                 | •                            |      | •    |      |

## Operating behavior that includes a typical value:

| Symbol          | Description                                    | Min.  | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|-------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10 AM | 70   | 130  | μA   |

# 3.3 Typical-value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | D°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

## 5.2.2 LVD and POR operating requirements Table 2. LVD and POR operating requirements

| Symbol                                                                               | Description                                                                                                                                                             | Min.                         | Тур.                         | Max.                         | Unit             | Notes |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------|-------|

| V <sub>POR</sub>                                                                     | Falling VDD POR detect voltage                                                                                                                                          | 0.8                          | 1.1                          | 1.5                          | V                |       |

| $V_{LVDH}$                                                                           | Falling low-voltage detect threshold — high range (LVDV=01)                                                                                                             | 2.48                         | 2.56                         | 2.64                         | V                |       |

| V <sub>lvw1h</sub><br>V <sub>lvw2h</sub><br>V <sub>lvw3h</sub><br>V <sub>lvw4h</sub> | Low-voltage warning thresholds — high range<br>• Level 1 falling (LVWV=00)<br>• Level 2 falling (LVWV=01)<br>• Level 3 falling (LVWV=10)<br>• Level 4 falling (LVWV=11) | 2.62<br>2.72<br>2.82<br>2.92 | 2.70<br>2.80<br>2.90<br>3.00 | 2.78<br>2.88<br>2.98<br>3.08 | V<br>V<br>V<br>V | 1     |

| V <sub>HYSH</sub>                                                                    | Low-voltage inhibit reset/recover hysteresis — high range                                                                                                               | _                            | ±80                          |                              | mV               |       |

| $V_{LVDL}$                                                                           | Falling low-voltage detect threshold — low range (LVDV=00)                                                                                                              | 1.54                         | 1.60                         | 1.66                         | V                |       |

| V <sub>LVW1L</sub><br>V <sub>LVW2L</sub>                                             | Low-voltage warning thresholds — low range<br>• Level 1 falling (LVWV=00)                                                                                               | 1.74<br>1.84                 | 1.80<br>1.90                 | 1.86<br>1.96                 | V<br>V           | 1     |

| V <sub>LVW3L</sub><br>V <sub>LVW4L</sub>                                             | <ul> <li>Level 2 falling (LVWV=01)</li> <li>Level 3 falling (LVWV=10)</li> <li>Level 4 falling (LVWV=11)</li> </ul>                                                     | 1.94<br>2.04                 | 2.00<br>2.10                 | 2.06<br>2.16                 | V<br>V           |       |

| V <sub>HYSL</sub>                                                                    | Low-voltage inhibit reset/recover hysteresis — low range                                                                                                                | _                            | ±60                          | _                            | mV               |       |

| V <sub>BG</sub>                                                                      | Bandgap voltage reference                                                                                                                                               | 0.97                         | 1.00                         | 1.03                         | V                |       |

| t <sub>LPO</sub>                                                                     | Internal low power oscillator period factory trimmed                                                                                                                    | 900                          | 1000                         | 1100                         | μs               |       |

1. Rising thresholds are falling threshold + hysteresis voltage

## Table 3. VBAT power operating requirements

| Symbol                | Description                            | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------|------|------|------|------|-------|

| V <sub>POR_VBAT</sub> | Falling VBAT supply POR detect voltage | 0.8  | 1.1  | 1.5  | V    |       |

# 5.2.3 Voltage and current operating behaviors

Table 4. Voltage and current operating behaviors

| Symbol          | Description                                                                                        | Min.                  | Тур. | Max. | Unit | Notes |

|-----------------|----------------------------------------------------------------------------------------------------|-----------------------|------|------|------|-------|

| V <sub>OH</sub> | Output high voltage — high drive strength                                                          |                       |      | _    |      |       |

|                 | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -9mA                                | V <sub>DD</sub> – 0.5 | _    | _    | V    |       |

|                 | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -3\text{mA}$ | V <sub>DD</sub> – 0.5 | —    |      | V    |       |

Table continues on the next page...

# 5.2.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

|                       | Description                                                                   | Min. | Тур.  | Max.     | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------|------|-------|----------|------|-------|

| I <sub>DDA</sub>      | Analog supply current                                                         | _    | _     | See note | mA   | 1     |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks disabled, code executing from flash  |      |       |          |      | 2     |

|                       | • @ 1.8V                                                                      | —    | 49.28 | 73.85    | mA   |       |

|                       | • @ 3.0V                                                                      | —    | 49.08 | 73.93    | mA   |       |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks enabled, code executing from flash   |      |       |          |      | 3     |

|                       | • @ 1.8V                                                                      |      | 74.43 | 99.97    | mA   |       |

|                       | • @ 3.0V                                                                      | —    | 74.28 | 100.41   | mA   |       |

| I <sub>DD_WAIT</sub>  | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled    | _    | 34.67 | 58.5     | mA   | 2     |

| I <sub>DD_WAIT</sub>  | Wait mode reduced frequency current at 3.0 V — all peripheral clocks disabled | —    | 18.03 | 41.91    | mA   | 4     |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                    |      |       |          |      |       |

|                       | • @ -40 to 25°C                                                               | —    | 1.25  | 1.62     | mA   |       |

|                       | • @ 70°C                                                                      | —    | 2.93  | 4.39     | mA   |       |

|                       | • @ 85°C                                                                      | —    | 7.08  | 10.74    | mA   |       |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled     | —    | 1.03  | 4.48     | mA   | 5     |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled      | —    | 1.58  | 4.96     | mA   | 5     |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V                                     | _    | 0.64  | 4.29     | mA   | 5     |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                     |      |       |          |      |       |

|                       | • @ -40 to 25°C                                                               | —    | 0.22  | 0.38     | mA   |       |

|                       | • @ 70°C                                                                      | —    | 0.78  | 1.33     | mA   |       |

|                       | • @ 85°C                                                                      | _    | 2.18  | 3.56     | mA   |       |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                        |      |       |          |      |       |

|                       | • @ –40 to 25°C                                                               | _    | 0.22  | 0.37     | mA   |       |

|                       | • @ 70°C                                                                      | _    | 0.78  | 1.33     | mA   |       |

|                       | • @ 85°C                                                                      | _    | 2.16  | 3.52     | mA   |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                                 |      |       |          |      |       |

|                       | • @ -40 to 25°C                                                               |      | 4.09  | 5.58     | μA   |       |

|                       | • @ 70°C                                                                      | _    | 20.98 | 28.93    | μA   |       |

|                       | • @ 85°C                                                                      |      | 84.95 | 111.15   | μA   |       |

Table continues on the next page...

| Symbol             | Description | Min. | Max. | Unit | Notes |

|--------------------|-------------|------|------|------|-------|

| f <sub>FLASH</sub> | Flash clock | —    | 0.5  | MHz  |       |

| f <sub>LPTMR</sub> | LPTMR clock | _    | 4    | MHz  |       |

### Table 9. Device clock specifications (continued)

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

## 5.3.2 General switching specifications

These general purpose specifications apply to all pins configured for:

- GPIO signaling

- Other peripheral module signaling not explicitly stated elsewhere

Table 10. General switching specifications

| Symbol            | Description                                                                                                 | Min. | Max. | Unit                | Notes |

|-------------------|-------------------------------------------------------------------------------------------------------------|------|------|---------------------|-------|

|                   | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                          | 1.5  | _    | Bus clock<br>cycles | 1, 2  |

|                   | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter enabled) — Asynchronous path  | 100  | _    | ns                  | 3     |

|                   | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled) — Asynchronous path | 16   | _    | ns                  | 3     |

|                   | External reset pulse width (digital glitch filter disabled)                                                 | 100  | _    | ns                  | 3     |

|                   | Mode select (EZP_CS) hold time after reset deassertion                                                      | 2    | _    | Bus clock<br>cycles |       |

|                   | Port rise and fall time (high drive strength)                                                               |      |      |                     | 4     |

|                   | Slew disabled                                                                                               |      |      |                     |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                                                                                | —    | 14   | ns                  |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 8    | ns                  |       |

|                   | Slew enabled                                                                                                |      |      |                     |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                                                                                | —    | 36   | ns                  |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 24   | ns                  |       |

|                   | Port rise and fall time (low drive strength)                                                                |      |      |                     | 5     |

|                   | Slew disabled                                                                                               |      |      |                     |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                                                                                | _    | 14   | ns                  |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | _    | 8    | ns                  |       |

|                   | Slew enabled                                                                                                |      |      |                     |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | _    | 36   | ns                  |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | _    | 24   | ns                  |       |

| t <sub>io50</sub> | Port rise and fall time (high drive strength)                                                               |      |      |                     | 6     |

|                   | Slew disabled                                                                                               |      |      |                     |       |

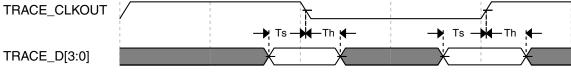

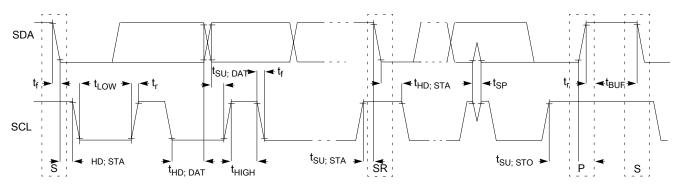

Figure 6. Trace data specifications

# 6.1.2 JTAG electricals

| Table 13. | JTAG limited | voltage range | electricals |

|-----------|--------------|---------------|-------------|

|-----------|--------------|---------------|-------------|

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 25   |      |

|        | Serial Wire Debug                                  | 0    | 50   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| JЗ     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 20   | _    | ns   |

|        | Serial Wire Debug                                  | 10   | —    | ns   |

| J4     | TCLK rise and fall times                           | —    | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 2.4  | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | _    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | —    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | —    | ns   |

| J11    | TCLK low to TDO data valid                         | —    | 17   | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 17   | ns   |

| J13    | TRST assert time                                   | 100  |      | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    |      | ns   |

## Table 14. JTAG full voltage range electricals

| Symbol | Description                 | Min. | Max. | Unit |

|--------|-----------------------------|------|------|------|

|        | Operating voltage           | 1.71 | 3.6  | V    |

| J1     | TCLK frequency of operation |      |      | MHz  |

Table continues on the next page...

### rempheral operating requirements and behaviors

| Symbol                   | Description                                                                                                                       |                                                                                           | Min. | Тур.  | Max.                                                        | Unit    | Notes |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------------|---------|-------|

| f <sub>dco</sub>         | DCO output<br>frequency range                                                                                                     | Low range (DRS=00)                                                                        | 20   | 20.97 | 25                                                          | MHz     | 2, 3  |

|                          |                                                                                                                                   | $640 \times f_{\text{fll_ref}}$                                                           | 40   | 44.04 | 50                                                          | N 41 1- | -     |

|                          |                                                                                                                                   | Mid range (DRS=01)<br>1280 × f <sub>fll ref</sub>                                         | 40   | 41.94 | 50                                                          | MHz     |       |

|                          |                                                                                                                                   | Mid-high range (DRS=10)                                                                   | 60   | 62.91 | 75                                                          | MHz     | _     |

|                          |                                                                                                                                   | $1920 \times f_{fll\_ref}$                                                                |      |       |                                                             |         |       |

|                          |                                                                                                                                   | High range (DRS=11)                                                                       | 80   | 83.89 | 100                                                         | MHz     |       |

|                          |                                                                                                                                   | 2560 × f <sub>fll_ref</sub>                                                               |      |       |                                                             |         |       |

| dco_t_DMX32              | DCO output<br>frequency                                                                                                           | Low range (DRS=00)<br>732 × f <sub>fll ref</sub>                                          | —    | 23.99 | _                                                           | MHz     | 4, 5  |

|                          |                                                                                                                                   | Mid range (DRS=01)                                                                        | _    | 47.97 |                                                             | MHz     | -     |

|                          |                                                                                                                                   | 1464 × f <sub>fll_ref</sub>                                                               |      |       |                                                             |         |       |

|                          |                                                                                                                                   | Mid-high range (DRS=10)                                                                   | —    | 71.99 | —                                                           | MHz     |       |

|                          |                                                                                                                                   | $2197 \times f_{fll\_ref}$                                                                |      |       |                                                             |         |       |

|                          |                                                                                                                                   | High range (DRS=11)                                                                       | _    | 95.98 | 95.98 —                                                     | MHz     | -     |

|                          |                                                                                                                                   | 2929 × f <sub>fll ref</sub>                                                               |      |       |                                                             |         |       |

| J <sub>cyc_fll</sub> Fl  | FLL period jitter                                                                                                                 |                                                                                           |      | 180   | _                                                           | ps      |       |

|                          | <ul> <li>f<sub>VCO</sub> = 48 MI</li> <li>f<sub>VCO</sub> = 98 MI</li> </ul>                                                      |                                                                                           | —    | 150   | _                                                           |         |       |

| t <sub>fll_acquire</sub> | FLL target frequen                                                                                                                | cy acquisition time                                                                       | _    | _     | 1                                                           | ms      | 6     |

|                          |                                                                                                                                   | PLL                                                                                       | .0,1 | •     |                                                             |         |       |

| f <sub>pll_ref</sub>     | PLL reference frec                                                                                                                | uency range                                                                               | 8    | _     | 16                                                          | MHz     |       |

| $f_{vcoclk_2x}$          | VCO output freque                                                                                                                 | ency                                                                                      | 180  | —     | 360                                                         | MHz     |       |

| f <sub>vcoclk</sub>      | PLL output freque                                                                                                                 | псу                                                                                       | 90   | —     | 180                                                         | MHz     |       |

| f <sub>vcoclk_90</sub>   | PLL quadrature ou                                                                                                                 | tput frequency                                                                            | 90   | —     | 180                                                         | MHz     |       |

| I <sub>pll</sub>         |                                                                                                                                   | rrent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>NV multiplier = 23) | _    | 2.8   | -                                                           | mA      |       |

| I <sub>pli</sub>         |                                                                                                                                   | rrent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>NV multiplier = 45) | _    | 4.7   | _                                                           | mA      | 7     |

| I <sub>pll</sub>         | PLL1 operating current<br>• VCO @ 184 MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>= 8 MHz, VDIV multiplier = 23) |                                                                                           | _    | 2.3   | -                                                           | mA      | 7     |

| I <sub>pll</sub>         | PLL1 operating cu<br>• VCO @ 360<br>= 8 MHz, VD                                                                                   | rrent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>NV multiplier = 45) | _    | 3.6   | -                                                           | mA      | 7     |

| t <sub>pll_lock</sub>    | = 8 MHZ, VDIV multiplier = 45)<br>Lock detector detection time                                                                    |                                                                                           | —    | _     | $100 \times 10^{-6}$<br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S       | 8     |

## Table 15. MCG specifications (continued)

### 6.4.1.4 Reliability specifications Table 23. NVM re

| able 23. | NVM reliability | specifications |

|----------|-----------------|----------------|

|----------|-----------------|----------------|

| Symbol                  | Description                            | Min. | Typ. <sup>1</sup> | Max. | Unit   | Notes |  |  |

|-------------------------|----------------------------------------|------|-------------------|------|--------|-------|--|--|

|                         | Program Flash                          |      |                   |      |        |       |  |  |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5    | 50                | _    | years  |       |  |  |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20   | 100               | _    | years  |       |  |  |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K | 50 K              |      | cycles | 2     |  |  |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>j</sub>  $\leq$  125°C.

# 6.4.2 EzPort switching specifications

| Table 24. | EzPort switching specification | ons |

|-----------|--------------------------------|-----|

|-----------|--------------------------------|-----|

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 1.71                    | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | _                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | _                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | _                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 5                       | —                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 5                       | _                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 2                       |                     | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)                | 5                       | _                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid                         | _                       | 16                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)                | 0                       | _                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state                       | _                       | 12                  | ns   |

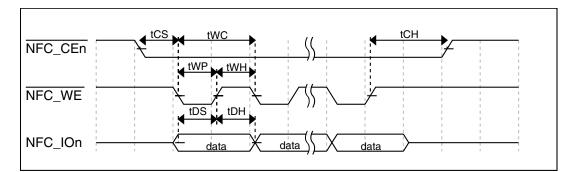

Figure 14. Write data latch cycle timing

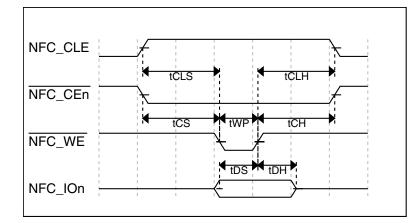

#### Peripheral operating requirements and behaviors

| Num | Description                             | Min. | Max. | Unit | Notes |

|-----|-----------------------------------------|------|------|------|-------|

| FB2 | Address, data, and control output valid | —    | 11.5 | ns   | 1     |

| FB3 | Address, data, and control output hold  | 0.5  | —    | ns   | 1     |

| FB4 | Data and FB_TA input setup              | 8.5  | —    | ns   | 2     |

| FB5 | Data and FB_TA input hold               | 0.5  | _    | ns   | 2     |

Table 26. Flexbus limited voltage range switching specifications (continued)

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

2. Specification is valid for all FB\_AD[31:0] and FB\_TA.

### Table 27. Flexbus full voltage range switching specifications

| Num | Description                             | Min.     | Max.   | Unit | Notes |

|-----|-----------------------------------------|----------|--------|------|-------|

|     | Operating voltage                       | 1.71     | 3.6    | V    |       |

|     | Frequency of operation                  | _        | FB_CLK | MHz  |       |

| FB1 | Clock period                            | 1/FB_CLK | _      | ns   |       |

| FB2 | Address, data, and control output valid | _        | 13.5   | ns   | 1     |

| FB3 | Address, data, and control output hold  | 0        | —      | ns   | 1     |

| FB4 | Data and FB_TA input setup              | 13.7     | —      | ns   | 2     |

| FB5 | Data and FB_TA input hold               | 0.5      | _      | ns   | 2     |

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

2. Specification is valid for all FB\_AD[31:0] and  $\overline{FB_TA}$ .

# 6.6 Analog

## 6.6.1 ADC electrical specifications

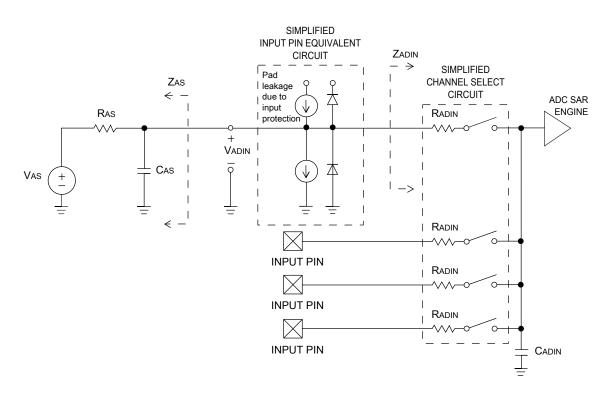

The 16-bit accuracy specifications listed in Table 28 and Table 29 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

The ADCx\_DP2 and ADCx\_DM2 ADC inputs are connected to the PGA outputs and are not direct device pins. Accuracy specifications for these pins are defined in Table 30 and Table 31.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol            | Description                       | Conditions                                                     | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-----------------------------------|----------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                    | Absolute                                                       | 1.71             |                   | 3.6              | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                    | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> ) | -100             | 0                 | +100             | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                    | Delta to V <sub>SS</sub> (V <sub>SS</sub> – V <sub>SSA</sub> ) | -100             | 0                 | +100             | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high        |                                                                | 1.13             | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    |       |

| V <sub>REFL</sub> | ADC reference voltage low         |                                                                | V <sub>SSA</sub> | $V_{SSA}$         | V <sub>SSA</sub> | V    |       |

| V <sub>ADIN</sub> | Input voltage                     | 16-bit differential mode                                       | VREFL            | _                 | 31/32 ×<br>VREFH | V    |       |

|                   |                                   | All other modes                                                | VREFL            | —                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input capacitance                 | 16-bit mode                                                    | _                | 8                 | 10               | pF   |       |

|                   |                                   | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>          | —                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance           |                                                                | _                | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source                     | 13-bit / 12-bit modes                                          |                  |                   |                  |      | 3     |

|                   | resistance<br>(external)          | f <sub>ADCK</sub> < 4 MHz                                      | —                | —                 | 5                | kΩ   |       |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 13-bit mode                                                  | 1.0              | _                 | 18.0             | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16-bit mode                                                    | 2.0              | _                 | 12.0             | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion rate               | ≤ 13-bit modes                                                 |                  |                   |                  |      | 5     |

### 6.6.1.1 16-bit ADC operating conditions Table 28. 16-bit ADC operating conditions

| Symbol            | Description            | Conditions                                                                                                   | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|------------------------|--------------------------------------------------------------------------------------------------------------|--------|-------------------|---------|------|-------|

|                   |                        | No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time                | 20.000 |                   | 818.330 | ksps |       |

| C <sub>rate</sub> | ADC conversion<br>rate | 16-bit mode<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 37.037 | _                 | 461.467 | ksps | 5     |

### Table 28. 16-bit ADC operating conditions (continued)

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 19. ADC input impedance equivalency diagram

## 6.6.1.2 16-bit ADC electrical characteristics

# Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ )

| Symbol               | Description                     | Conditions <sup>1</sup>              | Min.          | Typ. <sup>2</sup> | Max.            | Unit             | Notes                                         |

|----------------------|---------------------------------|--------------------------------------|---------------|-------------------|-----------------|------------------|-----------------------------------------------|

| I <sub>DDA_ADC</sub> | Supply current                  |                                      | 0.215         | —                 | 1.7             | mA               | 3                                             |

|                      | ADC asynchronous                | • ADLPC = 1, ADHSC = 0               | 1.2           | 2.4               | 3.9             | MHz              | t <sub>ADACK</sub> = 1/                       |

|                      | clock source                    | • ADLPC = 1, ADHSC = 1               | 2.4           | 4.0               | 6.1             | MHz              | f <sub>ADACK</sub>                            |

| f <sub>ADACK</sub>   |                                 | • ADLPC = 0, ADHSC = 0               | 3.0           | 5.2               | 7.3             | MHz              |                                               |

|                      |                                 | • ADLPC = 0, ADHSC = 1               | 4.4           | 6.2               | 9.5             | MHz              |                                               |

|                      | Sample Time                     | See Reference Manual chapter         | for sample ti | mes               |                 |                  | 1                                             |

| TUE                  | Total unadjusted                | 12-bit modes                         | —             | ±4                | ±6.8            | LSB <sup>4</sup> | 5                                             |

|                      | error                           | <ul> <li>&lt;12-bit modes</li> </ul> |               | ±1.4              | ±2.1            |                  |                                               |

| DNL                  | Differential non-               | 12-bit modes                         |               | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                                             |

|                      | linearity                       | <ul> <li>&lt;12-bit modes</li> </ul> | _             | ±0.2              | -0.3 to<br>0.5  |                  |                                               |

| INL                  | Integral non-linearity          | 12-bit modes                         |               | ±1.0              | -2.7 to         | LSB <sup>4</sup> | 5                                             |

|                      |                                 | <ul> <li>&lt;12-bit modes</li> </ul> |               | ±0.5              | +1.9            |                  |                                               |

|                      |                                 |                                      |               |                   | –0.7 to<br>+0.5 |                  |                                               |

| $E_{FS}$             | Full-scale error                | 12-bit modes                         | _             | -4                | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}$                          |

|                      |                                 | <li>&lt;12-bit modes</li>            | _             | -1.4              | -1.8            |                  |                                               |

| EQ                   | Quantization error              | 16-bit modes                         | _             | -1 to 0           | _               | LSB <sup>4</sup> |                                               |

|                      |                                 | <ul> <li>≤13-bit modes</li> </ul>    |               | -                 | ±0.5            |                  |                                               |

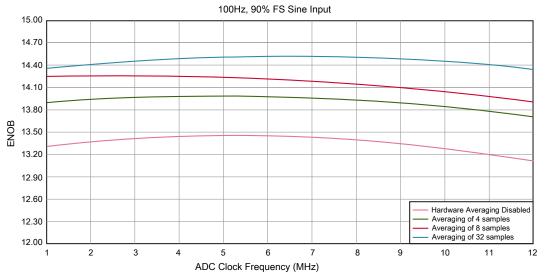

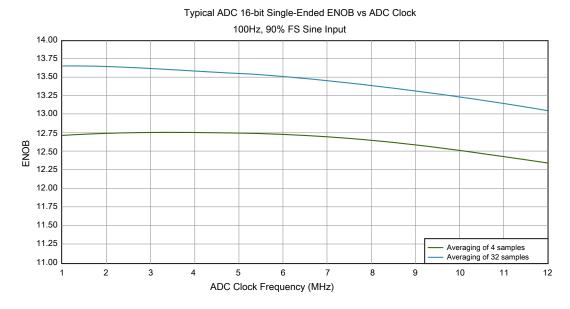

| ENOB                 | Effective number of             | 16-bit differential mode             |               |                   |                 |                  | 6                                             |

|                      | bits                            | • Avg = 32                           | 12.8          | 14.5              | —               | bits             |                                               |

|                      |                                 | • Avg = 4                            | 11.9          | 13.8              | _               | bits             | 5<br>5<br>V <sub>ADIN</sub> = V <sub>DD</sub> |

|                      |                                 | 16-bit single-ended mode             |               |                   |                 |                  |                                               |

|                      |                                 | • Avg = 32                           | 12.2          | 13.9              | _               | hito             |                                               |

|                      |                                 | • Avg = 4                            | 11.4          | 13.1              |                 | bits             |                                               |

|                      |                                 | -                                    |               |                   |                 | bits             |                                               |

| SINAD                | Signal-to-noise plus distortion | See ENOB                             | 6.02 ×        | ENOB +            | 1.76            | dB               |                                               |

| THD                  | Total harmonic                  | 16-bit differential mode             |               |                   |                 | dB               | 7                                             |

|                      | distortion                      | • Avg = 32                           |               | -94               | —               |                  |                                               |

|                      |                                 | 16-bit single-ended mode             |               |                   |                 | dB               |                                               |

|                      |                                 | <ul> <li>Avg = 32</li> </ul>         |               | -85               | —               |                  |                                               |

| 0555                 |                                 | _                                    |               |                   |                 |                  |                                               |

|                      | Spurious free<br>dynamic range  | 16-bit differential mode             | 82            | 95                | —               | dB               | 7                                             |

|                      |                                 | • Avg = 32                           |               |                   |                 | dB               |                                               |

|                      |                                 | 16-bit single-ended mode             | 78            | 90                |                 |                  |                                               |

| Symbol              | Description         | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>      | Max. | Unit  | Notes                                                                  |

|---------------------|---------------------|-------------------------------------------------|------|------------------------|------|-------|------------------------------------------------------------------------|

|                     |                     | • Avg = 32                                      |      |                        |      |       |                                                                        |

| E <sub>IL</sub>     | Input leakage error |                                                 |      | $I_{In} \times R_{AS}$ |      | mV    | I <sub>In</sub> = leakage<br>current                                   |

|                     |                     |                                                 |      |                        |      |       | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor slope   | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69 | mV/°C | 8                                                                      |

| V <sub>TEMP25</sub> | Temp sensor voltage | 25 °C                                           | 706  | 716                    | 726  | mV    | 8                                                                      |

# Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

4. 1 LSB =  $(V_{REFH} - V_{REFL})/2^N$

5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Differential ENOB vs ADC Clock

Figure 20. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

## 6.6.1.3 16-bit ADC with PGA operating conditions Table 30. 16-bit ADC with PGA operating conditions

| Symbol              | Description                | Conditions                                                                                                                                                   | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes                   |

|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|------|-------------------------|

| V <sub>DDA</sub>    | Supply voltage             | Absolute                                                                                                                                                     | 1.71             | _                 | 3.6              | V    |                         |

| V <sub>REFPGA</sub> | PGA ref voltage            |                                                                                                                                                              | VREF_OU<br>T     | VREF_OU<br>T      | VREF_OU<br>T     | V    | 2, 3                    |

| V <sub>ADIN</sub>   | Input voltage              |                                                                                                                                                              | V <sub>SSA</sub> | _                 | V <sub>DDA</sub> | V    |                         |

| V <sub>CM</sub>     | Input Common<br>Mode range |                                                                                                                                                              | V <sub>SSA</sub> | _                 | V <sub>DDA</sub> | V    |                         |

| R <sub>PGAD</sub>   | Differential input         | Gain = 1, 2, 4, 8                                                                                                                                            |                  | 128               | _                | kΩ   | IN+ to IN- <sup>4</sup> |

|                     | impedance                  | Gain = 16, 32                                                                                                                                                | _                | 64                | —                |      |                         |

|                     |                            | Gain = 64                                                                                                                                                    | _                | 32                | —                |      |                         |

| R <sub>AS</sub>     | Analog source resistance   |                                                                                                                                                              | _                | 100               | —                | Ω    | 5                       |

| Τ <sub>S</sub>      | ADC sampling time          |                                                                                                                                                              | 1.25             | _                 | —                | μs   | 6                       |

| C <sub>rate</sub>   | ADC conversion<br>rate     | <ul> <li>≤ 13 bit modes</li> <li>No ADC hardware<br/>averaging</li> <li>Continuous conversions<br/>enabled</li> <li>Peripheral clock = 50<br/>MHz</li> </ul> | 18.484           | _                 | 450              | Ksps | 7                       |

|                     |                            | 16 bit modes                                                                                                                                                 | 37.037           | —                 | 250              | Ksps | 8                       |

#### Peripheral operating requirements and behaviors

| Symbol | Description | Conditions                     | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|--------|-------------|--------------------------------|------|-------------------|------|------|-------|

|        |             | No ADC hardware averaging      |      |                   |      |      |       |

|        |             | Continuous conversions enabled |      |                   |      |      |       |

|        |             | Peripheral clock = 50<br>MHz   |      |                   |      |      |       |

### Table 30. 16-bit ADC with PGA operating conditions

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 6 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. ADC must be configured to use the internal voltage reference (VREF\_OUT)

- 3. PGA reference is internally connected to the VREF\_OUT pin. If the user wishes to drive VREF\_OUT with a voltage other than the output of the VREF module, the VREF module must be disabled.

- 4. For single ended configurations the input impedance of the driven input is  $R_{PGAD}/2$

- 5. The analog source resistance (R<sub>AS</sub>), external to MCU, should be kept as minimum as possible. Increased R<sub>AS</sub> causes drop in PGA gain without affecting other performances. This is not dependent on ADC clock frequency.

- The minimum sampling time is dependent on input signal frequency and ADC mode of operation. A minimum of 1.25µs time should be allowed for F<sub>in</sub>=4 kHz at 16-bit differential mode. Recommended ADC setting is: ADLSMP=1, ADLSTS=2 at 8 MHz ADC clock.

- 7. ADC clock = 18 MHz, ADLSMP = 1, ADLST = 00, ADHSC = 1

- 8. ADC clock = 12 MHz, ADLSMP = 1, ADLST = 01, ADHSC = 1

## 6.6.1.4 16-bit ADC with PGA characteristics Table 31. 16-bit ADC with PGA characteristics

| Symbol               | Description                  | Conditions                                     | Min.                                                                                                      | Typ. <sup>1</sup> | Max. | Unit                             | Notes                       |

|----------------------|------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|------|----------------------------------|-----------------------------|

| I <sub>DDA_PGA</sub> | Supply current               | Low power - 420<br>(ADC_PGA[PGALPb]=0)         |                                                                                                           | 644               | μA   | 2                                |                             |

| I <sub>DC_PGA</sub>  | Input DC current             |                                                | $\frac{2}{R_{\rm PGAD}} \left( \frac{(V_{\rm REFPGA} \times 0.583) - V_{\rm CM}}{({\rm Gain}+1)} \right)$ |                   |      | A                                | 3                           |

|                      |                              | Gain =1, $V_{REFPGA}$ =1.2V,<br>$V_{CM}$ =0.5V | -                                                                                                         | 1.54              | _    | μA                               |                             |

|                      |                              | Gain =64, $V_{REFPGA}$ =1.2V, $V_{CM}$ =0.1V   | _                                                                                                         | 0.57              |      | μA                               | 3<br>R <sub>AS</sub> < 100Ω |

| G                    | Gain <sup>4</sup>            | • PGAG=0                                       | 0.95                                                                                                      | 1                 | 1.05 |                                  | R <sub>AS</sub> < 100Ω      |

|                      |                              | • PGAG=1                                       | 1.9                                                                                                       | 2                 | 2.1  |                                  |                             |

|                      |                              | • PGAG=2                                       | 3.8                                                                                                       | 4                 | 4.2  |                                  |                             |

|                      |                              | • PGAG=3                                       | 7.6                                                                                                       | 8                 | 8.4  |                                  |                             |

|                      |                              | • PGAG=4                                       | 15.2                                                                                                      | 16                | 16.6 |                                  |                             |

|                      |                              | • PGAG=5                                       | 30.0                                                                                                      | 31.6              | 33.2 |                                  |                             |

|                      |                              | • PGAG=6                                       | 58.8                                                                                                      | 63.3              | 67.8 |                                  |                             |

| BW                   | Input signal                 | 16-bit modes                                   | _                                                                                                         | _                 | 4    | kHz                              |                             |

|                      | bandwidth                    | <ul> <li>&lt; 16-bit modes</li> </ul>          | _                                                                                                         | _                 | 40   | kHz                              |                             |

| PSRR                 | Power supply rejection ratio | Gain=1                                         | 84 -                                                                                                      |                   | dB   | V <sub>DDA</sub> = 3V<br>±100mV, |                             |

Table continues on the next page ...

| Symbol               | Description                                   | Conditions                                                                      | Min.                                                                                                                       | Typ. <sup>1</sup>      | Max. | Unit   | Notes                                                                  |

|----------------------|-----------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------|------|--------|------------------------------------------------------------------------|

|                      |                                               |                                                                                 |                                                                                                                            |                        |      |        | f <sub>VDDA</sub> = 50Hz,<br>60Hz                                      |

| CMRR                 | Common mode                                   | Gain=1                                                                          | _                                                                                                                          | -84                    | —    | dB     | V <sub>CM</sub> =                                                      |

|                      | rejection ratio                               | • Gain=64                                                                       | -                                                                                                                          | -85                    | —    | dB     | 500mVpp,<br>f <sub>VCM</sub> = 50Hz,<br>100Hz                          |

| V <sub>OFS</sub>     | Input offset<br>voltage                       | <ul> <li>Chopping disabled<br/>(ADC_PGA[PGACHPb]</li> </ul>                     | _                                                                                                                          | 2.4                    | _    | mV     | Output offset =<br>V <sub>OFS</sub> *(Gain+1)                          |

|                      |                                               | <ul> <li>=1)</li> <li>Chopping enabled<br/>(ADC_PGA[PGACHPb]<br/>=0)</li> </ul> | _                                                                                                                          | 0.2                    | _    | mV     |                                                                        |

| T <sub>GSW</sub>     | Gain switching<br>settling time               |                                                                                 | —                                                                                                                          | _                      | 10   | μs     | 5                                                                      |

| dG/dT                | Gain drift over full                          | • Gain=1                                                                        | —                                                                                                                          | 6                      | 10   | ppm/°C |                                                                        |

|                      | temperature range                             | • Gain=64                                                                       |                                                                                                                            | 31                     | 42   | ppm/°C |                                                                        |

| $dG/dV_{DDA}$        | Gain drift over<br>supply voltage             | <ul> <li>Gain=1</li> <li>Gain=64</li> </ul>                                     | _                                                                                                                          | 0.07                   | 0.21 | %/V    | V <sub>DDA</sub> from 1.71<br>to 3.6V                                  |

|                      |                                               |                                                                                 | —                                                                                                                          | 0.14                   | 0.31 | %/V    |                                                                        |

| EIL                  | Input leakage<br>error                        | All modes                                                                       |                                                                                                                            | $I_{In} \times R_{AS}$ |      | mV     | I <sub>In</sub> = leakage<br>current                                   |

|                      |                                               |                                                                                 |                                                                                                                            |                        |      |        | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

| V <sub>PP,DIFF</sub> | Maximum<br>differential input<br>signal swing |                                                                                 | $\left(\frac{(\min(V_x V_{DDA} - V_x) - 0.2) \times 4}{Gain}\right)$<br>where V <sub>X</sub> = V <sub>REFPGA</sub> × 0.583 |                        |      | V      | 6                                                                      |

|                      | Signal Swing                                  |                                                                                 |                                                                                                                            |                        |      |        |                                                                        |

| SNR                  | Signal-to-noise                               | Gain=1                                                                          | 80                                                                                                                         | 90                     | —    | dB     | 16-bit                                                                 |

|                      | ratio                                         | • Gain=64                                                                       | 52                                                                                                                         | 66                     |      | dB     | differential<br>mode,<br>Average=32                                    |

| THD                  | Total harmonic                                | • Gain=1                                                                        | 85                                                                                                                         | 100                    | _    | dB     | 16-bit                                                                 |

|                      | distortion                                    | • Gain=64                                                                       | 49                                                                                                                         | 95                     | _    | dB     | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

| SFDR                 | Spurious free                                 | Gain=1                                                                          | 85                                                                                                                         | 105                    | _    | dB     | 16-bit                                                                 |

|                      | dynamic range                                 | • Gain=64                                                                       | 53                                                                                                                         | 88                     | _    | dB     | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

| ENOB                 | Effective number                              | Gain=1, Average=4                                                               | 11.6                                                                                                                       | 13.4                   | —    | bits   | 16-bit                                                                 |