# E. Renesas Electronics America Inc - UPD70F3762GC-UEU-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                                      |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 77                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | <u> </u>                                                                             |

| RAM Size                   | 56К х 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3762gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.3 Pin I/O Circuit Types, I/O Buffer Power Supplies and Connection of Unused Pins

| Pin<br>Name | Alternate Function                         | I/O Circuit<br>Type |                   | Recommended Connection                                                                         | JG3-H        | JH3-H        |

|-------------|--------------------------------------------|---------------------|-------------------|------------------------------------------------------------------------------------------------|--------------|--------------|

| P00         | INTP00                                     | 10-D                | Input:            | Independently connect to $EV_{DD}$ or $V_{SS}$                                                 | -            | $\checkmark$ |

| P01         | INTP01                                     |                     | <b>.</b>          | via a resistor.                                                                                | -            | $\checkmark$ |

| P02         | NMI                                        |                     | Output:           | Leave open.                                                                                    | $\checkmark$ | $\checkmark$ |

| P03         | INTP02/ADTRG/UCLK                          |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P04         | INTP03                                     |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P05         | INTP04                                     |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P10         | ANO0                                       | 12-D                | Input:            | Independently connect to AVREF1 or                                                             | $\checkmark$ | $\checkmark$ |

| P11         | ANO1                                       |                     | Output:           | AVss via a resistor.<br>Leave open.                                                            | $\checkmark$ | $\checkmark$ |

| P20         | TIAB03/KR2/TOAB03/RTP02                    | 10-D                | Input:            | Independently connect to $EV_{\text{DD}}$ or $V_{\text{SS}}$                                   | -            | $\checkmark$ |

| P21         | SIF2/TIAB00/KR3/TOAB00/RTP03               |                     | Outout            | via a resistor.                                                                                | -            | $\checkmark$ |

| P22         | SOF2/KR4/RTP04                             |                     | Output:           | Leave open.                                                                                    | -            | $\checkmark$ |

| P23         | SCKF2/KR5/RTP05                            |                     |                   |                                                                                                | -            | $\checkmark$ |

| P24         | INTP05                                     |                     |                   |                                                                                                | -            | $\checkmark$ |

| P25         | INTP06                                     |                     |                   |                                                                                                | -            | $\checkmark$ |

| P30         | TXDC0/SOF4/INTP07                          | 10-D                | Input:            | Independently connect to $EV_{\text{DD}}$ or $V_{\text{SS}}$                                   | $\checkmark$ | $\checkmark$ |

| P31         | RXDC0/SIF4/INTP08                          |                     | 0.1.1             | via a resistor.                                                                                | $\checkmark$ | $\checkmark$ |

| P32         | ASCKC0/SCKF4/TIAA00/TOAA00                 |                     | Output:           | Leave open.                                                                                    | $\checkmark$ | $\checkmark$ |

| P33         | TIAA01/TOAA01/RTCDIV/RTCCL                 |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P34         | TIAA10/TOAA10/TOAA1OFF/INTP09              |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P35         | TIAA11/TOAA11/RTC1HZ                       |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P36         | TXDC3/SCL00/CTXD0 <sup>Note</sup> /UDMARQ0 |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P37         | RXDC3/SDA00/CRXD0 <sup>Note</sup> /UDMAAK0 |                     |                   |                                                                                                | $\checkmark$ | $\checkmark$ |

| P40         | SIF0/TXDC4/SDA01                           | 10-D                | Input:            | Independently connect to $EV_{DD}$ or $V_{SS}$                                                 | $\checkmark$ | $\checkmark$ |

| P41         | SOF0/RXDC4/SCL01                           |                     | <u> </u>          | via a resistor.                                                                                | $\checkmark$ | $\checkmark$ |

| P42         | SCKF0/INTP10                               |                     | Output:           | Leave open.                                                                                    | $\checkmark$ | $\checkmark$ |

| P50         | TIAB01/KR0/TOAB01/RTP00/UDMARQ1            | 10-D                | Input:            | Independently connect to $EV_{DD}$ or $V_{SS}$                                                 | $\checkmark$ | $\checkmark$ |

| P51         | TIAB02/KR1/TOAB02/RTP01/UDMAAK1            |                     | <b>.</b>          | via a resistor.                                                                                | $\checkmark$ | $\checkmark$ |

| P52         | TIAB03/KR2/TOAB03/RTP02/DDI                |                     | Output:           | Leave open.                                                                                    | $\checkmark$ | -            |

| P53         | SIF2/TIAB00/KR3/TOAB00/RTP03/DDO           |                     |                   |                                                                                                | $\checkmark$ | -            |

| P54         | SOF2/KR4/RTP04/DCK                         |                     |                   |                                                                                                | $\checkmark$ | -            |

| P55         | SCKF2/KR5/RTP05/DMS                        |                     |                   |                                                                                                | $\checkmark$ | -            |

| P56         | INTP05/DRST                                | 10-N                | Input:<br>Output: | Independently connect to Vss via a resistor. Fixing to VDD level is prohibited.<br>Leave open. | V            | _            |

|             |                                            |                     | Culput.           | Internally pull-down after reset by RESET pin.                                                 |              |              |

**Note** μPD70F3770, 70F3771 only

Remark JG3-H: V850ES/JG3-H, JH3-H: V850ES/JH3-H

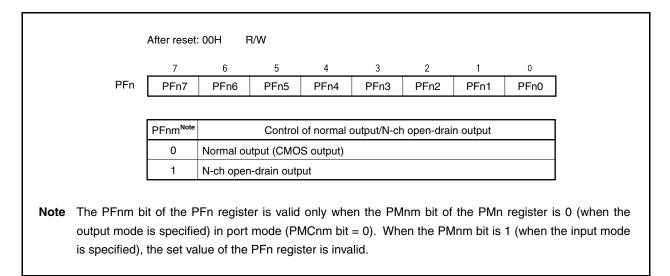

# (6) Port n function register (PFn)

The PFn register specifies normal output or N-ch open-drain output.

Each bit of this register corresponds to one pin of port n, and the output mode of the port pin can be specified in 1bit units.

| ( | 2/2 | ) |

|---|-----|---|

| ١ |     | 1 |

| V850ES/JH3 | 8-H      |           |              |               |             |            |       |       |  |  |

|------------|----------|-----------|--------------|---------------|-------------|------------|-------|-------|--|--|

|            | set: 00H | R/W       | Address: F   | FFFF440H      | I           |            |       |       |  |  |

|            | 7        | 6         | 5            | 4             | 3           | 2          | 1     | 0     |  |  |

| PMC0       | 0        | 0         | PMC05        | PMC04         | PMC03       | PMC02      | PMC01 | PMC00 |  |  |

|            |          |           |              |               |             |            | -     |       |  |  |

|            | PMC05    |           | Spe          | ecification o | f P05 pin o | peration m | iode  |       |  |  |

|            | 0        | I/O port  |              |               |             |            |       |       |  |  |

|            | 1        | INTP04 ii | nput         |               |             |            |       |       |  |  |

|            | PMC04    |           | Spe          | ecification o | f P04 pin c | peration m | ode   |       |  |  |

|            | 0        | I/O port  |              |               |             |            |       |       |  |  |

|            | 1        | INTP03 ii | INTP03 input |               |             |            |       |       |  |  |

|            | PMC03    |           | Spe          | ecification o | f P03 pin c | peration m | iode  |       |  |  |

|            | 0        | I/O port  |              |               | •           |            |       |       |  |  |

|            | 1        |           | nput/ADTR0   | G input/UCL   | _K input    |            |       |       |  |  |

|            | PMC02    |           | Spe          | ecification o | f P02 pin o | peration m | ode   |       |  |  |

|            | 0        | I/O port  |              |               |             |            |       |       |  |  |

|            | 1        | NMI inpu  | t            |               |             |            |       |       |  |  |

|            | PMC01    |           | Spe          | ecification o | f P01 pin c | peration m | lode  |       |  |  |

|            | 0        | I/O port  |              |               |             |            |       |       |  |  |

|            | 1        | INTP01 ii | nput         |               |             |            |       |       |  |  |

|            | PMC00    |           | Spe          | ecification o | f P00 pin c | peration m | lode  |       |  |  |

|            | 0        | I/O port  |              |               |             |            |       |       |  |  |

|            | 1        | INTP00 ii | nput         |               |             |            |       |       |  |  |

# (4) Port 0 function control register (PFC0)

| After res | et: 00H                     | 0H R/W Address: FFFFF460H |            |           |             |                  |         |            |              |  |

|-----------|-----------------------------|---------------------------|------------|-----------|-------------|------------------|---------|------------|--------------|--|

|           | 7                           | 6                         | 5          | 4         | 3           | 2                | 1       | 0          | _            |  |

| PFC0      | 0                           | 0                         | 0          | 0         | PFC03       | 0                | 0       | 0          |              |  |

| Remark    | For deta<br><b>specific</b> |                           | ernate fun | ction spe | cification, | see <b>4.3.1</b> | (6) Por | t 0 altern | ate function |  |

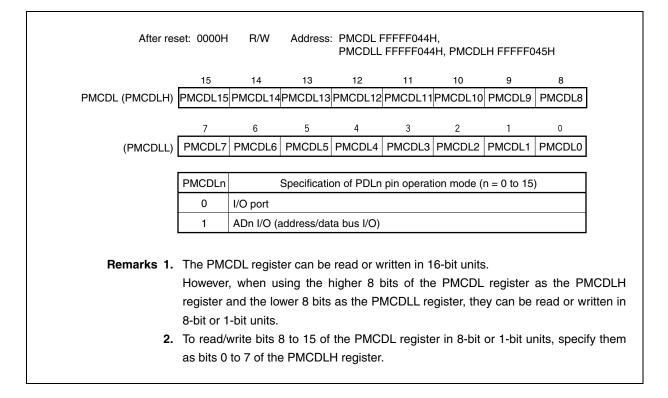

# (3) Port DL mode control register (PMCDL)

# 4.4 Port Register Settings When Alternate Function Is Used

Table 4-20 shows the port register settings when each port is used for an alternate function. When using a port pin as an alternate-function pin, refer to the description of each pin.

#### (e) Clearing overflow flag

The overflow flag can be cleared to 0 by clearing the TAAnOVF bit to 0 with the CLR instruction and by writing 8-bit data (bit 0 is 0) to the TAAnOPT0 register. To accurately detect an overflow, read the TAAnOVF bit when it is 1, and then clear the overflow flag by using a bit manipulation instruction.

| (i) Operation to write 0 (without conflict with setting)                   | (iii) Operation to clear to 0 (without conflict with setting)                                                             |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Overflow<br>set signal<br>0 write signal<br>Overflow flag<br>(TAAnOVF bit) | Overflow<br>set signal<br>0 write signal<br>Register<br>access signal Read Write<br>Overflow flag<br>(TAAnOVF bit)        |

| (ii) Operation to write 0 (conflict with setting)                          | (iv) Operation to clear to 0 (conflict with setting) Overflow Set signal O write signal Register Access signal Read Write |

| (TAAnOVF bit)                                                              | Overflow flag<br>(TAAnOVF bit)                                                                                            |

To clear the overflow flag to 0, read the overflow flag to check if it is set to 1, and clear it with the CLR instruction. If 0 is written to the overflow flag without checking if the flag is 1, the set information of the overflow may be erased by writing 0 ((ii) in the above chart). Therefore, software may judge that no overflow has occurred even when an overflow has actually occurred.

If execution of the CLR instruction conflicts with occurrence of an overflow when the overflow flag is cleared to 0 with the CLR instruction, the overflow flag remains set (1) even after execution of the clear instruction.

#### (2) Operation timing in pulse width measurement mode

#### (a) Clearing overflow flag

The overflow flag can be cleared to 0 by clearing the TAAnOVF bit to 0 with the CLR instruction and by writing 8-bit data (bit 0 is 0) to the TAAnOPT0 register. To accurately detect an overflow, read the TAAnOVF bit when it is 1, and then clear the overflow flag by using a bit manipulation instruction.

| (i) Operation to write 0 (without conflict with setting)                   | (iii) Operation to clear to 0 (without conflict with setting)                                                      |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Overflow<br>set signal<br>0 write signal<br>Overflow flag<br>(TAAnOVF bit) | Overflow<br>set signal<br>0 write signal<br>Register<br>access signal Read Write<br>Overflow flag<br>(TAAnOVF bit) |

| (ii) Operation to write 0 (conflict with setting)                          | (iv) Operation to clear to 0 (conflict with setting)                                                               |

| Overflow<br>set signal                                                     | Overflow<br>set signal                                                                                             |

| 0 write signal                                                             | 0 write signal                                                                                                     |

| Overflow flag<br>(TAAnOVF bit)                                             | Register Read Write                                                                                                |

|                                                                            | Overflow flag<br>(TAAnOVF bit)                                                                                     |

| <b>Remark</b> n = 0 to 3, 5                                                |                                                                                                                    |

To clear the overflow flag to 0, read the overflow flag to check if it is set to 1, and clear it with the CLR instruction. If 0 is written to the overflow flag without checking if the flag is 1, the set information of the overflow may be erased by writing 0 ((ii) in the above chart). Therefore, software may judge that no overflow has occurred even when an overflow has actually occurred.

If execution of the CLR instruction conflicts with occurrence of an overflow when the overflow flag is cleared to 0 with the CLR instruction, the overflow flag remains set (1) even after execution of the clear instruction.

# 8.5 Operation

TABn can perform the following operations.

| Operation                                            | TABnCTL1.TABnEST Bit<br>(Software Trigger Bit) | TIABn0 Pin<br>(External Trigger Input) | Capture/Compare<br>Register Setting | Compare Register<br>Write |

|------------------------------------------------------|------------------------------------------------|----------------------------------------|-------------------------------------|---------------------------|

| Interval timer mode                                  | Invalid                                        | Invalid                                | Compare only                        | Anytime write             |

| External event count mode <sup>Note 1</sup>          | Invalid                                        | Invalid                                | Compare only                        | Anytime write             |

| External trigger pulse output mode <sup>Note 2</sup> | Valid                                          | Valid                                  | Compare only                        | Batch write               |

| One-shot pulse output mode <sup>Note 2</sup>         | Valid                                          | Valid                                  | Compare only                        | Anytime write             |

| PWM output mode                                      | Invalid                                        | Invalid                                | Compare only                        | Batch write               |

| Free-running timer mode                              | Invalid                                        | Invalid                                | Switching enabled                   | Anytime write             |

| Pulse width measurement mode <sup>Note 2</sup>       | Invalid                                        | Invalid                                | Capture only                        | Not applicable            |

| Triangular wave PWM mode                             | Invalid                                        | Invalid                                | Compare only                        | Batch write               |

- **Notes 1.** To use the external event count mode, specify that the valid edge of the TIABn0 pin capture trigger input is not detected (by clearing the TABnIOC1.TABnIS1 and TABnIOC1.TABnIS0 bits to "00").

- 2. When using the external trigger pulse output mode, one-shot pulse output mode, and pulse width measurement mode, select the internal clock as the count clock (by clearing the TABnCTL1.TABnEEE bit to 0).

**Remark** n = 0, 1

# (2) TAB1 option register 2 (TAB1OPT2)

The TAB1OPT2 register is an 8-bit register that controls the timer Q option function.

This register can be rewritten when the TAB1CTL0.TAB1CE bit is 1. However, rewriting the TAB1DTM bit is prohibited when the TAB1CE bit is 1. The same value can be rewritten.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

| Allel I                                                          | eset: 00H                                                                                                                                                                                                                                                                     | R/W                                                                                                                                       | Addres                                                                                                                 | s: FFFFF5                                                                                                                       | 81H                                                                                                              |                                                                                |                                                                                            |                                                                     |                                                                                      |                                                |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------|

|                                                                  | <7>                                                                                                                                                                                                                                                                           | <6>                                                                                                                                       | <5>                                                                                                                    | <4>                                                                                                                             | <3>                                                                                                              | <2                                                                             | 2>                                                                                         | <1>                                                                 | <0>                                                                                  | _                                              |

| TAB1OPT2                                                         | TAB1RDE                                                                                                                                                                                                                                                                       | TAB1DTM                                                                                                                                   | TAB1ATM3                                                                                                               | TAB1ATM2                                                                                                                        | TAB1AT                                                                                                           | 3 TAB1                                                                         | AT2                                                                                        | TAB1AT1                                                             | TAB1AT0                                                                              | )                                              |

|                                                                  | TAB1RDE                                                                                                                                                                                                                                                                       |                                                                                                                                           |                                                                                                                        | Trans                                                                                                                           | fer culling                                                                                                      | enable                                                                         | ;                                                                                          |                                                                     |                                                                                      | 1                                              |

|                                                                  | 0                                                                                                                                                                                                                                                                             | Do not cul<br>and valley                                                                                                                  | ,                                                                                                                      | transfer tin                                                                                                                    | iing is gen                                                                                                      | erated                                                                         | every                                                                                      | time at c                                                           | rest                                                                                 | 1                                              |

|                                                                  | 1                                                                                                                                                                                                                                                                             | Cull transformed register.                                                                                                                | er at the s                                                                                                            | ame interv                                                                                                                      | al as interr                                                                                                     | upt cul                                                                        | ling se                                                                                    | et by the ∃                                                         | TAB1OPT1                                                                             |                                                |

|                                                                  | TAB1DTM                                                                                                                                                                                                                                                                       | D                                                                                                                                         | ead-time o                                                                                                             | counter ope                                                                                                                     | ration mo                                                                                                        | de sele                                                                        | ection                                                                                     | m = 1 to                                                            | 3)                                                                                   | 1                                              |

|                                                                  | TAB1DTM     Dead-time counter operation mode selection (m = 1 to 3)       0     The dead-time counter counts up normally and, if TOAB1m output of TAB1 is at a narrow interval (TOAB1m output width < dead-time width), the dead-time counter is cleared and counts up again. |                                                                                                                                           |                                                                                                                        |                                                                                                                                 |                                                                                                                  |                                                                                |                                                                                            |                                                                     |                                                                                      |                                                |

|                                                                  | 1 The dead-time counter counts up normally and, if TOAB1m output of TAB1 is at a narrow interval (TOAB1m output width < dead-time width), the dead-time counter counts down and the dead-time control width is automatically narrowed.                                        |                                                                                                                                           |                                                                                                                        |                                                                                                                                 |                                                                                                                  |                                                                                |                                                                                            |                                                                     |                                                                                      |                                                |

|                                                                  |                                                                                                                                                                                                                                                                               | the TAB1D<br>stop the time<br>d bit.                                                                                                      |                                                                                                                        |                                                                                                                                 | 0                                                                                                                | •                                                                              |                                                                                            |                                                                     |                                                                                      | ]                                              |

|                                                                  |                                                                                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                                        |                                                                                                                                 |                                                                                                                  |                                                                                |                                                                                            |                                                                     |                                                                                      |                                                |

| set<br>Thi:<br>and<br>(TA                                        | en using i<br>to other th<br>s means th<br>I transfers<br>B1RDE bit<br>en genera                                                                                                                                                                                              | han 00000)<br>hat interru<br>, cannot k<br>t = 0), tran                                                                                   | ), be sure<br>opts and<br>be set se<br>sfers are                                                                       | e to set th<br>transfers<br>parately<br>e not perf                                                                              | e TAB1F<br>are ger<br>If inter<br>ormed n                                                                        | RDE binerate<br>rupts<br>ormal                                                 | it to 1<br>d at t<br>and f<br>ly.                                                          | he sam<br>transfer                                                  | e timing.<br>s are set                                                               | Inter<br>sepa                                  |

| Thi:<br>and<br>(TA<br>2. Wh<br>Not<br>not<br>TO/<br>take<br>pin: | to other th<br>s means th<br>I transfers<br>B1RDE bit                                                                                                                                                                                                                         | han 00000<br>hat interru<br>, cannot k<br>= 0), tran<br>ting a dea<br>te operatio<br>d, so the<br>s are in the<br>s such as<br>a high-imp | ), be sure<br>opts and<br>be set se<br>sfers are<br>d-time po<br>out sto<br>output<br>neir defa<br>s making<br>pedance | e to set th<br>transfers<br>parately.<br>e not perf<br>eriod, set<br>pped (TA<br>levels of<br>ult states<br>the TOA<br>state be | the TAB1F<br>are ger<br>If inter<br>ormed n<br>the TAB<br>B1CTL0.<br>the TO/<br>a. There<br>B1T1 to<br>fore stop | RDE bi<br>nerate<br>rupts<br>ormal<br>1DTC<br>TAB1<br>AB1T1<br>fore, 1<br>TOAE | it to 1<br>d at 1<br>and 1<br>ly.<br>regis<br>CE bi<br>I to <sup>-</sup><br>for th<br>B1T3 | transfer<br>ster to 1<br>it = 0), a<br>TOAB1T<br>ie prote<br>and TO | e timing.<br>s are set<br>or highe<br>dead-tim<br>3 and To<br>ction of t<br>AB1B1 to | Inter<br>sepa<br>r.<br>OAB1<br>the sy<br>o TOA |

# (3) Intermittent batch rewrite mode (transfer culling mode)

This mode is set by clearing the TAB1OPT0.TAB1CMS bit to 0 and setting the TAB1OPT2.TAB1RDE bit to 1. In this mode, the values written to each compare register are transferred to the internal buffer register all at once after the culled transfer timing and compared with the counter value. The transfer timing is the timing at which an interrupt is generated (INTTAB1CC0, INTTAB1OV) by interrupt culling.

For details of the interrupt culling function, see **11.4.3** Interrupt culling function.

### (a) Rewriting procedure

If data is written to the TAB1CCR1 register, the data of the TAB1CCR0 to TAB1CCR3, TAB1OPT1, TAA4CCR0, and TAA4CCR1 registers are transferred all at once to the internal buffer register at the next transfer timing. Therefore, write to the TAB1CCR1 register last. Writing to the register is prohibited after the TAB1CCR1 register has been written until the transfer timing is generated (until the INTTAB1OV or INTTAB1CC0 interrupt occurs). The operation procedure is as follows.

- <1> Rewrite the TAB1CCR0, TAB1CCR2, TAB1CCR3, TAB1OPT1, TAA4CCR0, and TAA4CCR1 registers. Do not rewrite registers that do not have to be rewritten.

- <2> Rewrite the TAB1CCR1 register.

Rewrite the same value to the register even when it is not necessary to rewrite the TAB1CCR1 register.

<3> Hold the next rewriting pending until the transfer timing is generated.

Perform the next rewrite after the INTTAB1OV or INTTAB1CC0 interrupt has occurred.

<4> Return to <1>.

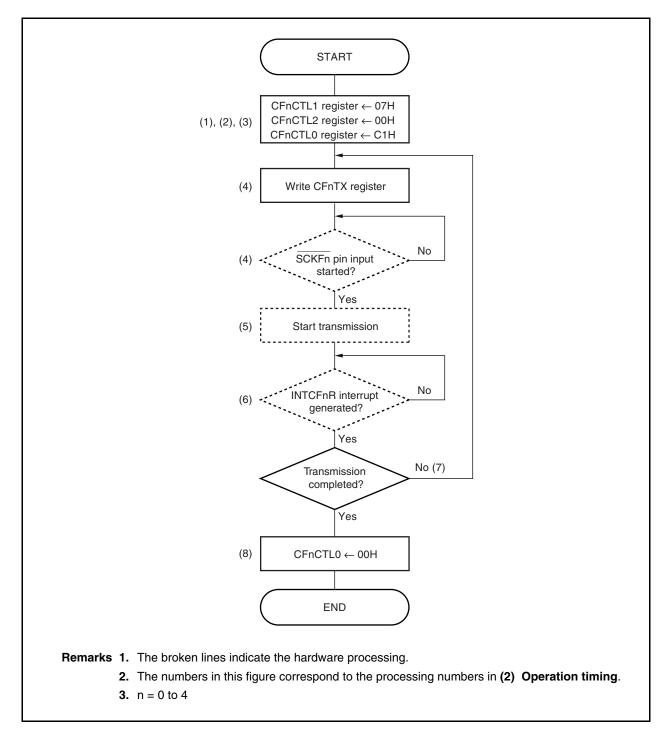

# 18.6.4 Single transfer mode (slave mode, transmission mode)

MSB first (CFnCTL0.CFnDIR bit = 0), communication type 1 (CFnCTL1.CFnCKP and CFnCTL1.CFnDAP bits = 00), communication clock ( $f_{CCLK}$ ) = external clock ( $\overline{SCKFn}$ ) (CFnCTL1.CFnCKS2 to CFnCTL1.CFnCKS0 bits = 111), transfer data length = 8 bits (CFnCTL2.CFnCL3 to CFnCTL2.CFnCL0 bits = 0000)

# (1) Operation flow

## 19.1.2 UARTC4, CSIF0, and I<sup>2</sup>C01 mode switching

In the V850ES/JG3-H and V850ES/JH3-H, UARTC4, CSIF0, and I<sup>2</sup>C01 share the same pins and therefore cannot be used simultaneously. Switching among UARTC4, CSIF0, and I<sup>2</sup>C01 must be set in advance, using the PMC4, PFC4, and PFCE4 registers.

# Caution The transmit/receive operation of UARTC4, CSIF0, and I<sup>2</sup>C01 is not guaranteed if these functions are switched during transmission or reception. Be sure to disable the one that is not used.

| After re | set: 00H  | R/W             | Address:   | FFFFF448F              | 1        |        |        |        |

|----------|-----------|-----------------|------------|------------------------|----------|--------|--------|--------|

| Allerie  | 361. 0011 | 10,00           | Address.   | 11111440               |          |        |        |        |

|          | 7         | 6               | 5          | 4                      | 3        | 2      | 1      | 0      |

| PMC4     | 0         | 0               | 0          | 0                      | 0        | PMC42  | PMC41  | PMC40  |

|          |           |                 |            |                        |          |        |        |        |

| After re | set: 00H  | R/W             | Address:   | FFFF468H               | ł        |        |        |        |

|          | 7         | 6               | 5          | 4                      | 3        | 2      | 1      | 0      |

| PFC4     | 0         | 0               | 0          | 0                      | 0        | PFC42  | PFC41  | PFC40  |

|          |           |                 |            |                        |          |        |        |        |

| After re | set: 00H  | R/W             | Address:   | FFFF708H               | ł        |        |        |        |

|          | 7         | 6               | 5          | 4                      | 3        | 2      | 1      | 0      |

| PFCE4    | 0         | 0               | 0          | 0                      | 0        | 0      | PFCE41 | PFCE40 |

|          |           |                 |            |                        |          |        |        |        |

|          | PMC4n     | PFC4n           | PFCE4n     |                        | Operatio | n mode |        |        |

|          | 0         | ×               | ×          | Port I/O m             | ode      |        |        |        |

|          | 1         | 0               | 0          | CSIF0 mo               | de       |        |        |        |

|          | 1         | 0               | 1          | I <sup>2</sup> C01 mod | le       |        |        |        |

|          | 1         | 1               | 0          | UARTC4 r               | node     |        |        |        |

|          | Remarks   | s <b>1.</b> n=0 | 0, 1       |                        |          |        |        |        |

|          |           | <b>2.</b> × = 0 | don't care |                        |          |        |        |        |

Figure 19-2. UARTC4, CSIF0, and I<sup>2</sup>C01 Mode Switch Settings

## (3) When arbitration loss occurs during data transfer

# (9) CAN0 module error counter register (C0ERC)

The C0ERC register indicates the count value of the transmission/reception error counter.

|             | 15         | 14                                                                                                                                                   | 13             | 12                              | 11           | 10             | 9            | 8            |  |  |  |  |

|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------|--------------|----------------|--------------|--------------|--|--|--|--|

| C0ERC       | REPS       | REC6                                                                                                                                                 | REC5           | REC4                            | REC3         | REC2           | REC1         | REC0         |  |  |  |  |

|             | 7          | 6                                                                                                                                                    | 5              | 4                               | 3            | 2              | 1            | 0            |  |  |  |  |

|             | TEC7       | TEC6                                                                                                                                                 | TEC5           | TEC4                            | TEC3         | TEC2           | TEC1         | TEC0         |  |  |  |  |

| REPS        |            | Reception error passive status bit                                                                                                                   |                |                                 |              |                |              |              |  |  |  |  |

| 0           | The valu   | The value of the reception error counter is not error passive (< 128)                                                                                |                |                                 |              |                |              |              |  |  |  |  |

| 1           | The valu   | e of the rece                                                                                                                                        | ption error co | ounter is in the                | error passiv | re range (≥ 12 | 28)          |              |  |  |  |  |

|             |            |                                                                                                                                                      |                |                                 |              |                |              |              |  |  |  |  |

| REC6 to REC | 0          |                                                                                                                                                      |                | Reception e                     | rror counter | bit            |              |              |  |  |  |  |

| 0 to 127    |            | •                                                                                                                                                    |                | e bits reflect t<br>CAN protoco |              | he reception   | error counte | r. The       |  |  |  |  |

|             | REC6 to RI |                                                                                                                                                      | RECS0 bit      |                                 |              |                | ception err  | or passive : |  |  |  |  |

| TEC/ IO TEC | -          |                                                                                                                                                      |                |                                 |              |                |              |              |  |  |  |  |

| 0 to 255    |            | Number of transmission errors. These bits reflect the status of the transmission error counter. The number of errors is defined by the CAN protocol. |                |                                 |              |                |              |              |  |  |  |  |

(2/2)

# (a) Read

| TSLOCK | Time stamp lock function enable bit                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Time stamp lock function stopped.<br>The TSOUT signal toggles each time the selected time stamp capture event occurs.                                                                                                                                        |

| 1      | Time stamp lock function enabled.<br>The TSOUT signal toggled each time the selected time stamp capture event occurred. However, the<br>TSOUT output signal is locked when a data frame has been correctly received to message buffer<br>0 <sup>Note</sup> . |

Note The TSEN bit is automatically cleared to 0.

| TSSEL | Time stamp capture event selection bit               |

|-------|------------------------------------------------------|

| 0     | The time stamp capture event is SOF.                 |

| 1     | The time stamp capture event is the last bit of EOF. |

| TSEN | TSOUT operation setting bit         |  |  |  |  |  |

|------|-------------------------------------|--|--|--|--|--|

| 0    | TSOUT toggle operation is disabled. |  |  |  |  |  |

| 1    | TSOUT toggle operation is enabled.  |  |  |  |  |  |

|      |                                     |  |  |  |  |  |

Remark The TSOUT signal is output from the CAN controller to a timer. For details, refer to CHAPTER 7 16-BIT TIMER/EVENT COUNTER A (TAA).

## (b) Write

| Set TSLOCK       | Clear TSLOCK | Setting of TSLOCK bit       |  |  |  |

|------------------|--------------|-----------------------------|--|--|--|

| 0                | 1            | TSLOCK bit is cleared to 0. |  |  |  |

| 1                | 0            | TSLOCK bit is set to 1.     |  |  |  |

| Other than above |              | TSLOCK bit is not changed.  |  |  |  |

| Set TSSEL        | Clear TSSEL | Setting of TSSEL bit      |  |  |  |  |

|------------------|-------------|---------------------------|--|--|--|--|

| 0                | 1           | SSEL bit is cleared to 0. |  |  |  |  |

| 1                | 0           | TSSEL bit is set to 1.    |  |  |  |  |

| Other than above |             | TSSEL bit is not changed. |  |  |  |  |

| Set TSEN         | Clear TSEN | Setting of TSEN bit      |  |  |  |  |

|------------------|------------|--------------------------|--|--|--|--|

| 0                | 1          | SEN bit is cleared to 0. |  |  |  |  |

| 1                | 0          | TSEN bit is set to 1.    |  |  |  |  |

| Other than above |            | TSEN bit is not changed. |  |  |  |  |

## (29) UF0 FIFO clear 0 register (UF0FIC0)

This register clears each FIFO.

This register is write-only, in 8-bit units. If this register is read, 00H is read.

FW can clear the target FIFO by writing 1 to the corresponding bit of this register. The bit to which 1 has been written is automatically cleared to 0. Writing 0 to the bit is invalid.

The related bits are invalid if each endpoint is not supported by the setting of the UF0EnIM register (n = 1, 3, 7) and the current setting of the interface.

|             | 7      | 6        | 5                                   | 4                                                                                                                                                                                                                                                                                                                                                                              | 3            | 2                                          | 1            | 0          | Address          | After reset   |  |

|-------------|--------|----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|--------------|------------|------------------|---------------|--|

|             | BKI2SC | BKI2CC   | BKI1SC                              | BKI1CC                                                                                                                                                                                                                                                                                                                                                                         | ITR2C        | ITR1C                                      | EP0WC        | EP0RC      | 00200060H        | 00H           |  |

|             |        |          |                                     |                                                                                                                                                                                                                                                                                                                                                                                |              |                                            |              |            |                  |               |  |

| Bit positio | n      | Bit name |                                     | Function                                                                                                                                                                                                                                                                                                                                                                       |              |                                            |              |            |                  |               |  |

| 7, 5        | BKI    | InSC     | 1: C<br>Writing<br>BKInNł<br>The BK | These bits clear only the FIFO on the SIE side of the UF0BIn register (reset the counter<br>1: Clear<br>Writing these bits is invalid while an IN token for Endpoint m is being processed with the<br>BKInNK bit set to 1.<br>The BKInNK bit is automatically cleared to 0 by clearing the FIFO. Make sure that the<br>FIFO on the CPU side is empty when these bits are used. |              |                                            |              |            |                  |               |  |

| 6, 4        | BKI    | InCC     |                                     | bits clear oi<br>Clear                                                                                                                                                                                                                                                                                                                                                         | nly the FIF  | O on the C                                 | PU side of   | the UF0BIn | register (reset  | the counter). |  |

| 2           | ITR    | 1C       | 1: C<br>Writing<br>IT1NK            | These bits clear the UF0INT1 register (reset the counter).<br>1: Clear<br>Writing these bits is invalid while an IN token for Endpoint 7 is being processed with the<br>IT1NK bit set to 1.<br>The IT1NK bit is automatically cleared to 0 by clearing the FIFO.                                                                                                               |              |                                            |              |            |                  |               |  |

| 1           | EPO    | DWC      | 1: C<br>Writing<br>EP0NK            | This bit clears the UF0E0W register (resets the counter).<br>1: Clear<br>Writing this bit is invalid while an IN token for Endpoint0 is being processed with the<br>EP0NKW bit set to 1.<br>The EP0NKW bit is automatically cleared to 0 by clearing the FIFO.                                                                                                                 |              |                                            |              |            |                  |               |  |

| 0           | EP     | ORC      | 1: C<br>When t                      | lear<br>he EP0NKI                                                                                                                                                                                                                                                                                                                                                              | R bit is set | egister (res<br>to 1 (excep<br>clearing th | ot when it h | ,          | t by FW), the EF | PONKR bit is  |  |

m = 3 where n = 2

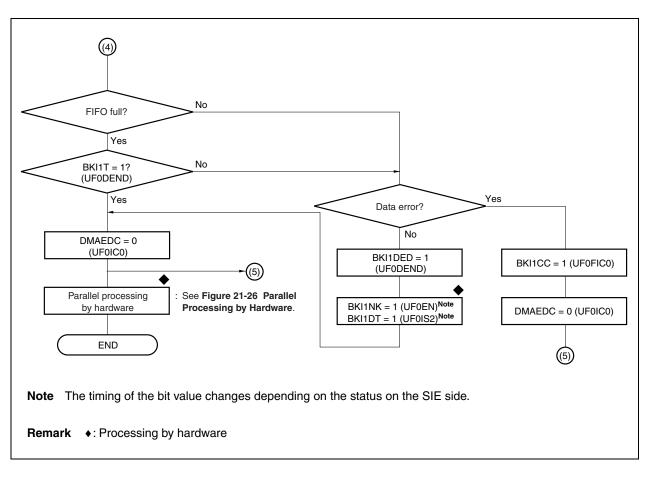

Figure 21-33 DMA Processing by Bulk Transfer (IN) (4/4)

#### (4) DMA addressing control registers 0 to 3 (DADC0 to DADC3)

The DADC0 to DADC3 registers are 16-bit registers that control the DMA transfer mode for DMA channel n (n = 0 to 3).

These registers can be read or written in 16-bit units.

Reset sets these registers to 0000H.

|              | 15         | 14         | 13         | 12           | 11           | 10            | 9           | 8         |

|--------------|------------|------------|------------|--------------|--------------|---------------|-------------|-----------|

| DADCn        | 0          | DS0        | 0          | 0            | 0            | 0             | 0           | 0         |

| (n = 0 to 3) | 7          | 6          | 5          | 4            | 3            | 2             | 1           | 0         |

|              | ,<br>SAD1  | SAD0       | DAD1       | DAD0         | 0            | 0             | 0           | 0         |

|              | 0/101      | 0,120      | BRBT       | BRBO         | 0            | 0             | Ū           |           |

|              |            | 1          |            |              |              |               |             |           |

|              | DS0        |            |            | Setting of   | of transfer  | data size     |             |           |

|              | 0          | 8 bits     |            |              |              |               |             |           |

|              | 1          | 16 bits    |            |              |              |               |             |           |

|              | SAD1       | SAD0       | Setting    | g of count c | lirection of | f the transfe | er source a | ddress    |

|              | 0          | 0          | Incremen   | t            |              |               |             |           |

|              | 0          | 1          | Decrement  |              |              |               |             |           |

|              | 1          | 0          | Fixed      |              |              |               |             |           |

|              | 1          | 1          | Setting pr | rohibited    |              |               |             |           |

|              | DAD1       | DAD0       | Cotti      | ing of count | direction    | of the desti  | notion odd  | ****      |

|              | 0          | 0          | Incremen   | ing of count | airection    | or the dest   | nation add  | less      |

|              | 0          | 1          | Decreme    | -            |              |               |             |           |

|              | 1          | 0          | Fixed      |              |              |               |             |           |

|              | 1          | 1          | Setting pr | rohibited    |              |               |             |           |

|              |            |            | County pr  |              |              |               |             |           |

| s 1. Be sure | to clear b | its 15. 13 | to 8. and  | 3 to 0 of    | the DAD      | Cn reaist     | er to 0.    |           |

| 2. Set the   |            |            |            |              |              | -             |             | sabled (E |

| bit = 0).    |            | <b>J</b>   |            | 5            | 5            |               |             |           |

- Period from after completion of DMA transfer (DCHCn.TCn bit = 1) to start of the next DMA transfer

- 3. The DS0 bit specifies the size of the transfer data, and does not control bus sizing. If 8-bit data (DS0 bit = 0) is set, therefore, the lower data bus is not always used.

- 4. If the transfer data size is set to 16 bits (DS0 bit = 1), transfer cannot be started from an odd address. Transfer is always started from an address with the first bit of the lower address aligned to 0.

- 5. If DMA transfer is executed on an on-chip peripheral I/O register (as the transfer source or destination), be sure to specify the same transfer size as the register size. For example, to execute DMA transfer on an 8-bit register, be sure to specify 8-bit transfer.

## 22.9 DMA Transfer Start Factors

There are two types of DMA transfer start factors, as shown below.

#### (1) Request by software

If the STGn bit is set to 1 while the DCHCn.TCn bit = 1 and Enn bit = 1 (DMA transfer enabled), DMA transfer is started.

To request the next DMA transfer cycle immediately after that, confirm, by using the DBCn register, that the preceding DMA transfer cycle has been completed, and set the STGn bit to 1 again (n = 0 to 3).

TCn bit = 0, Enn bit = 1  $\downarrow$ STGn bit = 1 ... Starts the first DMA transfer.  $\downarrow$ Confirm that the contents of the DBCn register have been updated. STGn bit = 1 ... Starts the second DMA transfer.  $\downarrow$ :  $\downarrow$

Generation of terminal count ... Enn bit = 0, TCn bit = 1, and INTDMAn signal is generated.

#### (2) Request by on-chip peripheral I/O

If an interrupt request is generated from the on-chip peripheral I/O set by the DTFRn register when the DCHCn.TCn bit = 0 and Enn bit = 1 (DMA transfer enabled), DMA transfer is started.

- Cautions 1. Two start factors (software trigger and hardware trigger) cannot be used for one DMA channel. If two start factors are simultaneously generated for one DMA channel, only one of them is valid. The start factor that is valid cannot be identified.

- 2. A new transfer request that is generated after the preceding DMA transfer request was generated or in the preceding DMA transfer cycle is ignored (cleared).

- 3. The transfer request interval of the same DMA channel varies depending on the setting of bus wait in the DMA transfer cycle, the start status of the other channels, or the external bus hold request. In particular, as described in Caution 2, a new transfer request that is generated for the same channel before the DMA transfer cycle or during the DMA transfer cycle is ignored. Therefore, the transfer request intervals for the same DMA channel must be sufficiently separated by the system. When the software trigger is used, completion of the DMA transfer cycle that was generated before can be checked by updating the DBCn register.

| <5> QB-V850ESJX3H <sup>Note</sup><br>In-circuit emulator                                          | The in-circuit emulator serves to debug hardware and software when developing application systems using the V850ES/JG3-H or V850ES/JH3-H. It supports the integrated debugger ID850QB. This emulator should be used in combination with a power supply unit and emulation probe. Use the USB interface cable to connect this emulator to the host machine. |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <3> USB interface cable                                                                           | Cable to connect the host machine and the QB-V850ESJX3H.                                                                                                                                                                                                                                                                                                   |

| <4> AC adapter                                                                                    | 100 to 240 V can be supported by replacing the AC plug.                                                                                                                                                                                                                                                                                                    |

| <9> QB-100GC-EA-04S<br>QB-128GF-EA-01S<br>QB-100GC-EA-05T<br>QB-128GF-EA-02T<br>Exchange adapter  | Adapter to perform pin conversion.<br>• QB-100GC-EA-04S: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-EA-01S: 128-pin plastic LQFP (GF-GAT type)<br>• QB-100GC-EA-05T: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-EA-02T: 128-pin plastic LQFP (GC-GAT type)                                                                                     |

| <10> QB-100-CA-01S<br>QB-128-CA-01S<br>(S type only)<br>Check pin adapter                         | Adapter used in waveform monitoring using the oscilloscope, etc.<br>• QB-100-CA-01S: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128-CA-01S: 128-pin plastic LQFP (GF-GAT type)                                                                                                                                                                             |

| <11> QB-100-SA-01S<br>QB-144-SA-01S<br>QB-100GC-YS-01T<br>QB-128GF-YS-01T<br>Space adapter        | Adapter to adjust the height.<br>• QB-100-SA-01S: 100-pin plastic LQFP (GC-UEU type)<br>• QB-144-SA-01S: 128-pin plastic LQFP (GF-GAT type)<br>• QB-100GC-YS-01T: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-YS-01T: 128-pin plastic LQFP (GF-GAT type)                                                                                              |

| <12> QB-100GC-YQ-01T<br>QB-128GF-YQ-01T<br>(T type only)<br>YQ connector                          | Conversion adapter to connect target connector and exchange adapter<br>• QB-100GC-YQ-01T: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-YQ-01T: 128-pin plastic LQFP (GF-GAT type)                                                                                                                                                                      |

| <13> QB-100GC-MA-01S<br>QB-128GF-MA-01S<br>QB-100GC-HQ-01T<br>QB-128GF-HQ-01T<br>Mount adapter    | Adapter to mount the V850ES/JG3-H or V850ES/JH3-H on a socket.<br>• QB-100GC-MA-01S: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-MA-01S: 128-pin plastic LQFP (GF-GAT type)<br>• QB-100GC-HQ-01T: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-HQ-01T: 128-pin plastic LQFP (GF-GAT type)                                                         |

| <14> QB-100GC-TC-01S<br>QB-128GF-TC-01S<br>QB-100GC-NQ-01T<br>QB-128GF-NQ-01T<br>Target connector | Connector to solder on the target system.<br>• QB-100GC-TC-01S: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-TC-01S: 128-pin plastic LQFP (GF-GAT type)<br>• QB-100GC-NQ-01T: 100-pin plastic LQFP (GC-UEU type)<br>• QB-128GF-NQ-01T: 128-pin plastic LQFP (GF-GAT type)                                                                              |

**Note** The QB-V850ESJX3H is supplied with a power supply unit, USB interface cable, and flash memory programmer (MINICUBE2). It is also supplied with integrated debugger ID850QB as control software.

**Remark** The numbers in the angle brackets correspond to the numbers in Figure A-2.

|            |                                      |      | (6/37 |

|------------|--------------------------------------|------|-------|

| Symbol     | Name                                 | Unit | Page  |

| COMDATA110 | CAN0 message data byte 1 register 10 | CAN  | 969   |

| COMDATA111 | CAN0 message data byte 1 register 11 | CAN  | 969   |

| COMDATA112 | CAN0 message data byte 1 register 12 | CAN  | 969   |

| C0MDATA113 | CAN0 message data byte 1 register 13 | CAN  | 969   |

| C0MDATA114 | CAN0 message data byte 1 register 14 | CAN  | 969   |

| C0MDATA115 | CAN0 message data byte 1 register 15 | CAN  | 969   |

| C0MDATA116 | CAN0 message data byte 1 register 16 | CAN  | 969   |

| C0MDATA117 | CAN0 message data byte 1 register 17 | CAN  | 969   |

| COMDATA118 | CAN0 message data byte 1 register 18 | CAN  | 969   |

| COMDATA119 | CAN0 message data byte 1 register 19 | CAN  | 969   |

| COMDATA120 | CAN0 message data byte 1 register 20 | CAN  | 969   |

| COMDATA121 | CAN0 message data byte 1 register 21 | CAN  | 969   |

| C0MDATA122 | CAN0 message data byte 1 register 22 | CAN  | 969   |

| C0MDATA123 | CAN0 message data byte 1 register 23 | CAN  | 969   |

| C0MDATA124 | CAN0 message data byte 1 register 24 | CAN  | 969   |

| C0MDATA125 | CAN0 message data byte 1 register 25 | CAN  | 969   |

| COMDATA126 | CAN0 message data byte 1 register 26 | CAN  | 969   |

| COMDATA127 | CAN0 message data byte 1 register 27 | CAN  | 969   |

| COMDATA128 | CAN0 message data byte 1 register 28 | CAN  | 969   |

| C0MDATA129 | CAN0 message data byte 1 register 29 | CAN  | 969   |

| COMDATA130 | CAN0 message data byte 1 register 30 | CAN  | 969   |

| COMDATA131 | CAN0 message data byte 1 register 31 | CAN  | 969   |

| COMDATA200 | CAN0 message data byte 2 register 00 | CAN  | 969   |

| COMDATA201 | CAN0 message data byte 2 register 01 | CAN  | 969   |

| COMDATA202 | CAN0 message data byte 2 register 02 | CAN  | 969   |

| C0MDATA203 | CAN0 message data byte 2 register 03 | CAN  | 969   |

| COMDATA204 | CAN0 message data byte 2 register 04 | CAN  | 969   |

| COMDATA205 | CAN0 message data byte 2 register 05 | CAN  | 969   |

| COMDATA206 | CAN0 message data byte 2 register 06 | CAN  | 969   |

| COMDATA207 | CAN0 message data byte 2 register 07 | CAN  | 969   |

| COMDATA208 | CAN0 message data byte 2 register 08 | CAN  | 969   |

| COMDATA209 | CAN0 message data byte 2 register 09 | CAN  | 969   |

| COMDATA210 | CAN0 message data byte 2 register 10 | CAN  | 969   |

| COMDATA211 | CAN0 message data byte 2 register 11 | CAN  | 969   |

| C0MDATA212 | CAN0 message data byte 2 register 12 | CAN  | 969   |

| C0MDATA213 | CAN0 message data byte 2 register 13 | CAN  | 969   |

| COMDATA214 | CAN0 message data byte 2 register 14 | CAN  | 969   |

| COMDATA215 | CAN0 message data byte 2 register 15 | CAN  | 969   |

| COMDATA216 | CAN0 message data byte 2 register 16 | CAN  | 969   |

| C0MDATA217 | CAN0 message data byte 2 register 17 | CAN  | 969   |