# E. Renesas Electronics America Inc - UPD70F3767GF-GAT-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                                      |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 96                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 56K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 128-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3767gf-gat-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.4 Operation

## 6.4.1 Operation of each clock

The following table shows the operation status of each clock.

| Register Setting and                | -               |                                        |              |                         |              |                  |                     |                  |                     |  |

|-------------------------------------|-----------------|----------------------------------------|--------------|-------------------------|--------------|------------------|---------------------|------------------|---------------------|--|

| Operation Status                    |                 | CLK Bi                                 | t = 0, MCK   | Bit = 0                 |              |                  | Bit = 1,<br>Bit = 0 | CLS E<br>MCK     | Bit = 1,<br>Bit = 1 |  |

|                                     | During<br>Reset | During<br>Oscillation<br>Stabilization | HALT<br>Mode | IDLE1,<br>IDLE2<br>Mode | STOP<br>Mode | Subclock<br>Mode | Sub-IDLE<br>Mode    | Subclock<br>Mode | Sub-IDLE<br>Mode    |  |

| Target Clock                        |                 | Time Count                             |              |                         |              |                  |                     |                  |                     |  |

| Main clock oscillator (fx)          | ×               | 0                                      | 0            | 0                       | ×            | 0                | 0                   | ×                | ×                   |  |

| Subclock oscillator (fxr)           | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |

| CPU clock (fcpu)                    | ×               | ×                                      | ×            | ×                       | ×            | 0                | ×                   | 0                | ×                   |  |

| Internal system clock (fclk)        | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | 0                | ×                   |  |

| Main clock (in PLL mode, fxx)       | ×               | O <sup>Note</sup>                      | 0            | ×                       | ×            | 0                | 0                   | ×                | ×                   |  |

| Peripheral clock (fxx to fxx/1,024) | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | ×                | ×                   |  |

| WT clock (main)                     | ×               | 0                                      | 0            | 0                       | ×            | 0                | 0                   | ×                | ×                   |  |

| WT clock (sub)                      | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |

| WDT2 clock (internal oscillation)   | ×               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |

| WDT2 clock (main)                   | ×               | ×                                      | 0            | ×                       | ×            | 0                | ×                   | ×                | ×                   |  |

| WDT2 clock (sub)                    | 0               | 0                                      | 0            | 0                       | 0            | 0                | 0                   | 0                | 0                   |  |

### Table 6-1. Operation Status of Each Clock

Note Lockup time

#### Remark O: Operable

×: Stopped

#### 6.4.2 Clock output function

The clock output function is used to output the internal system clock (fcLK) from the CLKOUT pin.

The internal system clock (fcLK) is selected by using the PCC.CK3 to PCC.CK0 bits.

The CLKOUT pin functions alternately as the PCM1 pin and functions as a clock output pin if so specified by the control register of port CM.

The status of the CLKOUT pin is the same as the internal system clock in Table 6-1 and the pin can output the clock when it is in the operable status. It outputs a low level in the stopped status. However, the CLKOUT pin is in the port mode (PCM1 pin: input mode) after reset and until it is set in the output mode. Therefore, the status of the pin is Hi-Z.

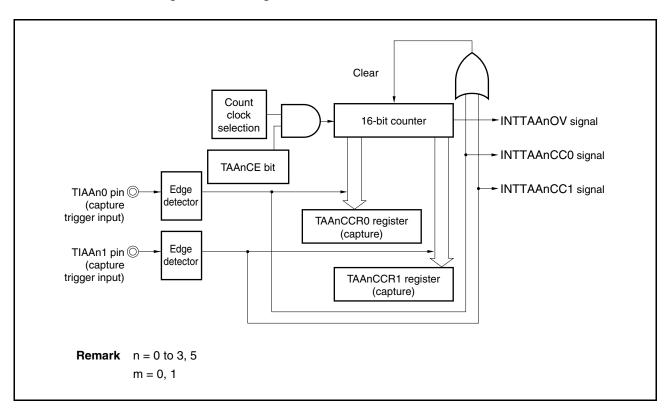

#### 7.5.7 Pulse width measurement mode (TAAnMD2 to TAAnMD0 bits = 110)

In the pulse width measurement mode, 16-bit timer/event counter AA starts counting when the TAAnCTL0.TAAnCE bit is set to 1. Each time the valid edge input to the TIAAnm pin has been detected, the count value of the 16-bit counter is stored in the TAAnCCRm register, and the 16-bit counter is cleared to 0000H.

The interval of the valid edge can be measured by reading the TAAnCCRm register after a capture interrupt request signal (INTTAAnCCm) occurs.

Select either the TIAAn0 or TIAAn1 pin as the capture trigger input pin. Specify "No edge detection" for the unused pins by using the TAAnIOC1 register.

When an external clock is used as the count clock, measure the pulse width of the TIAAn1 pin because the external clock is fixed to the TIAAn0 pin. At this time, clear the TAAnIOC1.TAAnIS1 and TAAnIOC1.TAAnIS0 bits to 00 (capture trigger input (TIAAn0 pin): No edge detection).

Figure 7-39. Configuration in Pulse Width Measurement Mode

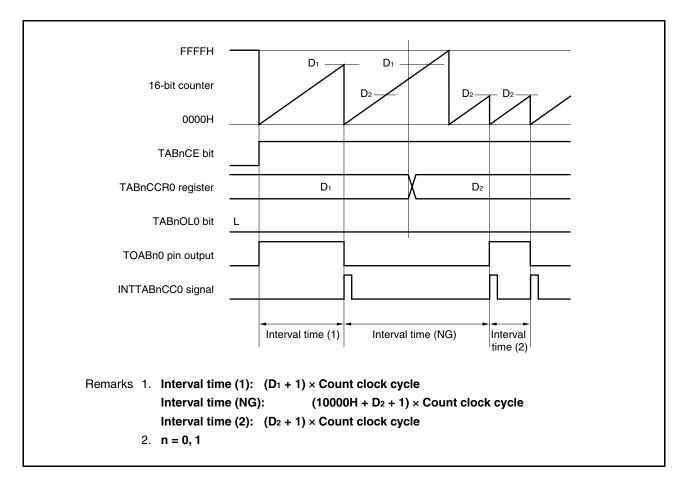

#### (c) Notes on rewriting TABnCCR0 register

To change the value of the TABnCCR0 register to a smaller value, stop counting once and then change the set value.

If the value of the TABnCCR0 register is rewritten to a smaller value during counting, the 16-bit counter may overflow.

If the value of the TABnCCR0 register is changed from  $D_1$  to  $D_2$  while the count value is greater than  $D_2$  but less than  $D_1$ , the count value is transferred to the CCR0 buffer register as soon as the TABnCCR0 register has been rewritten. Consequently, the value of the 16-bit counter that is compared is  $D_2$ .

Because the count value has already exceeded D<sub>2</sub>, however, the 16-bit counter counts up to FFFFH, overflows, and then counts up again from 0000H. When the count value matches D<sub>2</sub>, the INTTABnCC0 signal is generated and the output of the TOABn0 pin is inverted.

Therefore, the INTTABnCC0 signal may not be generated at the interval time " $(D_1 + 1) \times \text{Count clock cycle}$ " or " $(D_2 + 1) \times \text{Count clock cycle}$ " originally expected, but may be generated at an interval of " $(10000H + D_2 + 1) \times \text{Count clock period}$ ".

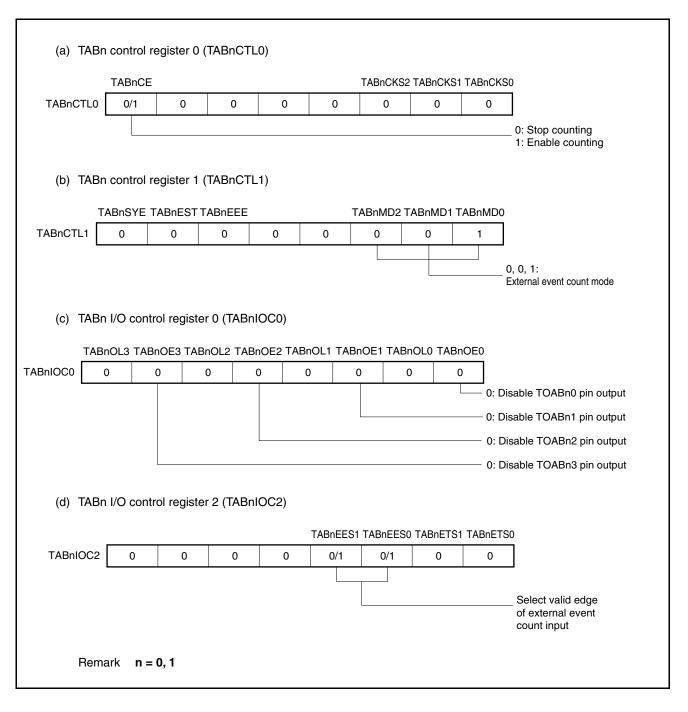

When the TABnCE bit is set to 1, the value of the 16-bit counter is cleared from FFFFH to 0000H. The counter counts each time the valid edge of the external event count input is detected. Additionally, the set value of the TABnCCR0 register is transferred to the CCR0 buffer register.

When the count value of the 16-bit counter matches the value of the CCR0 buffer register, the 16-bit counter is cleared to 0000H, and a compare match interrupt request signal (INTTABnCC0) is generated.

The INTTABnCC0 signal is generated each time the valid edge of the external event count input has been detected (set value of TABnCCR0 register + 1) times.

Figure 8-11. Register Setting for Operation in External Event Count Mode (1/2)

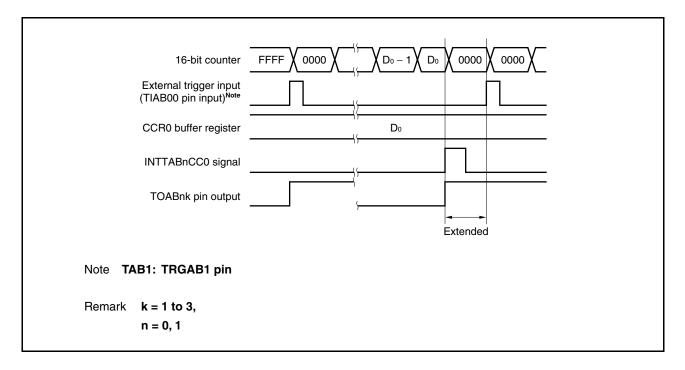

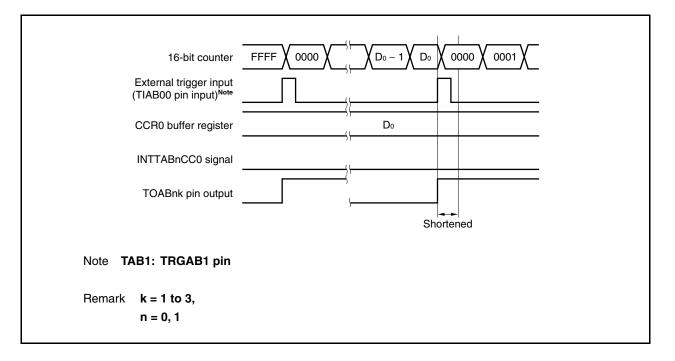

#### (d) Conflict between trigger detection and match with CCR0 buffer register

If the trigger is detected immediately after the INTTABnCC0 signal is generated, the 16-bit counter is cleared to 0000H and continues counting up. Therefore, the active period of the TOABnk pin is extended by time from generation of the INTTABnCC0 signal to trigger detection.

If the trigger is detected immediately before the INTTABnCC0 signal is generated, the INTTABnCC0 signal is not generated. The 16-bit counter is cleared to 0000H, the TOABnk pin is asserted, and the counter continues counting. Consequently, the inactive period of the PWM waveform is shortened.

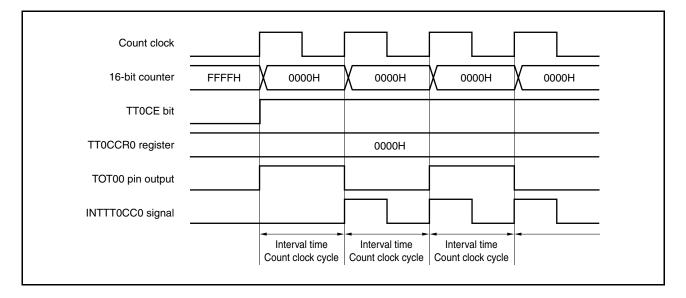

#### (2) Interval timer mode operation timing

## (a) Operation if TT0CCR0 register is set to 0000H

If the TT0CCR0 register is set to 0000H, the INTTT0CC0 signal is generated at each count clock, and the output of the TOT00 pin is inverted.

The value of the 16-bit counter is always 0000H.

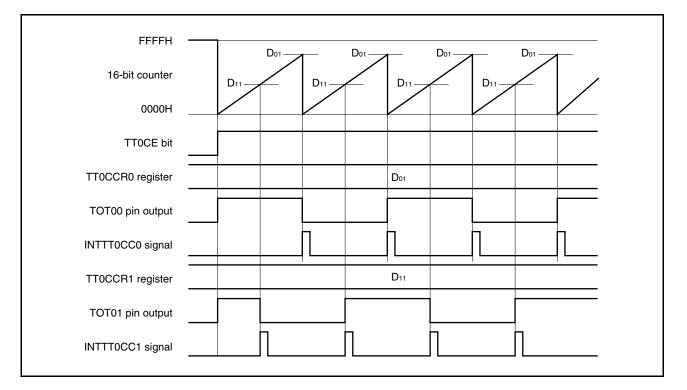

When the TT0CCR1 register is set to the same value as the TT0CCR0 register, the INTTT0CC0 signal is generated at the same timing as the INTTT0CC1 signal and the TOT01 pin output is inverted. In other words, a square wave can be output from the TOT01 pin.

The following shows the operation when the TT0CCR1 register is set to other than the value set in the TT0CCR0 register.

If the set value of the TT0CCR1 register is less than the set value of the TT0CCR0 register, the INTTT0CC1 signal is generated once per cycle. At the same time, the output of the TOT01 pin is inverted.

The TOT01 pin outputs a square wave after outputting a short-width pulse.

#### Figure 9-12. Timing Chart When Do1 ≥ D11

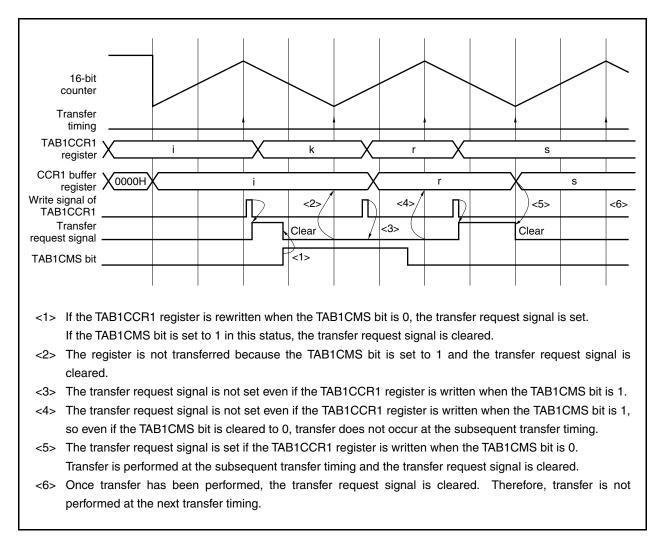

## (4) Rewriting TAB1OPT0.TAB1CMS bit

The TAB1CMS bit can select the anytime rewrite mode and batch rewrite mode. This bit can be rewritten during timer operation (when TAB1CTL0.TAB1CE bit = 1). However, the operation and caution illustrated in Figure 11-36 are necessary.

If the TAB1CCR1 register is written when the TAB1CMS bit is cleared to 0, a transfer request signal (internal signal) is set.

When the transfer request signal is set, the register is transferred at the next transfer timing, and the transfer request signal is cleared. This transfer request signal is also cleared when the TAB1CMS bit is set to 1.

#### Figure 11-36. Rewriting TAB1CMS Bit

## 18.4 Registers

The following registers are used to control CSIFn.

- CSIFn control register 0 (CFnCTL0)

- CSIFn control register 1 (CFnCTL1)

- CSIFn control register 2 (CFnCTL2)

- CSIFn status register (CFnSTR)

- (1) CSIFn control register 0 (CFnCTL0)

CFnCTL0 is a register that controls the CSIFn serial transfer operation. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 01H.

|              |                        |                                                                                                                                                                                                     | (1/3) |

|--------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| After res    | et: 01H                | R/W Address: CF0CTL0 FFFFFD00H, CF1CTL0 FFFFFD10H,<br>CF2CTL0 FFFFFD20H, CF3CTL0 FFFFFD30H,<br>CF4CTL0 FFFFFD40H                                                                                    |       |

|              | <7>                    | <6> <5> <4> 3 2 1 <0>                                                                                                                                                                               |       |

| CFnCTL0      |                        | CFnTXE <sup>Note</sup> CFnDIR <sup>Note</sup> 0 0 CFnTMS <sup>Note</sup> CFnSCE                                                                                                                     |       |

| (n = 0 to 4) |                        |                                                                                                                                                                                                     |       |

|              | CFnPWR                 | Specification of CSIFn operation disable/enable                                                                                                                                                     |       |

|              | 0                      | Disables CSIFn operation and resets the CFnSTR register                                                                                                                                             |       |

|              | 1                      | Enables CSIFn operation                                                                                                                                                                             |       |

|              | • The CFr              | nPWR bit controls the CSIFn operation and resets the internal circuit.                                                                                                                              |       |

|              |                        |                                                                                                                                                                                                     |       |

|              | CFnTXE <sup>Note</sup> | Specification of transmit operation disable/enable                                                                                                                                                  |       |

|              | 0                      | Disables transmit operation                                                                                                                                                                         |       |

|              | 1                      | Enables transmit operation                                                                                                                                                                          |       |

|              | The SO                 | Fn output is low level when the CFnTXE bit is 0.                                                                                                                                                    |       |

|              |                        |                                                                                                                                                                                                     |       |

|              | CFnRXE <sup>Note</sup> | Specification of receive operation disable/enable                                                                                                                                                   |       |

|              | 0                      | Disables receive operation                                                                                                                                                                          |       |

|              | 1                      | Enables receive operation                                                                                                                                                                           |       |

|              | transferr              | ption completion interrupt is output even when the prescribed data is red, and the receive data (CFnRX register) is not updated, because the operation is disabled by clearing the CFnRXE bit to 0. |       |

|              | Ho                     | ese bits can only be rewritten when the CFnPWR bit = 0.<br>wever, CFnPWR bit = 1 can also be set at the same time as<br>writing these bits.                                                         |       |

|              | Caution                | To forcibly suspend transmission/reception, clear the CFnPWR<br>bit to 0 instead of the CFnRXE and CFnTXE bits.<br>At this time, the clock output is stopped.                                       |       |

(4/4)

| Bit position | Bit name | Function                                                                                    |

|--------------|----------|---------------------------------------------------------------------------------------------|

| 0            | BKI1NK   | This bit controls NAK to Endpoint1 (bulk 1 transfer (IN)).                                  |

|              |          | 1: Do not transmit NAK.                                                                     |

|              |          | 0: Transmit NAK (default value).                                                            |

|              |          | This bit is cleared to 0 only when the FIFO connected to the SIE side of the UF0BI1         |

|              |          | register (64-byte FIFO of bank configuration) cannot receive data. It is set to 1 when a    |

|              |          | toggle operation is performed (the data of the UF0BI1 register is retained until            |

|              |          | transmission has been correctly completed). The bank is changed (toggle operation)          |

|              |          | when the following conditions are satisfied.                                                |

|              |          | Data is correctly written to the FIFO connected to the CPU bus side (writing has            |

|              |          | been completed and the FIFO is full or the UF0DEND register is set).                        |

|              |          | <ul> <li>The value of the FIFO counter connected to the SIE side is 0.</li> </ul>           |

|              |          | This bit is automatically set to 1 and data transmission is started when the FIFO on the    |

|              |          | CPU side becomes full and a FIFO toggle operation is performed as a result of writing       |

|              |          | data to the FIFO. However, if the FIFO on the CPU side becomes full as a result of writing  |

|              |          | data to it by DMA while the BKI1T bit of the UF0DEND register is cleared to 0, the toggle   |

|              |          | operation is not performed because the condition of the toggle operation is not satisfied   |

|              |          | until the BKI1DED bit of the UF0DEND register is set to 1. To send a short packet that      |

|              |          | does not make the FIFO on the CPU side full, set the BKI1DED bit to 1 after completing      |

|              |          | writing data. When the BKI1DED bit is set to 1, a toggle operation is performed and at the  |

|              |          | same time, this bit is automatically set to 1. This bit is also cleared to 0 as soon as the |

|              |          | UF0BI1 register has been cleared.                                                           |

Cautions 1. If DMA is enabled while data is being written to the UF0BI1 register in the PIO mode, a DMA request is immediately issued.

- 2. If 64-byte data is written in the DMA transfer mode, the DMA request signal becomes inactive. If the BKI1NK bit is then set to 1, data is transmitted in synchronization with an IN token. The DMA request signal becomes active again as long as the DMA request is not masked as soon as the FIFO is toggled. If the BKI1NK bit is not set, data is not transmitted even if an IN token has been received. In this case, set the BKI1DED bit of the UF0DEND register to 1.

- 3. If the TC signal is received in the DMA transfer mode, the DMA request signal becomes inactive. At the same time, the DMA request is masked. If the BKI1NK bit is not set to 1, data is not transmitted even if an IN token is received. When the BKI1DED bit of the UF0DEND register is set to 1 by FW, data is transmitted in synchronization with the IN token. To execute DMA transfer again, unmask the DMA request.

## 21.8 Register Values in Specific Status

| Register Name    | After CPU Reset (RESET) | After Bus Reset                                          |

|------------------|-------------------------|----------------------------------------------------------|

| UF0E0N register  | 00H                     | Value is held.                                           |

| UF0E0NA register | 00H                     | Value is held.                                           |

| UF0EN register   | 00H                     | Value is held.                                           |

| UF0ENM register  | 00H                     | Value is held.                                           |

| UF0SDS register  | 00H                     | Value is held.                                           |

| UF0CLR register  | 00H                     | Value is held.                                           |

| UF0SET register  | 00H                     | Value is held.                                           |

| UF0EPS0 register | 00H                     | Value is held.                                           |

| UF0EPS1 register | 00H                     | Value is held.                                           |

| UF0EPS2 register | 00H                     | Value is held.                                           |

| UF0IS0 register  | 00H                     | Value is held.                                           |

| UF0IS1 register  | 00H                     | Value is held.                                           |

| UF0IS2 register  | 00H                     | Value is held.                                           |

| UF0IS3 register  | 00H                     | Value is held.                                           |

| UF0IS4 register  | 00H                     | Value is held.                                           |

| UF0IM0 register  | 00H                     | Value is held.                                           |

| UF0IM1 register  | 00H                     | Value is held.                                           |

| UF0IM2 register  | 00H                     | Value is held.                                           |

| UF0IM3 register  | 00H                     | Value is held.                                           |

| UF0IM4 register  | 00H                     | Value is held.                                           |

| UF0IC0 register  | FFH                     | Value is held.                                           |

| UF0IC1 register  | FFH                     | Value is held.                                           |

| UF0IC2 register  | FFH                     | Value is held.                                           |

| UF0IC3 register  | FFH                     | Value is held.                                           |

| UF0IC4 register  | FFH                     | Value is held.                                           |

| UF0IDR register  | 00H                     | Value is held.                                           |

| UF0DMS0 register | 00H                     | Value is held.                                           |

| UF0DMS1 register | 00H                     | Value is held.                                           |

| UF0FIC0 register | 00H                     | Value is held.                                           |

| UF0FIC1 register | 00H                     | Value is held.                                           |

| UF0DEND register | 00H                     | Value is held.                                           |

| UF0GPR register  | 00H                     | Value is held.                                           |

| UF0MODC register | 00H                     | Value is held.                                           |

| UF0MODS register | 00H                     | Bit 2 (CONF): Cleared (0),<br>Other bits: Value is held. |

| UF0AIFN register | 00H                     | Value is held.                                           |

| UF0AAS register  | 00H                     | Value is held.                                           |

| UF0ASS register  | 00H                     | 00H                                                      |

| UF0E1IM register | 00H<br>00H              | Value is held.                                           |

|                  |                         |                                                          |

| UF0E2IM register | 00H                     | Value is held.                                           |

## Table 21-8. Register Values in Specific Status (1/2)

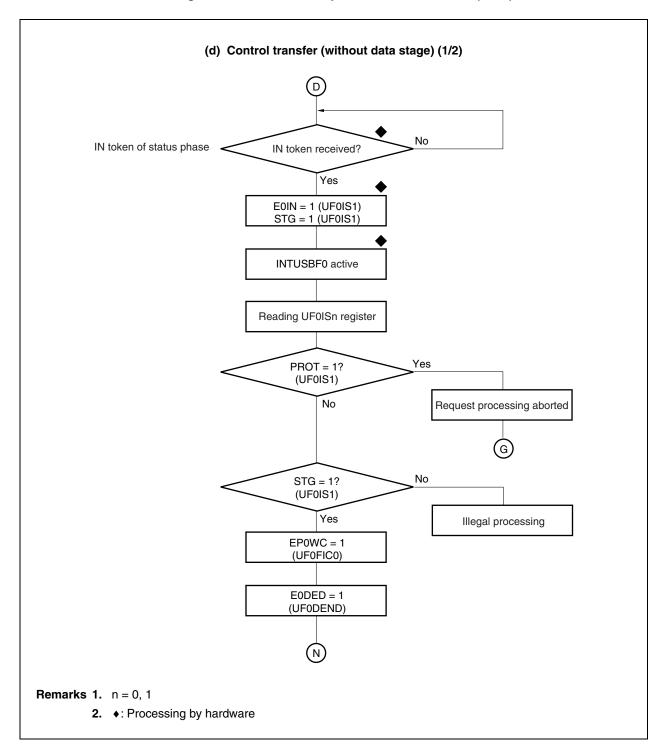

## Figure 21-24. CPUDEC Request for Control Transfer (11/12)

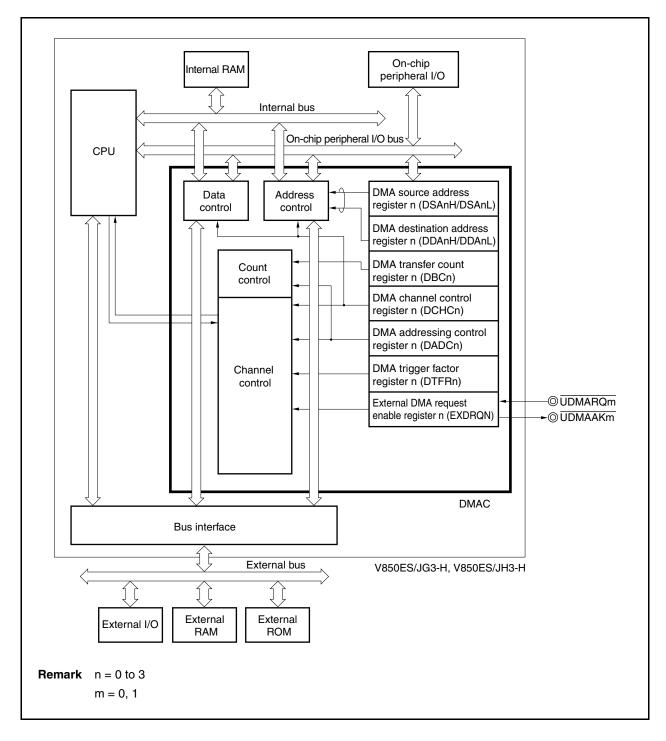

## 22.2 Configuration

## (2) DMA destination address registers 0 to 3 (DDA0 to DDA3)

The DDA0 to DDA3 registers set the DMA destination address (26 bits each) for DMA channel n (n = 0 to 3). These registers are divided into two 16-bit registers, DDAnH and DDAnL. These registers can be read or written in 16-bit units.

| After re:                                                                                                                                                   | set: Undefined R/W                                                                                                                                                            | Address: DDA0H FFFF086H, DDA1H FFFF08EH,<br>DA2H FFFF096H, DDA3H FFFFF09EH,<br>DDA0L FFFF084H, DDA1L FFFFF08CH,<br>DDA2L FFFFF094H, DDA3L FFFFF09CH                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDAnH<br>(n = 0 to 3)<br>DDAnL<br>(n = 0 to 3)                                                                                                              | IR 0 0 0                                                                                                                                                                      | 11       10       9       8       7       6       5       4       3       2       1       0         0       0       DA25       DA24       DA23       DA22       DA21       DA20       DA19       DA18       DA17       DA16         11       10       9       8       7       6       5       4       3       2       1       0         A11       DA10       DA9       DA8       DA7       DA6       DA5       DA4       DA3       DA2       DA1       DA0                                                                 |

|                                                                                                                                                             | IR<br>0 External me<br>1 Internal RAN                                                                                                                                         | Specification of DMA transfer destination<br>emory or on-chip peripheral I/O<br>M                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                             | (default valu<br>During DMA                                                                                                                                                   | ess (A25 to A16) of DMA transfer destination<br>ue is undefined).<br>A transfer, the next DMA transfer destination address is held.<br>transfer is completed, the DMA transfer source address set                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                             | (default valu<br>During DMA                                                                                                                                                   | ess (A15 to A0) of DMA transfer destination<br>ue is undefined).<br>A transfer, the next DMA transfer destination address is held.<br>transfer is completed, the DMA transfer source address set                                                                                                                                                                                                                                                                                                                           |

| <ol> <li>Set the (DCHCn</li> <li>Perio</li> <li>Perio</li> <li>Perio</li> <li>DMA</li> <li>When the read. It caution</li> <li>Following starting</li> </ol> | DDAnH and DDAnL r<br>.Enn bit = 0).<br>d from after reset to<br>d from after channel<br>d from after comple<br>transfer<br>ne value of the DDAr<br>f reading and updat<br>s). | o of the DDAnH register to 0.<br>registers at the following timing when DMA transfer is disabled<br>start of first DMA transfer<br>initialization by DCHCn.INITn bit to start of DMA transfer<br>stion of DMA transfer (DCHCn.TCn bit = 1) to start of the next<br>in register is read, two 16-bit registers, DDAnH and DDAnL, are<br>ting conflict, a value being updated may be read (see 22.13<br>SAnH, DSAnL, DDAnH, DDAnL, and DBCn registers before<br>ese registers are not set, the operation when DMA transfer is |

### (3) Oscillation stabilization time select register (OSTS)

The wait time until the oscillation stabilizes after the STOP mode is released or the wait time until the on-chip flash memory stabilizes after the IDLE2 mode is released is controlled by the OSTS register. This register can be read or written in 8-bit units.

Reset sets this register to 06H.

|      | 7                                                             | 6                                                                                                    | 5                                                                                                                   | 4                                                                                                             | 3                                                                                    | 2                                                    | 1                             | 0                                      |

|------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|----------------------------------------|

| OSTS | 0                                                             | 0                                                                                                    | 0                                                                                                                   | 0                                                                                                             | 0                                                                                    | OSTS2                                                | OSTS1                         | OSTS0                                  |

|      |                                                               |                                                                                                      |                                                                                                                     |                                                                                                               |                                                                                      |                                                      |                               |                                        |

|      | OSTS2                                                         | OSTS1                                                                                                | OSTS0                                                                                                               | Selection                                                                                                     | of oscillati                                                                         | on stabilizati                                       | on time/s                     | etup time <sup>№</sup>                 |

|      |                                                               |                                                                                                      |                                                                                                                     |                                                                                                               |                                                                                      |                                                      | fx                            |                                        |

|      |                                                               |                                                                                                      |                                                                                                                     |                                                                                                               |                                                                                      | 3 M                                                  | Hz                            | 6 MHz                                  |

|      | 0                                                             | 0                                                                                                    | 0                                                                                                                   | 2 <sup>10</sup> /fx                                                                                           |                                                                                      | 0.341                                                |                               | 0.171 ms                               |

|      | 0                                                             | 0                                                                                                    | 1                                                                                                                   | 2 <sup>11</sup> /fx                                                                                           |                                                                                      | 0.683                                                | 3 ms                          | 0.341 ms                               |

|      | 0                                                             | 1                                                                                                    | 0                                                                                                                   | 2 <sup>12</sup> /fx                                                                                           |                                                                                      | 1.365                                                | 5 ms                          | 0.683 ms                               |

|      | 0                                                             | 1                                                                                                    | 1                                                                                                                   | 2 <sup>13</sup> /fx                                                                                           |                                                                                      | 2.730                                                | ) ms                          | 1.365 ms                               |

|      | 1                                                             | 0                                                                                                    | 0                                                                                                                   | 2 <sup>14</sup> /fx                                                                                           |                                                                                      | 5.461                                                | 1 ms                          | 2.731 ms                               |

|      | 1                                                             | 0                                                                                                    | 1                                                                                                                   | 2 <sup>15</sup> /fx                                                                                           |                                                                                      | 10.92                                                | 3 ms                          | 5.461 ms                               |

|      | 1                                                             | 1                                                                                                    | 0                                                                                                                   | 2 <sup>16</sup> /fx                                                                                           |                                                                                      | 21.85                                                | 5 ms                          | 10.92 ms                               |

|      |                                                               |                                                                                                      |                                                                                                                     |                                                                                                               |                                                                                      |                                                      |                               |                                        |

|      | The oscilla<br>DLE2 mod                                       |                                                                                                      |                                                                                                                     |                                                                                                               | etup time                                                                            | e are requi                                          | ired whe                      | en the ST                              |

| I    | DLE2 moo<br>ns 1. The<br>unt<br>the                           | le are rele<br>wait tim<br>il the clo<br>STOP me                                                     | eased, res<br>ne followi<br>ck oscilla<br>ode, rega                                                                 | pectively.<br>ng releas<br>ation star<br>rdless of<br>interrupt                                               | se of the<br>ts ("a" i<br>whethe                                                     | STOP mo<br>n the figu<br>r the STOF<br>signal.       | ode doe<br>re belov           | es not inc<br>w) followi               |

| I    | DLE2 moo<br>ns 1. The<br>unt<br>the                           | le are rele<br>wait tim<br>il the clo<br>STOP me<br>occurrer                                         | eased, res<br>ne followi<br>ck oscilla<br>ode, rega                                                                 | spectively.<br>ng releas<br>ation star<br>rdless of<br>interrupt<br>STOP m<br>STOP m                          | se of the<br>ts ("a" i<br>whethei<br>request                                         | STOP mo<br>n the figu<br>r the STOF<br>signal.       | ode doe<br>re belov           | es not inc<br>w) followi               |

| I    | DLE2 mod<br>ns 1. The<br>unt<br>the<br>the<br>2. Be           | le are rele<br>wait tim<br>il the clo<br>STOP me<br>occurrer<br>Voltage w                            | eased, res<br>ne followi<br>ck oscilla<br>ode, rega<br>nce of an<br>aveform of<br>Vss -<br>et bits 3 t              | spectively.<br>ng releas<br>ation star<br>rdless of<br>interrupt<br>STOP m<br>X1 pin<br>                      | se of the<br>ts ("a" in<br>whethen<br>request<br>ode releas                          | STOP mo<br>n the figu<br>r the STOF<br>signal.       | ode doe<br>re belov<br>P mode | es not inc<br>w) followi<br>is release |

| I    | DLE2 mod<br>ns 1. The<br>unt<br>the<br>the<br>2. Be<br>3. The | le are rele<br>wait tim<br>il the clo<br>STOP me<br>occurrer<br>Voltage w<br>sure to se<br>oscillati | eased, res<br>ne followi<br>ck oscilla<br>ode, rega<br>nce of an<br>aveform of<br>Vss -<br>et bits 3 t<br>on stabil | ng releas<br>ation star<br>rdless of<br>interrupt<br>STOP m<br>X1 pin<br>X1 pin<br>Co 7 to "0"<br>ization tin | se of the<br>ts ("a" in<br>whethen<br>request<br>ode releas<br>a a<br>,<br>me follow | STOP mo<br>n the figu<br>r the STOF<br>signal.<br>se | ode doe<br>re belov<br>P mode | es not inc<br>w) followi<br>is release |

| I    | DLE2 mod<br>ns 1. The<br>unt<br>the<br>the<br>2. Be<br>3. The | le are rele<br>wait tim<br>il the clo<br>STOP me<br>occurrer<br>Voltage w<br>sure to se<br>oscillati | eased, res<br>ne followi<br>ck oscilla<br>ode, rega<br>nce of an<br>aveform of<br>Vss -<br>et bits 3 t<br>on stabil | spectively.<br>ng releas<br>ation star<br>rdless of<br>interrupt<br>STOP m<br>X1 pin<br>                      | se of the<br>ts ("a" in<br>whethen<br>request<br>ode releas<br>a a<br>,<br>me follow | STOP mo<br>n the figu<br>r the STOF<br>signal.<br>se | ode doe<br>re belov<br>P mode | es not inc<br>w) followi<br>is release |

| <ul> <li>voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>utions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as positive after external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OCDM       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    | set: 01H <sup>Note</sup>                                                                                                                                                                                                                         | R/W                                                                        | Address                                      | s: FFFFF9                                     | FCH                                         |                                    |                       |              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|---------------------------------------------|------------------------------------|-----------------------|--------------|

| OCDM       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <th0< th=""></th0<>                                                                                                                                                                                   | OCDM       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <th0< th=""> <th0< th=""></th0<></th0<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    | 7                                                                                                                                                                                                                                                | 6                                                                          | 5                                            | 4                                             | 3                                           | 2                                  | 1                     | <0>          |

| 0       Selects normal operation mode (in which a pin that functions alternately as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.         1       When DRST pin is low:<br>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin)<br>When DRST pin is high:<br>On-chip debug mode (in which a pin that functions alternately as an on-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)         te       RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM), voltage detector (LVI), however, the value of the OCDM register is retained.         utions 1.       When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as portafter external reset, any of the following actions must be taken.         •       Input a low level to the P56/INTP05/DRST pin.         •       Set the OCDM0 bit. In this case, take the following actions. | 0         Selects normal operation mode (in which a pin that functions alternately<br>as on-chip debug function pin is used as a port/peripheral function pin) and<br>disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.           1         When DRST pin is low:<br>Normal operation mode (in which a pin that functions alternately as an<br>on-chip debug function pin is used as a port/peripheral function pin)<br>When DRST pin is high:<br>On-chip debug mode (in which a pin that functions alternately as an<br>on-chip debug function pin is used as an on-chip debug mode pin)           ote         RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM),<br>voltage detector (LVI), however, the value of the OCDM register is retained.           autions 1.         When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as portarter external reset, any of the following actions must be taken.           •         Input a low level to the P56/INTP05/DRST pin.           •         Set the OCDM0 bit. In this case, take the following actions.           <1>Clear the OCDM0 bit to 0.           <2> Fix the P56/INTP05/DRST pin to low level until <1> is completed.           2.         The DRST pin has an on-chip pull-down resistor. This resistor is disconnected with the oten is the public p | OCDM                                               | 0                                                                                                                                                                                                                                                | 0                                                                          |                                              |                                               |                                             |                                    |                       | OCDM0        |

| 0       Selects normal operation mode (in which a pin that functions alternately as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.         1       When DRST pin is low:<br>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin)<br>When DRST pin is high:<br>On-chip debug mode (in which a pin that functions alternately as an on-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)         te       RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.         utions 1.       When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as prafter external reset, any of the following actions must be taken.         •       Input a low level to the P56/INTP05/DRST pin.         •       Set the OCDM0 bit. In this case, take the following actions.    | 0       Selects normal operation mode (in which a pin that functions alternately as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.         1       When DRST pin is low:<br>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin) When DRST pin is high:<br>On-chip debug function pin is used as a port/peripheral function pin)         vhen DRST pin is high:<br>On-chip debug function pin is used as an on-chip debug mode pin)         ote         RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.         autions 1.       When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as per after external reset, any of the following actions must be taken.         •       Input a low level to the P56/INTP05/DRST pin.         •       Set the OCDM0 bit. In this case, take the following actions.         <1> Clear the OCDM0 bit to 0.         <2> Fix the P56/INTP05/DRST pin to low level until <1> is completed.         2.       The DRST pin has an on-chip pull-down resistor. This resistor is disconnected with the oten pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |                                                                                                                                                                                                                                                  |                                                                            |                                              |                                               |                                             |                                    |                       |              |

| <ul> <li>as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.</li> <li>1 When DRST pin is low:<br/>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin) When DRST pin is high:<br/>On-chip debug function pin is used as an on-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)</li> <li>te RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>utions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as pr after external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> </ul>            | <ul> <li>as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P56/INTP05/DRST pin.</li> <li>1 When DRST pin is low:<br/>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin) When DRST pin is high:<br/>On-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)</li> <li>te RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>utions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as prafter external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> <li>&lt;1&gt; Clear the OCDM0 bit to 0.</li> <li>&lt;2&gt; Fix the P56/INTP05/DRST pin to low level until &lt;1&gt; is completed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    | OCDM0                                                                                                                                                                                                                                            |                                                                            |                                              | C                                             | peration mo                                 | ode                                |                       |              |

| <ul> <li>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin) When DRST pin is high:</li> <li>On-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)</li> <li>te RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>utions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as p after external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>Normal operation mode (in which a pin that functions alternately as an on-chip debug function pin is used as a port/peripheral function pin) When DRST pin is high:</li> <li>On-chip debug mode (in which a pin that functions alternately as an on-chip debug function pin is used as an on-chip debug mode pin)</li> <li>Dete RESET input sets this register to 01H. After reset by the WDT2RES signal, clock monitor (CLM) voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>Buttions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as prafter external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> <li>&lt;1&gt; Clear the OCDM0 bit to 0.</li> <li>&lt;2&gt; Fix the P56/INTP05/DRST pin to low level until &lt;1&gt; is completed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    | 0                                                                                                                                                                                                                                                | as on-chip                                                                 | debug fui                                    | nction pin i                                  | s used as a                                 | port/perip                         | heral funct           | ion pin) and |

| <ul> <li>voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>utions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as particle after external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>voltage detector (LVI), however, the value of the OCDM register is retained.</li> <li>autions 1. When using the DDI, DDO, DCK, and DMS pins not as on-chip debug pins but as particle after external reset, any of the following actions must be taken.</li> <li>Input a low level to the P56/INTP05/DRST pin.</li> <li>Set the OCDM0 bit. In this case, take the following actions.</li> <li>&lt;1&gt; Clear the OCDM0 bit to 0.</li> <li>&lt;2&gt; Fix the P56/INTP05/DRST pin to low level until &lt;1&gt; is completed.</li> </ul> 2. The DRST pin has an on-chip pull-down resistor. This resistor is disconnected w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    | Normal operation mode (in which a pin that functions alternately as an<br>on-chip debug function pin is used as a port/peripheral function pin)<br>When DRST pin is high:<br>On-chip debug mode (in which a pin that functions alternately as an |                                                                            |                                              |                                               |                                             |                                    |                       |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <2> Fix the P56/INTP05/ $\overline{\text{DRST}}$ pin to low level until <1> is completed.<br>2. The $\overline{\text{DRST}}$ pin has an on-chip pull-down resistor. This resistor is disconnected whet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | after ext                                          | ternal rese                                                                                                                                                                                                                                      | et, any of                                                                 |                                              |                                               |                                             |                                    |                       |              |