# E. Renesas Electronics America Inc - UPD70F3771GF-GAT-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                             |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CANbus, CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 96                                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                |                                                                                      |

| RAM Size                   | 40K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 128-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3771gf-gat-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

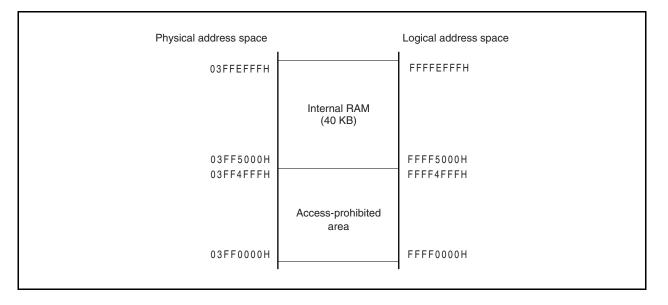

## (b) Internal RAM (40 KB)

40 KB are allocated to addresses 03FF5000H to 03FFEFFFH in the following products. Accessing addresses 03FF0000H to 03FF4FFFH is prohibited.

• μPD70F3761, 70F3766

## Figure 3-8. Internal RAM Area (40 KB)

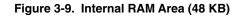

## (c) Internal RAM (48 KB)

48 KB are allocated to addresses 03FF3000H to 03FFEFFFH in the following products. Accessing addresses 03FF0000H to 03FF2FFFH is prohibited.

• μPD70F3762, 70F3767

| Address   | Function Register Name           | Symbol   | R/W | Manip        | oulatab      | Default Value |       |

|-----------|----------------------------------|----------|-----|--------------|--------------|---------------|-------|

|           |                                  |          |     | 1            | 8            | 16            |       |

| FFFFFA24H | UARTC2 status register           | UC2STR   | R/W | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFA26H | UARTC2 receive data register     | UC2RX    | R   |              |              |               | 01FFH |

| FFFFFA26H | UARTC2 receive data register L   | UC2RXL   |     |              | $\checkmark$ |               | FFH   |

| FFFFFA28H | UARTC2 transmit data register    | UC2TX    | R/W |              |              | $\checkmark$  | 01FFH |

| FFFFFA28H | UARTC2 transmit data register L  | UC2TXL   |     |              | $\checkmark$ |               | FFH   |

| FFFFFA2AH | UARTC2 option control register 1 | UC2OPT1  |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFA30H | UARTC3 control register 0        | UC3CTL0  |     | $\checkmark$ | $\checkmark$ |               | 10H   |

| FFFFFA31H | UARTC3 control register 1        | UC3CTL1  |     |              | $\checkmark$ |               | 00H   |

| FFFFFA32H | UARTC3 control register 2        | UC3CTL2  |     |              |              |               | FFH   |

| FFFFFA33H | UARTC3 option control register 0 | UC3OPT0  |     | $\checkmark$ |              |               | 14H   |

| FFFFFA34H | UARTC3 status register           | UC3STR   |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFA36H | UARTC3 receive data register     | UC3RX    | R   |              |              |               | 01FFH |

| FFFFFA36H | UARTC3 receive data register L   | UC3RXL   |     |              | $\checkmark$ |               | FFH   |

| FFFFFA38H | UARTC3 transmit data register    | UC3TX    | R/W |              |              | $\checkmark$  | 01FFH |

| FFFFFA38H | UARTC3 transmit data register L  | UC3TXL   |     |              | $\checkmark$ |               | FFH   |

| FFFFFA3AH | UARTC3 option control register 1 | UC3OPT1  |     |              |              |               | 00H   |

| FFFFFA40H | UARTC4 control register 0        | UC4CTL0  |     |              |              |               | 10H   |

| FFFFFA41H | UARTC4 control register 1        | UC4CTL1  |     |              | $\checkmark$ |               | 00H   |

| FFFFFA42H | UARTC4 control register 2        | UC4CTL2  |     |              | $\checkmark$ |               | FFH   |

| FFFFFA43H | UARTC4 option control register 0 | UC4OPT0  |     | $\checkmark$ | $\checkmark$ |               | 14H   |

| FFFFFA44H | UARTC4 status register           | UC4STR   |     | $\checkmark$ |              |               | 00H   |

| FFFFFA46H | UARTC4 receive data register     | UC4RX    | R   |              |              |               | 01FFH |

| FFFFFA46H | UARTC4 receive data register L   | UC4RXL   |     |              |              |               | FFH   |

| FFFFFA48H | UARTC4 transmit data register    | UC4TX    | R/W |              |              |               | 01FFH |

| FFFFFA48H | UARTC4 transmit data register L  | UC4TXL   |     |              | $\checkmark$ |               | FFH   |

| FFFFFA4AH | UARTC4 option control register 1 | UC4OPT1  |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFA80H | TMM0 control register 0          | TM0CTL0  |     | $\checkmark$ |              |               | 00H   |

| FFFFFA84H | TMM0 compare register 0          | TM0CMP0  |     |              |              | $\checkmark$  | 0000H |

| FFFFFA90H | TMM1 control register 0          | TM1CTL0  |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFA94H | TMM1 compare register 0          | TM1CMP0  |     |              |              | $\checkmark$  | 0000H |

| FFFFFAA0H | TMM2 control register 0          | TM2CTL0  |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFAA4H | TMM2 compare register 0          | TM2CMP0  |     |              |              | $\checkmark$  | 0000H |

| FFFFFAB0H | TMM3 control register 0          | TM3CTL0  |     | $\checkmark$ | $\checkmark$ |               | 00H   |

| FFFFFAB4H | TMM3 compare register 0          | TM3CMP0  |     |              |              |               | 0000H |

| FFFFFAD0H | Sub-count register               | RC1SUBC  | R   | İ            |              | $\checkmark$  | 0000H |

| FFFFFAD2H | Second count register            | RC1SEC   | R/W | İ            | $\checkmark$ |               | 00H   |

| FFFFFAD3H | Minute count register            | RC1MIN   | 1   |              | $\checkmark$ |               | 00H   |

| FFFFFAD4H | Hour count register              | RC1HOUR  | 1   |              | $\checkmark$ |               | 12H   |

| FFFFFAD5H | Week count register              | RC1WEEK  | 1   |              |              |               | 00H   |

| FFFFFAD6H | Day count register               | RC1DAY   | 1   |              |              |               | 01H   |

| FFFFFAD7H | Month count register             | RC1MONTH | 1   |              |              |               | 01H   |

| FFFFFAD8H | Year count register              | RC1YEAR  | 1   |              |              |               | 00H   |

| FFFFFAD9H | Time error correction register   | RC1SUBU  |     | $\checkmark$ |              |               | 00H   |

| Address   | Function Register Name            | Symbol  | R/W       | Manip        | oulatab      | le Bits      | Default Value |

|-----------|-----------------------------------|---------|-----------|--------------|--------------|--------------|---------------|

|           |                                   |         |           | 1            | 8            | 16           |               |

| FFFFFD14H | CSIF1 receive data register       | CF1RX   | R         |              |              |              | 0000H         |

| FFFFFD14H | CSIF1 receive data register L     | CF1RXL  |           |              | $\checkmark$ |              | 00H           |

| FFFFFD16H | CSIF1 transmit data register      | CF1TX   | R/W       |              |              | $\checkmark$ | 0000H         |

| FFFFFD16H | CSIF1 transmit data register L    | CF1TXL  |           |              | $\checkmark$ |              | 00H           |

| FFFFFD20H | CSIF2 control register 0          | CF2CTL0 |           | $\checkmark$ | $\checkmark$ |              | 01H           |

| FFFFFD21H | CSIF2 control register 1          | CF2CTL1 |           | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFD22H | CSIF2 control register 2          | CF2CTL2 |           |              | $\checkmark$ |              | 00H           |

| FFFFFD23H | CSIF2 status register             | CF2STR  |           | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFD24H | CSIF2 receive data register       | CF2RX   | R         |              |              | $\checkmark$ | 0000H         |

| FFFFFD24H | CSIF2 receive data register L     | CF2RXL  |           |              | $\checkmark$ |              | 00H           |

| FFFFFD26H | CSIF2 transmit data register      | CF2TX   | R/W       |              |              |              | 0000H         |

| FFFFFD26H | CSIF2 transmit data register L    | CF2TXL  |           |              | $\checkmark$ |              | 00H           |

| FFFFFD30H | CSIF3 control register 0          | CF3CTL0 |           |              | $\checkmark$ |              | 01H           |

| FFFFFD31H | CSIF3 control register 1          | CF3CTL1 |           |              |              |              | 00H           |

| FFFFD32H  | CSIF3 control register 2          | CF3CTL2 |           |              |              |              | 00H           |

| FFFFFD33H | CSIF3 status register             | CF3STR  |           |              | V            |              | 00H           |

| FFFFFD34H | CSIF3 receive data register       | CF3RX   | R         |              | ,            | V            | 0000H         |

| FFFFFD34H | CSIF3 receive data register L     | CF3RXL  |           |              |              | ,            | 00H           |

| FFFFFD36H | CSIF3 transmit data register      | CF3TX   | R/W       |              | ,            | V            | 0000H         |

| FFFFD36H  | CSIF3 transmit data register L    | CF3TXL  |           |              |              |              | 00H           |

| FFFFFD40H | CSIF4 control register 0          | CF4CTL0 |           | $\checkmark$ |              |              | 01H           |

| FFFFFD41H | CSIF4 control register 1          | CF4CTL1 |           |              |              |              | 00H           |

| FFFFFD42H | CSIF4 control register 2          | CF4CTL2 |           |              |              |              | 00H           |

| FFFFD43H  | CSIF4 status register             | CF4STR  |           |              |              |              | 00H           |

| FFFFFD44H | CSIF4 receive data register       | CF4RX   | R         |              |              |              | 0000H         |

| FFFFFD44H | CSIF4 receive data register L     | CF4RXL  |           |              | $\checkmark$ |              | 00H           |

| FFFFFD46H | CSIF4 transmit data register      | CF4TX   | R/W       |              |              |              | 0000H         |

| FFFFFD46H | CSIF4 transmit data register L    | CF4TXL  | -         |              | $\checkmark$ |              | 00H           |

| FFFFFD80H | IIC shift register 0              | IIC0    |           |              | $\checkmark$ |              | 00H           |

| FFFFFD82H | IIC control register 0            | IICC0   |           | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFD83H | Slave address register 0          | SVA0    |           |              |              |              | 00H           |

| FFFFD84H  | IIC clock select register 0       | IICCL0  |           | $\checkmark$ |              |              | 00H           |

| FFFFFD85H | IIC function expansion register 0 | IICX0   |           |              |              |              | 00H           |

| FFFFFD86H | IIC status register 0             | IICS0   | R         |              |              |              | 00H           |

| FFFFFD8AH | IIC flag register 0               | IICF0   | R/W       |              |              |              | 00H           |

| FFFFFD90H | IIC shift register 1              | IIC1    |           |              |              |              | 00H           |

| FFFFFD92H | IIC control register 1            | IICC1   |           |              |              |              | 00H           |

| FFFFFD93H | Slave address register 1          | SVA1    | 1         |              |              |              | 00H           |

| FFFFFD94H | IIC clock select register 1       | IICCL1  | 1         | $\checkmark$ | √            | l            | 00H           |

| FFFFFD95H | IIC function expansion register 1 | IICX1   | 1         |              | √            | 1            | 00H           |

| FFFFFD96H | IIC status register 1             | IICS1   | R         | √            | √<br>√       | 1            | 00H           |

| FFFFFD9AH | IIC flag register 1               | IICF1   | R/W       | V            | ,<br>√       |              | 00H           |

|           |                                   |         | · · · · · | <u> </u>     | <u> </u>     |              |               |

## (1) Main clock oscillator

The main clock oscillator oscillates the following frequencies (fx).

- In clock-through mode

- fx = 3.0 to 6.0 MHz

- In PLL mode

- fx = 3.0 to 6.0 MHz (×8)

## (2) Subclock oscillator

The sub-resonator oscillates a frequency of 32.768 kHz (fxr).

## (3) Main clock oscillator stop control

This circuit generates a control signal that stops oscillation of the main clock oscillator. Oscillation of the main clock oscillator is stopped in the STOP mode or when the PCC.MCK bit = 1 (valid only when the PCC.CLS bit = 1).

## (4) Internal oscillator

Oscillates a frequency (fR) of 220 kHz (TYP.).

## (5) Prescaler 1

This prescaler generates the clock (fxx to fxx/1,024) to be supplied to the following on-chip peripheral functions: TAA, TAB, TMM, TMT, CSIF, UARTC,  $I^2$ C, CAN, ADC, DAC, WDT2

## (6) Prescaler 2

This circuit divides the main clock (fxx).

The clock generated by prescaler 2 (fxx to fxx/32) is supplied to the selector that generates the CPU clock (fcpu) and internal system clock (fcLk).

fclk is the clock supplied to the INTC, ROM, and RAM blocks, and can be output from the CLKOUT pin.

## (7) Prescaler 3

This circuit divides the clock generated by the main clock oscillator (fx) to a specific frequency (32.768 kHz) and supplies that clock to the real-time counter (RTC) block.

## (8) PLL

This circuit multiplies the clock generated by the main clock oscillator (fx) by 8. It operates in two modes: clock-through mode in which fx is output as is, and PLL mode in which a multiplied clock is output. These modes can be selected by using the PLLCTL.SELPLL bit.

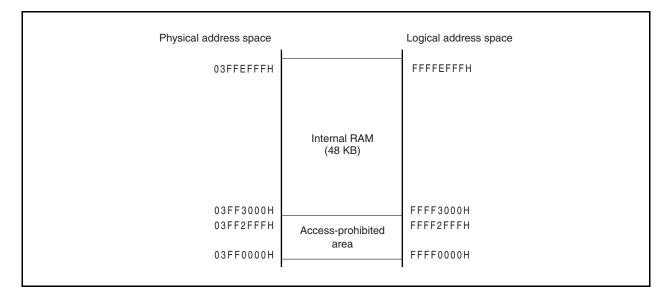

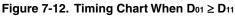

If the set value of the TAAnCCR1 register is less than the set value of the TAAnCCR0 register, the INTTAAnCC1 signal is generated once per cycle. At the same time, the output of the TOAAn1 pin is inverted. The TOAAn1 pin outputs a square wave with the same cycle as that output by the TOAAn0 pin.

Figure 7-31. Setting of Registers in PWM Output Mode (1/2)

In order to transfer data from the TT0CCRn register to the CCRn buffer register, the TT0CCR1 register must be written.

To change both the cycle and active level width of the PWM waveform at this time, first set the cycle to the TT0CCR0 register and then set the active level width to the TT0CCR1 register.

To change only the cycle of the PWM waveform, first set the cycle to the TT0CCR0 register, and then write the same value (same as preset value of the TT0CCR1 register) to the TT0CCR1 register.

To change only the active level width (duty factor) of the PWM waveform, only the TT0CCR1 register has to be set.

After data is written to the TT0CCR1 register, the value written to the TT0CCRn register is transferred to the CCRn buffer register in synchronization with clearing of the 16-bit counter, and is used as the value compared with the 16-bit counter.

To write the TT0CCR0 or TT0CCR1 register again after writing the TT0CCR1 register once, do so after the INTTT0CC0 signal is generated. Otherwise, the value of the CCRn buffer register may become undefined because the timing of transferring data from the TT0CCRn register to the CCRn buffer register conflicts with writing the TT0CCRn register.

**Remark** n = 0, 1

## (9) Day count register (RC1DAY)

The RC1DAY register is an 8-bit register that takes a value of 1 to 31 (decimal) and indicates the count value of days.

It counts up when the hour counter overflows.

This counter counts as follows.

- 01 to 31 (January, March, May, July, August, October, December)

- 01 to 30 (April, June, September, November)

- 01 to 29 (February in leap year)

- 01 to 28 (February in normal year)

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (2 x 32.768 kHz) later. Set a decimal value of 00 to 31 to this register in BCD code.

This register can be read or written in 8-bit units.

Reset sets this register to 01H.

- Caution Setting a value other than 01 to 31 to the RC1DAY register is prohibited. Setting a value outside the above-mentioned count range, such as "February 30" is also prohibited.

- Remark See 12.4.1 Initial settings, 12.4.2 Rewriting each counter during the real-time counter operation, and 12.4.3 Reading each counter during the real-time counter operation when reading or writing the RC1DAY register.

|                 | After reset: | 01H | R/W | Address | FFFFFA | 06H |   |   |   |

|-----------------|--------------|-----|-----|---------|--------|-----|---|---|---|

| 7 6 5 4 3 2 1 0 |              | 7   | 6   | 5       | 4      | 3   | 2 | 1 | 0 |

| RC1DAY 0 0      | C1DAY        | 0   | 0   |         |        |     |   |   |   |

# (2) Operation timing

**Remark** n = 0 to 4

## 19.7.4 Operation without communication

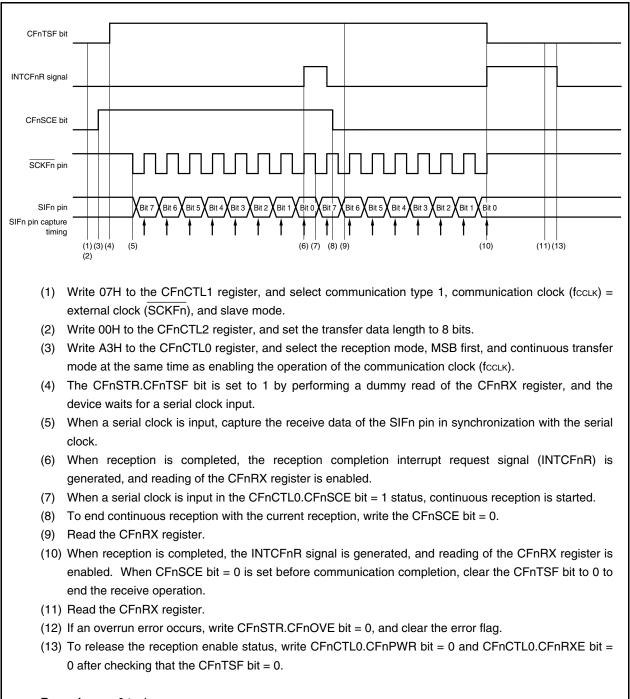

## (1) Start ~ Code ~ Data ~ Data ~ Stop

## 19.7.5 Arbitration loss operation (operation as slave after arbitration loss)

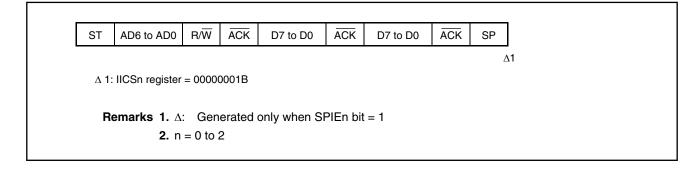

(1) When arbitration loss occurs during transmission of slave address data

| ST                           | AD6 to AD0                                                                                                                       | R/W                                                                           | ĀCK                                                                      | D7 to D0                    | ĀCK       | D7 to D0              | ĀCK       | SP            |             |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------|-----------|-----------------------|-----------|---------------|-------------|

|                              | 1                                                                                                                                |                                                                               |                                                                          | 1                           | ▲2        |                       | ▲3        | Δ4            | 1           |

| <b>▲</b> 1                   | : IICSn register                                                                                                                 | = 01012                                                                       | X110B (                                                                  | Example: Whe                | en IICSn. | ALDn bit is re        | ad during | g interrupt   | t servicing |

| ▲2                           | : IICSn register                                                                                                                 | = 00012                                                                       | X000B                                                                    |                             |           |                       |           |               |             |

| <b>▲</b> 3                   | : IICSn register                                                                                                                 | = 00012                                                                       | X000B                                                                    |                             |           |                       |           |               |             |

| Δ4:                          | IICSn register                                                                                                                   | = 00000                                                                       | 0001B                                                                    |                             |           |                       |           |               |             |

| -                            | omorko 1 🔺                                                                                                                       |                                                                               |                                                                          | aratad                      |           |                       |           |               |             |

| R                            | emarks 1. 🔺                                                                                                                      |                                                                               |                                                                          | only when II                | CCn SP    | IEn hit – 1           |           |               |             |

|                              |                                                                                                                                  | : don'                                                                        |                                                                          |                             | 0011.01   |                       |           |               |             |

|                              |                                                                                                                                  |                                                                               |                                                                          |                             |           |                       |           |               |             |

|                              | <b>2.</b> n                                                                                                                      | = 0 to 2                                                                      | 2                                                                        |                             |           |                       |           |               |             |

|                              | <b>2.</b> n                                                                                                                      | = 0 to 2                                                                      | 2                                                                        |                             |           |                       |           |               |             |

| Wh                           | 2. n<br>en WTIMn bi                                                                                                              |                                                                               | 2                                                                        |                             |           |                       |           |               |             |

|                              | en WTIMn bi                                                                                                                      | t = 1                                                                         |                                                                          | D7 to D0                    | ACK       | D7 to D0              | ĀCK       | SP            |             |

|                              |                                                                                                                                  |                                                                               | ACK                                                                      | D7 to D0                    | ĀĊĸ       | D7 to D0              | ĀCK       | SP            | 1           |

| ST                           | en WTIMn bi                                                                                                                      | t = 1<br>R/W                                                                  | ĀĊĸ                                                                      | 1                           |           | 2                     |           | <b>∆</b> 3 ∆4 |             |

| ST<br>▲1                     | en WTIMn bi                                                                                                                      | <b>t = 1</b><br>R/W                                                           | <u>АСК</u><br>Х110В (                                                    | 1                           |           | 2                     |           | <b>∆</b> 3 ∆4 |             |

| ST<br>▲1<br>▲2               | en WTIMn bi<br>AD6 to AD0<br>: IICSn register                                                                                    | t = 1<br>R/W<br>= 01012<br>= 00012                                            | ACK<br>X110B (<br>X100B                                                  | 1                           |           | 2                     |           | <b>∆</b> 3 ∆4 |             |

| ST<br>▲1<br>▲2<br>▲3         | AD6 to AD0                                                                                                                       | t = 1<br>R/W<br>= 01012<br>= 00012                                            | ACK<br>X110B (<br>X100B<br>XX00B                                         | 1                           |           | 2                     |           | ▲3 ∆4         |             |

| ST<br>▲1<br>▲2<br>▲3         | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register                                            | t = 1<br>R/W<br>= 01012<br>= 00012                                            | ACK<br>X110B (<br>X100B<br>XX00B                                         | 1                           |           | 2                     |           | ▲3 ∆4         |             |

| ST<br>▲1<br>▲2<br>▲3<br>∆ 4: | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register                                            | t = 1<br>$R/\overline{W}$<br>= 01012<br>= 00012<br>= 000012                   | ACK<br>X110B (<br>X100B<br>XX00B<br>XX00B<br>0001B                       | 1<br>Example: Whe           |           | 2                     |           | ▲3 ∆4         |             |

| ST<br>▲1<br>▲2<br>▲3<br>∆ 4: | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register<br>IICSn register<br>emarks 1. ▲           | t = 1<br>R/W<br>= 01012<br>= 00012<br>= 00000<br>A: Alwa<br>: Gen             | ACK<br>X110B (<br>X100B<br>XX00B<br>D001B<br>ays gen<br>erated           | 1<br>Example: Whe           | en ALDn   | .2<br>bit is read dur |           | ▲3 ∆4         |             |

| ST<br>▲1<br>▲2<br>▲3<br>∆ 4: | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register<br>IICSn register<br>emarks 1. ▲<br>∆<br>X | t = 1<br>R/W<br>r = 01012<br>r = 00012<br>r = 00002<br>r = 00002<br>r = 00002 | ACK<br>X110B (<br>X100B<br>XX00B<br>0001B<br>ays gen<br>erated<br>t care | 1<br>Example: Whe<br>erated | en ALDn   | .2<br>bit is read dur |           | ▲3 ∆4         |             |

## 20.1.2 Overview of functions

Table 20-1 presents an overview of the CAN controller functions.

| Function                   | Details                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol                   | CAN protocol ISO 11898 (standard and extended frame transmission/reception)                                                                                                                                                                                                                                                                                                                                                        |

| Baud rate                  | Maximum 1 Mbps (CAN clock input ≥ 8 MHz)                                                                                                                                                                                                                                                                                                                                                                                           |

| Data storage               | Storing messages in the CAN RAM                                                                                                                                                                                                                                                                                                                                                                                                    |

| Number of messages         | <ul> <li>32 message buffers/channels</li> <li>Each message buffer can be set to be either a transmit message buffer or a receive message buffer.</li> </ul>                                                                                                                                                                                                                                                                        |

| Message reception          | <ul> <li>Unique ID can be set to each message buffer.</li> <li>Mask setting of four patterns is possible for each channel.</li> <li>A receive completion interrupt is generated each time a message is received and stored in a message buffer.</li> <li>Two or more receive message buffers can be used as a FIFO receive buffer (multi-buffer receive block function).</li> <li>Receive history list function</li> </ul>         |

| Message transmission       | <ul> <li>Unique ID can be set to each message buffer.</li> <li>Transmit completion interrupt for each message buffer</li> <li>Message buffer numbers 0 to 7 specified as transmit message buffers can be used for<br/>automatic block transfer. Message transmission interval is programmable (automatic<br/>block transmission function (hereafter referred to as "ABT")).</li> <li>Transmission history list function</li> </ul> |

| Remote frame processing    | Remote frame processing by transmit message buffer                                                                                                                                                                                                                                                                                                                                                                                 |

| Time stamp function        | <ul> <li>The time stamp function can be set for a receive message when a 16-bit timer is used in combination.</li> <li>The time stamp capture trigger can be selected (SOF or EOF in a CAN message frame can be detected).</li> </ul>                                                                                                                                                                                              |

| Diagnostic function        | <ul> <li>Readable error counters</li> <li>"Valid protocol operation flag" for verification of bus connections</li> <li>Receive-only mode</li> <li>Single-shot mode</li> <li>CAN protocol error type decoding</li> <li>Self-test mode</li> </ul>                                                                                                                                                                                    |

| Release from bus-off state | <ul> <li>Can be forcibly released from bus-off by software (timing restrictions are ignored).</li> <li>Cannot be automatically released from bus-off (release request by software is required).</li> </ul>                                                                                                                                                                                                                         |

| Power save mode            | <ul><li>CAN sleep mode (can be woken up by CAN bus)</li><li>CAN stop mode (cannot be woken up by CAN bus)</li></ul>                                                                                                                                                                                                                                                                                                                |

| 10 | $\langle \alpha \rangle$ |

|----|--------------------------|

| 12 | 121                      |

| 1  |                          |

|            | 15      | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|

| C0MDATA45m | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 |

|            | 15      | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 | MDATA45 |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |         |         |         |         |         |         |         |         |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| C0MDATA4m  | MDATA4  |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |         |         |         |         |         |         |         |         |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| C0MDATA5m  | MDATA5  |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |         |         |         |         |         |         |         |         |

|            | 15      | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

| C0MDATA67m | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 |

|            | 15      | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 | MDATA67 |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |         |         |         |         |         |         |         |         |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| C0MDATA6m  | MDATA6  |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |         |         |         |         |         |         |         |         |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| C0MDATA7m  | MDATA7  |

|            | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

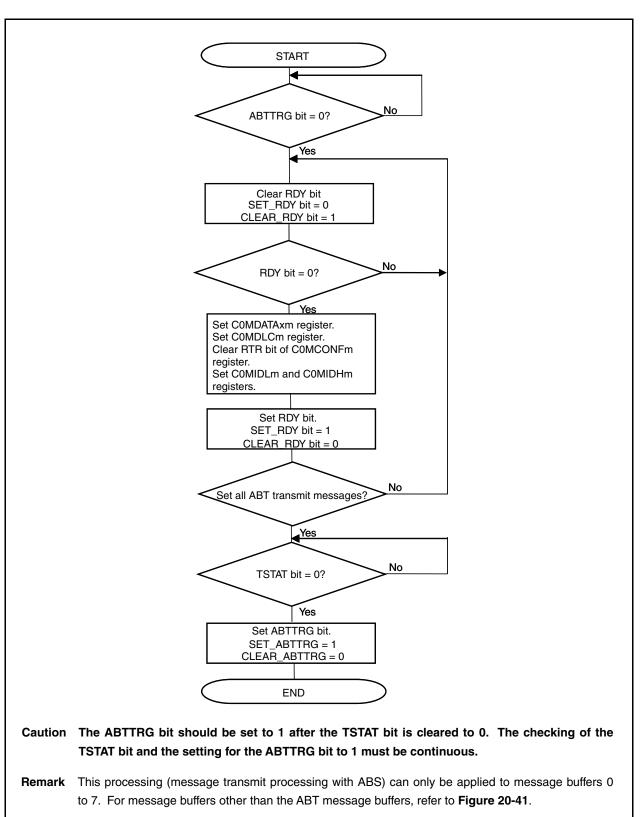

Figure 20-42 shows the processing for a transmit message buffer (COMCONFm.MT2 to COMCONFm.MT0 bits = 000B).

Figure 20-42. ABT Message Transmit Processing

## 21.6.3 EPC control registers

## (1) UF0 EP0NAK register (UF0E0N)

This register controls NAK of Endpoint0 (except an automatically executed request).

This register can be read or written in 8-bit units (however, bit 0 can only be read).

It takes five USB clocks to reflect the status on this register after the UF0FIC0 and UF0FIC1 registers have been set. If it is necessary to read the status correctly, therefore, separate a write signal that accesses the UF0FIC0 and UF0FIC1 registers from a read signal that accesses the UF0EPS0, UF0EPS1, UF0EPS2, UF0E0N, and UF0EN registers by at least four USB clocks.

While NAK is being transmitted to Endpoint0 Read, Endpoint2, and Endpoint4, a write access to the EP0NKR bit is ignored.

|              | 7  | 6                 | 5                                                                                                                      | 4                                                                                                                                                                    | 3                                                                                                                                                        | 2                                                                                                                                                              | 1                                                                                                                        | 0                                                                                                                                                | Address                                                                                                                                                                                    | After reset                                                                                         |  |

|--------------|----|-------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| UF0E0N       | 0  | 0                 | 0                                                                                                                      | 0                                                                                                                                                                    | 0                                                                                                                                                        | 0                                                                                                                                                              | <b>EP0NKR</b>                                                                                                            | <b>EP0NKW</b>                                                                                                                                    | 00200000H                                                                                                                                                                                  | 00H                                                                                                 |  |

|              |    |                   |                                                                                                                        |                                                                                                                                                                      |                                                                                                                                                          |                                                                                                                                                                |                                                                                                                          |                                                                                                                                                  |                                                                                                                                                                                            |                                                                                                     |  |

| Bit position |    | Bit name Function |                                                                                                                        |                                                                                                                                                                      |                                                                                                                                                          |                                                                                                                                                                |                                                                                                                          |                                                                                                                                                  |                                                                                                                                                                                            |                                                                                                     |  |

| 1            | EF | PONKR             | reques<br>data. I<br>read by<br>1: T<br>0: E<br>Set this<br>reason<br>transm                                           | t). It is auto<br>t is also cle<br>v FW (coun<br>ransmit NA<br>to not trans<br>s bit to 1 by<br>even wher                                                            | omatically<br>ared to 0 f<br>ter value =<br>.K.<br>smit NAK (<br>FW when<br>n USBF is<br>until this b                                                    | set to 1 by<br>by hardwar<br>= 0).<br>default valu<br>data shou<br>ready for n<br>it is cleared                                                                | hardware w<br>e when the<br>ue).<br>Id not be rea<br>eceiving dat<br>d to 0 by FW                                        | then Endpoin<br>data of the U<br>ceived from a<br>a. In this ca                                                                                  | n automatically<br>nt0 has correct<br>JF0E0R registe<br>the USB bus fo<br>se, USBF cont<br>also cleared to                                                                                 | lly received<br>er has been<br>or some<br>inues                                                     |  |

| 0            | EF | PONKW             | automa<br>the dat<br>The da<br>necess<br>the hos<br>EODED<br>is full.<br>automa<br>1: C<br>0: T<br>If contr<br>data st | a of Endpo<br>ta of Endpo<br>ta of the U<br>ary to rewr<br>at could not<br>b bit of the<br>As soon as<br>attically set<br>transmit NA<br>ol transfer<br>age, this bi | cuted requ<br>int0 is tran<br>F0E0W reg<br>ite this bit<br>receive da<br>UF0DEND<br>to 1 at the<br>smit NAK.<br>K (default<br>enters the<br>t is cleared | est). This<br>ismitted an<br>gister is re-<br>even in the<br>ata correct<br>register to<br>D bit of the<br>same time<br>value).<br>status stag<br>d to 0 as so | ti is automa<br>d the host c<br>ained until t<br>e case of a n<br>y. To send a<br>1. This bit<br>UF0DEND<br>ge while ACP | atically clear<br>orrectly rece<br>his bit is clea<br>etransmissic<br>a short pack<br>is automatic<br>register is s<br>C cannot be<br>FOEOW regi | rolled (except<br>ed to 0 by hard<br>ives the transr<br>ared. Therefor<br>on request that<br>et, be sure to s<br>ally set to 1 wh<br>et to 1, the EP<br>correctly recei<br>ster is cleared | dware when<br>mitted data.<br>e, it is not<br>is made if<br>set the<br>nen the FIFO<br>PONKW bit is |  |

## (10) UF0 EP status 2 register (UF0EPS2)

This register indicates the USB bus status and the presence or absence of register data.

This register is read-only, in 8-bit units.

The related bits are invalid if each endpoint is not supported by the setting of the UF0EnIM register (n = 1 to 4, 7) and the current setting of the interface.

|              | 7   | 6        | 5                                                                                                                                                                                                                                             | 4                                                                                                                                                                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                   | Address                                                                                                         | After reset                                                                                                                                                                          |

|--------------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UF0EPS2      | 0   | 0        | HALT7                                                                                                                                                                                                                                         | HALT4                                                                                                                                                                                                                                                                                                                 | HALT3                                                                                                                                                                                                                                                                                                 | HALT2                                                                                                                                                                                                                                                                                                                                              | HALT1                                                                                                                                                                                                                                                                                                                              | HALT0                                                                                                                                                                                                                                               | 00200012H                                                                                                       | 00H                                                                                                                                                                                  |

| Bit position | E   | Bit name |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                     |                                                                                                                 |                                                                                                                                                                                      |

| 5 to 0       | HAL | Tn       | conditio<br>satisfied<br>1: Er<br>0: Er<br>The SNI<br>occurrer<br>is receiv<br>also clea<br>bit is no<br>Feature<br>or SET_<br>is receiv<br>0, until t<br>The HAI<br>Endpoir<br>SET_CO<br>Feature<br>request<br>Endpoir<br>same as<br>Endpoir | n, such as<br>h, such as<br>hdpoint is s<br>hdpoint is r<br>DSTL bit is<br>hce of an c<br>red in this s<br>ared to 0.<br>t cleared to<br>is cleared to<br>FEATURE<br>red due to<br>he next SE<br>LTn bit is n<br>t request,<br>DNFIGURA<br>is cleared<br>is correctly<br>t0, is cleared<br>s the current<br>t0 cannot | occurrence<br>ts are auto<br>talled.<br>ot stalled (<br>set to 1 as<br>verrun or r<br>status, the s<br>of Endpoint<br>of Until the<br>by FW. If t<br>Endpoint0<br>the CPUDE<br>TUP token<br>ot cleared<br>Halt Featur<br>TION required<br>by FW. Will<br>processed<br>ed after the<br>othly set value | e of an over<br>matically se<br>default values<br>soon as the<br>eception of<br>SNDSTL bit<br>0 is stalled<br>CLEAR_F<br>he GET_S <sup>2</sup><br>request is<br>EC interrupt<br>is received<br>to 0 until Er<br>re is cleared<br>lest to the in<br>men the SE <sup>2</sup><br>d, the Halt F<br>e request has<br>use, and these<br>if it is set bit | run and re<br>et to 1 by h<br>ne).<br>The HALTO b<br>an undefir<br>t is cleared<br>by the SET<br>EATURE E<br>FATURE E<br>FATURE E<br>FATURE E<br>FATURE E<br>FATURE E<br>TATUS Enc<br>received, of<br>request, the<br>d by the SE<br>therface to<br>$\Gamma_INTERF_A$<br>Feature of a<br>as been pro-<br>se bits are<br>ecause the | ception of a<br>ardware.<br>bit has been<br>hed request.<br>I to 0 and, th<br>r_FEATURE<br>Endpoint0, CLE<br>or if a reque<br>he HALT0 b<br>eceives the<br>ET_INTERF,<br>which the e<br>ACE or SET<br>all the targe<br>occessed, ev<br>also cleared | endpoint is linker<br>CONFIGURA<br>t endpoints, exc<br>ven if the wValue<br>d to 0. Halt Fea<br>ponse is made i | auest, is<br>esult of<br>TUP token<br>ALT0 bit is<br>uest, this<br>ed or Halt<br>Endpoint0,<br>sed by FW<br>d cleared to<br>JRE<br>d, or Halt<br>TION<br>sept<br>e is the<br>ture of |

**Remark** n = 0 to 4, 7, 8

## (2) DMA destination address registers 0 to 3 (DDA0 to DDA3)

The DDA0 to DDA3 registers set the DMA destination address (26 bits each) for DMA channel n (n = 0 to 3). These registers are divided into two 16-bit registers, DDAnH and DDAnL. These registers can be read or written in 16-bit units.

| After re:                                                                                                                                                   | set: Undefined R/W                                                                                                                                                            | Address: DDA0H FFFF086H, DDA1H FFFF08EH,<br>DA2H FFFF096H, DDA3H FFFFF09EH,<br>DDA0L FFFF084H, DDA1L FFFFF08CH,<br>DDA2L FFFFF094H, DDA3L FFFFF09CH                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDAnH<br>(n = 0 to 3)<br>DDAnL<br>(n = 0 to 3)                                                                                                              | IR 0 0 0                                                                                                                                                                      | 11       10       9       8       7       6       5       4       3       2       1       0         0       0       DA25       DA24       DA23       DA22       DA21       DA20       DA19       DA18       DA17       DA16         11       10       9       8       7       6       5       4       3       2       1       0         A11       DA10       DA9       DA8       DA7       DA6       DA5       DA4       DA3       DA2       DA1       DA0                                                                 |

|                                                                                                                                                             | IR<br>0 External me<br>1 Internal RAN                                                                                                                                         | Specification of DMA transfer destination<br>emory or on-chip peripheral I/O<br>M                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                             | (default valu<br>During DMA                                                                                                                                                   | ess (A25 to A16) of DMA transfer destination<br>ue is undefined).<br>A transfer, the next DMA transfer destination address is held.<br>transfer is completed, the DMA transfer source address set                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                             | (default valu<br>During DMA                                                                                                                                                   | ess (A15 to A0) of DMA transfer destination<br>ue is undefined).<br>A transfer, the next DMA transfer destination address is held.<br>transfer is completed, the DMA transfer source address set                                                                                                                                                                                                                                                                                                                           |

| <ol> <li>Set the (DCHCn</li> <li>Perio</li> <li>Perio</li> <li>Perio</li> <li>DMA</li> <li>When the read. It caution</li> <li>Following starting</li> </ol> | DDAnH and DDAnL r<br>.Enn bit = 0).<br>d from after reset to<br>d from after channel<br>d from after comple<br>transfer<br>ne value of the DDAr<br>f reading and updat<br>s). | o of the DDAnH register to 0.<br>registers at the following timing when DMA transfer is disabled<br>start of first DMA transfer<br>initialization by DCHCn.INITn bit to start of DMA transfer<br>stion of DMA transfer (DCHCn.TCn bit = 1) to start of the next<br>in register is read, two 16-bit registers, DDAnH and DDAnL, are<br>ting conflict, a value being updated may be read (see 22.13<br>SAnH, DSAnL, DDAnH, DDAnL, and DBCn registers before<br>ese registers are not set, the operation when DMA transfer is |

## (11) Read values of DSAn and DDAn registers

Values in the middle of updating may be read from the DSAn and DDAn registers during DMA transfer (n = 0 to 3). For example, if the DSAnH register and then the DSAnL register are read when the DMA transfer source address (DSAn register) is 0000FFFFH and the count direction is incremental (DADCn.SAD1 and DADCn.SAD0 bits = 00), the value of the DSAn register differs as follows, depending on whether DMA transfer is executed immediately after the DSAnH register is read.

## (a) If DMA transfer does not occur while DSAn register is read

- <1> Read value of DSAnH register: DSAnH = 0000H

- <2> Read value of DSAnL register: DSAnL = FFFFH

## (b) If DMA transfer occurs while DSAn register is read

- <1> Read value of DSAnH register: DSAnH = 0000H

- <2> Occurrence of DMA transfer

- <3> Incrementing DSAn register: DSAn = 00100000H

- <4> Read value of DSAnL register: DSAnL = 0000H

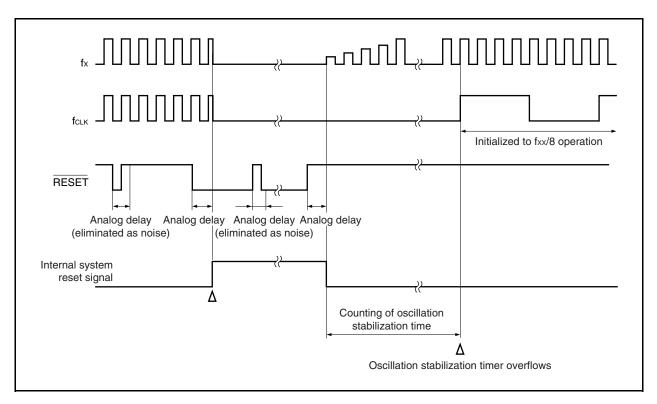

Figure 26-2. Timing of Reset Operation by RESET Pin Input

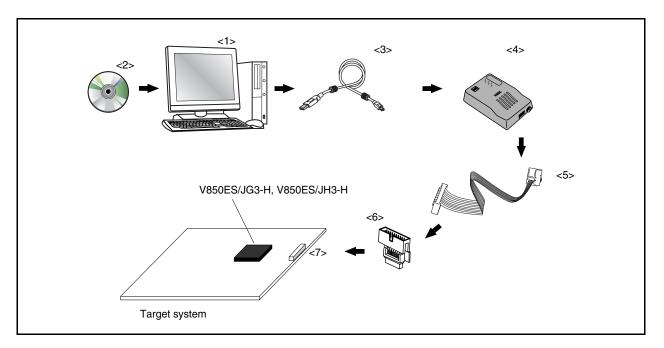

## A.4.2 When using MINICUBE QB-V850MINI

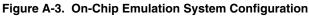

## (1) On-chip emulation using MINICUBE

The system configuration when connecting MINICUBE to the host machine (PC-9821 series, PC/AT compatible) is shown below.

| <1> | Host machine                                          | PC with USB ports                                                                                                                                                                      |

|-----|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <2> | CD-ROM <sup>Note 1</sup>                              | Contents such as integrated debugger ID850QB, N-Wire Checker, device driver, and documents are included in CD-ROM. It is supplied with MINICUBE.                                       |

| <3> | USB interface cable                                   | USB cable to connect the host machine and MINICUBE. It is supplied with MINICUBE. The cable length is approximately 2 m.                                                               |

| <4> | MINICUBE<br>On-chip debug emulator                    | This on-chip debug emulator serves to debug hardware and software when developing application systems using the V850ES/JG3-H or V850ES/JH3-H. It supports integrated debugger ID850QB. |

| <5> | OCD cable                                             | Cable to connect MINICUBE and the target system.<br>It is supplied with MINICUBE. The cable length is approximately 20 cm.                                                             |

| <6> | Connector conversion board<br>KEL adapter             | This conversion board is supplied with MINICUBE.                                                                                                                                       |

| <7> | MINICUBE connector<br>KEL connector <sup>Note 2</sup> | 8830E-026-170S (supplied with MINICUBE)<br>8830E-026-170L (sold separately)                                                                                                            |

Notes 1. Download the device file from the Renesas Electronics website.

http://www2.renesas.com/micro/en/ods/index.html

2. Product of KEL Corporation

**Remark** The numbers in the angular brackets correspond to the numbers in Figure A-3.