#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

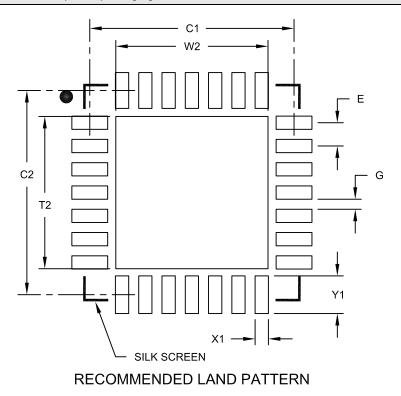

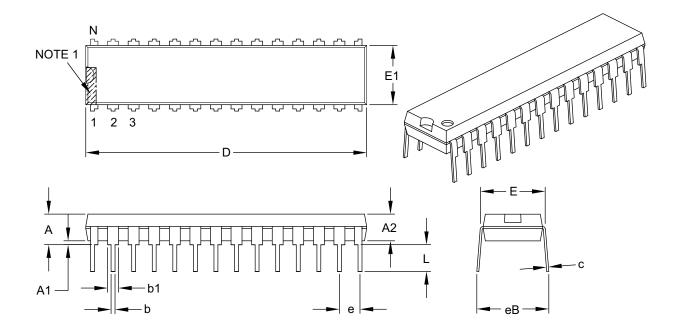

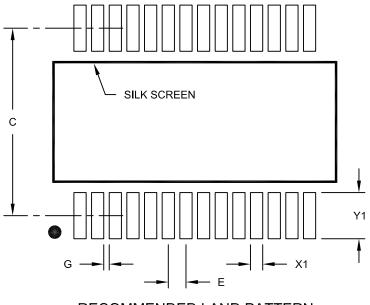

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga102-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | F                             | Pin Number    |                        |     |                 |                              |

|----------|-------------------------------|---------------|------------------------|-----|-----------------|------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | I/O | Input<br>Buffer | Description                  |

| RA0      | 2                             | 27            | 19                     | I/O | ST              | PORTA Digital I/O.           |

| RA1      | 3                             | 28            | 20                     | I/O | ST              |                              |

| RA2      | 9                             | 6             | 30                     | I/O | ST              |                              |

| RA3      | 10                            | 7             | 31                     | I/O | ST              |                              |

| RA4      | 12                            | 9             | 34                     | I/O | ST              |                              |

| RA7      | _                             |               | 13                     | I/O | ST              |                              |

| RA8      | _                             |               | 32                     | I/O | ST              |                              |

| RA9      | _                             |               | 35                     | I/O | ST              |                              |

| RA10     | _                             |               | 12                     | I/O | ST              |                              |

| RB0      | 4                             | 1             | 21                     | I/O | ST              | PORTB Digital I/O.           |

| RB1      | 5                             | 2             | 22                     | I/O | ST              |                              |

| RB2      | 6                             | 3             | 23                     | I/O | ST              |                              |

| RB3      | 7                             | 4             | 24                     | I/O | ST              |                              |

| RB4      | 11                            | 8             | 33                     | I/O | ST              |                              |

| RB5      | 14                            | 11            | 41                     | I/O | ST              |                              |

| RB6      | 15                            | 12            | 42                     | I/O | ST              |                              |

| RB7      | 16                            | 13            | 43                     | I/O | ST              |                              |

| RB8      | 17                            | 14            | 44                     | I/O | ST              |                              |

| RB9      | 18                            | 15            | 1                      | I/O | ST              |                              |

| RB10     | 21                            | 18            | 8                      | I/O | ST              |                              |

| RB11     | 22                            | 19            | 9                      | I/O | ST              |                              |

| RB12     | 23                            | 20            | 10                     | I/O | ST              |                              |

| RB13     | 24                            | 21            | 11                     | I/O | ST              |                              |

| RB14     | 25                            | 22            | 14                     | I/O | ST              |                              |

| RB15     | 26                            | 23            | 15                     | I/O | ST              |                              |

| RC0      | —                             | _             | 25                     | I/O | ST              | PORTC Digital I/O.           |

| RC1      | —                             | _             | 26                     | I/O | ST              |                              |

| RC2      | —                             |               | 27                     | I/O | ST              | ]                            |

| RC3      | _                             | _             | 36                     | I/O | ST              |                              |

| RC4      | _                             | _             | 37                     | I/O | ST              |                              |

| RC5      | —                             |               | 38                     | I/O | ST              | ]                            |

| RC6      | —                             | _             | 2                      | I/O | ST              | ]                            |

| RC7      | _                             | _             | 3                      | I/O | ST              |                              |

| RC8      | —                             |               | 4                      | I/O | ST              | ]                            |

| RC9      | —                             | _             | 5                      | I/O | ST              |                              |

| REFO     | 24                            | 21            | 11                     | 0   | _               | Reference Clock Output.      |

| Legend:  | TTL = TTL inp                 |               |                        |     | ST =            | Schmitt Trigger input buffer |

#### **TABLE 1-2:** PIC24FJ64GA104 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog level input/output

I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

DS39951C-page 16

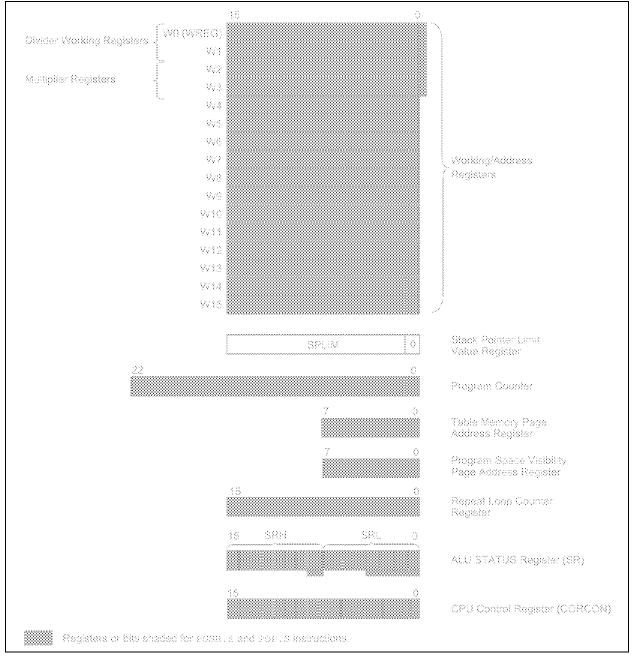

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

| FIGURE 3-2: | <b>PROGRAMMER'S MODEL</b> |

|-------------|---------------------------|

|-------------|---------------------------|

## TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12                 | Bit 11  | Bit 10                 | Bit 9                  | Bit 8                 | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0         | All<br>Resets |

|--------------|------|---------|---------|---------|------------------------|---------|------------------------|------------------------|-----------------------|---------|---------|---------|------------------------|------------------------|------------------------|------------------------|---------------|---------------|

| CNEN1        | 0060 | CN15IE  | CN14IE  | CN13IE  | CN12IE                 | CN11IE  | CN10IE <sup>(1)</sup>  | CN9IE <sup>(1)</sup>   | CN8IE <sup>(1)</sup>  | CN7IE   | CN6IE   | CN5IE   | CN4IE                  | CN3IE                  | CN2IE                  | CN1IE                  | CN0IE         | 0000          |

| CNEN2        | 0062 | _       | CN30IE  | CN29IE  | CN28IE <sup>(1)</sup>  | CN27IE  | CN26IE <sup>(1)</sup>  | CN25IE <sup>(1)</sup>  | CN24IE                | CN23IE  | CN22IE  | CN21IE  | CN20IE <sup>(1)</sup>  | CN19IE <sup>(1)</sup>  | CN18IE <sup>(1)</sup>  | CN17IE <sup>(1)</sup>  | CN16IE        | 0000          |

| CNPU1        | 0068 | CN15PUE | CN14PUE | CN13PUE | CN12PUE                | CN11PUE | CN10PUE <sup>(1)</sup> | CN9PUE <sup>(1)</sup>  | CN8PUE <sup>(1)</sup> | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE                 | <b>CN3PUE</b>          | CN2PUE                 | CN1PUE                 | <b>CN0PUE</b> | 0000          |

| CNPU2        | 006A | -       | CN30PUE | CN29PUE | CN28PUE <sup>(1)</sup> | CN27PUE | CN26PUE <sup>(1)</sup> | CN25PUE <sup>(1)</sup> | CN24PUE               | CN23PUE | CN22PUE | CN21PUE | CN20PUE <sup>(1)</sup> | CN19PUE <sup>(1)</sup> | CN18PUE <sup>(1)</sup> | CN17PUE <sup>(1)</sup> | CN16PUE       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Unimplemented in 28-pin devices; read as '0'.

## EXAMPLE 5-4: LOADING THE WRITE BUFFERS (C LANGUAGE CODE)

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

unsigned int offset;

unsigned int i;

unsigned long progAddr = 0xXXXXX; // Address of row to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = progAddr>>16;

// Initialize PM Page Boundary SFR

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE (ASSEMBLY LANGUAGE CODE)

| DISI | #5          | ; | Block all interrupts with priority <7 |

|------|-------------|---|---------------------------------------|

|      |             | ; | for next 5 instructions               |

| MOV  | #0x55, W0   |   |                                       |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                      |

| MOV  | #0xAA, W1   | ; |                                       |

| MOV  | W1, NVMKEY  | ; | Write the AA key                      |

| BSET | NVMCON, #WR | ; | Start the erase sequence              |

| NOP  |             | ; |                                       |

| NOP  |             | ; |                                       |

| BTSC | NVMCON, #15 | ; | and wait for it to be                 |

| BRA  | \$-2        | ; | completed                             |

|      |             |   |                                       |

### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE (C LANGUAGE CODE)

| // C example using MPLAB | C30 |                                                                   |

|--------------------------|-----|-------------------------------------------------------------------|

| asm("DISI #5");          |     | Block all interrupts with priority < 7<br>for next 5 instructions |

| builtin_write_NVM();     | //  | Perform unlock sequence and set WR                                |

| Interrupt Source          | Vector | IVT Address | AIVT    | Interrupt Bit Locations |          |              |  |  |

|---------------------------|--------|-------------|---------|-------------------------|----------|--------------|--|--|

| interrupt Source          | Number | IVI Address | Address | Flag                    | Enable   | Priority     |  |  |

| ADC1 Conversion Done      | 13     | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |  |

| Comparator Event          | 18     | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |  |

| CRC Generator             | 67     | 00009Ah     | 00019Ah | IFS4<3>                 | IEC4<3>  | IPC16<14:12> |  |  |

| CTMU Event                | 77     | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |  |

| External Interrupt 0      | 0      | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |  |

| External Interrupt 1      | 20     | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |  |

| External Interrupt 2      | 29     | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |  |

| I2C1 Master Event         | 17     | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |  |

| I2C1 Slave Event          | 16     | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |  |

| I2C2 Master Event         | 50     | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |  |

| I2C2 Slave Event          | 49     | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |  |

| Input Capture 1           | 1      | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |  |

| Input Capture 2           | 5      | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |  |

| Input Capture 3           | 37     | 00005Eh     | 00015Eh | IFS2<5>                 | IEC2<5>  | IPC9<6:4>    |  |  |

| Input Capture 4           | 38     | 000060h     | 000160h | IFS2<6>                 | IEC2<6>  | IPC9<10:8>   |  |  |

| Input Capture 5           | 39     | 000062h     | 000162h | IFS2<7>                 | IEC2<7>  | IPC9<14:12>  |  |  |

| Input Change Notification | 19     | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |  |

| LVD Low-Voltage Detect    | 72     | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |  |

| Output Compare 1          | 2      | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |  |

| Output Compare 2          | 6      | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |  |

| Output Compare 3          | 25     | 000046h     | 000146h | IFS1<9>                 | IEC1<9>  | IPC6<6:4>    |  |  |

| Output Compare 4          | 26     | 000048h     | 000148h | IFS1<10>                | IEC1<10> | IPC6<10:8>   |  |  |

| Output Compare 5          | 41     | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |  |

| Parallel Master Port      | 45     | 00006Eh     | 00016Eh | IFS2<13>                | IEC2<13> | IPC11<6:4>   |  |  |

| Real-Time Clock/Calendar  | 62     | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |  |

| SPI1 Error                | 9      | 000026h     | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>    |  |  |

| SPI1 Event                | 10     | 000028h     | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>   |  |  |

| SPI2 Error                | 32     | 000054h     | 000154h | IFS2<0>                 | IEC2<0>  | IPC8<2:0>    |  |  |

| SPI2 Event                | 33     | 000056h     | 000156h | IFS2<1>                 | IEC2<1>  | IPC8<6:4>    |  |  |

| Timer1                    | 3      | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |  |

| Timer2                    | 7      | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |  |

| Timer3                    | 8      | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |  |

| Timer4                    | 27     | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |  |

| Timer5                    | 28     | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |  |

| UART1 Error               | 65     | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |  |

| UART1 Receiver            | 11     | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |  |

| UART1 Transmitter         | 12     | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |  |

| UART2 Error               | 66     | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |  |

| UART2 Receiver            | 30     | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |  |

| UART2 Transmitter         | 31     | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |  |

## TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| U-0          | U-0                                                                                          | R/W-0                             | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|-----------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|--|--|

|              | _                                                                                            | AD1IE                             | U1TXIE           | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |  |  |  |  |  |  |  |

| bit 15       |                                                                                              |                                   |                  | •                 |                  |                 | bit    |  |  |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                        | R/W-0                             | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |  |

| T2IE         | OC2IE                                                                                        | IC2IE                             | _                | T1IE              | OC1IE            | IC1IE           | INTOIE |  |  |  |  |  |  |  |

| bit 7        |                                                                                              |                                   |                  |                   |                  |                 | bit    |  |  |  |  |  |  |  |

| Legend:      |                                                                                              |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                       | W = Writable                      | bit              | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                        | '1' = Bit is set                  |                  | '0' = Bit is clea |                  | x = Bit is unkn | own    |  |  |  |  |  |  |  |

| bit 15-14    | Unimplemer                                                                                   | nted: Read as '                   | 0'               |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 13       | AD1IE: A/D                                                                                   | Conversion Cor                    | nplete Interrupt | t Enable bit      |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 12       | -                                                                                            | RT1 Transmitte                    |                  | ole bit           |                  |                 |        |  |  |  |  |  |  |  |

|              | 1 = Interrupt                                                                                | request enable                    | d                |                   |                  |                 |        |  |  |  |  |  |  |  |

|              | 0 = Interrupt                                                                                | request not ena                   | abled            |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 11       |                                                                                              | RT1 Receiver li                   |                  | bit               |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | 1 = Interrupt request enabled     |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 10       | 0 = Interrupt request not enabled                                                            |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              | SPI1IE: SPI1 Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled         |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              | <ul> <li>Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ul>         |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 9        | SPF1IE: SPI1 Fault Interrupt Enable bit                                                      |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 8        |                                                                                              | Interrupt Enab                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 7        |                                                                                              | Interrupt Enab                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 6        |                                                                                              | ut Compare Ch                     |                  | ot Enable bit     |                  |                 |        |  |  |  |  |  |  |  |

|              | •                                                                                            | request enable                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 5        | IC2IE: Input                                                                                 | Capture Chann                     | el 2 Interrupt E | nable bit         |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              | -                                                                                            | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 4        | -                                                                                            | nted: Read as '                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 3        |                                                                                              | Interrupt Enab<br>request enable  |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 2        | OC1IE: Outp                                                                                  | ut Compare Ch                     | annel 1 Interru  | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |  |

|              | 1 = Interrupt                                                                                | request enable                    | d                |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 1        | -                                                                                            | Capture Chann                     |                  | nable bit         |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

| bit 0        |                                                                                              | rnal Interrupt 0                  |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              | request enable                    |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

|              |                                                                                              |                                   |                  |                   |                  |                 |        |  |  |  |  |  |  |  |

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

# PIC24FJ64GA104 FAMILY

### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| —     | AD1IP2 | AD1IP1 | AD1IP0 | —   | U1TXIP2 | U1TXIP1 | U1TXIP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

| Legend:                                                           |         |                                                                                                         |                      |                    |  |

|-------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |         | U = Unimplemented bit, read as '0'                                                                      |                      |                    |  |

|                                                                   |         | '1' = Bit is set                                                                                        | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-7<br>bit 6-4                                               | AD1IP<2 | <b>nented:</b> Read as '0'<br>: <b>0&gt;:</b> A/D Conversion Comple<br>errupt is priority 7 (highest pr |                      |                    |  |

|         | •                                                          |

|---------|------------------------------------------------------------|

|         | •                                                          |

|         | 001 = Interrupt is priority 1                              |

|         | 000 = Interrupt source is disabled                         |

| bit 3   | Unimplemented: Read as '0'                                 |

| bit 2-0 | U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits     |

|         | 111 = Interrupt is priority 7 (highest priority interrupt) |

|         | •                                                          |

|         | •                                                          |

|         | •                                                          |

|         | 001 = Interrupt is priority 1                              |

|         | 000 = Interrupt source is disabled                         |

© 2010 Microchip Technology Inc.

## PIC24FJ64GA104 FAMILY

|                    | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | R/W-1            | R/W-0           | R/W-0  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|--|--|--|

| —                  | T4IP2                                                                                                                                       | T4IP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T4IP0                                                                                                  |                   | OC4IP2           | OC4IP1          | OC4IP0 |  |  |  |

| bit 15             |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 | bit    |  |  |  |

|                    |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |

| U-0                | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | U-0              | U-0             | U-0    |  |  |  |

|                    | OC3IP2                                                                                                                                      | OC3IP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OC3IP0                                                                                                 |                   |                  |                 |        |  |  |  |

| bit 7              |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 | bit    |  |  |  |

| Legend:            |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |

| R = Readat         | ole bit                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                    | U = Unimplei      | mented bit, read | d as '0'        |        |  |  |  |

| -n = Value a       | at POR                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        | '0' = Bit is cle  | eared            | x = Bit is unkr | nown   |  |  |  |

|                    |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |

| bit 15             | Unimplemer                                                                                                                                  | nted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0'                                                                                                     |                   |                  |                 |        |  |  |  |

| bit 14-12          | <b>T4IP&lt;2:0&gt;:</b> ⊺                                                                                                                   | Timer4 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Priority bits                                                                                          |                   |                  |                 |        |  |  |  |

|                    | 111 = Interru                                                                                                                               | pt is priority 7 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | highest priority                                                                                       | / interrupt)      |                  |                 |        |  |  |  |

|                    | •                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |

|                    | •                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |

|                    | •<br>001 = Interrupt is priority 1                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |  |  |  |