#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | •                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga102t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

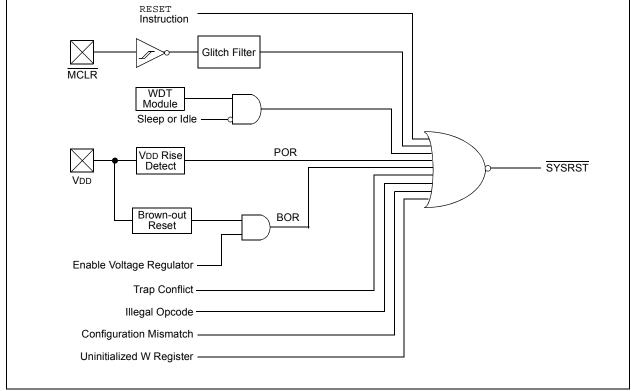

#### 6.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 7. "Reset" (DS39712).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

FIGURE 6-1:

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Refer to the specific peripheral or CPU Note: section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A Power-on Reset will clear all bits, except for the BOR and POR bits (RCON<1:0>), which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

RESET SYSTEM BLOCK DIAGRAM

### 7.3 Interrupt Control and Status Registers

The PIC24FJ64GA104 family of devices implements the following registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- · IEC0 through IEC4

- IPC0 through IPC20 (except IPC13, IPC14 and IPC17)

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit which is set by the respective peripherals, or an external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>); these indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which, together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test Register (INTTREG) that displays the status of the interrupt controller. When an interrupt request occurs, its associated vector number and the new interrupt priority level are latched into INTTREG.

This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors – such as when ISR remapping is used in bootloader applications. It also could be used to check if another interrupt is pending while in an ISR.

All interrupt registers are described in Register 7-1 through Register 7-32, on the following pages.

## 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

NOTES:

# 9.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |

|       | Section 39. "Power-Saving Features         |  |  |  |  |

|       | with Deep Sleep" (DS39727).                |  |  |  |  |

The PIC24FJ64GA104 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep, Idle and Deep Sleep modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals except RTCC and DSWDT. It also freezes I/O states and removes power to SRAM and Flash memory. The assembly syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

| EXAMPLE 9-1: | <b>PWRSAV INSTRUCTION SYNTAX</b> |

|--------------|----------------------------------|

|              |                                  |

| PWRSAV | #SLEEP_MODE  | ; Put the device into SLEEP mode      |

|--------|--------------|---------------------------------------|

| PWRSAV | #IDLE_MODE   | ; Put the device into IDLE mode       |

| BSET   | DSCON, #DSEN | ; Enable Deep Sleep                   |

| PWRSAV | #SLEEP_MODE  | ; Put the device into Deep SLEEP mode |

### REGISTER 10-13: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      |     |     | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 12-8  | SCK2R<4:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                         |

| bit 4-0   | SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 10-14: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS2R<4:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

## REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      | —   |     | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 12-8  | RP21R<4:0>: RP21 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP21 (see Table 10-3 for peripheral function numbers). |

| bit 7-5   | Unimplemented: Read as '0'                                                                            |

| bit 4-0   | RP20R<4:0>: RP20 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP20 (see Table 10-3 for peripheral function numbers). |

Note 1: This register is unimplemented in 28-pin devices; all bits read as '0'.

| U-0                                | U-0                                                                  | U-0 | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|----------------------------------------------------------------------|-----|--------|-----------------------------------------|--------|--------|--------|

|                                    | —                                                                    | —   | RP23R4 | RP23R3                                  | RP23R2 | RP23R1 | RP23R0 |

| bit 15                             |                                                                      |     |        |                                         |        |        | bit 8  |

|                                    |                                                                      |     |        |                                         |        |        |        |

| U-0                                | U-0                                                                  | U-0 | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|                                    | —                                                                    | —   | RP22R4 | RP22R3                                  | RP22R2 | RP22R1 | RP22R0 |

| bit 7                              |                                                                      |     |        |                                         |        |        | bit 0  |

|                                    |                                                                      |     |        |                                         |        |        |        |

| Legend:                            |                                                                      |     |        |                                         |        |        |        |

| R = Readable                       | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |        |                                         |        |        |        |

| -n = Value at POR '1' = Bit is set |                                                                      |     |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |

### **REGISTER 10-26:** RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

bit 15-13 Unimplemented: Read as '0'

bit 12-8 RP23R<4:0>: RP23 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP23 (see Table 10-3 for peripheral function numbers).

bit 7-5 Unimplemented: Read as '0'

bit 4-0 RP22R<4:0>: RP22 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP22 (see Table 10-3 for peripheral function numbers).

Note 1: This register is unimplemented in 28-pin devices; all bits read as '0'.

# 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two Independent 16-Bit Timers with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- ADC Event Trigger (Timer4/5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC event trigger; this is implemented only with Timer5. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON       |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | control bits are ignored. Only T2CON and    |  |  |  |  |  |  |  |

|       | T4CON control bits are used for setup and   |  |  |  |  |  |  |  |

|       | control. Timer2 and Timer4 clock and gate   |  |  |  |  |  |  |  |

|       | inputs are utilized for the 32-bit timer    |  |  |  |  |  |  |  |

|       | modules, but an interrupt is generated with |  |  |  |  |  |  |  |

|       | the Timer3 or Timer5 interrupt flags.       |  |  |  |  |  |  |  |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

| R/W-0              | U-0                                                                                                                 | R/W-0                    | U-0                   | U-0               | U-0             | U-0                  | U-0          |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------|-----------------|----------------------|--------------|--|--|--|--|

| TON <sup>(1)</sup> | _                                                                                                                   | TSIDL <sup>(1)</sup>     |                       |                   | —               |                      | _            |  |  |  |  |

| bit 15             |                                                                                                                     |                          |                       |                   |                 |                      | bit          |  |  |  |  |

|                    |                                                                                                                     |                          |                       |                   |                 |                      |              |  |  |  |  |

| U-0                | R/W-0                                                                                                               | R/W-0                    | R/W-0                 | U-0               | U-0             | R/W-0                | U-0          |  |  |  |  |

| —                  | TGATE <sup>(1)</sup>                                                                                                | TCKPS1 <sup>(1)</sup>    | TCKPS0 <sup>(1)</sup> | —                 | —               | TCS <sup>(1,2)</sup> | —            |  |  |  |  |

| bit 7              |                                                                                                                     |                          |                       |                   |                 |                      | bit          |  |  |  |  |

| Legend:            |                                                                                                                     |                          |                       |                   |                 |                      |              |  |  |  |  |

| R = Readab         | ole bit                                                                                                             | W = Writable             | bit                   | U = Unimplem      | nented bit, rea | d as '0'             |              |  |  |  |  |

| -n = Value a       | It POR                                                                                                              | '1' = Bit is set         |                       | '0' = Bit is clea |                 | x = Bit is unkno     | wn           |  |  |  |  |

|                    |                                                                                                                     |                          |                       |                   |                 |                      |              |  |  |  |  |

| bit 15             | TON: Timery                                                                                                         | On bit <sup>(1)</sup>    |                       |                   |                 |                      |              |  |  |  |  |

|                    |                                                                                                                     | 1 = Starts 16-bit Timery |                       |                   |                 |                      |              |  |  |  |  |

|                    | 0 = Stops 16                                                                                                        | -                        |                       |                   |                 |                      |              |  |  |  |  |

| bit 14             |                                                                                                                     | ted: Read as '           |                       |                   |                 |                      |              |  |  |  |  |

| bit 13             | <b>TSIDL:</b> Stop in Idle Mode bit <sup>(1)</sup><br>1 = Discontinue module operation when device enters Idle mode |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    |                                                                                                                     |                          | ion in Idle mode      |                   | emode           |                      |              |  |  |  |  |

| bit 12-7           |                                                                                                                     | ted: Read as '           |                       |                   |                 |                      |              |  |  |  |  |

| bit 6              | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup>                                              |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | When TCS = 1:                                                                                                       |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | This bit is ignored.                                                                                                |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | When TCS = 0:                                                                                                       |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | <ul> <li>1 = Gated time accumulation is enabled</li> <li>0 = Gated time accumulation is disabled</li> </ul>         |                          |                       |                   |                 |                      |              |  |  |  |  |

| bit 5-4            |                                                                                                                     |                          |                       | Select hits(1)    |                 |                      |              |  |  |  |  |

|                    | <b>TCKPS&lt;1:0&gt;:</b> Timery Input Clock Prescale Select bits <sup>(1)</sup><br>11 = 1:256                       |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | 10 = 1:64                                                                                                           |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | 01 = 1:8                                                                                                            |                          |                       |                   |                 |                      |              |  |  |  |  |

|                    | 00 = 1:1                                                                                                            |                          | - 1                   |                   |                 |                      |              |  |  |  |  |

| bit 3-2            | -                                                                                                                   | ted: Read as '           |                       |                   |                 |                      |              |  |  |  |  |

| bit 1              | -                                                                                                                   | Clock Source S           |                       |                   |                 |                      |              |  |  |  |  |

|                    |                                                                                                                     | clock from pin           | TyCK (on the ri       | sing eage)        |                 |                      |              |  |  |  |  |

| bit 0              |                                                                                                                     | ted: Read as '           | 0'                    |                   |                 |                      |              |  |  |  |  |

|                    | Vhen 32-hit oper                                                                                                    | ation is enable          | d (T2CON<3> (         | or T4CON<3>       | = 1) these hit  | s have no effect o   | on Timery    |  |  |  |  |

|                    | peration; all time                                                                                                  |                          |                       |                   |                 |                      | Shi titilety |  |  |  |  |

|                    | f TCS = 1, RPIN                                                                                                     |                          | -                     |                   |                 |                      |              |  |  |  |  |

Pin Select (PPS)" for more information. 3: Changing the value of TyCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: initialize OCx pin low, toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: initialize OCx pin low, toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: compare events continuously toggle OCx pin

- 010 = Single Compare Single-Shot mode: initialize OCx pin high, compare event forces OCx pin low

- 001 = Single Compare Single-Shot mode: initialize OCx pin low, compare event forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

- **2:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

# REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (When operating as I <sup>2</sup> C master. Applicable during master receive.)                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                       |

| bit 4 | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                             |

| DIL 4 | (When operating as I <sup>2</sup> C master. Applicable during master receive.)                                                                                                     |

|       | 1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware clear at end of master Acknowledge sequence.                                       |

|       | 0 = Acknowledge sequence is not in progress                                                                                                                                        |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                        |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul> |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                  |

|       | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>              |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enabled bit (when operating as I <sup>2</sup> C master)                                                                                      |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.                                                             |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                    |

| bit 0 | SEN: Start Condition Enabled bit (when operating as I <sup>2</sup> C master)                                                                                                       |

|       | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>           |

| RW-0       RW-0 <sup>(2)</sup> U-0       R/W-0 <sup>(2)</sup> R/W-0       R/W-0       R/W-0       R/W-0         CSF1       CSF0       ALP       —       CS1P       BEP       WRSP       RDSP         bit 7       bit       —       CS1P       BEP       WRSP       RDSP         bit 7       —       Dit       —       CS1P       BEP       WRSP       RDSP         bit 7       —       O       CS1P       BEP       WRSP       RDSP         bit 7       —       O       = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0          | U-0                                                                                            | R/W-0           | R/W-0                  | R/W-0                  | R/W-0           | R/W-0           | R/W-0  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------|-----------------|------------------------|------------------------|-----------------|-----------------|--------|--|--|--|

| RW-0       RW-0       RW-0 <sup>(2)</sup> U-0       RW-0 <sup>(2)</sup> RW-0       RW-0       RW-0         CSF1       CSF0       ALP       —       CS1P       BEP       WRSP       RDSP         bit       Dit       —       CS1P       BEP       WRSP       RDSP         bit       —       -       CS1P       BEP       WRSP       RDSP         bit       —       -       CS1P       BEP       WRSP       RDSP         bit       —       -       CS1P       BEP       WRSP       RDSP         bit       -       -       Other       -       CS1P       BEP       WRSP       RDSP         bit       -       -       -       -       Bit       -       -       Bit       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PMPEN          |                                                                                                | PSIDL           | ADRMUX1 <sup>(1)</sup> | ADRMUX0 <sup>(1)</sup> | PTBEEN          | PTWREN          | PTRDEN |  |  |  |

| CSF1       CSF0       ALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15         |                                                                                                | •               |                        |                        |                 |                 | bit 8  |  |  |  |

| CSF1       CSF0       ALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>D</b> 444 0 | <b>D</b> 1110                                                                                  | D (A) (2)       |                        | DAM (2)                |                 | DAMA            |        |  |  |  |

| bit 7 bit  Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown  PMPEN: Parallel Master Port Enable bit 1 = PMP is enabled 0 = PMP is disabled, no off-chip access performed Unimplemented: Read as '0' bit 13 PSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12-11 ADRMUX<1:0-: Address/Data Multiplexing Selection bits <sup>(1)</sup> 11 = Reserved 10 = All 16 bits of address are multiplexed on PMD<7:0> pins 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed o PMA<10:8- 00 = Address and data appear on separate pins 01 = PMEE port is enabled 0 = PMRE port is enabled 0 = PMREPORT is enabled                           |                | -                                                                                              | -               | 0-0                    |                        | -               | -               |        |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PMPEN: Parallel Master Port Enable bit<br>1 = PMP is enabled<br>0 = PMP is disabled, no off-chip access performed<br>bit 14 Unimplemented: Read as '0'<br>bit 13 PSIDL: Stop in Idle Mode bit<br>1 = Discontinue module operation when device enters Idle mode<br>0 = Continue module operation when device enters Idle mode<br>0 = Continue module operation when device enters Idle mode<br>1 = Discontinue module operation when device enters Idle mode<br>1 = Discontinue module operation when device enters Idle mode<br>1 = Discontinue module operation when device enters Idle mode<br>1 = Chartinue module operation when device enters Idle mode<br>1 = Chartinue module operation when device enters Idle mode<br>1 = Chartinue module operation when device enters Idle mode<br>1 = Chartinue module operation when device enters Idle mode<br>1 = Atl t6 bits of address are multiplexed on PMD<7:0> pins<br>01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed of<br>PMA<10.8><br>00 = Address and data appear on separate pins<br>01 = DMBE port is disabled<br>0 = PMBRP/PMENB port is enabled<br>0 = PMMRP/PMENB port is enabled<br>0 = PMMRP/PMENB port is disabled<br>bit 9 PTWREN: Write Enable Strobe Port Enable bit<br>1 = PMMRP/PMENB port is disabled<br>bit 8 PTRDEN: Read/Write Strobe Port Enable bit<br>1 = PMRD/PMWR port is disabled<br>bit 7-6 CSF<1:0;: Chip Select Function bits<br>1 = Reserved<br>1 = PMServed<br>1 = PMSS1 functions as chip set<br>1 = Reserved<br>0 = Active-low (PMALL and PMALH)<br>0 = Active-low (PMALL and PMALH)<br>0 = Active-low (PMCS1/PMCS1)<br>0 = Active-low (PMCS1/PMCS1)                                                                                                                                                                                   |                | CSF0                                                                                           | ALP             | —                      | CS1P                   | BEP             | WRSP            |        |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PMPEN: Parallel Master Port Enable bit       1 = PMP is enabled       x = Bit is unknown         bit 15       PMPEN: Parallel Master Port Enable bit       1 = PMP is enabled       x = Bit is unknown         bit 14       Unimplemented: Read as '0'       bit 13       PSIDL: Stop in Idle Mode bit       1 = Discontinue module operation when device enters Idle mode         bit 13       PSIDL: Stop in Idle Mode bit       1 = Discontinue module operation when device enters Idle mode       0 = Continue module operation in Idle mode         bit 12-11       ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup> 11 = Reserved       10 = All 16 bits of address are multiplexed on PMD<7:0> pins         01 = Lower 8 bits of address are multiplexed on PMD<7:0>       pins       01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins         01 = PMEEPits Bits enabled       0 = PMRP/PMENB port is enabled       0 = PMRP/PMENB port is enabled       0 = PMRP/PMENB port is enabled         0 = PMEEPits Bits bit 10       PTBEEN: Read/Write Strobe Port Enable bit       1 = PMWR/PMENB port is enabled       0 = PMRD/PMWR port is enabled         0 = PMCS1 functions as chip set       1 = PMWR/PMENB port is enabled       0 = PMCS1 functions as chip set <td< td=""><td>bit 7</td><td></td><td></td><td></td><td></td><td></td><td></td><td>bit</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 7          |                                                                                                |                 |                        |                        |                 |                 | bit    |  |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PMPEN: Parallel Master Port Enable bit       1 = PMP is enabled       0 = PMP is disabled, no off-chip access performed         bit 14       Unimplemented: Read as '0'       PSIDL: Stop in Idle Mode bit       1 = Discontinue module operation when device enters Idle mode         0 = Continue module operation in Idle mode       0 = Continue module operation in Idle mode       0 = Continue module operation in Idle mode         bit 12-11       ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup> 1 = Reserved       1 = All 16 bits of address are multiplexed on PMD<7:0> pins         01 = All 16 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed or PMA<10:8>       00 = Address and data appear on separate pins         bit 10       PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)       1 = PMEE port is enabled         0 = PMBE port is disabled       0 = PMWR/PMENB port is enabled       0 = PMWR/PMENB port is enabled         0 = PMBEP ort is disabled       0 = PMWR/PMENB port is disabled       0 = PMWR/PMENB port is disabled         bit 8       PTRDEN: Read/Write Strobe Port Enable bit       1 = PMRD/PMWR port is disabled         0 = PMCS1 functions as chip set       1 = Reserved       0 = PMCS1 functions as chip set         1 = Reserved       0 = Reserved       0 = Reserved       0 = Reserved </td <td>Legend:</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Legend:        |                                                                                                |                 |                        |                        |                 |                 |        |  |  |  |

| <ul> <li>PMPEN: Parallel Master Port Enable bit</li> <li>1 = PMP is enabled</li> <li>0 = PMP is disabled, no off-chip access performed</li> <li>Dit 14 Unimplemented: Read as '0'</li> <li>PSIDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>Dit 12-11 ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMA&lt;10:8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>DTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)</li> <li>1 = PMBE port is enabled</li> <li>0 = PMEE port is disabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is disabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = PMRCS1 functions as chip set</li> <li>0 = Reserved</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMALT and PMALH)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R = Readabl    | e bit                                                                                          | W = Writable    | bit                    | U = Unimplem           | ented bit, read | d as '0'        |        |  |  |  |

| <ul> <li>1 = PMP is enabled</li> <li>0 = PMP is disabled, no off-chip access performed</li> <li>0 = PMP is disabled, no off-chip access performed</li> <li>0 = SiDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>1 = Discontinue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Aldress/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMA&lt;7:0.8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>01 = PMBE port is enabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is disabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = PMCD/PMWR port is disabled</li> <li>0 = PMCS1 functions as chip set</li> <li>0 = PMCS1 functions as chip set</li> <li>0 = Reserved</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMACS1/PMCS1)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> </ul>                                                                                                                                                                                                    | -n = Value at  | POR                                                                                            | '1' = Bit is se | t                      | '0' = Bit is clea      | ired            | x = Bit is unkr | nown   |  |  |  |

| <ul> <li>1 = PMP is enabled</li> <li>0 = PMP is disabled, no off-chip access performed</li> <li>0 = PMP is disabled, no off-chip access performed</li> <li>0 = SiDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>1 = Discontinue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Aldress/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMA&lt;7:0.8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>01 = PMBE port is enabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is disabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = PMCD/PMWR port is disabled</li> <li>0 = PMCS1 functions as chip set</li> <li>0 = PMCS1 functions as chip set</li> <li>0 = Reserved</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMACS1/PMCS1)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> </ul>                                                                                                                                                                                                    |                |                                                                                                |                 |                        |                        |                 |                 |        |  |  |  |

| <ul> <li>0 = PMP is disabled, no off-chip access performed</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>PSIDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>bit 12-11</li> <li>ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins</li> <li>01 = Lower 8 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMA&lt;10:8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>bit 10</li> <li>PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)</li> <li>1 = PMBE port is enabled</li> <li>0 = PMBE port is disabled</li> <li>bit 9</li> <li>PTWREN: Write Enable Strobe Port Enable bit</li> <li>1 = PMRD/PMENB port is disabled</li> <li>bit 8</li> <li>PTRDEN: Read/Write Strobe Port Enable bit</li> <li>1 = PMRD/PMWR port is disabled</li> <li>bit 7-6</li> <li>CSF&lt;1:0&gt;: Chip Select Function bits</li> <li>1 = Reserved</li> <li>0 = PMRD/PMWR port is disabled</li> <li>bit 5</li> <li>ALP: Address Latch Polarity bit<sup>(2)</sup></li> <li>1 = Active-high (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15         |                                                                                                |                 | rt Enable bit          |                        |                 |                 |        |  |  |  |

| bit 14       Unimplemented: Read as '0'         bit 13       PSIDL: Stop in Idle Mode bit         1 = Discontinue module operation when device enters Idle mode       0 = Continue module operation in Idle mode         0 = Continue module operation in Idle mode       0 = Continue module operation in Idle mode         bit 12-11       ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup> 11 = Reserved       10 = All 16 bits of address are multiplexed on PMD<7:0> pins         01 = All 16 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed or PMA-10:8>         00 = Address and data appear on separate pins       00 = Address and data appear on separate pins         01 = PMBE port is enabled       0 = PMBE port is enabled         0 = PMBE port is enabled       0 = PMBE port is enabled         0 = PMWR/PMENB port is enabled       0 = PMWR/PMENB port is enabled         0 = PMRD/PMWR port is enabled       0 = PMRD/PMWR port is disabled         bit 7-6       CSF<1:0>: Chip Select Function bits         11 = Reserved       10 = PMCS1 functions as chip set         10 = PMCS1 functions as chip set       1 = Reserved         10 = Reserved       0 = Reserved         00 = Reserved       0 = Reserved         00 = Reserved       0 = Reserved         01 = Active-high (PMALL and PMALH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                                                                |                 |                        | <b>f</b>               |                 |                 |        |  |  |  |

| <ul> <li>bit 13 PSIDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>0 = Continue module operation in Idle mode</li> <li>bit 12-11 ADRMUX-1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins</li> <li>01 = Lower 8 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed on PMD&lt;10&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>00 = Address and data appear on separate pins</li> <li>01 = PMBE port is enabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMWR/PMENB port is enabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = Reserved</li> <li>10 = Reserved</li> <li>11 = Reserved</li> <li>12 = Reserved</li> <li>13 = Reserved</li> <li>14 = Reserved</li> <li>15 ALP: Address Latch Polarity bit<sup>(2)</sup></li> <li>14 = Active-high (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> <li>0 = Active-low (PMALS 1/PMCS1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                                                                                                |                 |                        | errormed               |                 |                 |        |  |  |  |

| <ul> <li>a Discontinue module operation when device enters Idle mode</li> <li>a Discontinue module operation in Idle mode</li> <li>bit 12-11</li> <li>ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>a Reserved</li> <li>a All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins</li> <li>bit 10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed on PMD</li> <li>a Address and data appear on separate pins</li> <li>bit 10</li> <li>PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)</li> <li>a PMWR/PMENB port is enabled</li> <li>bit 9</li> <li>PTWREN: Write Enable Strobe Port Enable bit</li> <li>a PMWR/PMENB port is enabled</li> <li>bit 8</li> <li>PTRDEN: Read/Write Strobe Port Enable bit</li> <li>a PMRD/PMWR port is disabled</li> <li>bit 7-6</li> <li>CSF&lt;1:0:: Chip Select Function bits</li> <li>a Reserved</li> <li>a PMCS1 functions as chip set</li> <li>a Reserved</li> <li>bit 5</li> <li>ALP: Address Latch Polarity bit<sup>(2)</sup></li> <li>a Active-high (PMALL and PMALH)</li> <li>bit 4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CS1P: Chip Select 1 Pola</li></ul> |                | -                                                                                              |                 |                        |                        |                 |                 |        |  |  |  |

| <ul> <li>0 = Continue module operation in Idle mode</li> <li>bit 12-11</li> <li>ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = All 16 bits of address are multiplexed on PMD&lt;7:0&gt; pins</li> <li>01 = Lower 8 bits of address are multiplexed on PMD&lt;7:0&gt; pins; upper 3 bits are multiplexed or PMA&lt;10:8&gt;</li> <li>00 = Address and data appear on separate pins</li> <li>bit 10</li> <li>PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)</li> <li>1 = PMBE port is enabled</li> <li>0 = PMBE port is enabled</li> <li>0 = PMBE port is disabled</li> <li>0 = PMRD/PMENB port is enabled</li> <li>0 = PMRD/PMENB port is enabled</li> <li>0 = PMRD/PMWR port is disabled</li> <li>0 = Reserved</li> <li>10 = PMCS1 functions as chip set</li> <li>0 = Reserved</li> <li>1 = Active-high (PMALL and PMALH)</li> <li>0 = Active-low (PMCS1/PMCS1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DIT 13         | •                                                                                              |                 |                        | uine entere Idle       |                 |                 |        |  |  |  |

| bit 12-11       ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup> 11 = Reserved       10 = All 16 bits of address are multiplexed on PMD<7:0> pins         01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed or PMA<10:8>         00 = Address and data appear on separate pins         bit 10       PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)         1 = PMBE port is enabled         0 = PMWR/PMENB port is enabled         0 = PMRD/PMWR port is enabled         0 = PMCS1 functions as chip set         0 = Reserved         0 = Active-ligh (PMALL and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                                                                                                |                 |                        |                        |                 |                 |        |  |  |  |