#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga104-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-2: PIC24FJ64GA104 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

| Pin Number |                               |               |                        |     |                                                                                       |                                                            |

|------------|-------------------------------|---------------|------------------------|-----|---------------------------------------------------------------------------------------|------------------------------------------------------------|

| Function   | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | I/O | Input<br>Buffer                                                                       | Description                                                |

| VCAP       | 20                            | 17            | 7                      | Р   | _                                                                                     | External Filter Capacitor Connection (regulator enabled).  |

| Vdd        | 13, 28                        | 10, 25        | 28, 40                 | Р   | _                                                                                     | Positive Supply for Peripheral Digital Logic and I/O Pins. |

| VDDCORE    | 20                            | 17            | 7                      | Р   | <ul> <li>Positive Supply for Microcontroller Core Logic (regula disabled).</li> </ul> |                                                            |

| VREF-      | 3                             | 28            | 20                     | I   | ANA                                                                                   | A/D and Comparator Reference Voltage (low) Input.          |

| VREF+      | 2                             | 27            | 19                     | I   | ANA                                                                                   | A/D and Comparator Reference Voltage (high) Input.         |

| Vss        | 8, 27                         | 5, 24         | 29, 39                 | Р   | _                                                                                     | Ground Reference for Logic and I/O Pins.                   |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

### 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This section applies only to PIC     | 24FJ   |

|-------|--------------------------------------|--------|

|       | devices with an on-chip voltage regu | lator. |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 25.2 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

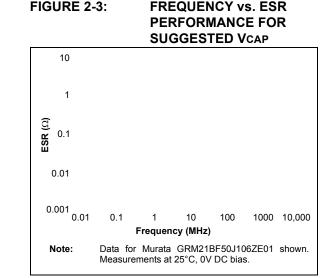

When the regulator is enabled, a low-ESR (<5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu$ F, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 28.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 28.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

### TABLE 4-7: INPUT CAPTURE REGISTER MAP

| © 2010     |  |

|------------|--|

| Microchip  |  |

| Technology |  |

| Inc.       |  |

| File<br>Name | Addr | Bit 15 | Bit 14                          | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7       | Bit 6       | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|---------------------------------|--------|---------|---------|---------|-------|------------|-------------|-------------|-------|----------|----------|----------|----------|----------|---------------|

| IC1CON1      | 0140 | _      | _                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | _           | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2      | 0142 | _      | —                               | —      | —       | —       | _       | —     | IC32       | ICTRIG      | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF       | 0144 |        |                                 |        |         |         |         |       | Input Capt | ure 1 Buffe | r Register  |       |          |          |          |          |          | 0000          |

| IC1TMR       | 0146 |        |                                 |        |         |         |         |       | Timer      | Value 1 Re  | egister     |       |          |          |          |          |          | xxxx          |

| IC2CON1      | 0148 | —      | —                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | —          | —           | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2      | 014A | —      | —                               | —      | —       | —       | —       | —     | IC32       | ICTRIG      | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF       | 014C |        | Input Capture 2 Buffer Register |        |         |         |         |       |            | 0000        |             |       |          |          |          |          |          |               |

| IC2TMR       | 014E |        | Timer Value 2 Register xx       |        |         |         |         |       | xxxx       |             |             |       |          |          |          |          |          |               |

| IC3CON1      | 0150 | —      | —                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —          | —           | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2      | 0152 | —      | _                               | _      | —       | —       | —       | _     | IC32       | ICTRIG      | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF       | 0154 |        |                                 |        |         |         |         |       | Input Capt | ure 3 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC3TMR       | 0156 |        |                                 |        |         |         |         |       | Timer      | Value 3 Re  | egister     |       | -        |          |          | -        |          | xxxx          |

| IC4CON1      | 0158 | —      | _                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | —           | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2      | 015A | —      | —                               | _      | —       | —       | —       | _     | IC32       | ICTRIG      | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF       | 015C |        |                                 |        |         |         |         |       | Input Capt | ure 4 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC4TMR       | 015E |        |                                 |        |         |         |         |       | Timer      | Value 4 Re  | egister     |       |          |          |          |          |          | xxxx          |

| IC5CON1      | 0160 | —      | —                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | —          | —           | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC5CON2      | 0162 | —      | _                               | _      | _       | _       | _       | _     | IC32       | ICTRIG      | TRIGSTAT    | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC5BUF       | 0164 |        |                                 |        |         |         |         |       | Input Capt | ure 5 Buffe | r Register  |       |          |          |          |          |          | 0000          |

| IC5TMR       | 0166 |        |                                 |        |         |         |         |       | Timer      | Value 5 Re  | gister      |       |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0, HC <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0, HS <sup>(1)</sup> | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------------------------|----------------------|--------------------------|-----|-----|-----|-----|-------|

| WR                        | WREN                 | WRERR                    |     | —   | —   | —   | —     |

| bit 15                    |                      |                          |     |     |     |     | bit 8 |

| U-0   | R/W-0 <sup>(1)</sup> | U-0 | U-0 | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |

|-------|----------------------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE                | —   | —   | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |

| bit 7 |                      |     |     |                       |                       |                       | bit 0                 |

| Legend:           | SO = Settable Only bit | HC = Hardware Clearable bit    | HS = Hardware Settable bit |

|-------------------|------------------------|--------------------------------|----------------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, read as | '0'                        |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared           | x = Bit is unknown         |

| bit 15   | WR: Write Control bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                        |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is<br/>cleared by hardware once the operation is complete.</li> </ul>                                                                                                                                                                             |

|          | 0 = Program or erase operation is complete and inactive                                                                                                                                                                                                                                                                                                     |

| bit 14   | WREN: Write Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                       |

|          | 1 = Enable Flash program/erase operations                                                                                                                                                                                                                                                                                                                   |

|          | 0 = Inhibit Flash program/erase operations                                                                                                                                                                                                                                                                                                                  |

| bit 13   | WRERR: Write Sequence Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                         |

|          | 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set<br>automatically on any set attempt of the WR bit)                                                                                                                                                                                                               |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                                                                                                                                                       |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                  |

| bit 6    | ERASE: Erase/Program Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                              |

|          | <ul> <li>1 = Perform the erase operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>0 = Perform the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> </ul>                                                                                                                                                    |

| bit 5-4  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                  |

| bit 3-0  | NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                      |

|          | 1111 = Memory bulk erase operation (ERASE = 1) or no operation (ERASE = $0$ ) <sup>(3)</sup><br>0011 = Memory word program operation (ERASE = $0$ ) or no operation (ERASE = $1$ )<br>0010 = Memory page erase operation (ERASE = $1$ ) or no operation (ERASE = $0$ )<br>0001 = Memory row program operation (ERASE = $0$ ) or no operation (ERASE = $1$ ) |

| Note 1:  | These bits can only be reset on POR.                                                                                                                                                                                                                                                                                                                        |

|          | All other combinations of NVMOP<3:0> are unimplemented.                                                                                                                                                                                                                                                                                                     |

**3:** Available in ICSP<sup>™</sup> mode only. Refer to device programming specification.

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred. Note that BOR is also set after a Power-on Reset.

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                          | Clearing Event          |

|-------------------|--------------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                                    | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access      | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                           | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                             | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                      | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                           | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                              | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                               | POR                     |

| BOR (RCON<1>)     | POR, BOR                                               | —                       |

| POR (RCON<0>)     | POR                                                    | —                       |

| DPSLP (RCON<10>)  | PWRSAV #SLEEP instruction with DSCON <dsen> set</dsen> | POR                     |

TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

# TABLE 6-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant |

|------------|--------------------------|

| POR        | FNOSC Configuration bits |

| BOR        | (CW2<10:8>)              |

| MCLR       | COSC Control bits        |

| WDTO       | (OSCCON<14:12>)          |

| SWR        |                          |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the System Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Interrupt Source          | Vector | IVT Address | AIVT    | Interrupt Bit Locations |          |              |  |

|---------------------------|--------|-------------|---------|-------------------------|----------|--------------|--|

| interrupt Source          | Number | IVI Address | Address | Flag                    | Enable   | Priority     |  |

| ADC1 Conversion Done      | 13     | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| Comparator Event          | 18     | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| CRC Generator             | 67     | 00009Ah     | 00019Ah | IFS4<3>                 | IEC4<3>  | IPC16<14:12> |  |

| CTMU Event                | 77     | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |

| External Interrupt 0      | 0      | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| External Interrupt 1      | 20     | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| External Interrupt 2      | 29     | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| I2C1 Master Event         | 17     | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| I2C1 Slave Event          | 16     | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| I2C2 Master Event         | 50     | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| I2C2 Slave Event          | 49     | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| Input Capture 1           | 1      | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| Input Capture 2           | 5      | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| Input Capture 3           | 37     | 00005Eh     | 00015Eh | IFS2<5>                 | IEC2<5>  | IPC9<6:4>    |  |

| Input Capture 4           | 38     | 000060h     | 000160h | IFS2<6>                 | IEC2<6>  | IPC9<10:8>   |  |

| Input Capture 5           | 39     | 000062h     | 000162h | IFS2<7>                 | IEC2<7>  | IPC9<14:12>  |  |

| Input Change Notification | 19     | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| LVD Low-Voltage Detect    | 72     | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |

| Output Compare 1          | 2      | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |

| Output Compare 2          | 6      | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |

| Output Compare 3          | 25     | 000046h     | 000146h | IFS1<9>                 | IEC1<9>  | IPC6<6:4>    |  |

| Output Compare 4          | 26     | 000048h     | 000148h | IFS1<10>                | IEC1<10> | IPC6<10:8>   |  |

| Output Compare 5          | 41     | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |

| Parallel Master Port      | 45     | 00006Eh     | 00016Eh | IFS2<13>                | IEC2<13> | IPC11<6:4>   |  |

| Real-Time Clock/Calendar  | 62     | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |

| SPI1 Error                | 9      | 000026h     | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>    |  |

| SPI1 Event                | 10     | 000028h     | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>   |  |

| SPI2 Error                | 32     | 000054h     | 000154h | IFS2<0>                 | IEC2<0>  | IPC8<2:0>    |  |

| SPI2 Event                | 33     | 000056h     | 000156h | IFS2<1>                 | IEC2<1>  | IPC8<6:4>    |  |

| Timer1                    | 3      | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |

| Timer2                    | 7      | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |

| Timer3                    | 8      | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |

| Timer4                    | 27     | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |

| Timer5                    | 28     | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |

| UART1 Error               | 65     | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |

| UART1 Receiver            | 11     | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |

| UART1 Transmitter         | 12     | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |

| UART2 Error               | 66     | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |

| UART2 Receiver            | 30     | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |

| UART2 Transmitter         | 31     | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |

### TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| U-0          | U-0                                                                                            | R/W-0                                                                                                  | U-0           | U-0               | U-0             | R/W-0           | U-0    |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------|-----------------|--------|--|--|--|--|

|              | —                                                                                              | PMPIF                                                                                                  | _             | —                 | _               | OC5IF           |        |  |  |  |  |

| bit 15       |                                                                                                |                                                                                                        |               |                   |                 |                 | bit    |  |  |  |  |

|              |                                                                                                |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

| R/W-0        | R/W-0                                                                                          | R/W-0                                                                                                  | U-0           | U-0               | U-0             | R/W-0           | R/W-0  |  |  |  |  |

| IC5IF        | IC4IF                                                                                          | IC3IF                                                                                                  | —             | —                 | —               | SPI2IF          | SPF2IF |  |  |  |  |

| bit 7        |                                                                                                |                                                                                                        |               |                   |                 |                 | bit    |  |  |  |  |

| Legend:      |                                                                                                |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

| R = Readab   | le bit                                                                                         | W = Writable b                                                                                         | it            | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value a | t POR                                                                                          | '1' = Bit is set                                                                                       |               | '0' = Bit is clea |                 | x = Bit is unkr | nown   |  |  |  |  |

|              |                                                                                                |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

| bit 15-14    | Unimplemen                                                                                     | nted: Read as '0'                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 13       | PMPIF: Para                                                                                    | llel Master Port I                                                                                     | nterrupt Flag | Status bit        |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has occu                                                                                       |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has not o                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 12-10    | •                                                                                              | nted: Read as '0'                                                                                      |               |                   | •••             |                 |        |  |  |  |  |

| bit 9        | •                                                                                              | <b>OC5IF:</b> Output Compare Channel 5 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |               |                   |                 |                 |        |  |  |  |  |

|              | •                                                                                              | request has occurrequest has not o                                                                     |               |                   |                 |                 |        |  |  |  |  |

| bit 8        | -                                                                                              | nted: Read as '0'                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 7        | -                                                                                              | Capture Channel                                                                                        |               | lag Status bit    |                 |                 |        |  |  |  |  |

|              | 1 = Interrupt request has occurred                                                             |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has not o                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 6        | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                       |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has occu<br>request has not o                                                                  |               |                   |                 |                 |        |  |  |  |  |

| bit 5        | •                                                                                              | •                                                                                                      |               | lag Status hit    |                 |                 |        |  |  |  |  |

| DIL J        | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has not o                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 4-2      | Unimplemen                                                                                     | nted: Read as '0'                                                                                      | 1             |                   |                 |                 |        |  |  |  |  |

| bit 1        | SPI2IF: SPI2 Event Interrupt Flag Status bit                                                   |                                                                                                        |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has occu                                                                                       |               |                   |                 |                 |        |  |  |  |  |

|              | -                                                                                              | request has not o                                                                                      |               |                   |                 |                 |        |  |  |  |  |

| bit 0        |                                                                                                | SPF2IF: SPI2 Fault Interrupt Flag Status bit                                                           |               |                   |                 |                 |        |  |  |  |  |

|              |                                                                                                | request has occu                                                                                       |               |                   |                 |                 |        |  |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0          | U-0                                                                                  | R/W-0                             | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------|-----------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

|              | _                                                                                    | AD1IE                             | U1TXIE           | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |  |  |  |  |

| bit 15       |                                                                                      |                                   |                  | •                 |                  |                 | bit    |  |  |  |  |

| R/W-0        | R/W-0                                                                                | R/W-0                             | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IE         | OC2IE                                                                                | IC2IE                             | _                | T1IE              | OC1IE            | IC1IE           | INTOIE |  |  |  |  |

| bit 7        |                                                                                      |                                   |                  |                   |                  |                 | bit    |  |  |  |  |

| Legend:      |                                                                                      |                                   |                  |                   |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                                                               | W = Writable                      | bit              | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value a | t POR                                                                                | '1' = Bit is set                  |                  | '0' = Bit is clea |                  | x = Bit is unkn | own    |  |  |  |  |

| bit 15-14    | Unimplemer                                                                           | nted: Read as '                   | 0'               |                   |                  |                 |        |  |  |  |  |

| bit 13       | AD1IE: A/D                                                                           | Conversion Cor                    | nplete Interrupt | t Enable bit      |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |

| bit 12       | -                                                                                    | RT1 Transmitte                    |                  | ole bit           |                  |                 |        |  |  |  |  |

|              | 1 = Interrupt                                                                        | request enable                    | d                |                   |                  |                 |        |  |  |  |  |

|              | 0 = Interrupt                                                                        | request not ena                   | abled            |                   |                  |                 |        |  |  |  |  |

| bit 11       |                                                                                      | RT1 Receiver li                   |                  | bit               |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable                    |                  |                   |                  |                 |        |  |  |  |  |

| bit 10       |                                                                                      | request not ena                   |                  | -<br>             |                  |                 |        |  |  |  |  |

|              | SPI1IE: SPI1 Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled |                                   |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 9        | SPF1IE: SPI1 Fault Interrupt Enable bit                                              |                                   |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |

| bit 8        |                                                                                      | Interrupt Enab                    |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable                    |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 7        |                                                                                      | Interrupt Enab                    |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |

| bit 6        |                                                                                      | ut Compare Ch                     |                  | ot Enable bit     |                  |                 |        |  |  |  |  |

|              | •                                                                                    | request enable                    |                  |                   |                  |                 |        |  |  |  |  |

|              | 0 = Interrupt request not enabled                                                    |                                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 5        | IC2IE: Input                                                                         | Capture Chann                     | el 2 Interrupt E | nable bit         |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable                    |                  |                   |                  |                 |        |  |  |  |  |

|              | -                                                                                    | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 4        | -                                                                                    | nted: Read as '                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 3        |                                                                                      | Interrupt Enab<br>request enable  |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 2        | OC1IE: Outp                                                                          | ut Compare Ch                     | annel 1 Interru  | pt Enable bit     |                  |                 |        |  |  |  |  |

|              | 1 = Interrupt                                                                        | request enable                    | d                |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request not ena                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 1        | -                                                                                    | Capture Chann                     |                  | nable bit         |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable<br>request not ena |                  |                   |                  |                 |        |  |  |  |  |

| bit 0        |                                                                                      | rnal Interrupt 0                  |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      | request enable                    |                  |                   |                  |                 |        |  |  |  |  |

|              |                                                                                      |                                   |                  |                   |                  |                 |        |  |  |  |  |

### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0          | U-0                           | R/W-0                               | U-0           | U-0               | U-0              | U-0             | R/W-0 |  |  |  |

|--------------|-------------------------------|-------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|

| —            | —                             | CTMUIE                              | —             | —                 | —                | —               | LVDIE |  |  |  |

| bit 15       |                               |                                     |               |                   |                  |                 | bit 8 |  |  |  |

|              |                               |                                     |               |                   |                  |                 |       |  |  |  |

| U-0          | U-0                           | U-0                                 | U-0           | R/W-0             | R/W-0            | R/W-0           | U-0   |  |  |  |

| _            | _                             | —                                   | —             | CRCIE             | U2ERIE           | U1ERIE          | —     |  |  |  |

| bit 7        |                               |                                     |               |                   |                  |                 | bit 0 |  |  |  |

|              |                               |                                     |               |                   |                  |                 |       |  |  |  |

| Legend:      |                               |                                     |               |                   |                  |                 |       |  |  |  |

| R = Readab   | le bit                        | W = Writable b                      | it            | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value a | It POR                        | '1' = Bit is set                    |               | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |  |

|              |                               |                                     |               |                   |                  |                 |       |  |  |  |

| bit 15-14    | Unimplemen                    | nted: Read as '0                    | ,             |                   |                  |                 |       |  |  |  |

| bit 13       | CTMUIE: CT                    | MU Interrupt Ena                    | able bit      |                   |                  |                 |       |  |  |  |

|              |                               | request enabled<br>request not enat | bled          |                   |                  |                 |       |  |  |  |

| bit 12-9     | Unimplemen                    | ted: Read as '0                     | ,             |                   |                  |                 |       |  |  |  |

| bit 8        | LVDIE: Low-                   | Voltage Detect Ir                   | nterrupt Enab | ole bit           |                  |                 |       |  |  |  |

|              |                               | request enabled request not enabled | bled          |                   |                  |                 |       |  |  |  |

| bit 7-4      | -                             | ted: Read as '0                     |               |                   |                  |                 |       |  |  |  |

| bit 3        | CRCIE: CRC                    | Generator Inter                     | rupt Enable b | bit               |                  |                 |       |  |  |  |

|              |                               | request enabled<br>request not enat | bled          |                   |                  |                 |       |  |  |  |

| bit 2        | U2ERIE: UAI                   | RT2 Error Interru                   | pt Enable bit | t                 |                  |                 |       |  |  |  |

|              | 1 = Interrupt request enabled |                                     |               |                   |                  |                 |       |  |  |  |

|              | 0 = Interrupt                 | request not enat                    | oled          |                   |                  |                 |       |  |  |  |

| bit 1        |                               | RT1 Error Interru                   | pt Enable bit | t                 |                  |                 |       |  |  |  |

|              |                               | request enabled                     | lad           |                   |                  |                 |       |  |  |  |

| hit O        | •                             | request not enab                    |               |                   |                  |                 |       |  |  |  |

| bit 0        | Unimplemen                    | ted: Read as '0                     |               |                   |                  |                 |       |  |  |  |

### 9.2.4.3 Exiting Deep Sleep Mode

Deep Sleep mode exits on any one of the following events:

- POR event on VDD supply. If there is no DSBOR circuit to re-arm the VDD supply POR circuit, the external VDD supply must be lowered to the natural arming voltage of the POR circuit.

- DSWDT time-out. When the DSWDT timer times out, the device exits Deep Sleep.

- RTCC alarm (if RTCEN = 1).

- Assertion ('0') of the  $\overline{\text{MCLR}}$  pin.

- Assertion of the INT0 pin (if the interrupt was enabled before Deep Sleep mode was entered). The polarity configuration is used to determine the assertion level ('0' or '1') of the pin that will cause an exit from Deep Sleep mode. Exiting from Deep Sleep mode requires a change on the INT0 pin while in Deep Sleep mode.

### **Note:** Any interrupt pending when entering Deep Sleep mode is cleared.

Exiting Deep Sleep mode generally does not retain the state of the device and is equivalent to a Power-on Reset (POR) of the device. Exceptions to this include the RTCC (if present), which remains operational through the wake-up, the DSGPRx registers and the DSWDT bit.

Wake-up events that occur from the time Deep Sleep exits, until the time that the POR sequence completes, are ignored, and are not captured in the DSWAKE register.

The sequence for exiting Deep Sleep mode is:

- 1. After a wake-up event, the device exits Deep Sleep and performs a POR. The DSEN bit is cleared automatically. Code execution resumes at the Reset vector.

- To determine if the device exited Deep Sleep, read the Deep Sleep bit, DPSLP (RCON<10>). This bit will be set if there was an exit from Deep Sleep mode. If the bit is set, clear it.

- 3. Determine the wake-up source by reading the DSWAKE register.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCON<1>).

- If application context data has been saved, read it back from the DSGPR0 and DSGPR1 registers.

- 6. Clear the RELEASE bit (DSCON<0>).

### 9.2.4.4 Deep Sleep Wake-up Time

Since wake-up from Deep Sleep results in a POR, the wake-up time from Deep Sleep is the same as the device POR time. Also, because the internal regulator is turned off, the voltage on VCAP may drop depending on how long the device is asleep. If VCAP has dropped below 2V, then there will be additional wake-up time while the regulator charges VCAP.

Deep Sleep wake-up time is specified in **Section 28.0 "Electrical Characteristics**" as TDSWU. This specification indicates the worst-case wake-up time, including the full POR Reset time (including TPOR and TRST), as well as the time to fully charge a 10  $\mu$ F capacitor on VCAP which has discharged to 0V. Wake-up may be significantly faster if VCAP has not discharged.

### 9.2.4.5 Saving Context Data with the DSGPR0/DSGPR1 Registers

As exiting Deep Sleep mode causes a POR, most Special Function Registers reset to their default POR values. In addition, because VDDCORE power is not supplied in Deep Sleep mode, information in data RAM may be lost when exiting this mode.

Applications which require critical data to be saved prior to Deep Sleep may use the Deep Sleep General Purpose registers, DSGPR0 and DSGPR1, or data EEPROM (if available). Unlike other SFRs, the contents of these registers are preserved while the device is in Deep Sleep mode. After exiting Deep Sleep, software can restore the data by reading the registers and clearing the RELEASE bit (DSCON<0>).

### 9.2.4.6 I/O Pins During Deep Sleep

During Deep Sleep, the general purpose I/O pins retain their previous states and the Secondary Oscillator (SOSC) will remain running, if enabled. Pins that are configured as inputs (TRIS bit is set) prior to entry into Deep Sleep remain high-impedance during Deep Sleep. Pins that are configured as outputs (TRIS bit is clear) prior to entry into Deep Sleep remain as output pins during Deep Sleep. While in this mode, they continue to drive the output level determined by their corresponding LAT bit at the time of entry into Deep Sleep. NOTES:

| U-0                                | U-0         | U-0             | R/W-0             | R/W-0                              | R/W-0              | R/W-0  | R/W-0  |  |

|------------------------------------|-------------|-----------------|-------------------|------------------------------------|--------------------|--------|--------|--|

| —                                  | —           | —               | RP25R4            | RP25R3                             | RP25R2             | RP25R1 | RP25R0 |  |

| bit 15                             |             |                 |                   |                                    |                    |        | bit 8  |  |

|                                    |             |                 |                   |                                    |                    |        |        |  |

| U-0                                | U-0         | U-0             | R/W-0             | R/W-0                              | R/W-0              | R/W-0  | R/W-0  |  |

| —                                  | —           | —               | RP24R4            | RP24R3                             | RP24R2             | RP24R1 | RP24R0 |  |

| bit 7                              |             |                 |                   |                                    |                    |        | bit 0  |  |

|                                    |             |                 |                   |                                    |                    |        |        |  |

| Legend:                            |             |                 |                   |                                    |                    |        |        |  |

| R = Readable                       | bit         | W = Writable    | bit               | U = Unimplemented bit, read as '0' |                    |        |        |  |

| -n = Value at POR '1' = Bit is set |             |                 | '0' = Bit is clea | ared                               | x = Bit is unknown |        |        |  |

|                                    |             |                 |                   |                                    |                    |        |        |  |

| bit 15-13                          | Unimplement | ted: Read as 'd | )'                |                                    |                    |        |        |  |

| bit 12-8                           | RP25R<5:0>: | RP25 Output     | Pin Mapping b     | its                                |                    |        |        |  |

|                                    |             |                 |                   |                                    |                    |        |        |  |

### REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

Peripheral output number n is assigned to pin, RP25 (see Table 10-3 for peripheral function numbers).

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP24R<5:0>:** RP24 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP24 (see Table 10-3 for peripheral function numbers).

Note 1: This register is unimplemented in 28-pin devices; all bits read as '0'.

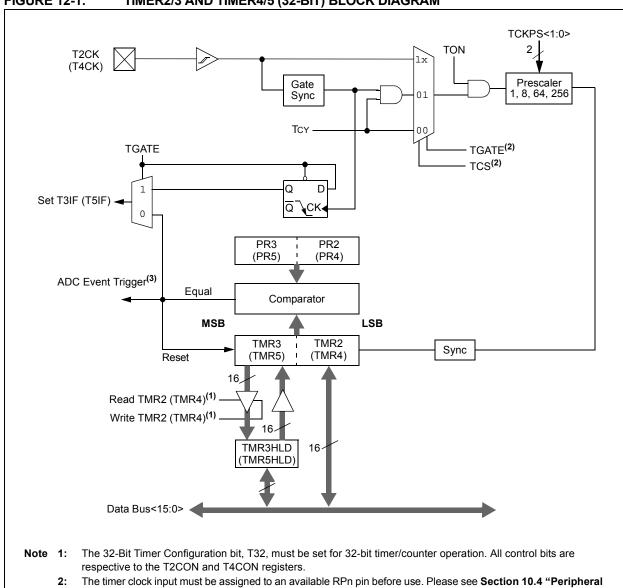

#### **FIGURE 12-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

Pin Select (PPS)" for more information.

3: The ADC event trigger is available only on Timer 2/3 in 32-bit mode and Timer 3 in 16-bit mode.

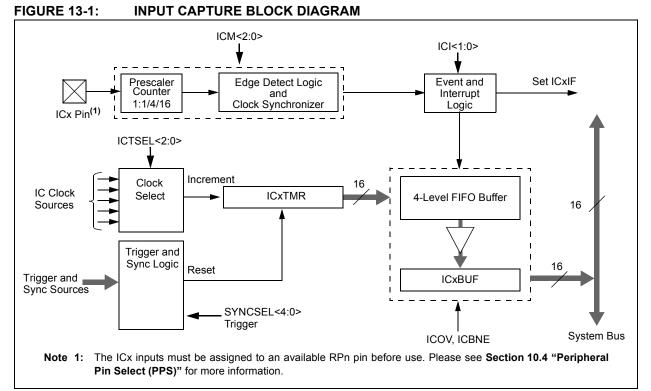

### 13.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 34. "Input Capture with Dedicated Timer" (DS39722).

Devices in the PIC24FJ64GA104 family all feature 5 independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 20 user-selectable trigger/sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 13-1) and ICxCON2 (Register 13-2). A general block diagram of the module is shown in Figure 13-1.

### 13.1 General Operating Modes

#### 13.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the input capture module operates in a free-running mode. The internal 16-bit counter ICxTMR counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSEL bits to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSEL bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSEL bits determine the sync/trigger source.

When the SYNCSEL bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This OC module<sup>(1)</sup> 11110 = Reserved 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1 01010 = Input Capture 5<sup>(2)</sup> 01001 = Reserved 01000 = Reserved 00111 = Reserved 00110 = Reserved 00101 = Output Compare 5<sup>(1)</sup> 00100 = Output Compare  $4^{(1)}$ 00011 = Output Compare 3<sup>(1)</sup> 00010 = Output Compare 2<sup>(1)</sup> 00001 = Output Compare 1<sup>(1)</sup> 00000 = Not synchronized to any other module

- Note 1: Do not use an OC module as its own trigger source, either by selecting this mode or another equivalent SYNCSEL setting.

- 2: Use these inputs as trigger sources only and never as sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCM bits (OCxCON1<1:0>) = 001.

### 21.0 10-BIT HIGH-SPEED A/D CONVERTER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 17. "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- Conversion speeds of up to 500 ksps

- 13 analog input pins

- External voltage reference input pins

- Internal band gap reference inputs

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- Selectable Buffer Fill modes

- · Four result alignment options

- Operation during CPU Sleep and Idle modes

On all PIC24FJ64GA104 family devices, the 10-bit A/D Converter has 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is shown in Figure 21-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- Configure port pins as analog inputs and/or select band gap reference inputs (AD1PCFGL<15:0> and AD1PCFGH<1:0>).

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

### 25.5.2 CODE SEGMENT PROTECTION

In addition to global General Segment protection, a separate subrange of the program memory space can be individually protected against writes and erases. This area can be used for many purposes where a separate block of erase and write-protected code is needed, such as bootloader applications. Unlike common boot block implementations, the specially protected segment in the PIC24FJ64GA104 family devices can be located by the user anywhere in the program space and configured in a wide range of sizes.

Code segment protection provides an added level of protection to a designated area of program memory, by disabling the NVM safety interlock, whenever a write or erase address falls within a specified range. It does not override General Segment protection controlled by the GCP or GWRP bits. For example, if GCP and GWRP are enabled, enabling segmented code protection for the bottom half of program memory does not undo General Segment protection for the top half.

The size and type of protection for the segmented code range are configured by the WPFPx, WPEND, WPCFG and WPDIS bits in Configuration Word 3. Code segment protection is enabled by programming the WPDIS bit (= 0). The WPFP bits specify the size of the segment to be protected by specifying the 512-word code page that is the start or end of the protected segment. The specified region is inclusive, therefore, this page will also be protected.

The WPEND bit determines if the protected segment uses the top or bottom of the program space as a boundary. Programming WPEND (= 0) sets the bottom of program memory (000000h) as the lower boundary of the protected segment. Leaving WPEND unprogrammed (= 1) protects the specified page through the last page of implemented program memory, including the Configuration Word locations. A separate bit, WPCFG, is used to independently protect the last page of program space, including the Flash Configuration Words. Programming WPCFG (= 0) protects the last page, regardless of the other bit settings. This may be useful in circumstances where write protection is needed for both a code segment in the bottom of memory, as well as the Flash Configuration Words.

The various options for segment code protection are shown in Table 25-2.

### 25.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes, or reads in two ways. The primary protection method is the same as that of the RP registers – shadow registers contain a complimentary value which is constantly compared with the actual value.

To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. When the GCP bit is set, the source data for device configuration is also protected as a consequence. Even if General Segment protection is not enabled, the device configuration can be protected by using the appropriate code cement protection setting.

| Segmen | Segment Configuration Bits |       | Segment Configuration Bits<br>Write/Erase Protection of Code Segment                                                                                                                |  | Write/Erace Protection of Code Segment |

|--------|----------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------|

| WPDIS  | WPEND                      | WPCFG | Write/Erase Protection of Code Segment                                                                                                                                              |  |                                        |

| 1      | x                          | 1     | No additional protection enabled; all program memory protection is configured by GCP and GWRP                                                                                       |  |                                        |

| 1      | x                          | 0     | Last code page protected, including Flash Configuration Words                                                                                                                       |  |                                        |

| 0      | 1                          | 0     | Addresses from the first address of code page are defined by WPFP<5:0> through the end of implemented program memory (inclusive) are protected, including Flash Configuration Words |  |                                        |

| 0      | 0                          | 0     | Address, 000000h, through the last address of code page, defined by WPFP<5:0> (inclusive) is protected                                                                              |  |                                        |

| 0      | 1                          | 1     | Addresses from first address of code page, defined by WPFP<5:0> through the end of implemented program memory (inclusive), are protected, including Flash Configuration Words       |  |                                        |

| 0      | 0                          | 1     | Addresses from first address of code page, defined by WPFP<5:0> through the end of implemented program memory (inclusive), are protected                                            |  |                                        |

### TABLE 25-2: SEGMENT CODE PROTECTION CONFIGURATION OPTIONS

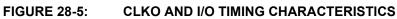

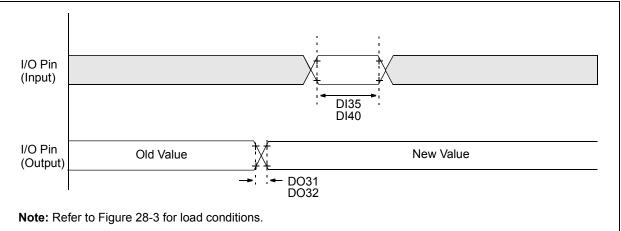

### TABLE 28-20: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |      |                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |            |

|--------------------|------|---------------------------------------|------------------------------------------------------|--------------------|-----|-------|------------|

| Param<br>No.       | Sym  | Characteristic                        | Min                                                  | Typ <sup>(1)</sup> | Мах | Units | Conditions |

| DO31               | TioR | Port Output Rise Time                 | _                                                    | 10                 | 25  | ns    |            |

| DO32               | TIOF | Port Output Fall Time                 | _                                                    | 10                 | 25  | ns    |            |

| DI35               | Tinp | INTx pin High or Low<br>Time (output) | 20                                                   | —                  | _   | ns    |            |

| DI40               | Trbp | CNx High or Low Time<br>(input)       | 2                                                    | —                  |     | Тсү   |            |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

### TABLE 28-21: RESET, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS