Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga102t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|---------------|------------------------------|

|               |                              |

| U-0     | U-0 | U-0           | U-0 | U-0                 | U-0   | U-0 | U-0   |

|---------|-----|---------------|-----|---------------------|-------|-----|-------|

|         | —   | _             | —   | —                   | —     | —   | —     |

| bit 15  |     |               |     |                     |       | •   | bit 8 |

|         |     |               |     |                     |       |     |       |

| U-0     | U-0 | U-0           | U-0 | R/C-0               | R/W-0 | U-0 | U-0   |

| _       | _   |               | —   | IPL3 <sup>(1)</sup> | PSV   | —   | _     |

| bit 7   |     |               |     |                     |       | •   | bit 0 |

|         |     |               |     |                     |       |     |       |

| Legend. |     | C = Clearable | hit |                     |       |     |       |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space visible in data space                                                                                       |

|          | 0 = Program space not visible in data space                                                                                   |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

## TABLE 4-8: OUTPUT COMPARE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8       | Bit 7        | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|---------|---------|---------|--------|-------------|--------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1   | 0190 | _      | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2        | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2   | 0192 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS     | 0194 |        |        |          |         |         |         | Οι     | utput Compa | are 1 Second | lary Register |        |          |          |          |          |          | 0000          |

| OC1R      | 0196 |        |        |          |         |         |         |        | Output C    | Compare 1 R  | egister       |        |          |          |          |          |          | 0000          |

| OC1TMR    | 0198 |        |        |          |         |         |         |        | Timer       | Value 1 Reg  | ister         |        |          |          |          |          |          | xxxx          |

| OC2CON1   | 019A | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2        | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2   | 019C | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS     | 019E |        |        |          |         |         |         | Οι     | utput Compa | are 2 Second | lary Register |        |          |          |          |          |          | 0000          |

| OC2R      | 01A0 |        |        |          |         |         |         |        | Output C    | Compare 2 R  | egister       |        |          |          |          |          |          | 0000          |

| OC2TMR    | 01A2 |        |        |          |         |         |         |        | Timer       | Value 2 Reg  | ister         |        |          |          |          |          |          | xxxx          |

| OC3CON1   | 01A4 | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2        | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2   | 01A6 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | -       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS     | 01A8 |        |        |          |         |         |         | Οι     | utput Compa | are 3 Second | lary Register |        |          |          |          |          |          | 0000          |

| OC3R      | 01AA |        |        |          |         |         |         |        | Output C    | Compare 3 R  | egister       |        |          |          |          |          |          | 0000          |

| OC3TMR    | 01AC |        |        |          |         |         |         |        | Timer       | Value 3 Reg  | ister         |        |          |          |          |          |          | xxxx          |

| OC4CON1   | 01AE |        | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2        | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2   | 01B0 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS     | 01B2 |        |        |          |         |         |         | Οι     | utput Compa | are 4 Second | lary Register |        |          |          |          |          |          | 0000          |

| OC4R      | 01B4 |        |        |          |         |         |         |        | Output C    | Compare 4 R  | egister       |        |          |          |          |          |          | 0000          |

| OC4TMR    | 01B6 |        |        |          |         |         |         |        | Timer       | Value 4 Reg  | ister         |        |          |          |          |          |          | xxxx          |

| OC5CON1   | 01B8 | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2        | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2   | 01BA | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS     | 01BC |        |        |          |         |         |         | Ou     | utput Compa | are 5 Second | lary Register |        |          |          |          |          |          | 0000          |

| OC5R      | 01BE |        |        |          |         |         |         |        | Output C    | Compare 5 R  | egister       |        |          |          |          |          |          | 0000          |

| OC5TMR    | 01C0 |        |        |          |         |         |         |        | Timer       | Value 5 Reg  | ister         |        |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

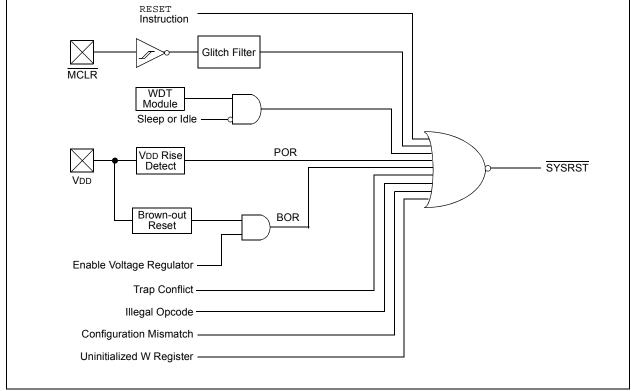

#### 6.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 7. "Reset" (DS39712).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

FIGURE 6-1:

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Refer to the specific peripheral or CPU Note: section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A Power-on Reset will clear all bits, except for the BOR and POR bits (RCON<1:0>), which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

RESET SYSTEM BLOCK DIAGRAM

## PIC24FJ64GA104 FAMILY

| U-0           | R/W-0           | U-0                             | U-0              | U-0               | U-0              | U-0             | U-0   |

|---------------|-----------------|---------------------------------|------------------|-------------------|------------------|-----------------|-------|

|               | RTCIE           |                                 | _                |                   | _                | —               | _     |

| bit 15        |                 |                                 |                  |                   |                  |                 | bit 8 |

|               |                 |                                 |                  |                   |                  |                 |       |

| U-0           | U-0             | U-0                             | U-0              | U-0               | R/W-0            | R/W-0           | U-0   |

| —             | —               | —                               | —                | —                 | MI2C2IE          | SI2C2IE         |       |

| bit 7         |                 |                                 |                  |                   |                  |                 | bit 0 |

|               |                 |                                 |                  |                   |                  |                 |       |

| Legend:       |                 |                                 |                  |                   |                  |                 |       |

| R = Readable  | e bit           | W = Writable                    | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at | POR             | '1' = Bit is set                |                  | '0' = Bit is clea | ared             | x = Bit is unkn | iown  |

|               |                 |                                 |                  |                   |                  |                 |       |

| bit 15        | Unimplemen      | ted: Read as '                  | כי               |                   |                  |                 |       |

| bit 14        | RTCIE: Real-    | Time Clock/Ca                   | lendar Interrup  | t Enable bit      |                  |                 |       |

|               |                 | equest enable                   |                  |                   |                  |                 |       |

|               | 0 = Interrupt r | equest not ena                  | bled             |                   |                  |                 |       |

| bit 13-3      | Unimplemen      | ted: Read as '                  | כ'               |                   |                  |                 |       |

| bit 2         | MI2C2IE: Mas    | ster I2C2 Even                  | t Interrupt Enal | ble bit           |                  |                 |       |

|               |                 | equest enable                   |                  |                   |                  |                 |       |

|               | •               | equest not ena                  |                  |                   |                  |                 |       |

| bit 1         |                 | ve I2C2 Event I                 | •                | e bit             |                  |                 |       |

|               |                 | equest enable<br>equest not ena |                  |                   |                  |                 |       |

| bit 0         |                 | ted: Read as '                  |                  |                   |                  |                 |       |

|               |                 |                                 |                  |                   |                  |                 |       |

#### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

# PIC24FJ64GA104 FAMILY

#### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|-------|--------|--------|--------|-----|-----|-----|-------|

| —     | PMPIP2 | PMPIP1 | PMPIP0 | _   | —   | —   | —     |

| bit 7 |        |        |        |     |     |     | bit 0 |

## Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-7 Unimplemented: Read as '0'

| bit 6-4 | <pre>PMPIP&lt;2:0&gt;: Parallel Master Port Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)</pre> |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

|         | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                  |

| hit 2 0 | Unimplemented, Dood op (o)                                                                                                           |

bit 3-0 Unimplemented: Read as '0'

٦

| U-0                   | U-0                                                                                                                                | U-0                                                                                                                                                                                 | U-0                                                                                      | U-0                         | R/W-1            | R/W-0           | R/W-0    |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------|----------|

| _                     |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             | MI2C2IP2         | MI2C2IP1        | MI2C2IP0 |

| bit 15                | ·                                                                                                                                  |                                                                                                                                                                                     |                                                                                          |                             |                  |                 | bit 8    |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| U-0                   | R/W-1                                                                                                                              | R/W-0                                                                                                                                                                               | R/W-0                                                                                    | U-0                         | U-0              | U-0             | U-0      |

| _                     | SI2C2IP2                                                                                                                           | SI2C2IP1                                                                                                                                                                            | SI2C2IP0                                                                                 | —                           | —                | —               | —        |

| bit 7                 |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 | bit 0    |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| Legend:               |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| R = Readab            | le bit                                                                                                                             | W = Writable                                                                                                                                                                        | bit                                                                                      | U = Unimple                 | mented bit, read | 1 as '0'        |          |

| -n = Value a          | It POR                                                                                                                             | '1' = Bit is set                                                                                                                                                                    |                                                                                          | '0' = Bit is cle            | eared            | x = Bit is unkr | nown     |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| bit 15-11             | Unimplemen                                                                                                                         | ted: Read as '                                                                                                                                                                      | ٥'                                                                                       |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

| bit 15-11<br>bit 10-8 | MI2C2IP<2:0                                                                                                                        |                                                                                                                                                                                     | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0<br>111 = Interrup                                                                                                      | >: Master I2C2<br>ot is priority 7 (I                                                                                                                                               | Event Interrup<br>highest priority                                                       |                             |                  |                 |          |

|                       | MI2C2IP<2:0<br>111 = Interrup<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1                                                                                                                           | Event Interrup<br>highest priority<br>abled                                              |                             |                  |                 |          |

| bit 10-8              | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen                                                    | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis                                                                                                       | Event Interrup<br>highest priority<br>abled                                              | interrupt)                  |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br><b>ted:</b> Read as '(                                                                             | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br>ted: Read as '(<br>>: Slave I2C2 E                                                                 | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br>ted: Read as '(<br>>: Slave I2C2 E                                                                 | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | <ul> <li>Master I2C2</li> <li>tis priority 7 (I</li> <li>tis priority 1</li> <li>source is dis</li> <li>ted: Read as '(</li> <li>Slave I2C2 E</li> <li>tis priority 7 (I</li> </ul> | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup | <ul> <li>Master I2C2</li> <li>tis priority 7 (I</li> <li>tis priority 1</li> <li>source is dis</li> <li>ted: Read as '(</li> <li>Slave I2C2 E</li> <li>tis priority 7 (I</li> </ul> | Event Interrup<br>highest priority<br>abled<br>o'<br>Event Interrupt<br>highest priority | interrupt)<br>Priority bits |                  |                 |          |

## REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

## 7.4 Interrupt Setup Procedures

## 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to priority level 4. |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

## 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

## 9.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 39. "Power-Saving Features         |

|       | with Deep Sleep" (DS39727).                |

The PIC24FJ64GA104 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep, Idle and Deep Sleep modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

#### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals except RTCC and DSWDT. It also freezes I/O states and removes power to SRAM and Flash memory. The assembly syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

| EXAMPLE 9-1: | <b>PWRSAV INSTRUCTION SYNTAX</b> |

|--------------|----------------------------------|

|              |                                  |

| PWRSAV | #SLEEP_MODE  | ; Put the device into SLEEP mode      |

|--------|--------------|---------------------------------------|

| PWRSAV | #IDLE_MODE   | ; Put the device into IDLE mode       |

| BSET   | DSCON, #DSEN | ; Enable Deep Sleep                   |

| PWRSAV | #SLEEP_MODE  | ; Put the device into Deep SLEEP mode |

#### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains up to two 5-bit fields, with each field being associated with one RPn pin (see Register 10-15 through Register 10-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-3).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| TABLE 10-3  | SELECTABLE OUTPUT SOURCES  | (MAPS FUNCTION TO OUTPUT) |

|-------------|----------------------------|---------------------------|

| TADLE 10-J. | SELECTABLE COTT OF SCORCES |                           |

| Output Function Number <sup>(1)</sup> | Function             | Output Name              |

|---------------------------------------|----------------------|--------------------------|

| 0                                     | NULL <sup>(2)</sup>  | Null                     |

| 1                                     | C1OUT                | Comparator 1 Output      |

| 2                                     | C2OUT                | Comparator 2 Output      |

| 3                                     | U1TX                 | UART1 Transmit           |

| 4                                     | U1RTS <sup>(3)</sup> | UART1 Request To Send    |

| 5                                     | U2TX                 | UART2 Transmit           |

| 6                                     | U2RTS <sup>(3)</sup> | UART2 Request To Send    |

| 7                                     | SDO1                 | SPI1 Data Output         |

| 8                                     | SCK1OUT              | SPI1 Clock Output        |

| 9                                     | SS1OUT               | SPI1 Slave Select Output |

| 10                                    | SDO2                 | SPI2 Data Output         |

| 11                                    | SCK2OUT              | SPI2 Clock Output        |

| 12                                    | SS2OUT               | SPI2 Slave Select Output |

| 18                                    | OC1                  | Output Compare 1         |

| 19                                    | OC2                  | Output Compare 2         |

| 20                                    | OC3                  | Output Compare 3         |

| 21                                    | OC4                  | Output Compare 4         |

| 22                                    | OC5                  | Output Compare 5         |

| 23-28                                 | (unused)             | NC                       |

| 29                                    | CTPLS                | CTMU Output Pulse        |

| 30                                    | C3OUT                | Comparator 3 Output      |

| 31                                    | (unused)             | NC                       |

**Note 1:** Setting the RPORx register with the listed value assigns that output function to the associated RPn pin.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

3: IrDA<sup>®</sup> BCLK functionality uses this output.

## PIC24FJ64GA104 FAMILY

#### REGISTER 10-7: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| 11.0         | 11.0  | 11.0         | 11.0  | 11.0         | 11.0             | 11.0     | 11.0  |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

| _            | _     | _            |       | _            | —                |          | —     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| U-0          | U-0   | U-0          | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|              |       | _            | IC5R4 | IC5R3        | IC5R2            | IC5R1    | IC5R0 |

| bit 7        |       |              |       |              |                  | bit 0    |       |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplem | nented bit, read | l as '0' |       |

-n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown)

bit 15-5 Unimplemented: Read as '0'

bit 4-0 IC5R<4:0>: Assign Input Capture 5 (IC5) to Corresponding RPn or RPIn Pin bits

#### REGISTER 10-8: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                                | U-0 | U-0                                    | R/W-1             | R/W-1    | R/W-1           | R/W-1  | R/W-1  |

|------------------------------------|-----|----------------------------------------|-------------------|----------|-----------------|--------|--------|

| —                                  | —   | —                                      | OCFBR4            | OCFBR3   | OCFBR2          | OCFBR1 | OCFBR0 |

| bit 15                             |     |                                        |                   |          |                 |        | bit 8  |

|                                    |     |                                        |                   |          |                 |        |        |

| U-0                                | U-0 | U-0                                    | R/W-1             | R/W-1    | R/W-1           | R/W-1  | R/W-1  |

| —                                  | —   | —                                      | OCFAR4            | OCFAR3   | OCFAR2          | OCFAR1 | OCFAR0 |

| bit 7 bit                          |     |                                        |                   |          |                 |        | bit 0  |

|                                    |     |                                        |                   |          |                 |        |        |

| Legend:                            |     |                                        |                   |          |                 |        |        |

| R = Readable bit W = Writable b    |     | Dit U = Unimplemented bit, read as '0' |                   | l as '0' |                 |        |        |

| -n = Value at POR '1' = Bit is set |     |                                        | '0' = Bit is clea | ared     | x = Bit is unkr | iown   |        |

|                                    |     |                                        |                   |          |                 |        |        |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 OCFBR<4:0>: Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits

#### REGISTER 10-9: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   |     | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 12-8  | U1CTSR<4:0>: Assign UART1 Clear to Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                            |

| bit 4-0   | U1RXR<4:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

## REGISTER 10-10: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1 R/W-1 |        | R/W-1  |

|-------|-----|-----|--------|--------|-------------|--------|--------|

| —     | —   | —   | U2RXR4 | U2RXR3 | U2RXR2      | U2RXR1 | U2RXR0 |

| bit 7 |     |     |        |        |             |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 U2CTSR<4:0>: Assign UART2 Clear to Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 U2RXR<4:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

#### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: initialize OCx pin low, toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: initialize OCx pin low, toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: compare events continuously toggle OCx pin

- 010 = Single Compare Single-Shot mode: initialize OCx pin high, compare event forces OCx pin low

- 001 = Single Compare Single-Shot mode: initialize OCx pin low, compare event forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

- **2:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

#### REGISTER 19-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

## 21.0 10-BIT HIGH-SPEED A/D CONVERTER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 17. "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- Conversion speeds of up to 500 ksps

- 13 analog input pins

- External voltage reference input pins

- Internal band gap reference inputs

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- Selectable Buffer Fill modes

- · Four result alignment options

- Operation during CPU Sleep and Idle modes

On all PIC24FJ64GA104 family devices, the 10-bit A/D Converter has 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is shown in Figure 21-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- Configure port pins as analog inputs and/or select band gap reference inputs (AD1PCFGL<15:0> and AD1PCFGH<1:0>).

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

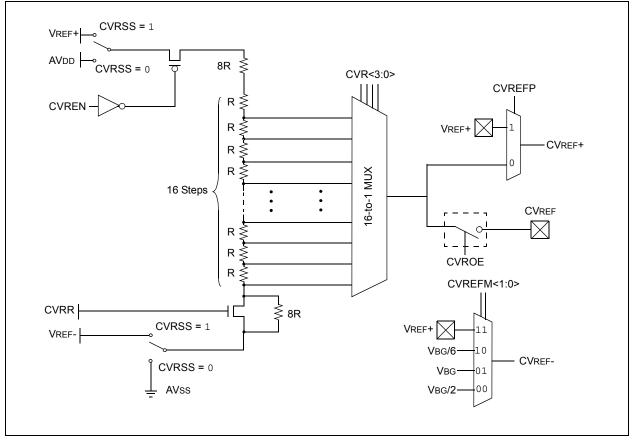

## 23.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 20. "Comparator Voltage Reference Module" (DS39709).

#### 23.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides two ranges of output

voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

## FIGURE 23-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 25.5.2 CODE SEGMENT PROTECTION

In addition to global General Segment protection, a separate subrange of the program memory space can be individually protected against writes and erases. This area can be used for many purposes where a separate block of erase and write-protected code is needed, such as bootloader applications. Unlike common boot block implementations, the specially protected segment in the PIC24FJ64GA104 family devices can be located by the user anywhere in the program space and configured in a wide range of sizes.

Code segment protection provides an added level of protection to a designated area of program memory, by disabling the NVM safety interlock, whenever a write or erase address falls within a specified range. It does not override General Segment protection controlled by the GCP or GWRP bits. For example, if GCP and GWRP are enabled, enabling segmented code protection for the bottom half of program memory does not undo General Segment protection for the top half.

The size and type of protection for the segmented code range are configured by the WPFPx, WPEND, WPCFG and WPDIS bits in Configuration Word 3. Code segment protection is enabled by programming the WPDIS bit (= 0). The WPFP bits specify the size of the segment to be protected by specifying the 512-word code page that is the start or end of the protected segment. The specified region is inclusive, therefore, this page will also be protected.

The WPEND bit determines if the protected segment uses the top or bottom of the program space as a boundary. Programming WPEND (= 0) sets the bottom of program memory (000000h) as the lower boundary of the protected segment. Leaving WPEND unprogrammed (= 1) protects the specified page through the last page of implemented program memory, including the Configuration Word locations. A separate bit, WPCFG, is used to independently protect the last page of program space, including the Flash Configuration Words. Programming WPCFG (= 0) protects the last page, regardless of the other bit settings. This may be useful in circumstances where write protection is needed for both a code segment in the bottom of memory, as well as the Flash Configuration Words.

The various options for segment code protection are shown in Table 25-2.

#### 25.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes, or reads in two ways. The primary protection method is the same as that of the RP registers – shadow registers contain a complimentary value which is constantly compared with the actual value.

To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. When the GCP bit is set, the source data for device configuration is also protected as a consequence. Even if General Segment protection is not enabled, the device configuration can be protected by using the appropriate code cement protection setting.

| Segmen | Segment Configuration Bits |       | Write/Erase Protection of Code Segment                                                                                                                                              |

|--------|----------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WPDIS  | WPEND                      | WPCFG | Write/Erase Protection of Code Segment                                                                                                                                              |

| 1      | x                          | 1     | No additional protection enabled; all program memory protection is configured by GCP and GWRP                                                                                       |

| 1      | x                          | 0     | Last code page protected, including Flash Configuration Words                                                                                                                       |

| 0      | 1                          | 0     | Addresses from the first address of code page are defined by WPFP<5:0> through the end of implemented program memory (inclusive) are protected, including Flash Configuration Words |

| 0      | 0                          | 0     | Address, 000000h, through the last address of code page, defined by WPFP<5:0> (inclusive) is protected                                                                              |

| 0      | 1                          | 1     | Addresses from first address of code page, defined by WPFP<5:0> through the end of implemented program memory (inclusive), are protected, including Flash Configuration Words       |

| 0      | 0                          | 1     | Addresses from first address of code page, defined by WPFP<5:0> through the end of implemented program memory (inclusive), are protected                                            |

## TABLE 25-2: SEGMENT CODE PROTECTION CONFIGURATION OPTIONS

| AC CHARACTERISTICS |       |                                  | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |                    |          |            |                                                                                                                           |  |

|--------------------|-------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup>    | Min                                                                                                                                                                                                                                                                        | Тур <sup>(2)</sup> | Max      | Units      | Conditions                                                                                                                |  |

| OS50               | Fplli | PLL Input Frequency<br>Range     | 3<br>3                                                                                                                                                                                                                                                                     | _                  | 8<br>6   | MHz<br>MHz | ECPLL, HSPLL, XTPLL<br>modes, -40°C $\leq$ TA $\leq$ +85°C<br>ECPLL, HSPLL, XTPLL<br>modes, -40°C $\leq$ TA $\leq$ +125°C |  |

| OS51               | Fsys  | PLL Output Frequency<br>Range    | 8<br>8                                                                                                                                                                                                                                                                     | _                  | 32<br>24 | MHz<br>MHz | $\begin{array}{l} -40^\circ C \leq T_A \leq +85^\circ C \\ -40^\circ C \leq T_A \leq +125^\circ C \end{array}$            |  |

| OS52               | Тгоск | PLL Start-up Time<br>(Lock Time) | -                                                                                                                                                                                                                                                                          | —                  | 2        | ms         |                                                                                                                           |  |

| OS53               | DCLK  | CLKO Stability (Jitter)          | -2                                                                                                                                                                                                                                                                         | 1                  | 2        | %          | Measured over 100 ms period                                                                                               |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 28-18: INTERNAL RC OSCILLATOR SPECIFICATIONS

|              |       |                               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |     |       |            |  |

|--------------|-------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------|--|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                      | Тур | Max | Units | Conditions |  |

|              | TFRC  | FRC Start-up Time             | _                                                                                                                                                                                                                                                                        | 15  | _   | μS    |            |  |

|              | TLPRC | LPRC Start-up Time            | —                                                                                                                                                                                                                                                                        | 500 | _   | μS    |            |  |

### TABLE 28-19: INTERNAL RC OSCILLATOR ACCURACY

|              |                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |               |     |       |                                                                            |  |

|--------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-------|----------------------------------------------------------------------------|--|

| Param<br>No. | Characteristic                        | Min                                                                                                                                                                                                                                                                      | Тур           | Max | Units | Conditions                                                                 |  |

| F20          | FRC Accuracy @ 8 MHz <sup>(1,3)</sup> | -1.25                                                                                                                                                                                                                                                                    | <u>+</u> 0.25 | 1.0 | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C, \ 3.0V \leq V\text{DD} \leq 3.6V$ |  |

| F21          | LPRC Accuracy @ 31 kHz <sup>(2)</sup> | -15                                                                                                                                                                                                                                                                      | _             | 15  | %     | $-40^{\circ}C \leq Ta \leq +85^{\circ}C, \ 3.0V \leq V\text{DD} \leq 3.6V$ |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. OSCTUN bits can be used to compensate for temperature drift.

2: Change of LPRC frequency as VDD changes.

**3:** To achieve this accuracy, physical stress applied to the microcontroller package (ex: by flexing the PCB) must be kept to a minimum.

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

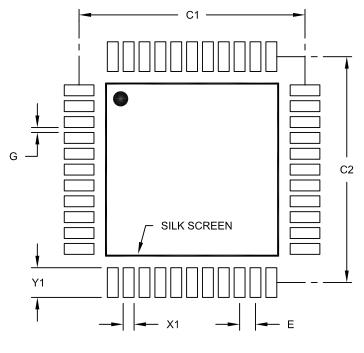

**RECOMMENDED LAND PATTERN**

|                          | Units | MILLIM   |       |      |

|--------------------------|-------|----------|-------|------|

| Dimension Limits         |       | MIN      | NOM   | MAX  |

| Contact Pitch            | E     | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1    |          | 11.40 |      |

| Contact Pad Spacing      | C2    |          | 11.40 |      |

| Contact Pad Width (X44)  | X1    |          |       | 0.55 |

| Contact Pad Length (X44) | Y1    |          |       | 1.50 |

| Distance Between Pads    | G     | 0.25     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A

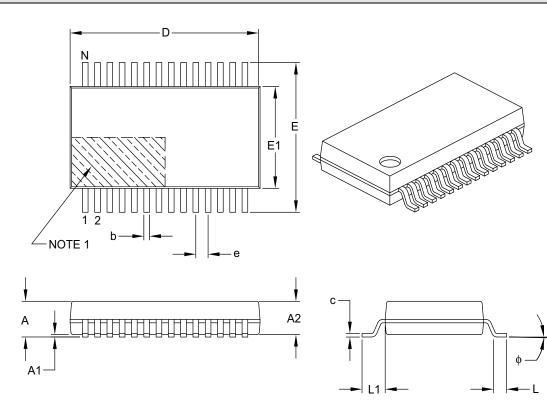

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |       |       |  |

|--------------------------|-----------|-------------|-------|-------|--|

| Dimensio                 | on Limits | MIN         | NOM   | MAX   |  |

| Number of Pins           | Ν         | 28          |       |       |  |

| Pitch                    | е         | 0.65 BSC    |       |       |  |

| Overall Height           | Α         | -           | -     | 2.00  |  |

| Molded Package Thickness | A2        | 1.65        | 1.75  | 1.85  |  |

| Standoff                 | A1        | 0.05        | -     | -     |  |

| Overall Width            | E         | 7.40        | 7.80  | 8.20  |  |

| Molded Package Width     | E1        | 5.00        | 5.30  | 5.60  |  |

| Overall Length           | D         | 9.90        | 10.20 | 10.50 |  |

| Foot Length              | L         | 0.55        | 0.75  | 0.95  |  |

| Footprint                | L1        | 1.25 REF    |       |       |  |

| Lead Thickness           | с         | 0.09        | -     | 0.25  |  |

| Foot Angle               | ф         | 0°          | 4°    | 8°    |  |

| Lead Width               | b         | 0.22        | _     | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**Santa Clara** Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

07/15/10