#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

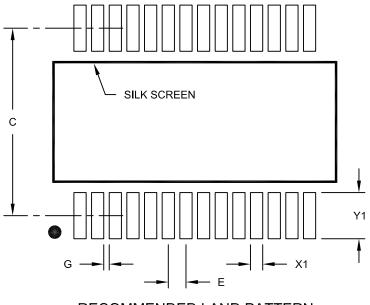

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga102t-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 CPU

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 2. "CPU" (DS39703).                |

The PIC24F CPU has a 16-bit (data), modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported either directly or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

#### 3.1 **Programmer's Model**

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory mapped.

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IADLE        | 4-3. | CFUC   |        | RE REGISTERS MAP |        |        |        |        |             |              |            |            |                |              |             |       |       |               |

|--------------|------|--------|--------|------------------|--------|--------|--------|--------|-------------|--------------|------------|------------|----------------|--------------|-------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13           | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6      | Bit 5      | Bit 4          | Bit 3        | Bit 2       | Bit 1 | Bit 0 | All<br>Resets |

| WREG0        | 0000 |        |        |                  |        |        |        |        | Working F   | Register 0   |            |            |                |              |             |       |       | 0000          |

| WREG1        | 0002 |        |        |                  |        |        |        |        | Working F   | Register 1   |            |            |                |              |             |       |       | 0000          |

| WREG2        | 0004 |        |        |                  |        |        |        |        | Working F   | Register 2   |            |            |                |              |             |       |       | 0000          |

| WREG3        | 0006 |        |        |                  |        |        |        |        | Working F   | Register 3   |            |            |                |              |             |       |       | 0000          |

| WREG4        | 8000 |        |        |                  |        |        |        |        | Working F   | Register 4   |            |            |                |              |             |       |       | 0000          |

| WREG5        | 000A |        |        |                  |        |        |        |        | Working F   | Register 5   |            |            |                |              |             |       |       | 0000          |

| WREG6        | 000C |        |        |                  |        |        |        |        | Working F   | Register 6   |            |            |                |              |             |       |       | 0000          |

| WREG7        | 000E |        |        |                  |        |        |        |        | Working F   | Register 7   |            |            |                |              |             |       |       | 0000          |

| WREG8        | 0010 |        |        |                  |        |        |        |        | Working F   | Register 8   |            |            |                |              |             |       |       | 0000          |

| WREG9        | 0012 |        |        |                  |        |        |        |        | Working F   | Register 9   |            |            |                |              |             |       |       | 0000          |

| WREG10       | 0014 |        |        |                  |        |        |        |        | Working R   | Register 10  |            |            |                |              |             |       |       | 0000          |

| WREG11       | 0016 |        |        |                  |        |        |        |        | Working F   | Register 11  |            |            |                |              |             |       |       | 0000          |

| WREG12       | 0018 |        |        |                  |        |        |        |        | Working R   | Register 12  |            |            |                |              |             |       |       | 0000          |

| WREG13       | 001A |        |        |                  |        |        |        |        | Working R   | Register 13  |            |            |                |              |             |       |       | 0000          |

| WREG14       | 001C |        |        |                  |        |        |        |        | Working R   | Register 14  |            |            |                |              |             |       |       | 0000          |

| WREG15       | 001E |        |        |                  |        |        |        |        | Working R   | Register 15  |            |            |                |              |             |       |       | 0800          |

| SPLIM        | 0020 |        |        |                  |        |        |        | Stack  | Pointer Lim | nit Value Re | gister     |            |                |              |             |       |       | xxxx          |

| PCL          | 002E |        |        |                  |        |        |        | Progra | m Counter I | Low Word R   | legister   |            |                |              |             |       |       | 0000          |

| PCH          | 0030 | —      | —      | —                | —      |        | —      | —      | —           |              |            |            |                | Register Hig |             |       |       | 0000          |

| TBLPAG       | 0032 | —      | —      | —                | —      |        | —      | —      | —           |              |            | Table N    | lemory Pag     | e Address F  | Register    |       |       | 0000          |

| PSVPAG       | 0034 |        | —      | —                | —      | —      | —      | —      | —           |              |            | rogram Spa | ace Visibility | / Page Addi  | ess Registe | er    |       | 0000          |

| RCOUNT       | 0036 |        |        |                  |        |        |        | Rep    | eat Loop C  | ounter Regi  | ster       |            |                |              |             |       |       | xxxx          |

| SR           | 0042 | _      | —      | —                | —      | _      | —      | _      | DC          | IPL2         | IPL1       | IPL0       | RA             | N            | OV          | Z     | С     | 0000          |

| CORCON       | 0044 | _      | —      | —                |        |        | _      | —      | —           |              | _          | —          | —              | IPL3         | PSV         | —     | —     | 0000          |

| DISICNT      | 0052 | —      | —      |                  |        |        |        |        | Disabl      | e Interrupts | Counter Re | egister    |                |              |             |       |       | xxxx          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0              | R/W-1                                                                                                        | R/W-0                                                                                                                        | R/W-0                                                                        | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| _                | T1IP2                                                                                                        | T1IP1                                                                                                                        | T1IP0                                                                        | _                 | OC1IP2           | OC1IP1          | OC1IP0  |  |  |  |  |  |  |

| bit 15           |                                                                                                              |                                                                                                                              |                                                                              |                   |                  |                 | bit     |  |  |  |  |  |  |

|                  |                                                                                                              |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

| U-0              | R/W-1                                                                                                        | R/W-0                                                                                                                        | R/W-0                                                                        | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

| _                | IC1IP2                                                                                                       | IC1IP1                                                                                                                       | IC1IP0                                                                       |                   | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |  |  |

| bit 7            |                                                                                                              |                                                                                                                              |                                                                              |                   |                  |                 | bit     |  |  |  |  |  |  |

| Legend:          |                                                                                                              |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

| R = Readab       | ole bit                                                                                                      | W = Writable                                                                                                                 | bit                                                                          | U = Unimpler      | nented bit, read | d as '0'        |         |  |  |  |  |  |  |

| -n = Value a     | at POR                                                                                                       | '1' = Bit is set                                                                                                             |                                                                              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 15           | Unimplemen                                                                                                   | ited: Read as '                                                                                                              | o'                                                                           |                   |                  |                 |         |  |  |  |  |  |  |

| bit 14-12        | -                                                                                                            |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  |                                                                                                              | <b>T1IP&lt;2:0&gt;:</b> Timer1 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)         |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | •                                                                                                            |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | •                                                                                                            |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | 001 = Interrupt is priority 1                                                                                |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | 000 = Interru                                                                                                | pt source is dis                                                                                                             | abled                                                                        |                   |                  |                 |         |  |  |  |  |  |  |

| bit 11           | Unimplemen                                                                                                   | ted: Read as '                                                                                                               | o'                                                                           |                   |                  |                 |         |  |  |  |  |  |  |

| bit 10-8         | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits                                                 |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                        |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | •                                                                                                            |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | •                                                                                                            |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  | 001 = Interrupt is priority 1                                                                                |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

|                  |                                                                                                              | 000 = Interrupt source is disabled                                                                                           |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

| hit 7            | Unimplemented: Read as '0'                                                                                   |                                                                                                                              |                                                                              |                   |                  |                 |         |  |  |  |  |  |  |

| bit 7            | -                                                                                                            |                                                                                                                              | כ'                                                                           | runt Driarity hit | -                |                 |         |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | IC1IP<2:0>:                                                                                                  | Input Capture C                                                                                                              | o'<br>Channel 1 Inter                                                        |                   | s                |                 |         |  |  |  |  |  |  |

|                  | IC1IP<2:0>:                                                                                                  |                                                                                                                              | o'<br>Channel 1 Inter                                                        |                   | S                |                 |         |  |  |  |  |  |  |

|                  | IC1IP<2:0>:                                                                                                  | Input Capture C                                                                                                              | o'<br>Channel 1 Inter                                                        |                   | S                |                 |         |  |  |  |  |  |  |

|                  | IC1IP<2:0>:<br>111 = Interru                                                                                 | Input Capture C<br>pt is priority 7 (                                                                                        | o'<br>Channel 1 Inter                                                        |                   | S                |                 |         |  |  |  |  |  |  |

|                  | IC1IP<2:0>:<br>111 = Interru                                                                                 | Input Capture C<br>pt is priority 7 (<br>pt is priority 1                                                                    | <sub>D</sub> '<br>Channel 1 Inter<br>highest priority                        |                   | S                |                 |         |  |  |  |  |  |  |

|                  | IC1IP<2:0>:<br>111 = Interru                                                                                 | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis                                                | <sub>D</sub> ,<br>Channel 1 Inter<br>highest priority<br>abled               |                   | S                |                 |         |  |  |  |  |  |  |

| bit 6-4          | IC1IP<2:0>:<br>111 = Interru                                                                                 | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br><b>ited:</b> Read as '                      | D'<br>Channel 1 Inter<br>highest priority<br>abled                           | interrupt)        | S                |                 |         |  |  |  |  |  |  |

| bit 6-4<br>bit 3 | IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis                                                | D'<br>Channel 1 Inter<br>highest priority<br>abled<br>D'<br>upt 0 Priority b | interrupt)        | S                |                 |         |  |  |  |  |  |  |

| bit 6-4<br>bit 3 | IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>: External Intern | D'<br>Channel 1 Inter<br>highest priority<br>abled<br>D'<br>upt 0 Priority b | interrupt)        | S                |                 |         |  |  |  |  |  |  |

| bit 6-4<br>bit 3 | IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>: External Intern | D'<br>Channel 1 Inter<br>highest priority<br>abled<br>D'<br>upt 0 Priority b | interrupt)        | S                |                 |         |  |  |  |  |  |  |

| bit 6-4<br>bit 3 | IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0><br>111 = Interru | Input Capture C<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>: External Intern | D'<br>Channel 1 Inter<br>highest priority<br>abled<br>D'<br>upt 0 Priority b | interrupt)        | S                |                 |         |  |  |  |  |  |  |

#### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0          | R/W-1                                                                                                                 | R/W-0                                | R/W-0    | U-0              | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|------------------|------------------|-----------------|----------|--|--|--|--|--|

|              | CNIP2                                                                                                                 | CNIP1                                | CNIP0    |                  | CMIP2            | CMIP1           | CMIP0    |  |  |  |  |  |

| bit 15       |                                                                                                                       |                                      |          |                  |                  |                 | bit 8    |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                 | R/W-0                                | R/W-0    | U-0              | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |

|              | MI2C1IP2                                                                                                              | MI2C1IP1                             | MI2C1IP0 | _                | SI2C1IP2         | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |

| bit 7        | -                                                                                                                     |                                      |          |                  |                  |                 | bit (    |  |  |  |  |  |

| Legend:      |                                                                                                                       |                                      |          |                  |                  |                 |          |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                | W = Writable                         | bit      | U = Unimple      | mented bit, read | d as '0'        |          |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                 | '1' = Bit is set                     |          | '0' = Bit is cle |                  | x = Bit is unkr | nown     |  |  |  |  |  |

| bit 15       | Unimplomon                                                                                                            | ted: Read as '                       | o,'      |                  |                  |                 |          |  |  |  |  |  |

| bit 14-12    | -                                                                                                                     | nput Change N                        |          | rrunt Priority b | its              |                 |          |  |  |  |  |  |

| ~            |                                                                                                                       | pt is priority 7 (                   |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      | ,        | • •              |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | 001 = Interru                                                                                                         | pt is priority 1                     |          |                  |                  |                 |          |  |  |  |  |  |

|              |                                                                                                                       | pt source is dis                     | abled    |                  |                  |                 |          |  |  |  |  |  |

| bit 11       | Unimplemen                                                                                                            | ted: Read as '                       | 0'       |                  |                  |                 |          |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits                                                                         |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                 |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                   |                                      |          |                  |                  |                 |          |  |  |  |  |  |

| hit 7        | -                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

| bit 7        | -                                                                                                                     | ted: Read as '                       |          | of Drianity bit- |                  |                 |          |  |  |  |  |  |

| bit 6-4      | MI2C1IP<2:0>: Master I2C1 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          | menupi)          |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •<br>001 = Interru                                                                                                    | nt is priority 1                     |          |                  |                  |                 |          |  |  |  |  |  |

|              |                                                                                                                       | pt is priority i<br>pt source is dis | abled    |                  |                  |                 |          |  |  |  |  |  |

| bit 3        | •                                                                                                                     | ted: Read as '                       |          |                  |                  |                 |          |  |  |  |  |  |

| bit 2-0      | -                                                                                                                     | >: Slave I2C1 E                      |          | Priority bits    |                  |                 |          |  |  |  |  |  |

|              |                                                                                                                       | pt is priority 7 (                   | •        | •                |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •                                                                                                                     |                                      |          |                  |                  |                 |          |  |  |  |  |  |

|              | •<br>001 = Interru                                                                                                    | pt is priority 1                     |          |                  |                  |                 |          |  |  |  |  |  |

#### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

#### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0          | U-0   | U-0          | U-0 | U-0          | U-0              | U-0      | U-0     |

|--------------|-------|--------------|-----|--------------|------------------|----------|---------|

| _            | _     | —            | _   | —            | —                | —        | —       |

| bit 15       |       |              |     |              |                  |          | bit 8   |

|              |       |              |     |              |                  |          |         |

| U-0          | U-0   | U-0          | U-0 | U-0          | R/W-1            | R/W-0    | R/W-0   |

| _            | —     | —            | —   | —            | INT1IP2          | INT1IP1  | INT1IP0 |

| bit 7        |       |              |     |              | •                |          | bit 0   |

|              |       |              |     |              |                  |          |         |

| Legend:      |       |              |     |              |                  |          |         |

| R = Readable | e bit | W = Writable | bit | U = Unimplem | nented bit, read | d as '0' |         |

| ••   |              |                  | •     |                |                    |

|------|--------------|------------------|-------|----------------|--------------------|

| -n = | Value at POR | '1' = Bit is set | '0' = | Bit is cleared | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is priority 7 (highest priority interrupt)

- •

bit 2-0

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

#### REGISTER 7-28: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0              | U-0                 | U-0                      | U-0              | U-0               | R/W-1            | R/W-0              | R/W-0  |  |

|------------------|---------------------|--------------------------|------------------|-------------------|------------------|--------------------|--------|--|

| _                | —                   | —                        | —                |                   | RTCIP2           | RTCIP1             | RTCIP0 |  |

| bit 15           |                     |                          |                  |                   |                  |                    | bit 8  |  |

|                  |                     |                          |                  |                   |                  |                    |        |  |

| U-0              | U-0                 | U-0                      | U-0              | U-0               | U-0              | U-0                | U-0    |  |

| —                | —                   | _                        | —                | —                 | —                | —                  | —      |  |

| bit 7            |                     |                          |                  |                   |                  |                    | bit 0  |  |

|                  |                     |                          |                  |                   |                  |                    |        |  |

| Legend:          |                     |                          |                  |                   |                  |                    |        |  |

| R = Readabl      | le bit              | W = Writable             | bit              | U = Unimplem      | nented bit, read | as '0'             |        |  |

| -n = Value at    | POR                 | '1' = Bit is set         |                  | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

| <b>Lit 45 44</b> | l lucius a lo ano a | ted. Deed ee W           | <b>.</b> '       |                   |                  |                    |        |  |

| bit 15-11        | -                   | ted: Read as '           |                  |                   |                  |                    |        |  |

| bit 10-8         | RTCIP<2:0>:         | Real-Time Clo            | ck/Calendar In   | terrupt Priority  | bits             |                    |        |  |

|                  | 111 = Interru       | pt is priority 7 (I      | nighest priority | interrupt)        |                  |                    |        |  |

|                  | •                   |                          |                  |                   |                  |                    |        |  |

|                  | •                   |                          |                  |                   |                  |                    |        |  |

|                  | •                   |                          |                  |                   |                  |                    |        |  |

|                  | 001 = Interru       | pt is priority 1         |                  |                   |                  |                    |        |  |

|                  |                     | pt source is dis         | abled            |                   |                  |                    |        |  |

| bit 7-0          |                     | i <b>ted:</b> Read as '( |                  |                   |                  |                    |        |  |

|                  | •                   |                          |                  |                   |                  |                    |        |  |

#### 9.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 39. "Power-Saving Features         |

|       | with Deep Sleep" (DS39727).                |

The PIC24FJ64GA104 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep, Idle and Deep Sleep modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

#### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals except RTCC and DSWDT. It also freezes I/O states and removes power to SRAM and Flash memory. The assembly syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

| EXAMPLE 9-1: | <b>PWRSAV INSTRUCTION SYNTAX</b> |

|--------------|----------------------------------|

|              |                                  |

| PWRSAV | #SLEEP_MODE  | ; Put the device into SLEEP mode      |

|--------|--------------|---------------------------------------|

| PWRSAV | #IDLE_MODE   | ; Put the device into IDLE mode       |

| BSET   | DSCON, #DSEN | ; Enable Deep Sleep                   |

| PWRSAV | #SLEEP_MODE  | ; Put the device into Deep SLEEP mode |

NOTES:

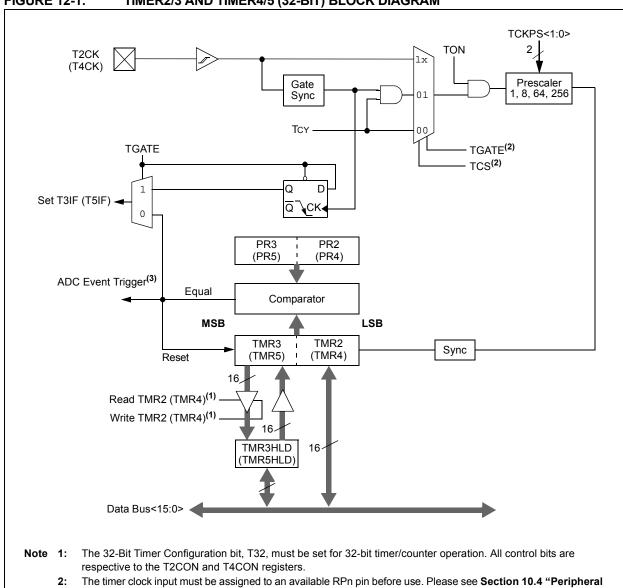

#### **FIGURE 12-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

Pin Select (PPS)" for more information.

3: The ADC event trigger is available only on Timer 2/3 in 32-bit mode and Timer 3 in 16-bit mode.

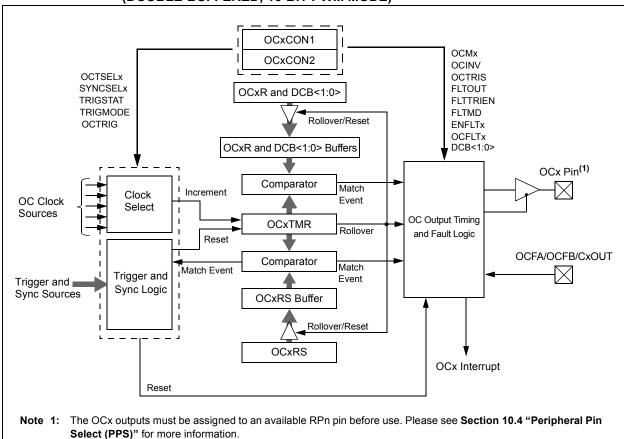

#### 14.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for edge-aligned PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired on-time and load it into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing 0x1F to SYNCSEL<4:0> (OCxCON2<4:0>) and '0' to OCTRIG (OCxCON2<7>).

- 5. Select a clock source by writing to the OCTSEL2<2:0> (OCxCON1<12:10>) bits.

- Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- Select the desired PWM mode in the OCM<2:0> (OCxCON1<2:0>) bits.

- 8. If a timer is selected as a clock source, set the TMRy prescale value and enable the time base by setting the TON (TxCON<15>) bit.

- Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

#### FIGURE 14-2: OUTPUT COMPARE BLOCK DIAGRAM (DOUBLE-BUFFERED, 16-BIT PWM MODE)

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                                     |

|       | 0 = Stop bit was not detected last                                                                                                                                                                                                       |

|       | Hardware set or clear when Start, Repeated Start or Stop is detected.                                                                                                                                                                    |

| bit 3 | S: Start bit                                                                                                                                                                                                                             |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                               |

|       | Hardware set or clear when Start, Repeated Start or Stop is detected.                                                                                                                                                                    |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                       |

|       | <ul> <li>1 = Read – indicates data transfer is output from the slave</li> <li>0 = Write – indicates data transfer is input to the slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit                                                                                                                                                                                               |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>        |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                     |

|       | 1 = Transmit is in progress, I2CxTRN is full<br>0 = Transmit is complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission                                               |

|       | Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.                                                                                                                                            |

© 2010 Microchip Technology Inc.

#### REGISTER 18-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| U-0    | R/W-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|-------|-----|-----|-----|-----------------------|----------------------|----------------------|

| —      | CS1   | —   | —   | —   | ADDR10 <sup>(1)</sup> | ADDR9 <sup>(1)</sup> | ADDR8 <sup>(1)</sup> |

| bit 15 |       |     |     |     |                       |                      | bit 8                |

| R/W-0                |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| ADDR7 <sup>(1)</sup> | ADDR6 <sup>(1)</sup> | ADDR5 <sup>(1)</sup> | ADDR4 <sup>(1)</sup> | ADDR3 <sup>(1)</sup> | ADDR2 <sup>(1)</sup> | ADDR1 <sup>(1)</sup> | ADDR0 <sup>(1)</sup> |

| bit 7                |                      |                      |                      |                      |                      |                      | bit 0                |

### Legend:

| Legena:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 15 | Unimplemented: Read | as | '0' |

|--------|---------------------|----|-----|

|--------|---------------------|----|-----|

- bit 14 CS1: Chip Select 1 bit

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Parallel Port Destination Address bits<sup>(1)</sup>

**Note 1:** PMA<10:2> bits are not available on 28-pin devices.

#### REGISTER 18-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                | R/W-0                |

|--------|--------|-----|-----|-----|-----------------------|----------------------|----------------------|

| —      | PTEN14 |     | —   | —   | PTEN10 <sup>(1)</sup> | PTEN9 <sup>(1)</sup> | PTEN8 <sup>(1)</sup> |

| bit 15 |        |     |     |     |                       |                      | bit 8                |

| R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------|-------|

| PTEN7 <sup>(1)</sup> | PTEN6 <sup>(1)</sup> | PTEN5 <sup>(1)</sup> | PTEN4 <sup>(1)</sup> | PTEN3 <sup>(1)</sup> | PTEN2 <sup>(1)</sup> | PTEN1 | PTEN0 |

| bit 7                |                      |                      |                      |                      |                      |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | PTEN14: PMCS1 Strobe Enable bit                                                                                                                 |

|           | <ul><li>1 = PMCS1 functions as chip select</li><li>0 = PMCS1 pin functions as port I/O</li></ul>                                                |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                      |

| bit 10-2  | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                         |

|           | 1 = PMA<10:2> function as PMP address lines                                                                                                     |

|           | 0 = PMA<10:2> function as port I/O                                                                                                              |

| bit 1-0   | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                       |

|           | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads function as port I/O</li> </ul> |

**Note 1:** PMA<10:2> bits are not available on 28-pin devices.

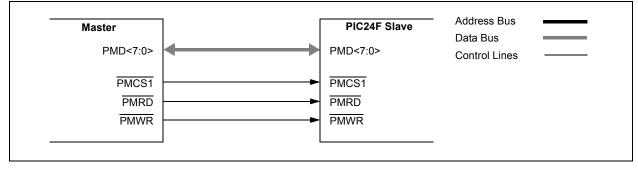

#### FIGURE 18-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

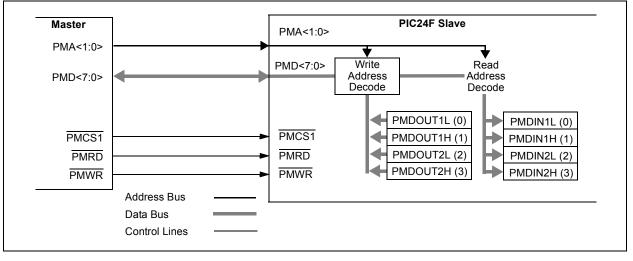

#### FIGURE 18-3: ADDRESSABLE PARALLEL SLAVE PORT EXAMPLE

#### TABLE 18-1: SLAVE MODE ADDRESS RESOLUTION

| PMA<1:0> | Output Register (Buffer) | Input Register (Buffer) |

|----------|--------------------------|-------------------------|

| 00       | PMDOUT1<7:0> (0)         | PMDIN1<7:0> (0)         |

| 01       | PMDOUT1<15:8> (1)        | PMDIN1<15:8> (1)        |

| 10       | PMDOUT2<7:0> (2)         | PMDIN2<7:0> (2)         |

| 11       | PMDOUT2<15:8> (3)        | PMDIN2<15:8> (3)        |

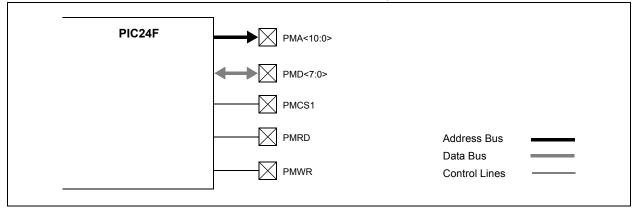

### FIGURE 18-4: MASTER MODE, DEMULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, SINGLE CHIP SELECT)

#### 19.2.4 RTCC CONTROL REGISTERS

### REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0 | R/W-0   | R-0, HSC | R-0, HSC               | R/W-0 | R/W-0   | R/W-0   |

|----------------------|-----|---------|----------|------------------------|-------|---------|---------|

| RTCEN <sup>(2)</sup> | —   | RTCWREN | RTCSYNC  | HALFSEC <sup>(3)</sup> | RTCOE | RTCPTR1 | RTCPTR0 |

| bit 15               |     |         |          |                        |       |         | bit 8   |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 | •     |       | •     |       |       |       | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  | RTCEN: RTCC Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = RTCC module is enabled</li> <li>0 = RTCC module is disabled</li> </ul>                                                                                                                                                                                                                                                                          |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                   |

| bit 13  | RTCWREN: RTCC Value Registers Write Enable bit                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = RTCVALH and RTCVALL registers can be written to by the user</li> <li>0 = RTCVALH and RTCVALL registers are locked out from being written to by the user</li> </ul>                                                                                                                                                                              |

| bit 12  | RTCSYNC: RTCC Value Registers Read Synchronization bit                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading due to a rollover ripple resulting in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.</li> <li>0 = RTCVALH, RTCVALL or ALCFGRPT registers can be read without concern over a rollover ripple</li> </ul> |

| bit 11  | HALFSEC: Half Second Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Second half period of a second</li> <li>0 = First half period of a second</li> </ul>                                                                                                                                                                                                                                                            |

| bit 10  | RTCOE: RTCC Output Enable bit                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = RTCC output is enabled</li> <li>0 = RTCC output is disabled</li> </ul>                                                                                                                                                                                                                                                                          |

| bit 9-8 | RTCPTR<1:0>: RTCC Value Register Window Pointer bits                                                                                                                                                                                                                                                                                                         |

|         | Points to the corresponding RTCC Value registers when reading the RTCVALH and RTCVALL registers. The RTCPTR<1:0> value decrements on every read or write of RTCVALH until it reaches '00'.                                                                                                                                                                   |

|         | <u>RTCVAL&lt;15:8&gt;:</u><br>00 = MINUTES<br>01 = WEEKDAY<br>10 = MONTH<br>11 = Reserved                                                                                                                                                                                                                                                                    |

|         | <u>RTCVAL&lt;7:0&gt;:</u>                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                                                                                                                              |

|         | 01 = HOURS<br>10 = DAY                                                                                                                                                                                                                                                                                                                                       |

|         | 11 = YEAR                                                                                                                                                                                                                                                                                                                                                    |

| Note 1: | The RCFGCAL register is only affected by a POR.                                                                                                                                                                                                                                                                                                              |

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

#### 28.1 DC Characteristics

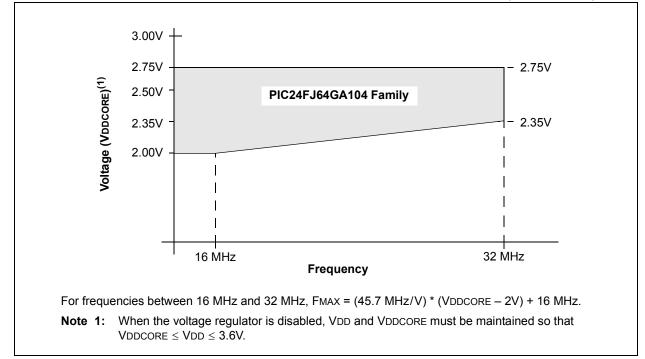

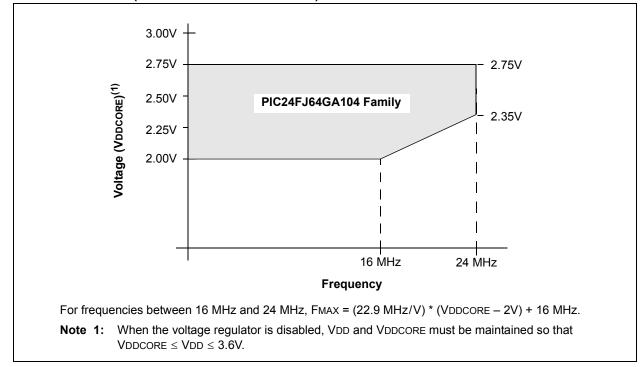

#### FIGURE 28-1: PIC24FJ64GA104 FAMILY VOLTAGE/FREQUENCY GRAPH (INDUSTRIAL)

#### FIGURE 28-2: PIC24FJ64GA104 FAMILY VOLTAGE/FREQUENCY GRAPH (EXTENDED TEMPERATURE)

### TABLE 28-7: DC CHARACTERISTICS: POWER-DOWN PERIPHERAL MODULE $\triangle$ CURRENT (IPD)

| DC CHARACI                                                                           | ERISTICS               |     | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |                     |                                        |  |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|----------------------------------------|--|--|--|--|--|

| Parameter<br>No.                                                                     | Typical <sup>(1)</sup> | Мах | Units                                                                                                                                                                                                          | Conditions |                     |                                        |  |  |  |  |  |

| $\Delta$ Power-Down Current (IPD): PMD Bits are Set, PMSLP Bit is '0' <sup>(2)</sup> |                        |     |                                                                                                                                                                                                                |            |                     |                                        |  |  |  |  |  |

| DC61                                                                                 | 0.2                    | 0.7 | μA                                                                                                                                                                                                             | -40°C      |                     |                                        |  |  |  |  |  |

| DC61a                                                                                | 0.2                    | 0.7 | μA                                                                                                                                                                                                             | +25°C      | 2.0V <sup>(3)</sup> |                                        |  |  |  |  |  |

| DC61i                                                                                | 0.2                    | 0.7 | μA                                                                                                                                                                                                             | +60°C      |                     |                                        |  |  |  |  |  |

| DC61b                                                                                | 0.23                   | 0.7 | μA                                                                                                                                                                                                             | +85°C      |                     |                                        |  |  |  |  |  |

| DC61m                                                                                | 0.3                    | 1.0 | μA                                                                                                                                                                                                             | +125°C     |                     |                                        |  |  |  |  |  |

| DC61c                                                                                | 0.25                   | 0.9 | μA                                                                                                                                                                                                             | -40°C      |                     |                                        |  |  |  |  |  |

| DC61d                                                                                | 0.25                   | 0.9 | μA                                                                                                                                                                                                             | +25°C      |                     | 31 kHz LPRC Oscillator with            |  |  |  |  |  |

| DC61j                                                                                | 0.25                   | 0.9 | μA                                                                                                                                                                                                             | +60°C      | 2.5∨ <sup>(3)</sup> | RTCC, WDT, DSWDT or                    |  |  |  |  |  |

| DC61e                                                                                | 0.28                   | 0.9 | μA                                                                                                                                                                                                             | +85°C      |                     | Timer 1: AllPRC <sup>(5)</sup>         |  |  |  |  |  |

| DC61p                                                                                | 0.5                    | 1.2 | μA                                                                                                                                                                                                             | +125°C     |                     |                                        |  |  |  |  |  |

| DC61f                                                                                | 0.6                    | 1.5 | μA                                                                                                                                                                                                             | -40°C      |                     |                                        |  |  |  |  |  |

| DC61g                                                                                | 0.6                    | 1.5 | μA                                                                                                                                                                                                             | +25°C      | 3.3∨ <b>(4)</b>     |                                        |  |  |  |  |  |

| DC61k                                                                                | 0.6                    | 1.5 | μA                                                                                                                                                                                                             | +60°C      |                     |                                        |  |  |  |  |  |

| DC61h                                                                                | 0.8                    | 1.5 | μA                                                                                                                                                                                                             | +85°C      |                     |                                        |  |  |  |  |  |

| DC61n                                                                                | 1.0                    | 1.7 | μA                                                                                                                                                                                                             | +125°C     |                     |                                        |  |  |  |  |  |