#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

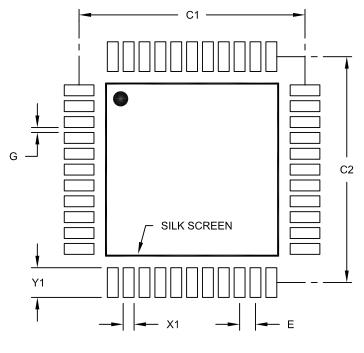

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga104-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

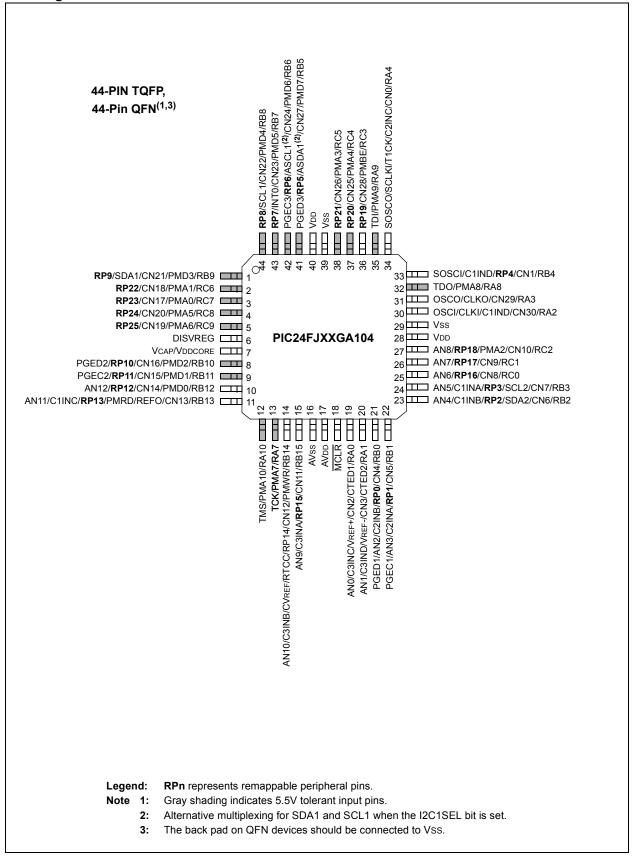

#### **Pin Diagrams**

### 3.0 CPU

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 2. "CPU" (DS39703).                |

The PIC24F CPU has a 16-bit (data), modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported either directly or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

### 3.1 **Programmer's Model**

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory mapped.

#### TABLE 4-15: PAD CONFIGURATION REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-----------|-----------|--------|---------------|

| PADCFG1   | 02FC | —      | _      | _      | —      |        | _      | _     | _     | _     | -     | _     | _     | _     | RTSECSEL1 | RTSECSEL0 | PMPTTL | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: ADC REGISTER MAP

| IADLE 4-  | 10.  |        |        |        |                       |        |        |        |                      | -                    |                      |       |        |        |        |        |        |               |

|-----------|------|--------|--------|--------|-----------------------|--------|--------|--------|----------------------|----------------------|----------------------|-------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9  | Bit 8                | Bit 7                | Bit 6                | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0  | 0300 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 0           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF1  | 0302 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 1           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF2  | 0304 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 2           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF3  | 0306 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 3           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF4  | 0308 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 4           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF5  | 030A |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 5           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF6  | 030C |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 6           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF7  | 030E |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 7           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF8  | 0310 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 8           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF9  | 0312 |        |        |        |                       |        |        |        | ADC Dat              | a Buffer 9           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFA  | 0314 |        |        |        |                       |        |        |        | ADC Data             | a Buffer 10          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFB  | 0316 |        |        |        |                       |        |        |        | ADC Data             | a Buffer 11          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFC  | 0318 |        |        |        |                       |        |        |        | ADC Data             | a Buffer 12          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFD  | 031A |        |        |        |                       |        |        |        | ADC Data             | a Buffer 13          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFE  | 031C |        |        |        |                       |        |        |        | ADC Data             | a Buffer 14          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFF  | 031E |        |        |        |                       |        |        | 1      |                      | a Buffer 15          | 1                    | 1     |        |        | 1      | 1      | 1      | xxxx          |

| AD1CON1   | 0320 | ADON   | —      | ADSIDL | —                     | _      | —      | FORM1  | FORM0                | SSRC2                | SSRC1                | SSRC0 | —      | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2   | 0322 | VCFG2  | VCFG1  | VCFG0  | r                     | _      | CSCNA  | _      | —                    | BUFS                 | —                    | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3   | 0324 | ADRC   | r      | r      | SAMC4                 | SAMC3  | SAMC2  | SAMC1  | SAMC0                | ADCS7                | ADCS6                | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS    | 0328 | CH0NB  | —      | —      | CH0SB4                | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0               | CHONA                | —                    | —     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFG   | 032C | PCFG15 |        |        | PCFG12 <sup>(1)</sup> | PCFG11 | PCFG10 | PCFG9  |                      | PCFG7 <sup>(1)</sup> |                      | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1CSSL   | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12 <sup>(1)</sup> | CSSL11 | CSSL10 | CSSL9  | CSSL8 <sup>(1)</sup> | CSSL7 <sup>(1)</sup> | CSSL6 <sup>(1)</sup> | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are not available on 28-pin devices; read as '0'.

#### TABLE 4-17: CTMU REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON   | 033C | CTMUEN | —      | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON  | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  |         | _        | -        | -       | -        | _        |          |          | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                   | U-0                                                                                                                                | U-0                                                                                                                                                                                 | U-0                                                                                      | U-0                         | R/W-1            | R/W-0           | R/W-0    |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------|----------|

| _                     |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             | MI2C2IP2         | MI2C2IP1        | MI2C2IP0 |

| bit 15                | ·                                                                                                                                  |                                                                                                                                                                                     |                                                                                          |                             |                  |                 | bit 8    |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| U-0                   | R/W-1                                                                                                                              | R/W-0                                                                                                                                                                               | R/W-0                                                                                    | U-0                         | U-0              | U-0             | U-0      |

| _                     | SI2C2IP2                                                                                                                           | SI2C2IP1                                                                                                                                                                            | SI2C2IP0                                                                                 | —                           | —                | —               | —        |

| bit 7                 |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 | bit 0    |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| Legend:               |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| R = Readab            | le bit                                                                                                                             | W = Writable                                                                                                                                                                        | bit                                                                                      | U = Unimple                 | mented bit, read | 1 as '0'        |          |

| -n = Value a          | It POR                                                                                                                             | '1' = Bit is set                                                                                                                                                                    |                                                                                          | '0' = Bit is cle            | eared            | x = Bit is unkr | nown     |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

|                       |                                                                                                                                    |                                                                                                                                                                                     |                                                                                          |                             |                  |                 |          |

| bit 15-11             | Unimplemen                                                                                                                         | ted: Read as '                                                                                                                                                                      | ٥'                                                                                       |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

| bit 15-11<br>bit 10-8 | MI2C2IP<2:0                                                                                                                        |                                                                                                                                                                                     | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0                                                                                                                        | >: Master I2C2                                                                                                                                                                      | Event Interrup                                                                           |                             |                  |                 |          |

|                       | MI2C2IP<2:0<br>111 = Interrup                                                                                                      | >: Master I2C2<br>ot is priority 7 (I                                                                                                                                               | Event Interrup<br>highest priority                                                       |                             |                  |                 |          |

|                       | MI2C2IP<2:0<br>111 = Interrup<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1                                                                                                                           | Event Interrup<br>highest priority<br>abled                                              |                             |                  |                 |          |

| bit 10-8              | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen                                                    | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis                                                                                                       | Event Interrup<br>highest priority<br>abled                                              | interrupt)                  |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br><b>ted:</b> Read as '(                                                                             | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br>ted: Read as '(<br>>: Slave I2C2 E                                                                 | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | >: Master I2C2<br>ot is priority 7 (I<br>ot is priority 1<br>ot source is dis<br>ted: Read as '(<br>>: Slave I2C2 E                                                                 | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0                                     | <ul> <li>Master I2C2</li> <li>tis priority 7 (I</li> <li>tis priority 1</li> <li>source is dis</li> <li>ted: Read as '(</li> <li>Slave I2C2 E</li> <li>tis priority 7 (I</li> </ul> | Event Interrup<br>highest priority<br>abled<br>D'<br>Event Interrupt                     | interrupt)<br>Priority bits |                  |                 |          |

| bit 10-8<br>bit 7     | MI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>SI2C2IP<2:0<br>111 = Interrup<br>001 = Interrup | <ul> <li>Master I2C2</li> <li>tis priority 7 (I</li> <li>tis priority 1</li> <li>source is dis</li> <li>ted: Read as '(</li> <li>Slave I2C2 E</li> <li>tis priority 7 (I</li> </ul> | Event Interrup<br>highest priority<br>abled<br>o'<br>Event Interrupt<br>highest priority | interrupt)<br>Priority bits |                  |                 |          |

#### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

|                  | R/W-1                                                                                  | R/W-0                                                                        | R/W-0                                               | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------|------------------|------------------|-----------------|---------|

| _                | CRCIP2                                                                                 | CRCIP1                                                                       | CRCIP0                                              |                  | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| bit 15           |                                                                                        |                                                                              |                                                     |                  |                  |                 | bit     |

|                  |                                                                                        |                                                                              |                                                     |                  |                  |                 |         |

| U-0              | R/W-1                                                                                  | R/W-0                                                                        | R/W-0                                               | U-0              | U-0              | U-0             | U-0     |

| —                | U1ERIP2                                                                                | U1ERIP1                                                                      | U1ERIP0                                             | —                |                  | —               | —       |

| bit 7            |                                                                                        |                                                                              |                                                     |                  |                  |                 | bit     |

| Legend:          |                                                                                        |                                                                              |                                                     |                  |                  |                 |         |

| R = Readab       | le bit                                                                                 | W = Writable                                                                 | bit                                                 | U = Unimplei     | mented bit, read | l as '0'        |         |

| -n = Value a     | It POR                                                                                 | '1' = Bit is set                                                             |                                                     | '0' = Bit is cle |                  | x = Bit is unkr | nown    |

|                  |                                                                                        |                                                                              |                                                     |                  |                  |                 |         |

| bit 15           | Unimplemen                                                                             | ted: Read as '                                                               | )'                                                  |                  |                  |                 |         |

| bit 14-12        | CRCIP<2:0>                                                                             | CRC Generate                                                                 | or Error Interru                                    | pt Priority bits |                  |                 |         |

|                  |                                                                                        | pt is priority 7 (I                                                          |                                                     |                  |                  |                 |         |

|                  | •                                                                                      |                                                                              | 5 , ,                                               | 1 /              |                  |                 |         |

|                  | •                                                                                      |                                                                              |                                                     |                  |                  |                 |         |

|                  | •<br>001 = Interru                                                                     | ntin muinuitud                                                               |                                                     |                  |                  |                 |         |

|                  |                                                                                        | pt is priority i<br>pt source is dis                                         | abled                                               |                  |                  |                 |         |

| bit 11           |                                                                                        | ted: Read as '                                                               |                                                     |                  |                  |                 |         |

| bit 10-8         | -                                                                                      | -: UART2 Error                                                               |                                                     | ritv bits        |                  |                 |         |

|                  |                                                                                        | pt is priority 7 (I                                                          |                                                     | •                |                  |                 |         |

|                  | •                                                                                      |                                                                              |                                                     |                  |                  |                 |         |

|                  |                                                                                        |                                                                              |                                                     |                  |                  |                 |         |

|                  | •                                                                                      |                                                                              |                                                     |                  |                  |                 |         |

|                  | •                                                                                      | at is priority d                                                             |                                                     |                  |                  |                 |         |

|                  | •<br>001 = Interru<br>000 = Interru                                                    |                                                                              | abled                                               |                  |                  |                 |         |

| bit 7            | 000 = Interru                                                                          | pt source is dis                                                             |                                                     |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen                                                            | pt source is dis<br>ted: Read as '(                                          | )'                                                  | ritv bits        |                  |                 |         |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                             | pt source is dis<br>ted: Read as '(<br>>: UART1 Error                        | )'<br>Interrupt Prio                                |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                             | pt source is dis<br>ted: Read as '(                                          | )'<br>Interrupt Prio                                |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                             | pt source is dis<br>ted: Read as '(<br>>: UART1 Error                        | )'<br>Interrupt Prio                                |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:03<br>111 = Interru<br>•<br>•                  | pt source is dis<br>ted: Read as '(<br>>: UART1 Error<br>pt is priority 7 (I | )'<br>Interrupt Prio                                |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru | pt source is dis<br>ted: Read as '(<br>>: UART1 Error<br>pt is priority 7 (I | <sup>)'</sup><br>Interrupt Prio<br>nighest priority |                  |                  |                 |         |

#### REGISTER 7-29: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

| U-0          | U-0                | U-0                 | U-0                       | U-0                 | U-0                 | U-0                 | U-0                 |

|--------------|--------------------|---------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|

| —            | —                  | —                   | —                         | —                   | —                   | —                   | _                   |

| bit 15       |                    |                     |                           |                     |                     |                     | bit 8               |

|              |                    |                     |                           |                     |                     |                     |                     |

| U-0          | U-0                | R/W-0               | R/W-0                     | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| —            | —                  | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7        | ÷                  | •                   |                           |                     | •                   |                     | bit 0               |

|              |                    |                     |                           |                     |                     |                     |                     |

| Legend:      |                    |                     |                           |                     |                     |                     |                     |

| R = Readal   | ble bit            | W = Writable        | bit                       | U = Unimplem        | nented bit, read    | l as '0'            |                     |

| -n = Value a | at POR             | '1' = Bit is set    |                           | '0' = Bit is clea   | ared                | x = Bit is unkr     | iown                |

|              |                    |                     |                           |                     |                     |                     |                     |

| bit 15-6     | Unimplemen         | ted: Read as '      | o'                        |                     |                     |                     |                     |

| bit 5-0      | TUN<5:0>: FI       | RC Oscillator T     | uning bits <sup>(1)</sup> |                     |                     |                     |                     |

|              | 011111 <b>= Ma</b> | ximum frequer       | ncy deviation             |                     |                     |                     |                     |

|              | 011110 =           |                     |                           |                     |                     |                     |                     |

|              | •                  |                     |                           |                     |                     |                     |                     |

|              | •                  |                     |                           |                     |                     |                     |                     |

|              | • 000001 =         |                     |                           |                     |                     |                     |                     |

|              |                    | nter frequency      | oscillator is ru          | inning at factory   | / calibrated free   | nuency              |                     |

|              | 111111 =           | inter inequency,    |                           | in ing at labters   |                     | lacitoy             |                     |

|              | •                  |                     |                           |                     |                     |                     |                     |

|              | •                  |                     |                           |                     |                     |                     |                     |

|              | •                  |                     |                           |                     |                     |                     |                     |

#### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

### 8.4 Clock Switching Operation

100001 =

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

100000 = Minimum frequency deviation

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM Configuration bits in CW2 must be programmed to '00'. (Refer to **Section 25.1 "Configuration Bits"** for further details.) If the FCKSM Configuration bits are unprogrammed ('1x'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### REGISTER 8-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| REGISTER     | 0-4. KEFC          |                                       |                  |                                        |                  |                 |               |

|--------------|--------------------|---------------------------------------|------------------|----------------------------------------|------------------|-----------------|---------------|

| R/W-0        | U-0                | R/W-0                                 | R/W-0            | R/W-0                                  | R/W-0            | R/W-0           | R/W-0         |

| ROEN         | —                  | ROSSLP                                | ROSEL            | RODIV3                                 | RODIV2           | RODIV1          | RODIV0        |

| bit 15       |                    |                                       |                  |                                        |                  |                 | bit 8         |

| U-0          | U-0                | U-0                                   | U-0              | U-0                                    | U-0              | U-0             | U-0           |

| _            | —                  | —                                     | _                | —                                      | —                | —               | —             |

| bit 7        |                    |                                       |                  |                                        |                  |                 | bit 0         |

| Legend:      |                    |                                       |                  |                                        |                  |                 |               |

| R = Readab   | le bit             | W = Writable                          | bit              | U = Unimplen                           | nented bit, read | d as '0'        |               |

| -n = Value a | t POR              | '1' = Bit is set                      |                  | '0' = Bit is clea                      | ared             | x = Bit is unki | nown          |

|              |                    |                                       |                  |                                        |                  |                 |               |

| bit 15       |                    | ence Oscillator<br>e oscillator is ei | -                |                                        |                  |                 |               |

|              | 0 = Reference      | e oscillator is di                    | sabled           |                                        |                  |                 |               |

| bit 14       | Unimplemen         | ted: Read as '                        | )'               |                                        |                  |                 |               |

| bit 13       | ROSSLP: Re         | ference Oscilla                       | tor Output Sto   | p in Sleep bit                         |                  |                 |               |

|              | 1 = Reference      | e oscillator con                      | tinues to run ir | n Sleep                                |                  |                 |               |

|              | 0 = Reference      | e oscillator is di                    | sabled in Slee   | p                                      |                  |                 |               |

| bit 12       | ROSEL: Refe        | erence Oscillato                      | or Source Sele   | ect bit                                |                  |                 |               |

|              |                    |                                       |                  | clock. Note that                       |                  |                 | enabled using |

|              |                    |                                       |                  | ains the operation<br>k; base clock re |                  |                 | the device    |

| bit 11-8     | -                  | Reference Os                          |                  |                                        |                  | K SWITCHING OF  |               |

| DIL I I-8    |                    |                                       |                  |                                        |                  |                 |               |

|              |                    | clock value div<br>clock value div    | -                |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              | 1011 <b>= Base</b> | clock value div                       | ided by 2,048    |                                        |                  |                 |               |

|              |                    | clock value div                       |                  |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              |                    | clock value div<br>clock value div    |                  |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              |                    | clock value div                       | •                |                                        |                  |                 |               |

|              | 0011 <b>= Base</b> | clock value div                       | ided by 8        |                                        |                  |                 |               |

|              |                    | clock value div                       |                  |                                        |                  |                 |               |

|              |                    | clock value div                       | ided by 2        |                                        |                  |                 |               |

|              | 0000 <b>= Base</b> | clock value                           |                  |                                        |                  |                 |               |

| bit 7-0      | Unimplemen         | ted: Read as '                        | )'               |                                        |                  |                 |               |

|              |                    |                                       |                  |                                        |                  |                 |               |

NOTES:

#### REGISTER 10-9: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   |     | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 12-8  | U1CTSR<4:0>: Assign UART1 Clear to Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                            |

| bit 4-0   | U1RXR<4:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

#### REGISTER 10-10: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 U2CTSR<4:0>: Assign UART2 Clear to Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 U2RXR<4:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

| R/W-0        | U-0                           | R/W-0                                           | U-0             | U-0               | U-0             | U-0              | U-0          |  |  |  |  |

|--------------|-------------------------------|-------------------------------------------------|-----------------|-------------------|-----------------|------------------|--------------|--|--|--|--|

| TON          |                               | TSIDL                                           | —               |                   | _               | _                | —            |  |  |  |  |

| bit 15       |                               |                                                 |                 |                   | •               |                  | bit          |  |  |  |  |

|              |                               |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| U-0          | R/W-0                         | R/W-0                                           | R/W-0           | U-0               | R/W-0           | R/W-0            | U-0          |  |  |  |  |

|              | TGATE                         | TCKPS1                                          | TCKPS0          |                   | TSYNC           | TCS              | _            |  |  |  |  |

| bit 7        |                               |                                                 |                 |                   |                 |                  | bit          |  |  |  |  |

| Legend:      |                               |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| R = Readab   | le bit                        | W = Writable                                    | bit             | U = Unimpler      | nented bit, rea | d as '0'         |              |  |  |  |  |

| -n = Value a | t POR                         | '1' = Bit is set                                |                 | '0' = Bit is cle  | ared            | x = Bit is unkno | own          |  |  |  |  |

|              |                               |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| bit 15       | TON: Timer1                   |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              | 1 = Starts 16<br>0 = Stops 16 |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| bit 14       | -                             | ted: Read as '                                  | י)              |                   |                 |                  |              |  |  |  |  |

| bit 13       | -                             | in Idle Mode bit                                |                 |                   |                 |                  |              |  |  |  |  |

|              | •                             |                                                 |                 | evice enters Idle | e mode          |                  |              |  |  |  |  |

|              |                               | module operati                                  |                 |                   |                 |                  |              |  |  |  |  |

| bit 12-7     | Unimplemen                    | ted: Read as '                                  | )'              |                   |                 |                  |              |  |  |  |  |

| bit 6        | TGATE: Time                   | GATE: Timer1 Gated Time Accumulation Enable bit |                 |                   |                 |                  |              |  |  |  |  |

|              | When $TCS = 1$ :              |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              | This bit is ign<br>When TCS = |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              |                               | <u>o.</u><br>ne accumulatio                     | n enabled       |                   |                 |                  |              |  |  |  |  |

|              |                               | ne accumulatio                                  |                 |                   |                 |                  |              |  |  |  |  |

| bit 5-4      | TCKPS<1:0>                    | : Timer1 Input                                  | Clock Prescal   | e Select bits     |                 |                  |              |  |  |  |  |

|              | 11 = 1:256                    |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8         |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              | 00 = 1:1                      |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| bit 3        | Unimplemen                    | ted: Read as '                                  | )'              |                   |                 |                  |              |  |  |  |  |

| bit 2        | -                             |                                                 |                 | hronization Sel   | ect bit         |                  |              |  |  |  |  |

|              | When TCS =                    |                                                 |                 |                   |                 |                  |              |  |  |  |  |

|              |                               | nize external clo                               |                 |                   |                 |                  |              |  |  |  |  |

|              | -                             | ynchronize exte                                 | ernal clock inp | ut                |                 |                  |              |  |  |  |  |

|              | When TCS =<br>This bit is ign |                                                 |                 |                   |                 |                  |              |  |  |  |  |

| bit 1        | -                             | Clock Source S                                  | Select hit      |                   |                 |                  |              |  |  |  |  |

|              |                               | clock from T1C                                  |                 | risina edae)      |                 |                  |              |  |  |  |  |

|              |                               | clock (Fosc/2)                                  |                 |                   |                 |                  |              |  |  |  |  |

| bit 0        | Unimplemen                    | ted: Read as '                                  | )'              |                   |                 |                  |              |  |  |  |  |

| Note 1: C    | hanging the value             | ue of TxCON w                                   | hile the timer  | is running (TON   | l = 1) causes t | he timer prescal | e counter to |  |  |  |  |

## **REGISTER 11-1:** T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup>

Note 1: Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

| R/W-0                | U-0                                 | R/W-0                                   | U-0              | U-0               | R-0              | R-0              | R-0             |

|----------------------|-------------------------------------|-----------------------------------------|------------------|-------------------|------------------|------------------|-----------------|

| SPIEN <sup>(1)</sup> | _                                   | SPISIDL                                 | _                | _                 | SPIBEC2          | SPIBEC1          | SPIBEC0         |

| bit 15               |                                     |                                         |                  |                   |                  |                  | bit 8           |

|                      |                                     |                                         |                  |                   |                  |                  |                 |

| R-0                  | R/C-0, HS                           | R/W-0                                   | R/W-0            | R/W-0             | R/W-0            | R-0              | R-0             |

| SRMPT                | SPIROV                              | SRXMPT                                  | SISEL2           | SISEL1            | SISEL0           | SPITBF           | SPIRBF          |

| bit 7                |                                     |                                         |                  |                   |                  |                  | bit 0           |

| Legend:              |                                     | C = Clearable                           | bit              | HS = Hardwa       | re Settable bit  |                  |                 |

| R = Readable         | e bit                               | W = Writable b                          | pit              | U = Unimpler      | nented bit, read | d as '0'         |                 |

| -n = Value at        | POR                                 | '1' = Bit is set                        |                  | '0' = Bit is cle  |                  | x = Bit is unkr  | nown            |

|                      |                                     |                                         |                  |                   |                  |                  |                 |

| bit 15               | SPIEN: SPIX                         | Enable bit <sup>(1)</sup>               |                  |                   |                  |                  |                 |

|                      | 1 = Enables r<br>0 = Disables r     | nodule and con<br>module                | figures SCKx,    | SDOx, SDIx a      | nd SSx as seria  | al port pins     |                 |

| bit 14               | Unimplemen                          | ted: Read as 'o                         | ,                |                   |                  |                  |                 |

| bit 13               | SPISIDL: Sto                        | p in Idle Mode I                        | pit              |                   |                  |                  |                 |

|                      |                                     | ue module oper<br>module operati        |                  |                   | e mode           |                  |                 |

| bit 12-11            | Unimplemen                          | ted: Read as 'o                         | '                |                   |                  |                  |                 |

| bit 10-8             | SPIBEC<2:0                          | >: SPIx Buffer E                        | lement Count     | bits (valid in E  | nhanced Buffer   | mode)            |                 |

|                      | Master mode:<br>Number of SF        | <u>:</u><br>PI transfers that           | are pending.     |                   |                  |                  |                 |

|                      | <u>Slave mode:</u><br>Number of SF  | PI transfers that                       | are unread.      |                   |                  |                  |                 |

| bit 7                | SRMPT: Shift                        | Register (SPIx                          | SR) Empty bit    | (valid in Enhar   | nced Buffer mo   | de)              |                 |

|                      |                                     | ft register is em<br>ft register is not |                  | to send or rece   | eive             |                  |                 |

| bit 6                | SPIROV: Rec                         | eive Overflow F                         | lag bit          |                   |                  |                  |                 |

|                      | •                                   | te/word is comp<br>e SPIxBUF regi       | •                | and discarded     | . The user softw | vare has not rea | ad the previous |

|                      | 0 = No overfl                       | ow has occurre                          | d                |                   |                  |                  |                 |

| bit 5                |                                     | ceive FIFO Em                           |                  | Enhanced But      | ffer mode)       |                  |                 |

|                      |                                     | FIFO is empty<br>FIFO is not emp        |                  |                   |                  |                  |                 |

| bit 4-2              | SISEL<2:0>:                         | SPIx Buffer Inte                        | errupt Mode bi   | its (valid in Enh | anced Buffer m   | node)            |                 |

|                      |                                     | pt when SPIx t                          |                  |                   |                  |                  |                 |

|                      |                                     | pt when last bit<br>pt when the las     |                  |                   |                  |                  |                 |

|                      |                                     | ipt when one da                         |                  |                   |                  |                  | one open spot   |

|                      | 011 = Interru                       | pt when SPIx re                         | eceive buffer is | s full (SPIRBF    | bit is set)      |                  |                 |

|                      |                                     | ipt when SPIx re<br>ipt when data is    |                  |                   |                  | a aat)           |                 |

|                      | 000 = Interru                       | ipt when the la<br>IPT bit set)         |                  |                   | •                | ,                | uffer is empty  |

|                      | SPIEN = 1, the<br>Peripheral Pin \$ | se functions mu<br>Select (PPS)" f      |                  |                   | Pn pins before   | use. See Sect    | ion 10.4        |

### REGISTER 15-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0                 | R/W-0    | U-0   | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|-----------------------|----------|-------|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV <sup>(1)</sup> | UTXISEL0 |       | UTXBRK    | UTXEN <sup>(2)</sup> | UTXBF | TRMT  |

| bit 15   |                       |          |       |           |                      |       | bit 8 |

|          |                       |          |       |           |                      |       |       |

| R/W-0    | R/W-0                 | R/W-0    | R-1   | R-0       | R-0                  | R/C-0 | R-0   |

| URXISEL1 | URXISEL0              | ADDEN    | RIDLE | PERR      | FERR                 | OERR  | URXDA |

| Legend:           | C = Clearable bit | HC = Hardware Clearable bit    |                |

|-------------------|-------------------|--------------------------------|----------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as | 0'             |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x =       | Bit is unknown |

bit 15,13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits

11 = Reserved; do not use

bit 7

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

#### bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit<sup>(1)</sup>

| DIL 14  |                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IREN = 0:                                                                                                                                                                                                                                                                                                                                                                                            |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <u>IREN = 1:</u>                                                                                                                                                                                                                                                                                                                                                                                     |