#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

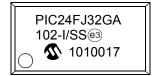

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga104t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

· Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

| TABLE     | 4-5: | INTE   | RRUPT   | CONTR   | ROLLER  | REGIS  | STER M   | AP       |          |       |          |          |          |         |          |          |               |   |

|-----------|------|--------|---------|---------|---------|--------|----------|----------|----------|-------|----------|----------|----------|---------|----------|----------|---------------|---|

| File Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0         |   |

| INTCON1   | 0080 | NSTDIS | _       | _       | _       | _      | _        | _        | —        |       |          | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _             | f |

| INTCON2   | 0082 | ALTIVT | DISI    | _       | _       | _      | _        | _        | _        | _     | _        | _        | _        |         | INT2EP   | INT1EP   | INT0EP        | T |

| IFS0      | 0084 | _      | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF  | OC2IF    | IC2IF    | _        | T1IF    | OC1IF    | IC1IF    | <b>INT0IF</b> | T |

| IFS1      | 0086 | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | OC4IF    | OC3IF    | _        | _     | _        | _        | INT1IF   | CNIF    | CMIF     | MI2C1IF  | SI2C1IF       |   |

| IFS2      | 0088 | _      | _       | PMPIF   | _       | —      | _        | OC5IF    | —        | IC5IF | IC4IF    | IC3IF    | —        | _       | —        | SPI2IF   | SPF2IF        |   |

| IFS3      | 008A |        | RTCIF   |         | _       | _      | _        | _        | _        | _     | —        | _        | _        |         | MI2C2IF  | SI2C2IF  | _             |   |

| IFS4      | 008C | _      | _       | CTMUIF  | _       | _      | _        | _        | LVDIF    | —     | —        | _        | —        | CRCIF   | U2ERIF   | U1ERIF   | _             |   |

| IEC0      | 0094 | _      | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE  | OC2IE    | IC2IE    | —        | T1IE    | OC1IE    | IC1IE    | INTOIE        |   |

| IEC1      | 0096 | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | OC4IE    | OC3IE    | _        | _     | —        | _        | INT1IE   | CNIE    | CMIE     | MI2C1IE  | SI2C1IE       |   |

| IEC2      | 0098 | _      | _       | PMPIE   | _       | _      | _        | OC5IE    | _        | IC5IE | IC4IE    | IC3IE    | —        | _       | _        | SPI2IE   | SPF2IE        |   |

| IEC3      | 009A | _      | RTCIE   |         | _       | —      | _        | —        | —        | —     | —        | _        | —        | _       | MI2C2IE  | SI2C2IE  | —             |   |

| IEC4      | 009C | _      | _       | CTMUIE  | _       | _      | _        | _        | LVDIE    | —     | —        | _        | —        | CRCIE   | U2ERIE   | U1ERIE   | _             |   |

| IPC0      | 00A4 |        | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2   | OC1IP1   | OC1IP0   | _     | IC1IP2   | IC1IP1   | IC1IP0   |         | INT0IP2  | INT0IP1  | INT0IP0       |   |

| IPC1      | 00A6 | _      | T2IP2   | T2IP1   | T2IP0   | —      | OC2IP2   | OC2IP1   | OC2IP0   | —     | IC2IP2   | IC2IP1   | IC2IP0   | _       | —        | _        | —             |   |

| IPC2      | 00A8 |        | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2  | SPI1IP1  | SPI1IP0  | _     | SPF1IP2  | SPF1IP1  | SPF1IP0  |         | T3IP2    | T3IP1    | T3IP0         |   |

| IPC3      | 00AA |        | _       | _       | _       | _      | _        | _        | _        | _     | AD1IP2   | AD1IP1   | AD1IP0   |         | U1TXIP2  | U1TXIP1  | U1TXIP0       |   |

| IPC4      | 00AC | _      | CNIP2   | CNIP1   | CNIP0   | —      | CMIP2    | CMIP1    | CMIP0    | —     | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0      |   |

| IPC5      | 00AE |        | _       | _       | _       | _      | _        | _        | _        | _     | —        | _        | _        |         | INT1IP2  | INT1IP1  | INT1IP0       |   |

| IPC6      | 00B0 | _      | T4IP2   | T4IP1   | T4IP0   | —      | OC4IP2   | OC4IP1   | OC4IP0   | —     | OC3IP2   | OC3IP1   | OC3IP0   | _       | _        | _        | _             |   |

| IPC7      | 00B2 | —      | U2TXIP2 | U2TXIP1 | U2TXIP0 | —      | U2RXIP2  | U2RXIP1  | U2RXIP0  | —     | INT2IP2  | INT2IP1  | INT2IP0  | —       | T5IP2    | T5IP1    | T5IP0         |   |

| IPC8      | 00B4 |        | _       | _       | _       | _      | _        | _        | _        | _     | SPI2IP2  | SPI2IP1  | SPI2IP0  |         | SPF2IP2  | SPF2IP1  | SPF2IP0       |   |

| IPC9      | 00B6 |        | IC5IP2  | IC5IP1  | IC5IP0  | _      | IC4IP2   | IC4IP1   | IC4IP0   | _     | IC3IP2   | IC3IP1   | IC3IP0   |         | _        | _        | _             |   |

| IPC10     | 00B8 | _      | _       |         | _       | —      | _        | —        | —        | —     | OC5IP2   | OC5IP1   | OC5IP0   | _       | —        | _        | —             |   |

| IPC11     | 00BA |        | _       | _       | _       | _      | _        | _        | _        | _     | PMPIP2   | PMPIP1   | PMPIP0   |         | _        | _        | _             |   |

| IPC12     | 00BC |        | _       | _       | _       | _      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _     | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 |         | _        | _        | _             |   |

| IPC15     | 00C2 | _      | _       | —       | _       | —      | RTCIP2   | RTCIP1   | RTCIP0   | —     | —        | -        | _        | _       | _        | —        | —             | Γ |

| IPC16     | 00C4 |        | CRCIP2  | CRCIP1  | CRCIP0  |        | U2ERIP2  | U2ERIP1  | U2ERIP0  | _     | U1ERIP2  | U1ERIP1  | U1ERIP0  | _       | _        | _        | _             |   |

| IPC18     | 00C8 |        |         |         | _       | _      |          | _        | _        |       | _        | _        | —        | _       | LVDIP2   | LVDIP1   | LVDIP0        | Ι |

| IPC19     | 00CA | _      | _       |         | _       | —      | _        | _        | _        |       | CTMUIP2  | CTMUIP1  | CTMUIP0  | _       | _        | —        | —             | ſ |

| INTTREG   | 00E0 | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM        | ĩ |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All

Resets

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

4444

4440

4444

0044

4444

0004

4440

4444

0044

4440

0040 0040

0440

0400

4440

0004

0040

0000

#### TABLE 4-23: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      | -      | -      | DPSLP  | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   |       | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _      | _      |       | _     | -      | —      | _     | 0100          |

| OSCTUN    | 0748 | _      |        | _      |        |        | _      |        | _      | -       |        | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON   | 074E | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _      | _      |       | _     | _      | _      | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-24: DEEP SLEEP REGISTER MAP

| File Name | Addr                                                                   | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8      | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0   | All<br>Resets <sup>(1)</sup> |

|-----------|------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|---------|------------|-------------|-----------|-------|-------|-------|--------|-------|---------|------------------------------|

| DSCON     | 758                                                                    | DSEN   |        |        | —      | _      | _      | _       | _          | _           | _         | —     |       | -     | —      | DSBOR | RELEASE | 0000                         |

| DSWAKE    | 075A                                                                   | _      | _      | _      | _      | _      | _      | _       | DSINT0     | DSFLT       | _         | _     | DSWDT | DSRTC | DSMCLR | _     | DSPOR   | 0001                         |

| DSGPR0    | 075C                                                                   |        |        |        |        |        |        | Deep SI | eep Genera | I Purpose R | egister 0 |       |       |       |        |       |         | 0000                         |

| DSGPR1    | 075E                                                                   |        |        |        |        |        |        | Deep SI | eep Genera | I Purpose R | egister 1 |       |       |       |        |       |         | 0000                         |

| Legend:   | — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |        |        |        |        |        |        |         |            |             |           |       |       |       |        |       |         |                              |

Note 1: The Deep Sleep registers are only reset on a VDD POR event.

#### TABLE 4-25: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3       | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|---------|-------------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | _     | _     | _     | ERASE | _     | _       | NVMOP3      | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | —      | _      | —      | _      | —      | —      | —     | —     |       |       | ١     | VMKEY R | egister<7:0 | >      |        |        | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-26: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | —      | —      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      |        | ADC1MD | 0000          |

| PMD2      | 0772 | _      | _      | _      | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | _      | _     | _     | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 | _      | _      |        | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _     |       | _      | _      | _      | I2C2MD | _      | 0000          |

| PMD4      | 0776 | _      | _      | _      | _      | _      | —      | —      | _     | —      |       |       | —      | REFOMD | CTMUMD | LVDMD  | —      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Interrupt Source          | Vector | IVT Address | AIVT    | Inte     | errupt Bit Locat | ions         |

|---------------------------|--------|-------------|---------|----------|------------------|--------------|

| interrupt Source          | Number | IVI Address | Address | Flag     | Enable           | Priority     |

| ADC1 Conversion Done      | 13     | 00002Eh     | 00012Eh | IFS0<13> | IEC0<13>         | IPC3<6:4>    |

| Comparator Event          | 18     | 000038h     | 000138h | IFS1<2>  | IEC1<2>          | IPC4<10:8>   |

| CRC Generator             | 67     | 00009Ah     | 00019Ah | IFS4<3>  | IEC4<3>          | IPC16<14:12> |

| CTMU Event                | 77     | 0000AEh     | 0001AEh | IFS4<13> | IEC4<13>         | IPC19<6:4>   |

| External Interrupt 0      | 0      | 000014h     | 000114h | IFS0<0>  | IEC0<0>          | IPC0<2:0>    |

| External Interrupt 1      | 20     | 00003Ch     | 00013Ch | IFS1<4>  | IEC1<4>          | IPC5<2:0>    |

| External Interrupt 2      | 29     | 00004Eh     | 00014Eh | IFS1<13> | IEC1<13>         | IPC7<6:4>    |

| I2C1 Master Event         | 17     | 000036h     | 000136h | IFS1<1>  | IEC1<1>          | IPC4<6:4>    |

| I2C1 Slave Event          | 16     | 000034h     | 000134h | IFS1<0>  | IEC1<0>          | IPC4<2:0>    |

| I2C2 Master Event         | 50     | 000078h     | 000178h | IFS3<2>  | IEC3<2>          | IPC12<10:8>  |

| I2C2 Slave Event          | 49     | 000076h     | 000176h | IFS3<1>  | IEC3<1>          | IPC12<6:4>   |

| Input Capture 1           | 1      | 000016h     | 000116h | IFS0<1>  | IEC0<1>          | IPC0<6:4>    |

| Input Capture 2           | 5      | 00001Eh     | 00011Eh | IFS0<5>  | IEC0<5>          | IPC1<6:4>    |

| Input Capture 3           | 37     | 00005Eh     | 00015Eh | IFS2<5>  | IEC2<5>          | IPC9<6:4>    |

| Input Capture 4           | 38     | 000060h     | 000160h | IFS2<6>  | IEC2<6>          | IPC9<10:8>   |

| Input Capture 5           | 39     | 000062h     | 000162h | IFS2<7>  | IEC2<7>          | IPC9<14:12>  |

| Input Change Notification | 19     | 00003Ah     | 00013Ah | IFS1<3>  | IEC1<3>          | IPC4<14:12>  |

| LVD Low-Voltage Detect    | 72     | 0000A4h     | 0001A4h | IFS4<8>  | IEC4<8>          | IPC18<2:0>   |

| Output Compare 1          | 2      | 000018h     | 000118h | IFS0<2>  | IEC0<2>          | IPC0<10:8>   |

| Output Compare 2          | 6      | 000020h     | 000120h | IFS0<6>  | IEC0<6>          | IPC1<10:8>   |

| Output Compare 3          | 25     | 000046h     | 000146h | IFS1<9>  | IEC1<9>          | IPC6<6:4>    |

| Output Compare 4          | 26     | 000048h     | 000148h | IFS1<10> | IEC1<10>         | IPC6<10:8>   |

| Output Compare 5          | 41     | 000066h     | 000166h | IFS2<9>  | IEC2<9>          | IPC10<6:4>   |

| Parallel Master Port      | 45     | 00006Eh     | 00016Eh | IFS2<13> | IEC2<13>         | IPC11<6:4>   |

| Real-Time Clock/Calendar  | 62     | 000090h     | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

| SPI1 Error                | 9      | 000026h     | 000126h | IFS0<9>  | IEC0<9>          | IPC2<6:4>    |

| SPI1 Event                | 10     | 000028h     | 000128h | IFS0<10> | IEC0<10>         | IPC2<10:8>   |

| SPI2 Error                | 32     | 000054h     | 000154h | IFS2<0>  | IEC2<0>          | IPC8<2:0>    |

| SPI2 Event                | 33     | 000056h     | 000156h | IFS2<1>  | IEC2<1>          | IPC8<6:4>    |

| Timer1                    | 3      | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>          | IPC0<14:12>  |

| Timer2                    | 7      | 000022h     | 000122h | IFS0<7>  | IEC0<7>          | IPC1<14:12>  |

| Timer3                    | 8      | 000024h     | 000124h | IFS0<8>  | IEC0<8>          | IPC2<2:0>    |

| Timer4                    | 27     | 00004Ah     | 00014Ah | IFS1<11> | IEC1<11>         | IPC6<14:12>  |

| Timer5                    | 28     | 00004Ch     | 00014Ch | IFS1<12> | IEC1<12>         | IPC7<2:0>    |

| UART1 Error               | 65     | 000096h     | 000196h | IFS4<1>  | IEC4<1>          | IPC16<6:4>   |

| UART1 Receiver            | 11     | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>         | IPC2<14:12>  |

| UART1 Transmitter         | 12     | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>         | IPC3<2:0>    |

| UART2 Error               | 66     | 000098h     | 000198h | IFS4<2>  | IEC4<2>          | IPC16<10:8>  |

| UART2 Receiver            | 30     | 000050h     | 000150h | IFS1<14> | IEC1<14>         | IPC7<10:8>   |

| UART2 Transmitter         | 31     | 000052h     | 000152h | IFS1<15> | IEC1<15>         | IPC7<14:12>  |

# TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| [            |                                                       |                                 |                                |                   |                 |                  |       |

|--------------|-------------------------------------------------------|---------------------------------|--------------------------------|-------------------|-----------------|------------------|-------|

| R/W-0        | U-0                                                   | U-0                             | U-0                            | U-0               | U-0             | U-0              | U-0   |

| NSTDIS       |                                                       | —                               | —                              | —                 | —               | —                | —     |

| bit 15       |                                                       |                                 |                                |                   |                 |                  | bit 8 |

|              |                                                       |                                 |                                |                   |                 |                  |       |

| U-0          | U-0                                                   | U-0                             | R/W-0                          | R/W-0             | R/W-0           | R/W-0            | U-0   |

| _            | —                                                     | —                               | MATHERR                        | ADDRERR           | STKERR          | OSCFAIL          | _     |

| bit 7        |                                                       |                                 |                                |                   |                 |                  | bit 0 |

|              |                                                       |                                 |                                |                   |                 |                  |       |

| Legend:      |                                                       |                                 |                                |                   |                 |                  |       |

| R = Readab   | le bit                                                | W = Writable                    | e bit                          | U = Unimplem      | ented bit, read | d as '0'         |       |

| -n = Value a | t POR                                                 | '1' = Bit is se                 | et                             | '0' = Bit is clea | ared            | x = Bit is unkno | own   |

| bit 14-5     | 1 = Interrupt r<br>0 = Interrupt r<br>Unimplement     | nesting is enal<br>ted: Read as | bled<br>'0'                    |                   |                 |                  |       |

| bit 4        | <b>MATHERR:</b> A<br>1 = Overflow t<br>0 = Overflow t | trap has occu                   |                                | t                 |                 |                  |       |

| bit 3        |                                                       | •                               | Trap Status bit                |                   |                 |                  |       |

|              | 1 = Address e<br>0 = Address e                        | error trap has                  | occurred                       |                   |                 |                  |       |

| bit 2        | STKERR: Sta                                           | ick Error Trap                  | Status bit                     |                   |                 |                  |       |

|              | 1 = Stack erro<br>0 = Stack erro                      |                                 |                                |                   |                 |                  |       |

| bit 1        | OSCFAIL: Os                                           | cillator Failure                | e Trap Status bit              | :                 |                 |                  |       |

|              | 1 = Oscillator<br>0 = Oscillator                      | •                               | as occurred<br>as not occurred |                   |                 |                  |       |

| bit 0        | Unimplement                                           | ted: Read as                    | '0'                            |                   |                 |                  |       |

|              |                                                       |                                 |                                |                   |                 |                  |       |

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

|                    | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | R/W-1            | R/W-0           | R/W-0  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| —                  | T4IP2                                                                                                                                       | T4IP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T4IP0                                                                                                  |                   | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15             |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 | bit    |

|                    |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| U-0                | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                  | U-0               | U-0              | U-0             | U-0    |

|                    | OC3IP2                                                                                                                                      | OC3IP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OC3IP0                                                                                                 |                   |                  |                 |        |

| bit 7              |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 | bit    |

| Legend:            |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| R = Readat         | ole bit                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                    | U = Unimplei      | mented bit, read | d as '0'        |        |

| -n = Value a       | at POR                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        | '0' = Bit is cle  | eared            | x = Bit is unkr | nown   |

|                    |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

| bit 15             | Unimplemer                                                                                                                                  | nted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0'                                                                                                     |                   |                  |                 |        |

| bit 14-12          | <b>T4IP&lt;2:0&gt;:</b> ⊺                                                                                                                   | Timer4 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Priority bits                                                                                          |                   |                  |                 |        |

|                    | 111 = Interru                                                                                                                               | pt is priority 7 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | highest priority                                                                                       | / interrupt)      |                  |                 |        |

|                    | •                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                    | •                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                    |                                                                                                                                             | pt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |                   |                  |                 |        |

|                    | 001 = menu                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |

|                    |                                                                                                                                             | ipt is priority i<br>ipt source is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | abled                                                                                                  |                   |                  |                 |        |

| bit 11             | 000 = Interru                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                   |                  |                 |        |