### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 57                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564l60l3bcoqr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.3 Device comparison

|          | Feature                     | SPC56EL60              | SPC56EL54                        |  |  |  |  |

|----------|-----------------------------|------------------------|----------------------------------|--|--|--|--|

|          | Туре                        |                        | 200z4<br>coupled operation)      |  |  |  |  |

|          | Architecture                | Har                    | vard                             |  |  |  |  |

|          | Execution speed             | 0–120 MHz              | z (+2% FM)                       |  |  |  |  |

|          | DMIPS intrinsic performance | >240                   | MIPS                             |  |  |  |  |

|          | SIMD (DSP + FPU)            | Ye                     | es                               |  |  |  |  |

| CPU      | MMU                         | 16 e                   | entry                            |  |  |  |  |

|          | Instruction set PPC         | Yes                    |                                  |  |  |  |  |

|          | Instruction set VLE         | Ye                     | es                               |  |  |  |  |

|          | Instruction cache           | 4 KB, EDC              |                                  |  |  |  |  |

|          | MPU-16 regions              | Yes, replicated module |                                  |  |  |  |  |

|          | Semaphore unit (SEMA4)      | Yes                    |                                  |  |  |  |  |

| Duese    | Core bus                    | AHB, 32-bit add        | ress, 64-bit data                |  |  |  |  |

| Buses    | Internal periphery bus      | 32-bit addres          | s, 32-bit data                   |  |  |  |  |

| Crossbar | Master × slave ports        |                        | Mode: 4 × 3<br>allel Mode: 6 × 3 |  |  |  |  |

|          | Flash                       | 1 MB, ECC, RWW         | 768 KB, ECC, RWW                 |  |  |  |  |

| Memory   | Static RAM (SRAM)           | 128 KB, ECC            | 96 KB, ECC                       |  |  |  |  |

exceptions, etc.), allowing the development tool to interpolate what transpires between the discontinuities. Thus, static code may be traced.

- Watchpoint messaging (WPM) via the auxiliary port

- Watchpoint trigger enable of program and/or data trace messaging

- Data tracing of instruction fetches via private opcodes

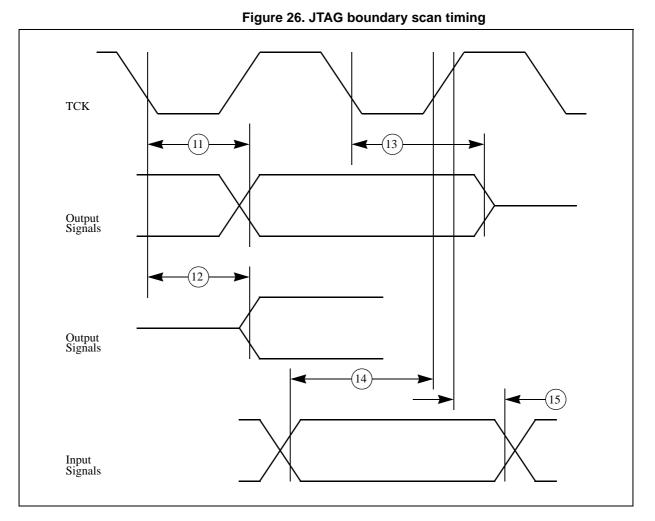

# 1.5.39 IEEE 1149.1 JTAG Controller (JTAGC)

The JTAGC block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with 5 pins:

- TDI

- TMS

- TCK

- TDO

- JCOMP

- Selectable modes of operation include JTAGC/debug or normal system operation

- 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS

- IDCODE

- EXTEST

- SAMPLE

- SAMPLE/PRELOAD

- 3 test data registers: a bypass register, a boundary scan register, and a device identification register. The size of the boundary scan register is parameterized to support a variety of boundary scan chain lengths.

- TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

|       | Table 4. LQ                  | (FP144 pin function | n summary (continu | ed)            |

|-------|------------------------------|---------------------|--------------------|----------------|

| Pin # | Port/function                | Peripheral          | Output function    | Input function |

|       |                              | SIUL                | GPIO[54]           | GPIO[54]       |

| 24    | DIG                          | DSPI_0              | CS2                | —              |

| 34    | D[6]                         | FlexPWM_0           | X[3]               | X[3]           |

|       |                              | FlexPWM_0           | _                  | FAULT[1]       |

| 35    | V <sub>SS_LV_PLL0_PLL1</sub> |                     |                    |                |

| 36    | V <sub>DD_LV_PLL0_PLL1</sub> |                     | _                  |                |

|       |                              | SIUL                | GPIO[55]           | GPIO[55]       |

| 07    |                              | DSPI_1              | CS3                |                |

| 37    | D[7] -                       | DSPI_0              | CS4                |                |

|       | -                            | SWG                 | analog output      |                |

| 38    | FCCU_F[0]                    | FCCU                | F[0]               | F[0]           |

| 39    | V <sub>DD_LV_COR</sub>       |                     | —                  |                |

| 40    | V <sub>SS_LV_COR</sub>       |                     | _                  |                |

|       |                              | SIUL                | —                  | GPIO[33]       |

| 41    | C[1]                         | ADC_0               | _                  | AN[2]          |

|       |                              | SIUL                | _                  | GPIO[68]       |

| 42    | E[4] -                       | ADC_0               | _                  | AN[7]          |

|       |                              | SIUL                | _                  | GPIO[23]       |

| 43    | B[7]                         | LINFlexD_0          | _                  | RXD            |

|       |                              | ADC_0               | _                  | AN[0]          |

|       |                              | SIUL                | _                  | GPIO[69]       |

| 44    | E[5] -                       | ADC_0               | —                  | AN[8]          |

|       |                              | SIUL                | _                  | GPIO[34]       |

| 45    | C[2]                         | ADC_0               | _                  | AN[3]          |

|       |                              | SIUL                | —                  | GPIO[70]       |

| 46    | E[6]                         | ADC_0               | _                  | AN[4]          |

|       |                              | SIUL                | _                  | GPIO[24]       |

| 47    | B[8]                         | eTimer_0            |                    | ETC[5]         |

|       | -                            | ADC_0               |                    | AN[1]          |

| 40    |                              | SIUL                | —                  | GPIO[71]       |

| 48    | E[7] -                       | ADC_0               | —                  | AN[6]          |

| 10    | FIG                          | SIUL                | _                  | GPIO[66]       |

| 49    | E[2] -                       | ADC_0               | —                  | AN[5]          |

| 50    | V <sub>DD_HV_ADR0</sub>      |                     |                    | 1              |

| 51    | V <sub>SS_HV_ADR0</sub>      |                     | _                  |                |

|       |                              |                     |                    |                |

Table 4. LQFP144 pin function summary (continued)

|       |                         | 2FP144 pin function | n summary (continu | ea)            |

|-------|-------------------------|---------------------|--------------------|----------------|

| Pin # | Port/function           | Peripheral          | Output function    | Input function |

|       |                         | SIUL                | —                  | GPIO[25]       |

| 52    | B[9]                    | ADC_0<br>ADC_1      | _                  | AN[11]         |

|       |                         | SIUL                | —                  | GPIO[26]       |

| 53    | B[10]                   | ADC_0<br>ADC_1      | _                  | AN[12]         |

|       |                         | SIUL                | —                  | GPIO[27]       |

| 54    | B[11]                   | ADC_0<br>ADC_1      | _                  | AN[13]         |

|       |                         | SIUL                | —                  | GPIO[28]       |

| 55    | B[12]                   | ADC_0<br>ADC_1      | _                  | AN[14]         |

| 56    | V <sub>DD_HV_ADR1</sub> |                     | —                  |                |

| 57    | V <sub>SS_HV_ADR1</sub> |                     | —                  |                |

| 58    | V <sub>DD_HV_ADV</sub>  |                     | —                  |                |

| 59    | V <sub>SS_HV_ADV</sub>  |                     | —                  |                |

|       |                         | SIUL                | —                  | GPIO[29]       |

| 60    | B[13]                   | LINFlexD_1          | —                  | RXD            |

|       |                         | ADC_1               | —                  | AN[0]          |

| 61    | E[9]                    | SIUL                | —                  | GPIO[73]       |

| 01    | L[9]                    | ADC_1               | —                  | AN[7]          |

|       |                         | SIUL                | —                  | GPIO[31]       |

| 62    | B[15]                   | SIUL                | —                  | EIRQ[20]       |

|       |                         | ADC_1               | —                  | AN[2]          |

| 63    | E[10]                   | SIUL                | —                  | GPIO[74]       |

| 03    | E[10]                   | ADC_1               | —                  | AN[8]          |

|       |                         | SIUL                | —                  | GPIO[30]       |

| 64    | D[14]                   | eTimer_0            | —                  | ETC[4]         |

| 64    | B[14]                   | SIUL                | —                  | EIRQ[19]       |

|       |                         | ADC_1               | —                  | AN[1]          |

| 6F    | E[14]                   | SIUL                | —                  | GPIO[75]       |

| 65    | E[11]                   | ADC_1               | —                  | AN[4]          |

| 66    | 0101                    | SIUL                | —                  | GPIO[32]       |

| 66    | C[0]                    | ADC_1               | —                  | AN[3]          |

| 67    | E[12]                   | SIUL                | —                  | GPIO[76]       |

| 07    | E[12]                   | ADC_1               | _                  | AN[6]          |

Table 4. LQFP144 pin function summary (continued)

|       |                            | GAZ57 pin function | on summary (continu | •              |

|-------|----------------------------|--------------------|---------------------|----------------|

| Pin # | Port/function              | Peripheral         | Output function     | Input function |

|       |                            | SIUL               | GPIO[128]           | GPIO[128]      |

| C9    | 1(0)                       | eTimer_2           | ETC[0]              | ETC[0]         |

| Ca    | I[0]                       | DSPI_0             | CS4                 | _              |

|       |                            | FlexPWM_1          | —                   | FAULT[0]       |

| C10   | JCOMP                      | _                  | —                   | JCOMP          |

| 011   | 11[44]                     | SIUL               | GPIO[123]           | GPIO[123]      |

| C11   | H[11] -                    | FlexPWM_1          | A[2]                | A[2]           |

|       |                            | SIUL               | GPIO[129]           | GPIO[129]      |

| 040   | 1541                       | eTimer_2           | ETC[1]              | ETC[1]         |

| C12   | I[1] -                     | DSPI_0             | CS5                 | _              |

|       |                            | FlexPWM_1          | _                   | FAULT[1]       |

| 040   | <b>F</b> [4,4]             | SIUL               | GPIO[94]            | GPIO[94]       |

| C13   | F[14]                      | LINFlexD_1         | TXD                 |                |

|       |                            | SIUL               | GPIO[17]            | GPI0[17]       |

|       |                            | eTimer_1           | ETC[3]              | ETC[3]         |

| 014   | D[4]                       | SSCM               | DEBUG[1]            | —              |

| C14   | B[1] -                     | FlexCAN_0          | _                   | RXD            |

|       |                            | FlexCAN_1          | —                   | RXD            |

|       |                            | SIUL               | —                   | EIRQ[16]       |

| C15   | V <sub>SS_HV_IO_RING</sub> |                    |                     |                |

|       |                            | SIUL               | GPIO[4]             | GPIO[4]        |

|       |                            | eTimer_1           | ETC[0]              | ETC[0]         |

| C16   | 0[4]                       | DSPI_2             | CS1                 | _              |

| 010   | A[4]                       | eTimer_0           | ETC[4]              | ETC[4]         |

|       |                            | MC_RGM             | —                   | FAB            |

|       |                            | SIUL               | —                   | EIRQ[4]        |

|       |                            | SIUL               | GPIO[92]            | GPI0[92]       |

| C17   | F[12]                      | eTimer_1           | ETC[3]              | ETC[3]         |

|       |                            | SIUL               | —                   | EIRQ[30]       |

| D4    | FIEL                       | SIUL               | GPIO[85]            | GPIO[85]       |

| D1    | F[5] -                     | NPC                | MDO[2]              | _              |

| 20    | E[4]                       | SIUL               | GPIO[84]            | GPIO[84]       |

| D2    | F[4] -                     | NPC                | MDO[3]              | _              |

Table 5. LFBGA257 pin function summary (continued)

| D'. " |                                                      |            | n summary (continu | -              |

|-------|------------------------------------------------------|------------|--------------------|----------------|

| Pin # | Port/function                                        | Peripheral | Output function    | Input function |

| N14   | Not connected                                        |            | —                  |                |

|       |                                                      | SIUL       | GPIO[44]           | GPIO[44]       |

| N15   | C[12]                                                | eTimer_0   | ETC[5]             | ETC[5]         |

|       |                                                      | DSPI_2     | CS3                | —              |

|       |                                                      | SIUL       | GPIO[2]            | GPIO[2]        |

|       |                                                      | eTimer_0   | ETC[2]             | ETC[2]         |

| N16   | 1010                                                 | FlexPWM_0  | A[3]               | A[3]           |

| NIO   | A[2] —                                               | DSPI_2     | —                  | SIN            |

|       |                                                      | MC_RGM     | —                  | ABS[0]         |

|       |                                                      | SIUL       | —                  | EIRQ[2]        |

|       |                                                      | SIUL       | GPIO[101]          | GPIO[101]      |

| N17   | G[5]                                                 | FlexPWM_0  | X[3]               | X[3]           |

|       |                                                      | DSPI_2     | CS3                |                |

| P1    | V <sub>SS_HV_OSC</sub>                               |            | —                  |                |

| P2    | RESET                                                |            | —                  |                |

|       |                                                      | SIUL       | GPIO[54]           | GPIO[54]       |

| P3    | D[6]                                                 | DSPI_0     | CS2                | —              |

| 15    | D[0]                                                 | FlexPWM_0  | X[3]               | X[3]           |

|       |                                                      | FlexPWM_0  | —                  | FAULT[1]       |

| P4    | V <sub>DD_LV_PLL0_PLL1</sub>                         |            |                    |                |

| P5    | $V_{\text{DD}\_\text{LV}\_\text{CORE}\_\text{RING}}$ |            | —                  |                |

| P6    | $V_{SS\_LV\_CORE\_RING}$                             |            | —                  |                |

|       |                                                      | SIUL       | _                  | GPIO[24]       |

| P7    | B[8]                                                 | eTimer_0   | _                  | ETC[5]         |

|       |                                                      | ADC_0      | —                  | AN[1]          |

| P8    | Not connected                                        |            | _                  |                |

| P9    | V <sub>SS_HV_IO_RING</sub>                           |            | _                  |                |

| P10   | V <sub>DD_HV_IO_RING</sub>                           |            | —                  |                |

|       |                                                      | SIUL       | —                  | GPIO[30]       |

| P11   | B[14] —                                              | eTimer_0   | —                  | ETC[4]         |

|       | נדיןס                                                | SIUL       | —                  | EIRQ[19]       |

|       |                                                      | ADC_1      |                    | AN[1]          |

| P12   | V <sub>DD_LV_CORE_RING</sub>                         |            | _                  |                |

| P13   | V <sub>SS_LV_CORE_RING</sub>                         |            |                    |                |

| P14   | V <sub>DD_HV_IO_RING</sub>                           |            | _                  |                |

Table 5. LFBGA257 pin function summary (continued)

- 2. This pad contains a weak pull-up.

- 3. EXTAL is an "Output" in "crystal" mode, and is an "Input" in "ext clock" mode.

- 4. In XOSC Bypass Mode, the analog portion of crystal oscillator (amplifier) is disabled. An external clock can be applied at EXTAL as an input. In XOSC Normal Mode, EXTAL is an output

- 5. This pad contains a weak pull-down.

- 6. RESET output shall be considered valid only after the 3.3V supply reaches its stable value.

Note: None of system pins (except RESET) provides an open drain output.

# 2.4 Pin muxing

Table 8 defines the pin list and muxing for this device.

Each entry of *Table 8* shows all the possible configurations for each pin, via the alternate functions. The default function assigned to each pin after reset is indicated by ALT0.

- Note: Pins labeled "NC" are to be left unconnected. Any connection to an external circuit or voltage may cause unpredictable device behavior or damage.

- Note: Pins labeled "Reserved" are to be tied to ground. Not doing so may cause unpredictable device behavior.

|   | Port  |            |            | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pa<br>spe  | Pad<br>eed <sup>(1)</sup> Pir |            | Pin #      | in #     |    |

|---|-------|------------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-------------------------------|------------|------------|----------|----|

|   | name  | PCR        | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0                    | 100<br>pkg | 144<br>pkg | 25<br>pk |    |

| l |       |            | SIUL       | GPIO[42]           | ALT0    | GPIO[42]  |                       |                        |            |                               |            |            |          |    |

|   |       |            | DSPI_2     | CS2                | ALT1    | _         |                       |                        |            |                               |            |            |          |    |

|   | C[10] | PCR[42]    | FlexPWM_0  | A[3]               | ALT3    | A[3]      | PSMI[23];<br>PADSEL=1 |                        | М          | S                             | 78         | 111        | A15      |    |

|   |       |            | FlexPWM_0  | _                  | _       | FAULT[1]  | PSMI[17];<br>PADSEL=0 |                        |            |                               |            |            |          |    |

| Ì |       | PCR[43]    | SIUL       | GPIO[43]           | ALT0    | GPIO[43]  |                       |                        |            |                               |            |            |          |    |

|   | C[11] |            | eTimer_0   | ETC[4]             | ALT1    | ETC[4]    | PSMI[7];<br>PADSEL=1  |                        | М          | s                             | 55         | 80         | M1       |    |

|   |       |            | DSPI_2     | CS2                | ALT2    | _         |                       |                        |            |                               |            |            |          |    |

|   |       | 2] PCR[44] | SIUL       | GPIO[44]           | ALT0    | GPIO[44]  | _                     |                        |            |                               |            |            |          |    |

|   | C[12] |            | eTimer_0   | ETC[5]             | ALT1    | ETC[5]    | PSMI[8];<br>PADSEL=0  |                        | _          | М                             | S          | 56         | 82       | N1 |

|   |       |            | DSPI_2     | CS3                | ALT2    | —         | _                     |                        |            |                               |            |            |          |    |

|   |       |            | SIUL       | GPIO[45]           | ALT0    | GPIO[45]  | —                     |                        |            |                               |            |            |          |    |

|   |       |            | eTimer_1   | ETC[1]             | ALT1    | ETC[1]    | PSMI[10];<br>PADSEL=0 |                        |            |                               |            |            | F15      |    |

|   | C[13] | PCR[45]    | CTU_0      | —                  | —       | EXT_IN    | PSMI[0];<br>PADSEL=0  | _                      | М          | S                             | 71         | 101        |          |    |

|   |       |            | FlexPWM_0  | _                  | _       | EXT_SYNC  | PSMI[15];<br>PADSEL=0 |                        |            |                               |            |            |          |    |

| Ì |       |            | SIUL       | GPIO[46]           | ALT0    | GPIO[46]  |                       |                        |            |                               |            |            |          |    |

|   | C[14] | PCR[46]    | eTimer_1   | ETC[2]             | ALT1    | ETC[2]    | PSMI[11];<br>PADSEL=1 |                        | М          | S                             | 72         | 103        | E15      |    |

|   |       |            | CTU_0      | EXT_TGR            | ALT2    |           | _                     | 1                      |            |                               |            |            |          |    |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

|      |         |             |                    | Table 8. Pi | n muxing (cor | tinued)               |                            |            |                         |            |            |            |

|------|---------|-------------|--------------------|-------------|---------------|-----------------------|----------------------------|------------|-------------------------|------------|------------|------------|

| Port | PCR     | Peripheral  | Alternate          | Output      | Input         | Input mux             | Weak pull<br>config during | Pa<br>spe  | ad<br>ed <sup>(1)</sup> |            | Pin #      |            |

| name | FUR     | Felipileiai | output<br>function | mux sel     | functions     | select                | reset                      | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|      |         | SIUL        | GPIO[50]           | ALT0        | GPIO[50]      |                       |                            |            |                         |            |            |            |

| D[2] | DCD[50] | eTimer_1    | ETC[3]             | ALT2        | ETC[3]        | PSMI[12];<br>PADSEL=1 |                            | М          | S                       |            | 140        | C5         |

| D[2] | PCR[50] | FlexPWM_0   | X[3]               | ALT3        | X[3]          | PSMI[30];<br>PADSEL=0 |                            | IVI        | 5                       |            | 140        | 05         |

|      |         | FlexRay     | —                  | —           | CB_RX         | —                     |                            |            |                         |            |            |            |

|      |         | SIUL        | GPIO[51]           | ALT0        | GPIO[51]      | —                     |                            |            |                         |            |            |            |

|      |         | FlexRay     | CB_TX              | ALT1        | _             | —                     |                            |            |                         |            |            |            |

| D[3] | PCR[51] | eTimer_1    | ETC[4]             | ALT2        | ETC[4]        | PSMI[13];<br>PADSEL=1 | -1<br> ;                   | SYM        | S                       | 89         | 128        | A7         |

|      |         | FlexPWM_0   | A[3]               | ALT3        | A[3]          | PSMI[23];<br>PADSEL=2 |                            |            |                         |            |            |            |

|      |         | SIUL        | GPIO[52]           | ALT0        | GPIO[52]      | —                     |                            |            |                         |            |            |            |

|      |         | FlexRay     | CB_TR_EN           | ALT1        | _             | —                     |                            |            |                         |            |            | В7         |

| D[4] | PCR[52] | eTimer_1    | ETC[5]             | ALT2        | ETC[5]        | PSMI[14];<br>PADSEL=2 | _                          | SYM        | S                       | 90         | 129        |            |

|      |         | FlexPWM_0   | B[3]               | ALT3        | B[3]          | PSMI[27];<br>PADSEL=2 |                            |            |                         |            |            |            |

|      |         | SIUL        | GPIO[53]           | ALT0        | GPIO[53]      | _                     |                            |            |                         |            |            | 1          |

| D[5] | PCR[53] | DSPI_0      | CS3                | ALT1        | _             | _                     |                            | М          | S                       | 22         | 33         | N3         |

|      |         | FlexPWM_0   |                    | _           | FAULT[2]      | PSMI[18];<br>PADSEL=0 |                            |            |                         |            |            | IND        |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

86/165

DocID15457 Rev 12

5

| _ |      |         |            |                     | Table 8. Pi | n muxing (cor | tinued)               |                            |            |                         |            |            |            |

|---|------|---------|------------|---------------------|-------------|---------------|-----------------------|----------------------------|------------|-------------------------|------------|------------|------------|

|   | Port | PCR     | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull<br>config during | Pa<br>spee | ad<br>ed <sup>(1)</sup> | Pin #      |            |            |

|   | name | FOR     | renpheral  | function            | mux sel     | functions     | select                | reset                      | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 257<br>pkg |

| Γ |      |         | SIUL       | GPIO[54]            | ALT0        | GPIO[54]      | —                     |                            |            |                         |            |            |            |

|   |      |         | DSPI_0     | CS2                 | ALT1        | _             | _                     |                            |            |                         |            |            |            |

|   | D[6] | PCR[54] | FlexPWM_0  | X[3]                | ALT3        | X[3]          | PSMI[30];<br>PADSEL=1 |                            | М          | S                       | 23         | 34         | P3         |

|   |      |         | FlexPWM_0  | _                   | _           | FAULT[1]      | PSMI[17];<br>PADSEL=1 |                            |            |                         |            |            |            |

| Ī |      |         | SIUL       | GPIO[55]            | ALT0        | GPIO[55]      | _                     |                            |            |                         |            |            |            |

|   | ודוס | PCR[55] | DSPI_1     | CS3                 | ALT1        | _             | _                     |                            |            | S                       | 26         | 37         | R4         |

|   | D[7] | FCR[55] | DSPI_0     | CS4                 | ALT3        | _             | _                     |                            | М          | 3                       | 20         | 57         | κ4         |

|   |      |         | SWG        | analog output       |             | _             | _                     |                            |            |                         |            |            |            |

| Ī |      |         | SIUL       | GPIO[56]            | ALT0        | GPIO[56]      | _                     |                            |            |                         |            |            |            |

|   |      |         | DSPI_1     | CS2                 | ALT1        | _             | _                     | ]                          |            |                         |            |            |            |

|   | D[8] | PCR[56] | eTimer_1   | ETC[4]              | ALT2        | ETC[4]        | PSMI[13];<br>PADSEL=2 |                            | М          | S                       | 21         | 32         | М3         |

|   |      |         | DSPI_0     | CS5                 | ALT3        | _             |                       |                            |            |                         |            |            |            |

|   |      |         | FlexPWM_0  | —                   | _           | FAULT[3]      | PSMI[19];<br>PADSEL=1 |                            |            |                         |            |            |            |

| Ī |      |         | SIUL       | GPIO[57]            | ALT0        | GPIO[57]      | _                     |                            |            |                         |            |            | 1          |

|   | D[9] | PCR[57] | FlexPWM_0  | X[0]                | ALT1        | X[0]          |                       |                            | М          | S                       | 15         | 26         | L3         |

|   |      |         | LINFlexD_1 | TXD                 | ALT2        |               | _                     | 1                          |            |                         |            |            |            |

87/165

Package pinouts and signal descriptions

96/165

DocID15457 Rev 12

|       |          |            |                    | Table 8. Pi | n muxing (cor | ntinued)              |                         |                             |            |            |            |            |     |

|-------|----------|------------|--------------------|-------------|---------------|-----------------------|-------------------------|-----------------------------|------------|------------|------------|------------|-----|

| Port  | PCR      | Peripheral | Alternate          | Output      | Input         | Input mux             | Weak pull config during | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |            |     |

| name  | FCK      | Peripheral | output<br>function | mux sel     | functions     | select                | reset                   | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 257<br>pkg |     |

| H[11] | PCR[123] | SIUL       | GPIO[123]          | ALT0        | GPIO[123]     | _                     |                         | М                           | S          |            | _          | C11        |     |

| п[т   | PCR[123] | FlexPWM_1  | A[2]               | ALT1        | A[2]          | _                     |                         | IVI                         | 5          |            | _          |            |     |

| H[12] | PCR[124] | SIUL       | GPIO[124]          | ALT0        | GPIO[124]     | _                     |                         | М                           | S          |            | _          | B10        |     |

| п[12] | PCR[124] | FlexPWM_1  | B[2]               | ALT1        | B[2]          | _                     |                         | IVI                         | 5          |            | _          | ы          |     |

|       |          | SIUL       | GPIO[125]          | ALT0        | GPIO[125]     | _                     |                         |                             |            |            |            |            |     |

| H[13] | PCR[125] | FlexPWM_1  | X[3]               | ALT1        | X[3]          | _                     |                         | М                           | s          |            | _          | G1         |     |

| []    |          | eTimer_2   | ETC[3]             | ALT2        | ETC[3]        | PSMI[42];<br>PADSEL=0 |                         |                             | _          |            |            |            |     |

|       |          | SIUL       | GPIO[126]          | ALT0        | GPIO[126]     | _                     |                         | _                           |            | S          | _          | _          |     |

| H[14] | PCR[126] | FlexPWM_1  | A[3]               | ALT1        | A[3]          | _                     |                         |                             | М          |            |            |            | A12 |

|       |          | eTimer_2   | ETC[4]             | ALT2        | ETC[4]        | _                     |                         |                             |            |            |            |            |     |

|       |          | SIUL       | GPIO[127]          | ALT0        | GPIO[127]     | _                     |                         |                             |            |            |            |            |     |

| H[15] | PCR[127] | FlexPWM_1  | B[3]               | ALT1        | B[3]          | _                     | <b>—</b>                | М                           | S          | —          | -          | J17        |     |

|       |          | eTimer_2   | ETC[5]             | ALT2        | ETC[5]        | _                     |                         |                             |            |            |            |            |     |

|       |          |            |                    |             | Port I        |                       | ·                       |                             |            |            |            | •          |     |

|       |          | SIUL       | GPIO[128]          | ALT0        | GPIO[128]     | _                     |                         |                             |            |            |            |            |     |

| I[0]  | PCR[128] | eTimer_2   | ETC[0]             | ALT1        | ETC[0]        | PSMI[39];<br>PADSEL=1 | ] _                     | М                           | S          | _          |            | C9         |     |

|       |          | DSPI_0     | CS4                | ALT2        | _             | _                     |                         |                             |            |            |            |            |     |

|       |          | FlexPWM_1  | _                  | —           | FAULT[0]      | _                     | ]                       |                             |            |            |            |            |     |

# Package pinouts and signal descriptions

|                                                    |    |                                                                               |                            | ,                            | 1                                            | 1    |

|----------------------------------------------------|----|-------------------------------------------------------------------------------|----------------------------|------------------------------|----------------------------------------------|------|

| Symbol                                             |    | Parameter                                                                     | Conditions                 | Min                          | Max                                          | Unit |

| V <sub>SS_HV_ADR0</sub><br>V <sub>SS_HV_ADR1</sub> | SR | ADC_0 ground and low reference voltage ADC_1 ground and low reference voltage | —                          | -0.1                         | 0.1                                          | ٧    |

| V <sub>DD_HV_ADV</sub>                             | SR | 3.3 V ADC supply voltage                                                      | _                          | -0.3                         | 4.5 <sup>(4), (3)</sup>                      | V    |

| $V_{SS_HV_ADV}$                                    | SR | 3.3 V ADC supply ground                                                       |                            | -0.1                         | 0.1                                          | V    |

| TV <sub>DD</sub>                                   | SR | Supply ramp rate                                                              | _                          | 3.0 × 10-6<br>(3.0<br>V/sec) | 0.5 V/µs                                     | V/µs |

| V <sub>IN</sub>                                    | SR | Voltage on any pin with respect to ground                                     | Valid only for<br>ADC pins | -0.3                         | 6.0 <sup>(4)</sup>                           | v    |

| V IN                                               |    | (V <sub>SS_HV_IOx</sub> ) or V <sub>ss_HV_ADRx</sub>                          | Relative to $V_{DD}$       | -0.3                         | V <sub>DD</sub> + 0.3 <sup>(4),</sup><br>(5) | v    |

| I <sub>INJPAD</sub>                                | SR | Injected input current on any pin during overload condition                   | —                          | -10                          | 10                                           | mA   |

| I <sub>INJSUM</sub>                                | SR | Absolute sum of all injected input currents during overload condition         | _                          | -50                          | 50                                           | mA   |

| T <sub>STG</sub>                                   | SR | Storage temperature                                                           | _                          | -55                          | 150                                          | °C   |

| Table 9. Absolute | e maximum | ratings <sup>(1)</sup> | (continued) |

|-------------------|-----------|------------------------|-------------|

|-------------------|-----------|------------------------|-------------|

1. Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Exposure to absolute maximum rating conditions for extended periods may affect device reliability or cause permanent damage to the device.

2. Any voltage between operating condition and absolute max rating can be sustained for maximum cumulative time of 10 hours.

3. Voltage overshoots during a high-to-low or low-to-high transition must not exceed 10 seconds per instance.

4. Internal structures hold the input voltage less than the maximum voltage on all pads powered by VDDE supplies, if the maximum injection current specification is met and VDDE is within the operating voltage specifications.

5.  $V_{DD}$  has to be considered equal to  $V_{DD_HV\_ADRx}$  in case of ADC pins, whilst it is  $V_{DD_HV\_IOx}$  for any other pin.

# 3.3 Recommended operating conditions

| Table 10 | . Recommended | operating | conditions | (3.3 | V) |

|----------|---------------|-----------|------------|------|----|

|----------|---------------|-----------|------------|------|----|

| Symbol                                                                     |    | Parameter                                                                                | Conditions | Min <sup>(1)</sup> | Max            | Unit |

|----------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------|------------|--------------------|----------------|------|

| V <sub>DD_HV_REG</sub>                                                     | SR | 3.3 V voltage regulator supply voltage                                                   | —          | 3.0                | 3.63           | V    |

| V <sub>DD_HV_IOx</sub>                                                     | SR | 3.3 V input/output supply voltage                                                        | —          | 3.0                | 3.63           | V    |

| V <sub>SS_HV_IOx</sub>                                                     | SR | Input/output ground voltage                                                              | —          | 0                  | 0              | V    |

| V <sub>DD_HV_FLA</sub>                                                     | SR | 3.3 V flash supply voltage                                                               | —          | 3.0                | 3.63           | V    |

| V <sub>SS_HV_FLA</sub>                                                     | SR | Flash memory ground                                                                      | —          | 0                  | 0              | V    |

| V <sub>DD_HV_OSC</sub>                                                     | SR | 3.3 V crystal oscillator amplifier supply voltage                                        | —          | 3.0                | 3.63           | V    |

| V <sub>SS_HV_OSC</sub>                                                     | SR | 3.3 V crystal oscillator amplifier reference voltage                                     | _          | 0                  | 0              | V    |

| V <sub>DD_HV_ADR0</sub> <sup>(2)</sup> ,<br>(3)<br>V <sub>DD_HV_ADR1</sub> | SR | 3.3 V / 5.0 V ADC_0 high reference voltage<br>3.3 V / 5.0 V ADC_1 high reference voltage | _          | 4.5 to<br>3.0 to   | 5.5 or<br>3.63 | V    |

| Symbol                                           |    | Parameter                                                                        | Conditions                     | Min <sup>(1)</sup> | Мах  | Unit |

|--------------------------------------------------|----|----------------------------------------------------------------------------------|--------------------------------|--------------------|------|------|

| V <sub>DD_HV_ADV</sub>                           | SR | 3.3 V ADC supply voltage                                                         | —                              | 3.0                | 3.63 | V    |

| V <sub>SS_HV_AD0</sub><br>V <sub>SS_HV_AD1</sub> | SR | ADC_0 ground and low reference voltage<br>ADC_1 ground and low reference voltage | _                              | 0                  | 0    | V    |

| V <sub>SS_HV_ADV</sub>                           | SR | 3.3 V ADC supply ground                                                          | —                              | 0                  | 0    | V    |

| V <sub>DD_LV, REGCOR</sub>                       | SR | Internal supply voltage                                                          | _                              | _                  | —    | ~    |

| V <sub>SS_LV_REGCOR</sub>                        | SR | Internal reference voltage                                                       | _                              | 0                  | 0    | V    |

| V <sub>DD_LV_CORx</sub> <sup>(2)</sup>           | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>           | SR | Internal reference voltage                                                       | —                              | 0                  | 0    | V    |

| V <sub>DD_LV_PLL</sub> <sup>(2)</sup>            | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_PLL</sub> <sup>(3)</sup>            | SR | Internal reference voltage                                                       | —                              | 0                  | 0    | V    |

| T <sub>A</sub>                                   | SR | Ambient temperature under bias                                                   | $f_{CPU} \leq 120 \text{ MHz}$ | -40                | 125  | °C   |

| TJ                                               | SR | Junction temperature under bias                                                  | —                              | -40                | 150  | °C   |

Table 10. Recommended operating conditions (3.3 V) (continued)

1. Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2.  $V_{DD\_HV\_ADR0}$  and  $V_{DD\_HV\_ADR1}$  cannot be operated at different voltages, and need to be supplied by the same voltage source.

3. VDD\_HV\_ADRx must always be applied and should be stable before LBIST starts. If this supply is not above its absolute minimum level, LBIST operations can fail.

4. Can be connected to emitter of external NPN. Low voltage supplies are not under user control. They are produced by an onchip voltage regulator.

For the device to function properly, the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter, if one is used.

# 3.4 Decoupling capacitors

The internal voltage regulator requires an external NPN ballast and some additional decoupling capacitors. These capacitors shall be placed on the board as close as possible to the associated pin.

| Symbol           |    | Parameter                                    | Conditions <sup>(1)</sup>                                                                                                        |      | Value              |      |      |

|------------------|----|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

| Symbo            | 1  |                                              |                                                                                                                                  | Min  | Тур                | Max  | Unit |

| C <sub>COL</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Max ESR = 100 mΩ.                                                                                         |      | 20                 |      | μF   |

| C <sub>LV1</sub> | SR | External decoupling /<br>stability capacitor | Sum of $C_{LV1}$ placed close to $V_{DD}/V_{SS\_LV\_CORy}$ pairs <sup>(2)</sup> .                                                | 12µF |                    | 40µF | μF   |

| C <sub>LV2</sub> | SR | External decoupling / stability capacitor    | Sum of C <sub>LV2</sub> placed close to<br>V <sub>DD</sub> /V <sub>SS_LV_CORy</sub> pairs shall be<br>between 300 nF and 900 nF. |      | 100 <sup>(2)</sup> |      | nF   |

| Table | 11. | Decoupling | capacitors |

|-------|-----|------------|------------|

|-------|-----|------------|------------|

SPC56XL60/54 makes a transition from HPREG1 to HPREG2. This transition is dynamic. Once HPREG2 is fully operational, the controller part of HPREG1 is switched off.

The following bipolar transistors are supported:

- BCP68 from ON Semiconductor

- BCX68 from Infineon

| Symbol              | Parameter                                              | Value              | Unit |

|---------------------|--------------------------------------------------------|--------------------|------|

| -                   |                                                        |                    |      |

| h <sub>FE</sub> (β) | DC current gain (Beta)                                 | 85 - 375           | —    |

| P <sub>D</sub>      | Maximum power dissipation @ $T_A$ =25°C <sup>(1)</sup> | 1.5                | W    |

| I <sub>CMaxDC</sub> | Maximum peak collector current                         | 1.0                | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage (Max)          | 600 <sup>(2)</sup> | mV   |

| V <sub>BE</sub>     | Base-to-emitter voltage (Max)                          | 1.0                | V    |

# Table 19. Characteristics

1. Derating factor 12mW/degC.

2. Adjust resistor at bipolar transistor collector for 3.3V to avoid VCE<VCE<sub>SAT</sub>.

The recommended external ballast transistor is the bipolar transistor BCP68 with the gain range of 85 up to 375 (for IC=500mA, VCE=1V) provided by several suppliers. This includes the gain variations BCP68-10, BCP68-16 and BCP68-25. The most important parameters for the interoperability with the integrated voltage regulator are the DC current gain (hFE) and the temperature coefficient of the gain (XTB). While the specified gain range of most BCP68 vendors is the same, there are slight variations in the temperature coefficient parameter. SPC56XL60/54 Voltage regulator operation was simulated against the typical variation on temperature coefficient and against the specified gain range to have a robust design.

| Sym               | bol | Parameter                                                         | Conditions                                                                                                          | Min | Тур | Max | Unit |

|-------------------|-----|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>ext</sub>  |     | External decoupling/<br>stability capacitor                       | Min, max values shall be<br>granted with respect to<br>tolerance, voltage,<br>temperature, and aging<br>variations. | 12  | _   | 40  | μF   |

|                   | SR  | Combined ESR of external capacitor                                | _                                                                                                                   | 1   | _   | 100 | mΩ   |

|                   | SR  | Number of pins for<br>external decoupling/<br>stability capacitor | _                                                                                                                   | 5   | _   | _   | _    |

| C <sub>V1V2</sub> | SR  | Total capacitance on 1.2 V pins                                   | Ceramic capacitors,<br>taking into account<br>tolerance, aging, voltage<br>and temperature<br>variation             | 300 | _   | 900 | nF   |

| t <sub>SU</sub>   |     | Start-up time after main supply stabilization                     | $C_{load}$ = 10 µF × 4                                                                                              | _   | _   | 2.5 | ms   |

| Table 20. \ | Voltage regulator | electrical | specifications |

|-------------|-------------------|------------|----------------|

|-------------|-------------------|------------|----------------|

twice the conversion period (T<sub>C</sub>). Again the conversion period T<sub>C</sub> is longer than the sampling time T<sub>S</sub>, which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter R<sub>F</sub>C<sub>F</sub> is definitively much higher than the sampling time T<sub>S</sub>, so the charge level on C<sub>S</sub> cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

# **Equation 11**

$$\frac{V_{A2}}{V_A} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

### **Equation 12**

$$C_F > 8192 \bullet C_S$$

# Table 27. ADC conversion characteristics

| Symbol                          |        | Parameter                                                                                                        | Conditions <sup>(1)</sup>             | Min | Тур | Max                      | Unit |

|---------------------------------|--------|------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----|--------------------------|------|

| f <sub>CK</sub>                 | S<br>R | ADC Clock frequency (depends on ADC configuration)<br>(The duty cycle depends on AD_CK <sup>(2)</sup> frequency) | _                                     | 3   | _   | 60                       | MHz  |

| f <sub>s</sub>                  | S<br>R | Sampling frequency                                                                                               |                                       | _   | _   | 983.<br>6 <sup>(3)</sup> | KHz  |

| t <sub>sample</sub>             | D      | Sample time <sup>(4)</sup>                                                                                       | 60 MHz                                | 383 | -   |                          | ns   |

| t <sub>eval</sub>               | D      | Evaluation time <sup>(5)</sup>                                                                                   | 60 MHz                                | 600 | —   | _                        | ns   |

| C <sub>S</sub> <sup>(6)</sup>   | D      | ADC input sampling capacitance                                                                                   | _                                     | _   | —   | 7.32                     | pF   |

| C <sub>P1</sub> <sup>(6)</sup>  | D      | ADC input pin capacitance 1                                                                                      | _                                     | —   | —   | 5 <sup>(7)</sup>         | pF   |

| C <sub>P2</sub> <sup>(6)</sup>  | D      | ADC input pin capacitance 2                                                                                      | _                                     | _   | —   | 0.8                      | pF   |

| R <sub>SW1</sub> <sup>(6)</sup> | D      | Internal resistance of analog source                                                                             | V <sub>REF</sub> range = 4.5 to 5.5 V | _   | —   | 0.3                      | kΩ   |

| rsw1` ′                         |        |                                                                                                                  | V <sub>REF</sub> range = 3.0 to 3.6 V | _   | —   | 875                      | W    |

| R <sub>AD</sub> <sup>(6)</sup>  | D      | Internal resistance of analog source                                                                             | —                                     | _   | —   | 825                      | W    |

| INL                             | Ρ      | Integral non linearity                                                                                           | —                                     | -3  | —   | 3                        | LSB  |

| DNL                             | Ρ      | Differential non linearity <sup>(8)</sup>                                                                        | —                                     | -1  | —   | 2                        | LSB  |

| OFS                             | Т      | Offset error                                                                                                     | —                                     | -6  | —   | 6                        | LSB  |

| GNE                             | Т      | Gain error                                                                                                       | —                                     | -6  | —   | 6                        | LSB  |

| IS1WINJ                         |        |                                                                                                                  | (single ADC channel)                  |     | •   |                          |      |

|                                 | С      | Max positive/negative injection                                                                                  |                                       | -3  | _   | 3                        | mA   |

# 3.21.4 Nexus timing

| Table 39 | . Nexus | debug | port timing <sup>(1)</sup> |

|----------|---------|-------|----------------------------|

|----------|---------|-------|----------------------------|

| No. | Symbol                                    |   | Parameter                                                                                      | Conditions | Min  | Max  | Unit              |

|-----|-------------------------------------------|---|------------------------------------------------------------------------------------------------|------------|------|------|-------------------|

| 1   | t <sub>MCYC</sub>                         | D | MCKO Cycle Time                                                                                | —          | 15.6 |      | ns                |

| 2   | t <sub>MDC</sub>                          | D | MCKO Duty Cycle                                                                                | —          | 40   | 60   | %                 |

| 3   | t <sub>MDOV</sub>                         | D | MCKO Low to MDO, $\overline{\text{MSEO}}$ , $\overline{\text{EVTO}}$ Data Valid <sup>(2)</sup> | —          | -0.1 | 0.25 | t <sub>MCYC</sub> |

| 4   | t <sub>EVTIPW</sub>                       | D | EVTI Pulse Width                                                                               | —          | 4.0  | —    | t <sub>TCYC</sub> |

| 5   | t <sub>EVTOPW</sub>                       | D | EVTO Pulse Width                                                                               | —          | 1    |      | t <sub>MCYC</sub> |

| 6   | t <sub>TCYC</sub>                         | D | TCK Cycle Time <sup>(3)</sup>                                                                  | —          | 62.5 | —    | ns                |

| 7   | t <sub>TDC</sub>                          | D | TCK Duty Cycle                                                                                 | —          | 40   | 60   | %                 |

| 8   | t <sub>NTDIS,</sub><br>t <sub>NTMSS</sub> | D | TDI, TMS Data Setup Time                                                                       | _          | 8    | _    | ns                |

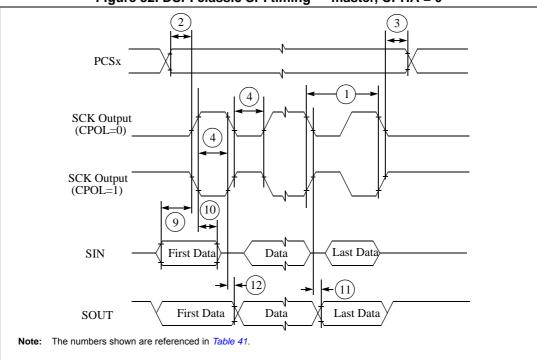

| No. | Symb            | ol              | Parameter                    | Conditions                  | Min | Мах | Unit |

|-----|-----------------|-----------------|------------------------------|-----------------------------|-----|-----|------|

|     |                 |                 |                              | Master (MTFE = 0)           | -2  | —   |      |

| 12  | t <sub>HO</sub> | <sub>HO</sub> D | D Data hold time for outputs | Slave                       | 6   | —   | ns   |

|     |                 |                 |                              | Master (MTFE = 1, CPHA = 0) | 6   | —   |      |

|     |                 |                 |                              | Master (MTFE = 1, CPHA = 1) | -2  | —   |      |

# Table 41. DSPI timing (continued)

1. Slave Receive Only Mode can operate at a maximum frequency of 60 MHz. In this mode, the DSPI can receive data on SIN, but no valid data is transmitted on SOUT.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23-Mar-2011 | 6<br>(continued) | <ul> <li>In the "Supply current characteristics (cut2)" table:</li> <li>Changed "I<sub>DD_LV_MAX</sub>" to "I<sub>DD_LV_MAX</sub>";</li> <li>Removed all "40-120 MHz" frequency ranges from the "Conditions" column;</li> <li>Updated the "Max" values column;</li> <li>Added parameter "I<sub>DD_LV_TYP</sub> + I<sub>DD_LV_PLL</sub>" with "P" classification and special footnote;</li> <li>Changed all "25°C" temperature conditions to "ambient";</li> <li>Added "T<sub>J</sub> = 150 °C" condition to parameters I<sub>DD_HV_ADC</sub>, I<sub>DD_HV_AREF</sub>, I<sub>DD_HV_OSC</sub>, and I<sub>DD_HV_FLASH</sub>.</li> <li>Changed the timing diagram in the "Main oscillator electrical characteristics" section to reference MTRANS assertion instead of V<sub>DDMIN</sub>.</li> <li>Updated the jitter specs in the "FMPLL electrical characteristics" table.</li> <li>In the "ADC conversion characteristics" table, changed all parameters with units of "counts" to units of "LSB" and updated Min/Max values.</li> <li>Changed I<sub>DD_LV_BIST</sub> + I<sub>DD_LV_PLL</sub> operating current (for both cases) to TBD.</li> <li>In the "ADC conversion characteristics" table.</li> <li>In the "ADC conversion characteristics" table.</li> <li>In the "ADC conversion characteristics" table.</li> <li>In the "Supply current characteristics (cut2)" section, added a footnote that I<sub>DD_HV_ADC</sub> and I<sub>DD_HV_AREF</sub> represent the total current of both ADCs in the "Current consumption characteristics" table.</li> <li>In the "ADC conversion characteristics" table.</li> <li>Changed OFS max from 2 to -6.</li> <li>Changed GNE max from 2 to 6.</li> <li>Changed GNE max from 2 to 6.</li> <li>Changed GNE max from 2 to 6.</li> <li>Changed SNR min from 69 to 67.</li> <li>Changed TUE max (without current injection) from -6 to -8.</li> <li>Changed TUE max (without current injection) from 8 to -10.</li> <li>Chang</li></ul> |  |

Table 45. Document revision history

| Date Revision |              | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|