#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 57                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l3ccfqr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.13  | Main os  | scillator electrical characteristics       | 6 |

|-------|----------|--------------------------------------------|---|

| 3.14  |          | electrical characteristics                 |   |

| 3.15  |          |                                            |   |

|       |          | z RC oscillator electrical characteristics |   |

| 3.16  |          | ectrical characteristics                   |   |

|       | 3.16.1   | Input Impedance and ADC Accuracy 120       |   |

| 3.17  | Flash n  | nemory electrical characteristics 12       | 5 |

| 3.18  | SWG e    | lectrical characteristics 12               | 7 |

| 3.19  | AC spe   | cifications                                | 7 |

|       | 3.19.1   | Pad AC specifications                      | 7 |

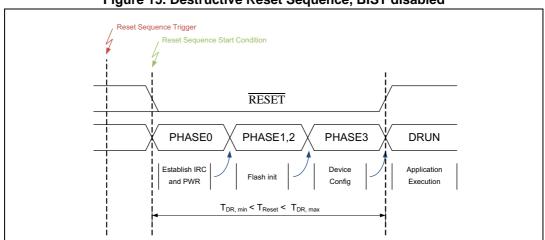

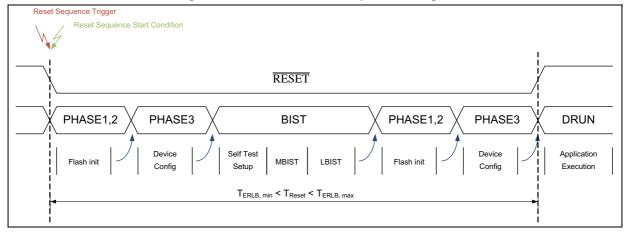

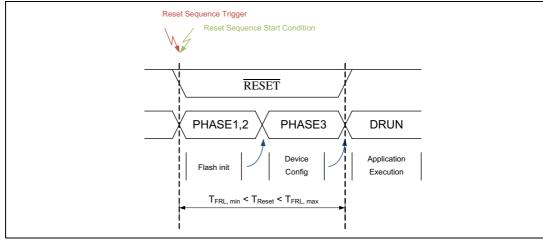

| 3.20  | Reset s  | sequence                                   | 8 |

|       | 3.20.1   | Reset sequence duration 12                 | 8 |

|       | 3.20.2   | Reset sequence description 12              | 9 |

|       | 3.20.3   | Reset sequence trigger mapping 13          | 1 |

|       | 3.20.4   | Reset sequence — start condition           | 2 |

|       | 3.20.5   | External watchdog window134                | 4 |

| 3.21  | AC timi  | ng characteristics                         | 4 |

|       | 3.21.1   | RESET pin characteristics                  | 4 |

|       | 3.21.2   | WKUP/NMI timing                            | 6 |

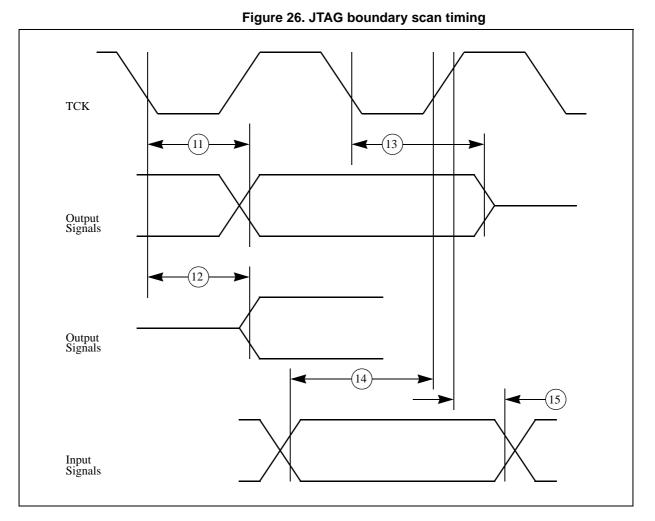

|       | 3.21.3   | IEEE 1149.1 JTAG interface timing          | 6 |

|       | 3.21.4   | Nexus timing                               | 8 |

|       | 3.21.5   | External interrupt timing (IRQ pin)14      | 1 |

|       | 3.21.6   | DSPI timing                                | 2 |

| Packa | age cha  | racteristics                               | B |

| 4.1   | ECOPA    | ACK®                                       | 8 |

| 4.2   | Packag   | e mechanical data 14                       | 8 |

| Orde  | ring inf | ormation                                   | 3 |

| Povis | sion his | tory                                       | 4 |

4

5

6

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- ±5% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the FMPLL

- RC oscillator is used as the default system clock during startup and can be used as back-up input source of FMPLL(s) in case XOSC fails

# 1.5.17 Clock, reset, power, mode and test control modules (MC\_CGM, MC\_RGM, MC\_PCU, and MC\_ME)

These modules provide the following:

- Clock gating and clock distribution control

- Halt, stop mode control

- Flexible configurable system and auxiliary clock dividers

- Various execution modes

- HALT and STOP mode as reduced activity low power mode

- Reset, Idle, Test, Safe

- Various RUN modes with software selectable powered modules

- No stand-by mode implemented (no internal switchable power domains)

#### 1.5.18 Periodic Interrupt Timer Module (PIT)

The PIT module implements the following features:

- 4 general purpose interrupt timers

- 32-bit counter resolution

- Can be used for software tick or DMA trigger operation

## 1.5.19 System Timer Module (STM)

The STM implements the following features:

- Up-counter with 4 output compare registers

- OS task protection and hardware tick implementation per AUTOSAR<sup>(a)</sup> requirement

The STM is replicated for each processor.

#### 1.5.20 Software Watchdog Timer (SWT)

This module implements the following features:

- Fault tolerant output

- Safe internal RC oscillator as reference clock

- Windowed watchdog

- Program flow control monitor with 16-bit pseudorandom key generation

- Allows a high level of safety (SIL3 monitor)

a. Automotive Open System Architecture.

## 1.5.25 System Status and Configuration Module (SSCM)

The SSCM on this device features the following:

- System configuration and status

- Debug port status and debug port enable

- Multiple boot code starting locations out of reset through implementation of search for valid Reset Configuration Half Word

- Sets up the MMU to allow user boot code to execute as either Power Architecture code (default) or as VLE code out of flash memory

- Triggering of device self-tests during reset phase of device boot

#### 1.5.26 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1Mbit/s

- 32 message buffers of 0 to 8 bytes data length

- Each message buffer configurable as receive or transmit buffer, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

## 1.5.28 Serial communication interface module (LINFlexD)

The LINFlexD module (LINFlex with DMA support) on this device features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Manages LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store as many as 8 data bytes

- Supports messages as long as 64 bytes

- Detection and flagging of LIN errors (Sync field, delimiter, ID parity, bit framing, checksum and Time-out errors)

- Classic or extended checksum calculation

- Configurable break duration of up to 50-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features (Loop back, LIN bus stuck dominant detection)

- Interrupt driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit, 9-bit, 16-bit, or 17-bit words)

- Configurable parity scheme: none, odd, even, always 0

- Speed as fast as 2 Mbit/s

- Error detection and flagging (Parity, Noise and Framing errors)

- Interrupt driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- Two receiver wake-up methods

- Support for DMA enabled transfers

#### 1.5.29 Deserial Serial Peripheral Interface (DSPI)

The DSPI modules provide a synchronous serial interface for communication between the SPC56ELx/SPC564Lx and external devices.

A DSPI module provides these features:

- Full duplex, synchronous transfers

- Master or slave operation

- Programmable master bit rates

- Programmable clock polarity and phase

## 1.5.33 Analog-to-Digital Converter module (ADC)

The ADC module features include:

Analog part:

- 2 on-chip ADCs

- 12-bit resolution SAR architecture

- Same digital interface as in the SPC560P family

- A/D Channels: 9 external, 3 internal and 4 shared with other A/D (total 16 channels)

- One channel dedicated to each T-sensor to enable temperature reading during application

- Separated reference for each ADC

- Shared analog supply voltage for both ADCs

- One sample and hold unit per ADC

- Adjustable sampling and conversion time

Digital part:

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range) before results are stored in the appropriate ADC result location

- 2 modes of operation: CPU Mode or CTU Mode

- CPU mode features

- Register based interface with the CPU: one result register per channel

- ADC state machine managing three request flows: regular command, hardware injected command, software injected command

- Selectable priority between software and hardware injected commands

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range)

- DMA compatible interface

- CTU mode features

- Triggered mode only

- 4 independent result queues ( $1 \times 16$  entries,  $2 \times 8$  entries,  $1 \times 4$  entries)

- Result alignment circuitry (left justified; right justified)

- 32-bit read mode allows to have channel ID on one of the 16-bit parts

- DMA compatible interfaces

- Built-in self-test features triggered by software

## 1.5.34 Cross Triggering Unit (CTU)

The ADC cross triggering unit allows automatic generation of ADC conversion requests on user selected conditions without CPU load during the PWM period and with minimized CPU load for dynamic configuration.

| Table 4. LQFP144 pin function summary (continued) |               |            |                 |                |  |  |  |  |  |  |

|---------------------------------------------------|---------------|------------|-----------------|----------------|--|--|--|--|--|--|

| Pin #                                             | Port/function | Peripheral | Output function | Input function |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[77]        | GPIO[77]       |  |  |  |  |  |  |

| 117                                               | <b>F</b> [12] | eTimer_0   | ETC[5]          | ETC[5]         |  |  |  |  |  |  |

| 117                                               | E[13]         | DSPI_2     | CS3             | _              |  |  |  |  |  |  |

|                                                   |               | SIUL       | _               | EIRQ[25]       |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[10]        | GPIO[10]       |  |  |  |  |  |  |

|                                                   |               | DSPI_2     | CS0             | CS0            |  |  |  |  |  |  |

| 118                                               | A[10]         | FlexPWM_0  | B[0]            | B[0]           |  |  |  |  |  |  |

|                                                   |               | FlexPWM_0  | X[2]            | X[2]           |  |  |  |  |  |  |

|                                                   |               | SIUL       | _               | EIRQ[9]        |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[78]        | GPIO[78]       |  |  |  |  |  |  |

| 119                                               | E[14]         | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |  |  |

|                                                   |               | SIUL       | _               | EIRQ[26]       |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[11]        | GPIO[11]       |  |  |  |  |  |  |

|                                                   | A[11]         | DSPI_2     | SCK             | SCK            |  |  |  |  |  |  |

| 120                                               |               | FlexPWM_0  | A[0]            | A[0]           |  |  |  |  |  |  |

|                                                   |               | FlexPWM_0  | A[2]            | A[2]           |  |  |  |  |  |  |

|                                                   |               | SIUL       | _               | EIRQ[10]       |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[79]        | GPIO[79]       |  |  |  |  |  |  |

| 121                                               | E[15]         | DSPI_0     | CS1             | —              |  |  |  |  |  |  |

|                                                   |               | SIUL       | _               | EIRQ[27]       |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[12]        | GPIO[12]       |  |  |  |  |  |  |

|                                                   |               | DSPI_2     | SOUT            | —              |  |  |  |  |  |  |

| 122                                               | A[12]         | FlexPWM_0  | A[2]            | A[2]           |  |  |  |  |  |  |

|                                                   |               | FlexPWM_0  | B[2]            | B[2]           |  |  |  |  |  |  |

|                                                   |               | SIUL       | —               | EIRQ[11]       |  |  |  |  |  |  |

| 123                                               | JCOMP         | _          | _               | JCOMP          |  |  |  |  |  |  |

|                                                   |               | SIUL       | GPIO[47]        | GPIO[47]       |  |  |  |  |  |  |

|                                                   |               | FlexRay    | CA_TR_EN        | —              |  |  |  |  |  |  |

| 104                                               | 0[45]         | eTimer_1   | ETC[0]          | ETC[0]         |  |  |  |  |  |  |

| 124                                               | C[15]         | FlexPWM_0  | A[1]            | A[1]           |  |  |  |  |  |  |

|                                                   |               | CTU_0      | _               | EXT_IN         |  |  |  |  |  |  |

|                                                   |               | FlexPWM_0  | _               | EXT_SYNC       |  |  |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

| Iable 4. LQFP144 pin function summary (continued)           Bin #         Bert/function |                          |            |                 |                |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|--------------------------|------------|-----------------|----------------|--|--|--|--|--|--|--|

| Pin #                                                                                   | Port/function            | Peripheral | Output function | Input function |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |  |  |  |  |  |  |

| 125                                                                                     | D[0]                     | FlexRay    | CA_TX           | _              |  |  |  |  |  |  |  |

| 120                                                                                     |                          | eTimer_1   | ETC[1]          | ETC[1]         |  |  |  |  |  |  |  |

|                                                                                         |                          | FlexPWM_0  | B[1]            | B[1]           |  |  |  |  |  |  |  |

| 126                                                                                     | V <sub>DD_HV_IO</sub>    |            | _               |                |  |  |  |  |  |  |  |

| 127                                                                                     | V <sub>SS_HV_IO</sub>    |            |                 |                |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |  |  |  |  |  |  |

| 128                                                                                     | 0121                     | FlexRay    | CB_TX           | _              |  |  |  |  |  |  |  |

| 120                                                                                     | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |  |  |  |  |  |  |

|                                                                                         |                          | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[52]        | GPI0[52]       |  |  |  |  |  |  |  |

| 100                                                                                     | DI4                      | FlexRay    | CB_TR_EN        |                |  |  |  |  |  |  |  |

| 129                                                                                     | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |  |  |  |

|                                                                                         |                          | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |  |  |  |

| 130                                                                                     | V <sub>DD_HV_REG_2</sub> |            | _               |                |  |  |  |  |  |  |  |

| 131                                                                                     | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |

| 132                                                                                     | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[80]        | GPIO[80]       |  |  |  |  |  |  |  |

| 133                                                                                     | FIOI                     | FlexPWM_0  | A[1]            | A[1]           |  |  |  |  |  |  |  |

| 155                                                                                     | F[0]                     | eTimer_0   | —               | ETC[2]         |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | —               | EIRQ[28]       |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[9]         | GPIO[9]        |  |  |  |  |  |  |  |

| 134                                                                                     | A101                     | DSPI_2     | CS1             | —              |  |  |  |  |  |  |  |

| 134                                                                                     | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |  |  |  |

|                                                                                         |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |

| 135                                                                                     | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | GPIO[13]        | GPIO[13]       |  |  |  |  |  |  |  |

|                                                                                         | [                        | FlexPWM_0  | B[2]            | B[2]           |  |  |  |  |  |  |  |

| 136                                                                                     | A[13]                    | DSPI_2     | —               | SIN            |  |  |  |  |  |  |  |

|                                                                                         |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |

|                                                                                         |                          | SIUL       | —               | EIRQ[12]       |  |  |  |  |  |  |  |

| 137                                                                                     | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

| D'. " |                                                      |            | n summary (continu | -              |

|-------|------------------------------------------------------|------------|--------------------|----------------|

| Pin # | Port/function                                        | Peripheral | Output function    | Input function |

| N14   | Not connected                                        |            | —                  |                |

|       |                                                      | SIUL       | GPIO[44]           | GPIO[44]       |

| N15   | C[12]                                                | eTimer_0   | ETC[5]             | ETC[5]         |

|       |                                                      | DSPI_2     | CS3                | —              |

|       |                                                      | SIUL       | GPIO[2]            | GPIO[2]        |

|       |                                                      | eTimer_0   | ETC[2]             | ETC[2]         |

| N16   | 1010                                                 | FlexPWM_0  | A[3]               | A[3]           |

| NIO   | A[2] —                                               | DSPI_2     | —                  | SIN            |

|       |                                                      | MC_RGM     | —                  | ABS[0]         |

|       |                                                      | SIUL       | —                  | EIRQ[2]        |

|       |                                                      | SIUL       | GPIO[101]          | GPIO[101]      |

| N17   | G[5]                                                 | FlexPWM_0  | X[3]               | X[3]           |

|       |                                                      | DSPI_2     | CS3                |                |

| P1    | V <sub>SS_HV_OSC</sub>                               |            | _                  |                |

| P2    | RESET                                                |            | —                  |                |

|       |                                                      | SIUL       | GPIO[54]           | GPIO[54]       |

| P3    | D[6]                                                 | DSPI_0     | CS2                | —              |

| 15    | D[0]                                                 | FlexPWM_0  | X[3]               | X[3]           |

|       |                                                      | FlexPWM_0  | —                  | FAULT[1]       |

| P4    | V <sub>DD_LV_PLL0_PLL1</sub>                         |            |                    |                |

| P5    | $V_{\text{DD}\_\text{LV}\_\text{CORE}\_\text{RING}}$ |            | —                  |                |

| P6    | $V_{SS\_LV\_CORE\_RING}$                             |            | —                  |                |

|       |                                                      | SIUL       | _                  | GPIO[24]       |

| P7    | B[8]                                                 | eTimer_0   | _                  | ETC[5]         |

|       |                                                      | ADC_0      | —                  | AN[1]          |

| P8    | Not connected                                        |            | _                  |                |

| P9    | V <sub>SS_HV_IO_RING</sub>                           |            | _                  |                |

| P10   | V <sub>DD_HV_IO_RING</sub>                           |            | —                  |                |

|       |                                                      | SIUL       | —                  | GPIO[30]       |

| P11   | B[14] —                                              | eTimer_0   | —                  | ETC[4]         |

|       | נדיןס                                                | SIUL       | —                  | EIRQ[19]       |

|       |                                                      | ADC_1      |                    | AN[1]          |

| P12   | V <sub>DD_LV_CORE_RING</sub>                         |            | _                  |                |

| P13   | V <sub>SS_LV_CORE_RING</sub>                         |            |                    |                |

| P14   | V <sub>DD_HV_IO_RING</sub>                           |            | _                  |                |

Table 5. LFBGA257 pin function summary (continued)

| Port                          |         | <b>D</b>   | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pa<br>spee | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |

|-------------------------------|---------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-----------------------------|------------|------------|------------|

| name                          | PCR     | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0                  | 100<br>pkg | 144<br>pkg | 25<br>pk   |

| F[7]<br>F[8]<br>F[9]<br>F[10] | PCR[87] | SIUL       | GPIO[87]           | ALT0    | GPIO[87]  | —                     |                        | F          | S                           |            | 19         | Ŀ          |

| Γ[/]                          | PCR[07] | NPC        | МСКО               | ALT2    | _         | _                     | _                      | Г          | 3                           | _          | 19         | J          |

| <b>E</b> [0]                  |         | SIUL       | GPIO[88]           | ALT0    | GPIO[88]  | _                     |                        | F          | S                           |            | 20         |            |

| F[8]                          | PCR[88] | NPC        | MSEO[1]            | ALT2    | _         | _                     | _                      | Г          | 5                           | _          | 20         | K          |

|                               |         | SIUL       | GPIO[89]           | ALT0    | GPIO[89]  | _                     |                        | F          | S                           |            | 22         | <b>K</b> 1 |

| F[9]                          | PCR[89] | NPC        | MSEO[0]            | ALT2    | _         | _                     | _                      | Г          | 5                           | _          | 23         |            |

|                               |         | SIUL       | GPIO[90]           | ALT0    | GPIO[90]  | _                     |                        | F          | <u>د</u>                    |            | 24         | L          |

| F[10]                         | PCR[90] | NPC        | EVTO               | ALT2    | _         | _                     |                        | F          | S                           | _          | 24         |            |

| <b>F</b> [44]                 | PCR[91] | SIUL       | GPIO[91]           | ALT0    | GPIO[91]  | _                     |                        |            | ¢                           |            | 25         | L2         |

| F[11]                         |         | NPC        | _                  | ALT2    | EVTI      | _                     |                        | М          | S                           | _          | 20         |            |

|                               |         | SIUL       | GPIO[92]           | ALT0    | GPIO[92]  | _                     |                        | М          |                             |            | 106        | C1         |

| F[12]                         | PCR[92] | eTimer_1   | ETC[3]             | ALT1    | ETC[3]    | PSMI[12];<br>PADSEL=2 |                        |            | S                           | _          |            |            |

|                               |         | SIUL       | _                  | _       | EIRQ[30]  | _                     |                        |            |                             |            |            |            |

|                               |         | SIUL       | GPIO[93]           | ALT0    | GPIO[93]  | —                     |                        |            |                             |            |            |            |

| F[13]                         | PCR[93] | eTimer_1   | ETC[4]             | ALT1    | ETC[4]    | PSMI[13];<br>PADSEL=3 | _                      | М          | S                           | _          | 112        | B14        |

|                               |         | SIUL       | _                  | _       | EIRQ[31]  | _                     |                        |            |                             |            |            |            |

| <b>F</b> [4]                  |         | SIUL       | GPIO[94]           | ALT0    | GPIO[94]  | —                     |                        | NA         | S                           |            | 115        | C13        |

| F[14]                         | PCR[94] | LINFlexD_1 | TXD                | ALT1    |           | _                     |                        | М          | 3                           | _          | 115        |            |

|                               |         | SIUL       | GPIO[95]           | ALT0    | GPIO[95]  | —                     |                        |            |                             |            |            |            |

| F[15]                         | PCR[95] | LINFlexD_1 | _                  | _       | RXD       | PSMI[32];<br>PADSEL=2 | ] —                    | М          | S                           | —          | 113        | D          |

Package pinouts and signal descriptions

91/165

| Port  | PCR                                                                                                                                                    | Deninkenst | Alternate          | Output  | Input     | Input mux | Weak pull              | Pad<br>speed <sup>(1)</sup> |            |            | Pin #      |          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|---------|-----------|-----------|------------------------|-----------------------------|------------|------------|------------|----------|

| name  | PCR                                                                                                                                                    | Peripheral | output<br>function | mux sel | functions | select    | config during<br>reset | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 25<br>pk |

|       | FlexPWM_0         —         —         FAULT[3]         PSMI[19];<br>PADSEL=2           SIUL         GPIO[108]         ALT0         GPIO[108]         — |            |                    |         |           |           |                        |                             |            |            |            |          |

| G[11] | PCR[107]                                                                                                                                               | FlexRay    | DBG3               | ALT1    | _         | —         | _                      | М                           | S          | _          | 75         | U        |

| 0[]   |                                                                                                                                                        | FlexPWM_0  | —                  | _       | FAULT[3]  |           |                        |                             | C          |            |            |          |

| 0[12] | DCD[109]                                                                                                                                               | SIUL       | GPIO[108]          | ALT0    | GPIO[108] | —         |                        | F                           | S          |            |            | F        |

| G[12] | PCR[100]                                                                                                                                               | NPC        | MDO[11]            | ALT2    | —         | —         |                        | Г                           | 3          | _          |            |          |

| 0[40] | DCD[400]                                                                                                                                               | SIUL       | GPIO[109]          | ALT0    | GPIO[109] | _         |                        | F                           | c          |            |            | F        |

| G[13] | PCR[109]                                                                                                                                               | NPC        | MDO[10]            | ALT2    | _         | _         |                        | Г                           | S          | _          |            |          |

| G[14] | PCR[110]                                                                                                                                               | SIUL       | GPIO[110]          | ALT0    | GPIO[110] | _         |                        | F                           | S          |            |            | А        |

| G[14] | FCR[110]                                                                                                                                               | NPC        | MDO[9]             | ALT2    | _         | —         |                        | Г                           | 3          | _          |            |          |

| G[15] | DCD[111]                                                                                                                                               | SIUL       | GPIO[111]          | ALT0    | GPIO[111] | —         |                        | F                           | S          |            |            | J2       |

| G[15] | PCR[111]                                                                                                                                               | NPC        | MDO[8]             | ALT2    | —         | —         |                        | Г                           | 3          | _          |            |          |

|       |                                                                                                                                                        |            | ·                  |         | Port H    |           |                        |                             |            |            |            | •        |

| цюі   | PCR[112]                                                                                                                                               | SIUL       | GPIO[112]          | ALT0    | GPIO[112] | —         |                        | F                           | S          |            |            | A        |

| H[0]  | FCR[112]                                                                                                                                               | NPC        | MDO[7]             | ALT2    | —         | _         |                        | Г                           | 3          | _          |            |          |

| H[1]  | PCR[113]                                                                                                                                               | SIUL       | GPIO[113]          | ALT0    | GPIO[113] | —         |                        | F                           | S          |            |            | F        |

| пы    | FCR[113]                                                                                                                                               | NPC        | MDO[6]             | ALT2    | —         | —         |                        | Г                           | 3          | _          |            |          |

| H[2]  | PCR[114]                                                                                                                                               | SIUL       | GPIO[114]          | ALT0    | GPIO[114] | —         |                        | F                           | S          |            |            | _        |

| пլ∠ј  | FCR[114]                                                                                                                                               | NPC        | MDO[5]             | ALT2    | —         | —         |                        | Г                           | 3          | _          |            | A4       |

| H[3]  | PCR[115]                                                                                                                                               | SIUL       | GPIO[115]          | ALT0    | GPIO[115] | —         |                        | F                           | S          |            | _          | G1       |

|       | FUR[110]                                                                                                                                               | NPC        | MDO[4]             | ALT2    | _         | _         | ] —                    | Г                           | 3          |            |            |          |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

#### Equation 2: $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

$\mathsf{R}_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $\mathsf{R}_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using *Equation 3*:

Equation 3  $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$T_T$ = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$ = thermal characterization parameter (°C/W)

$P_D$ = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### 3.5.1.1 References

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB on JEDEC site.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications," Electronic Packaging and Production, pp. 53–58, March 1998.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

Figure 15. Destructive Reset Sequence, BIST disabled

Figure 16. External Reset Sequence Long, BIST enabled

#### Figure 17. Functional Reset Sequence Long

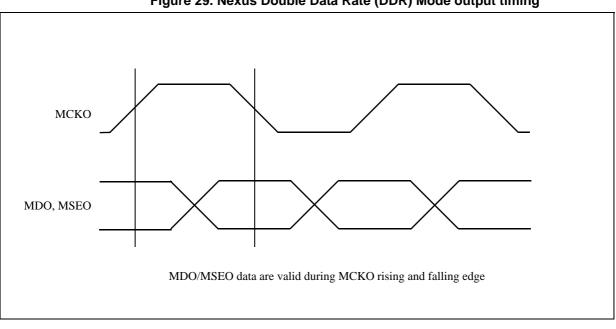

# 3.21.4 Nexus timing

| Table 39 | . Nexus | debug | port timing <sup>(1)</sup> |

|----------|---------|-------|----------------------------|

|----------|---------|-------|----------------------------|

| No. | Symbol                     |   | Parameter                                                                                      | Conditions | Min  | Max  | Unit              |

|-----|----------------------------|---|------------------------------------------------------------------------------------------------|------------|------|------|-------------------|

| 1   | t <sub>MCYC</sub>          | D | MCKO Cycle Time                                                                                | —          | 15.6 |      | ns                |

| 2   | t <sub>MDC</sub>           | D | MCKO Duty Cycle                                                                                | —          | 40   | 60   | %                 |

| 3   | t <sub>MDOV</sub>          | D | MCKO Low to MDO, $\overline{\text{MSEO}}$ , $\overline{\text{EVTO}}$ Data Valid <sup>(2)</sup> | —          | -0.1 | 0.25 | t <sub>MCYC</sub> |

| 4   | t <sub>EVTIPW</sub>        | D | EVTI Pulse Width                                                                               | —          | 4.0  | _    | t <sub>TCYC</sub> |

| 5   | t <sub>EVTOPW</sub>        | D | EVTO Pulse Width                                                                               | —          | 1    |      | t <sub>MCYC</sub> |

| 6   | t <sub>TCYC</sub>          | D | TCK Cycle Time <sup>(3)</sup>                                                                  | —          | 62.5 | —    | ns                |

| 7   | t <sub>TDC</sub>           | D | TCK Duty Cycle                                                                                 | —          | 40   | 60   | %                 |

| 8   | t <sub>NTDIS,</sub> D TDI, |   | TDI, TMS Data Setup Time                                                                       | _          | 8    | _    | ns                |

Figure 29. Nexus Double Data Rate (DDR) Mode output timing

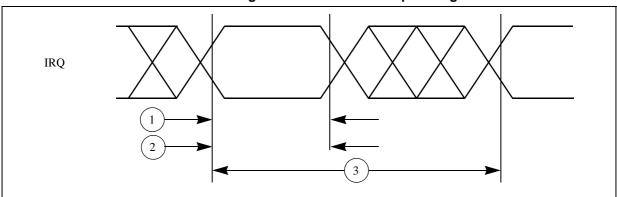

## Figure 31. External interrupt timing

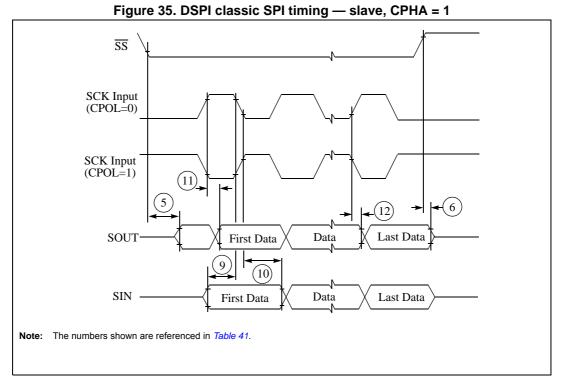

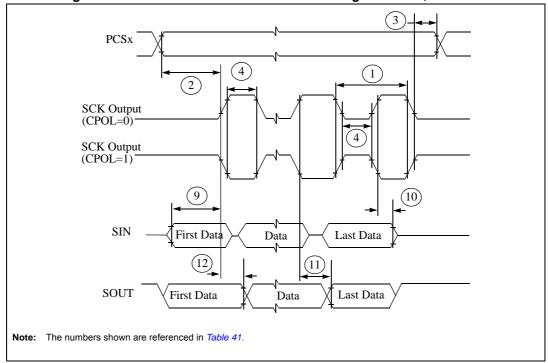

## 3.21.6 DSPI timing

|     |                   |    | la.                         | ble 41. DSPI timing                                    |                          |                          | 1    |

|-----|-------------------|----|-----------------------------|--------------------------------------------------------|--------------------------|--------------------------|------|

| No. | Symb              | ol | Parameter                   | Conditions                                             | Min                      | Max                      | Unit |

|     |                   | D  |                             | Master (MTFE = 0)                                      | 62                       | —                        |      |

| 1   | t <sub>SCK</sub>  | D  | DSPI cycle time             | Slave (MTFE = 0)                                       | 62                       | —                        | ns   |

|     |                   | D  |                             | Slave Receive Only Mode <sup>(1)</sup>                 | 16                       | —                        |      |

| 2   | t <sub>CSC</sub>  | D  | PCS to SCK delay            | —                                                      | 16                       | —                        | ns   |

| 3   | t <sub>ASC</sub>  | D  | After SCK delay             | —                                                      | 16                       | —                        | ns   |

| 4   | t <sub>SDC</sub>  | D  | SCK duty cycle              | —                                                      | t <sub>SCK</sub> /2 - 10 | t <sub>SCK</sub> /2 + 10 | ns   |

| 5   | t <sub>A</sub>    | D  | Slave access time           | SS active to SOUT valid                                | —                        | 40                       | ns   |

| 6   | t <sub>DIS</sub>  | D  | Slave SOUT disable time     | OUT disable time SS inactive to SOUT High-Z or invalid |                          | 10                       | ns   |

| 7   | t <sub>PCSC</sub> | D  | PCSx to PCSS time           | —                                                      | 13                       | —                        | ns   |

| 8   | t <sub>PASC</sub> | D  | PCSS to PCSx time           | —                                                      | 13                       | —                        | ns   |

|     |                   |    |                             | Master (MTFE = 0)                                      | 20                       | —                        |      |

| 9   | ÷                 | D  | Data setup time for inputs  | Slave                                                  | 2                        | —                        | 20   |

| 9   | t <sub>SUI</sub>  |    |                             | Master (MTFE = 1, CPHA = 0)                            | 5                        | —                        | ns   |

|     |                   |    |                             | Master (MTFE = 1, CPHA = 1)                            | 20                       | —                        |      |

|     |                   |    |                             | Master (MTFE = 0)                                      | -5                       | —                        |      |

| 10  | +                 | D  | Data hold time for inputs   | Slave                                                  | 4                        | —                        | 200  |

| 10  | t <sub>HI</sub>   |    |                             | Master (MTFE = 1, CPHA = 0)                            | 11                       | —                        | ns   |

|     |                   |    |                             | Master (MTFE = 1, CPHA = 1)                            | -5                       | —                        |      |

|     |                   |    |                             | Master (MTFE = 0)                                      | —                        | 4                        |      |

| 11  | tour              | D  | Data valid (after SCK edge) | Slave                                                  | _                        | 23                       | ns   |

|     | t <sub>suo</sub>  |    |                             | Master (MTFE = 1, CPHA = 0)                            | _                        | 12                       | 115  |

|     |                   |    |                             | Master (MTFE = 1, CPHA = 1)                            | _                        | 4                        |      |

# Table 41. DSPI timing

51

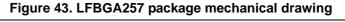

| Querra ha e l |      | mm   |      | inches <sup>(1)</sup> |        |        |  |

|---------------|------|------|------|-----------------------|--------|--------|--|

| Symbol        | Тур  | Min  | Max  | Тур                   | Min    | Max    |  |

| E3            | 17.5 |      |      | 0.6890                |        |        |  |

| е             | 0.5  |      |      | 0.0197                |        |        |  |

| L             | 0.6  | 0.45 | 0.75 | 0.0236                | 0.0177 | 0.0295 |  |

| L1            | 1    |      |      | 0.0394                |        |        |  |

| k             | 3.5° | 0.0° | 7.0° | 3.5°                  | 0.0°   | 7.0°   |  |

| Tolerance     |      | mm   |      |                       | inches |        |  |

| CCC           |      | 0.08 |      |                       | 0.0031 |        |  |

Table 43. LQFP144 mechanical data (continued)

1. Values in inches are converted from mm and rounded to four decimal digits.

DocID15457 Rev 12

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 14-Jun-2010 | 4<br>(continued) | In the "Main oscillator electrical characteristics" table, changed the maximum specification for g <sub>mXOSCHS</sub> (was 11 mA/V, is 11.8 mA/V).<br>Revised the "ADC electrical characteristics" section.In the "ADC conversion characteristics" table:<br>- Changed the t <sub>ADC_S</sub> specification (was TBD, is minimum of 383 ns).<br>- Added the footnote "No missing codes" to the DNL specification.<br>- Added specifications for SNR, THD, SINAD, and ENOB.<br>Revised the "Ordering information" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 23-Nov-2010 | 5                | Editorial changes and improvements.<br>Revised the Overview section.<br>Replaced references to PowerPC with references to Power Architecture.<br>In the feature summary, changed "As much as 128 KB on-chip SRAM" to<br>"128 KB on-chip SRAM".<br>In the "Feature details" section:<br>– In the "On-chip SRAM with ECC" section, added information about required<br>RAM wait states.<br>– In the PIT section, deleted "32-bit counter for real time interrupt, clocked<br>from main external oscillator" (not supported on this device).<br>– In the flash-memory section, changed "16 KB Test" to "16 KB test sector",<br>revised the wait state information, and deleted the associated Review_Q&A<br>content.<br>– In the SRAM section, revised the wait state information.<br>In the 100-pin pinout diagram:<br>– Renamed pin 41 (was VDD_HV_ADV0_ADV1, is VDD_HV_ADV).<br>– Renamed pin 42 (was VSS_HV_ADV0_ADV1, is VDS_HV_ADV).<br>In the 144-pin pinout diagram:<br>– Renamed pin 58 (was VDD_HV_ADV0_ADV1, is VDS_HV_ADV).<br>– Renamed pin 58 (was VDD_HV_ADV0_ADV1, is VSS_HV_ADV).<br>Added the "LQFP144 pin function summary" table.<br>In the "LQFP144 pin function summary" table, for pin 39, changed V <sub>SS_LV_COR</sub><br>to V <sub>DD_LV_COR</sub> .<br>In the "Supply pins" table:<br>– Changed the description for V <sub>DD_LV_COR</sub> (was "Voltage regulator supply<br>voltage", is "Core logic supply").<br>– Changed the description for V <sub>DD_HV_PMU</sub> (was "Core regulator supply", is<br>"Voltage regulator supply").<br>In the "Pin muxing" table:<br>– In the "Pad speed" column headings, changed "SRC = 0" to "SRC = 1" and<br>"SRC = 1" to "SRC = 0"<br>– For port B[6], changed the pad speed for SRC=0 (was M, is F).<br>In the "Thermal characteristics" section.<br>Added the "SWG electrical specifications" section.<br>In the "Nortage regulator electrical characteristics" section, changed the table<br>title (was "HPREG1, HPREG2, Main LVDs, Digital HVD, and Digital LVD<br>electrical specifications", is "Voltage regulator electrical characteristics") and<br>revised the table. |  |  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18-Sep-2013 | 10       | - Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 07-Feb-2014 | 11       | <ul> <li>Removed "TBC" symbol in <i>Table 9</i> and <i>Table 22</i></li> <li>Resolved some cross references.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 08-Jul-2015 | 12       | <ul> <li>Editorial and formatting changes throughout document.</li> <li><i>Chapter 1: Introduction:</i> <ul> <li>In <i>Table 1: SPC56ELx/SPC564Lx device summary</i> added the column for SPC56EL54 device</li> </ul> </li> <li><i>Chapter 3: Electrical characteristics:</i> <ul> <li>In <i>Table 9: Absolute maximum ratings</i>, added condition "Valid only for ADC pins" for V<sub>IN</sub> Symbol.</li> <li>Added Section 3.4: Decoupling capacitors.</li> <li><i>Figure 10: Input Equivalent Circuit:</i> changed "V<sub>DD</sub>" to "V<sub>REF</sub>" in Internal circuit scheme</li> <li>In <i>Table 32: Pad AC specifications (3.3 V, IPP_HVE = 0)</i> updated footnote 1 and footnote 2.</li> <li>Updated <i>Figure 13: Pad output delay</i></li> </ul> </li> </ul> |  |  |

| Table 45. Document revision history | Table 4 | 45. | Document | revision | history |

|-------------------------------------|---------|-----|----------|----------|---------|

|-------------------------------------|---------|-----|----------|----------|---------|

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID15457 Rev 12