#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 57                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l3ccfqy |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.5.14 Frequency-Modulated Phase-Locked Loop (FMPLL)

Each device has two FMPLLs.

Each FMPLL allows the user to generate high speed system clocks starting from a minimum reference of 4 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The FMPLL multiplication factor, output clock divider ratio are all software configurable. The FMPLLs have the following major features:

- Input frequency: 4–40 MHz continuous range (limited by the crystal oscillator)

- Voltage controlled oscillator (VCO) range: 256–512 MHz

- Frequency modulation via software control to reduce and control emission peaks

- Modulation depth ±2% if centered or 0% to -4% if downshifted via software control register

- Modulation frequency: triangular modulation with 25 kHz nominal rate

- Option to switch modulation on and off via software interface

- Output divider (ODF) for reduced frequency operation without re-lock

- 3 modes of operation

- Bypass mode

- Normal FMPLL mode with crystal reference (default)

- Normal FMPLL mode with external reference

- Lock monitor circuitry with lock status

- Loss-of-lock detection for reference and feedback clocks

- Self-clocked mode (SCM) operation

- On-chip loop filter

- Auxiliary FMPLL

- Used for FlexRay due to precise symbol rate requirement by the protocol

- Used for motor control periphery and connected IP (A/D digital interface CTU) to allow independent frequencies of operation for PWM and timers and jitter-free control

- Option to enable/disable modulation to avoid protocol violation on jitter and/or potential unadjusted error in electric motor control loop

- Allows to run motor control periphery at different (precisely lower, equal or higher as required) frequency than the system to ensure higher resolution

### 1.5.15 Main oscillator

•

The main oscillator provides these features:

- Input frequency range 4–40 MHz

- Crystal input mode

- External reference clock (3.3 V) input mode

- FMPLL reference

### 1.5.16 Internal Reference Clock (RC) oscillator

The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared to the stable bandgap reference voltage. The RC oscillator is the device safe clock.

DocID15457 Rev 12

|       |                         | 2FP144 pin function | n summary (continu | ea)            |

|-------|-------------------------|---------------------|--------------------|----------------|

| Pin # | Port/function           | Peripheral          | Output function    | Input function |

|       |                         | SIUL                | —                  | GPIO[25]       |

| 52    | B[9]                    | ADC_0<br>ADC_1      | _                  | AN[11]         |

|       |                         | SIUL                | —                  | GPIO[26]       |

| 53    | B[10]                   | ADC_0<br>ADC_1      | _                  | AN[12]         |

|       |                         | SIUL                | —                  | GPIO[27]       |

| 54    | B[11]                   | ADC_0<br>ADC_1      | _                  | AN[13]         |

|       |                         | SIUL                | —                  | GPIO[28]       |

| 55    | B[12]                   | ADC_0<br>ADC_1      | _                  | AN[14]         |

| 56    | V <sub>DD_HV_ADR1</sub> |                     | —                  |                |

| 57    | V <sub>SS_HV_ADR1</sub> |                     | —                  |                |

| 58    | V <sub>DD_HV_ADV</sub>  |                     | —                  |                |

| 59    | V <sub>SS_HV_ADV</sub>  |                     | —                  |                |

|       |                         | SIUL                | —                  | GPIO[29]       |

| 60    | B[13]                   | LINFlexD_1          | —                  | RXD            |

|       |                         | ADC_1               | —                  | AN[0]          |

| 61    | E[9]                    | SIUL                | —                  | GPIO[73]       |

| 01    | L[9]                    | ADC_1               | —                  | AN[7]          |

|       |                         | SIUL                | —                  | GPIO[31]       |

| 62    | B[15]                   | SIUL                | —                  | EIRQ[20]       |

|       |                         | ADC_1               | —                  | AN[2]          |

| 63    | E[10]                   | SIUL                | —                  | GPIO[74]       |

| 03    | E[10]                   | ADC_1               | —                  | AN[8]          |

|       |                         | SIUL                | —                  | GPIO[30]       |

| 64    | D[14]                   | eTimer_0            | —                  | ETC[4]         |

| 64    | B[14]                   | SIUL                | —                  | EIRQ[19]       |

|       |                         | ADC_1               | —                  | AN[1]          |

| 6F    | E[44]                   | SIUL                | —                  | GPIO[75]       |

| 65    | E[11]                   | ADC_1               | —                  | AN[4]          |

| 66    | 0101                    | SIUL                | —                  | GPIO[32]       |

| 66    | C[0]                    | ADC_1               | —                  | AN[3]          |

| 67    | E[12]                   | SIUL                | —                  | GPIO[76]       |

| 07    | E[12]                   | ADC_1               | _                  | AN[6]          |

Table 4. LQFP144 pin function summary (continued)

|       |                        | •          | on summary (continue | •              |

|-------|------------------------|------------|----------------------|----------------|

| Pin # | Port/function          | Peripheral | Output function      | Input function |

| 68    | E[0]                   | SIUL       |                      | GPIO[64]       |

|       | -[v]                   | ADC_1      | _                    | AN[5]          |

| 69    | BCTRL                  |            | _                    |                |

| 70    | $V_{DD_LV_COR}$        |            | _                    |                |

| 71    | $V_{SS_LV_COR}$        |            | —                    |                |

| 72    | V <sub>DD_HV_PMU</sub> |            | —                    |                |

|       |                        | SIUL       | GPIO[0]              | GPIO[0]        |

| 73    | 101                    | eTimer_0   | ETC[0]               | ETC[0]         |

| 73    | A[0]                   | DSPI_2     | SCK                  | SCK            |

|       |                        | SIUL       | —                    | EIRQ[0]        |

|       |                        | SIUL       | GPIO[1]              | GPIO[1]        |

| 74    | A [ 4 ]                | eTimer_0   | ETC[1]               | ETC[1]         |

| 74    | A[1]                   | DSPI_2     | SOUT                 |                |

|       |                        | SIUL       | _                    | EIRQ[1]        |

|       |                        | SIUL       | GPIO[107]            | GPIO[107]      |

| 75    | G[11]                  | FlexRay    | DBG3                 |                |

|       |                        | FlexPWM_0  | _                    | FAULT[3]       |

|       |                        | SIUL       | GPIO[58]             | GPIO[58]       |

| 76    | D[10]                  | FlexPWM_0  | A[0]                 | A[0]           |

|       |                        | eTimer_0   | _                    | ETC[0]         |

|       |                        | SIUL       | GPIO[106]            | GPIO[106]      |

| 77    | 01401                  | FlexRay    | DBG2                 |                |

| 77    | G[10]                  | DSPI_2     | CS3                  |                |

|       |                        | FlexPWM_0  | _                    | FAULT[2]       |

|       |                        | SIUL       | GPIO[59]             | GPIO[59]       |

| 78    | D[11]                  | FlexPWM_0  | B[0]                 | B[0]           |

|       |                        | eTimer_0   | _                    | ETC[1]         |

|       |                        | SIUL       | GPIO[105]            | GPIO[105]      |

|       |                        | FlexRay    | DBG1                 |                |

| 79    | G[9]                   | DSPI_1     | CS1                  |                |

|       |                        | FlexPWM_0  | —                    | FAULT[1]       |

|       |                        | SIUL       | —                    | EIRQ[29]       |

|       |                        | SIUL       | GPIO[43]             | GPIO[43]       |

| 80    | C[11]                  | eTimer_0   | ETC[4]               | ETC[4]         |

|       |                        | DSPI_2     | CS2                  |                |

|       | 1                      |            |                      |                |

Table 4. LQFP144 pin function summary (continued)

| Pin # | Port/function                       | Peripheral | Output function | Input function |

|-------|-------------------------------------|------------|-----------------|----------------|

|       |                                     | renpheral  | Output function | input function |

| K9    | V <sub>SS_LV</sub>                  |            | _               |                |

| K10   | V <sub>SS_LV</sub>                  |            | —               |                |

| K11   | V <sub>SS_LV</sub>                  |            | _               |                |

| K12   | V <sub>DD_LV</sub>                  |            | _               |                |

| K14   | Not connected                       |            | —               |                |

|       |                                     | SIUL       | GPIO[120]       | GPIO[120]      |

| K15   | H[8]                                | FlexPWM_1  | A[1]            | A[1]           |

|       |                                     | DSPI_0     | CS6             | —              |

|       |                                     | SIUL       | GPIO[119]       | GPIO[119]      |

| K16   | H[7]                                | FlexPWM_1  | X[1]            | X[1]           |

|       |                                     | eTimer_2   | ETC[1]          | ETC[1]         |

|       |                                     | SIUL       | GPIO[3]         | GPIO[3]        |

|       |                                     | eTimer_0   | ETC[3]          | ETC[3]         |

|       | -                                   | DSPI_2     | CS0             | CS0            |

| K17   | A[3]                                | FlexPWM_0  | B[3]            | B[3]           |

|       |                                     | MC_RGM     | _               | ABS[2]         |

|       | -                                   | SIUL       | _               | EIRQ[3]        |

|       |                                     | SIUL       | GPIO[90]        | GPIO[90]       |

| L1    | F[10]                               | NPC        | EVTO            |                |

|       |                                     | SIUL       | GPIO[91]        | GPIO[91]       |

| L2    | F[11]                               | NPC        | _               | EVTI           |

|       |                                     | SIUL       | GPIO[57]        | GPIO[57]       |

| L3    | D[9]                                | FlexPWM_0  | X[0]            | X[0]           |

| -     |                                     | LINFlexD_1 | TXD             |                |

| L4    | Not connected                       |            |                 |                |

| L6    | V <sub>DD_LV</sub>                  |            |                 |                |

| L7    | V <sub>DD_LV</sub>                  |            | _               |                |

| L8    | VSS_LV<br>V <sub>SS_LV</sub>        |            |                 |                |

| L9    |                                     |            |                 |                |

| L10   | V <sub>SS_LV</sub>                  |            |                 |                |

| L11   | V <sub>SS_LV</sub>                  |            |                 |                |

| L11   | V <sub>SS_LV</sub>                  |            |                 |                |

| L12   | V <sub>DD_LV</sub><br>Not connected |            |                 |                |

|       |                                     |            |                 |                |

| L15   | ТСК                                 |            | —               |                |

Table 5. LFBGA257 pin function summary (continued)

|                     | Supply                                                                                                                                                                                 |            |            |                       |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------------------|--|--|--|

| Symbol              | 100<br>pkg                                                                                                                                                                             | 144<br>pkg | 257<br>pkg |                       |  |  |  |

| V <sub>SS</sub> 1V2 | VSS_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                                        | 93         | 132        | VSS_LV <sup>(2)</sup> |  |  |  |

| V <sub>DD</sub> 1V2 | $\label{eq:VDD_LV_COR} VDD_LV_COR / \\ Decoupling pins for core logic. Decoupling capacitor must be \\ connected between these pins and the nearest V_{DD_LV_COR} pin. \\ \end{array}$ | _          | 135        | VDD_LV <sup>(1)</sup> |  |  |  |

| V <sub>SS</sub> 1V2 | VSS_LV_COR / Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                                            | _          | 137        | VSS_LV <sup>(2)</sup> |  |  |  |

#### Table 6. Supply pins (continued)

1. VDD\_LV balls are tied together on the LFBGA257 substrate.

2. VSS\_LV balls are tied together on the LFBGA257 substrate.

3. VDD\_HV balls are tied together on the LFBGA257 substrate.

4. VSS\_HV balls are tied together on the LFBGA257 substrate.

# 2.3 System pins

#### Table 7. System pins

|                      |                                                                                                                                                                                                                         |                     |            | Pin #      |            |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|------------|------------|

| Symbol               | Description                                                                                                                                                                                                             | Direction           | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|                      | Dedicated pins                                                                                                                                                                                                          |                     |            |            |            |

| MDO0 <sup>(1)</sup>  | Nexus Message Data Output — line                                                                                                                                                                                        | Output only         | —          | 9          | E1         |

| NMI <sup>(2)</sup>   | Non Maskable Interrupt                                                                                                                                                                                                  | Input only          | 1          | 1          | E4         |

| XTAL                 | Input for oscillator amplifier circuit and internal clock generator                                                                                                                                                     | Input only          | 18         | 29         | N1         |

| EXTAL <sup>(3)</sup> | Oscillator amplifier output                                                                                                                                                                                             | Input/Output<br>(4) | 19         | 30         | R1         |

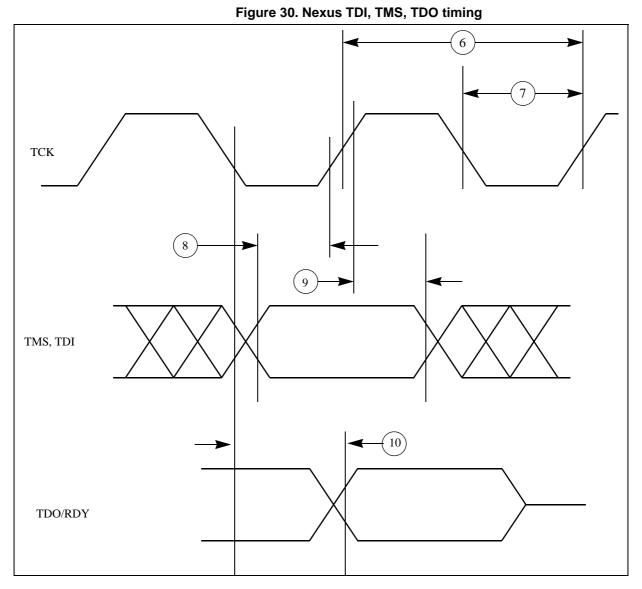

| TMS <sup>(2)</sup>   | JTAG state machine control                                                                                                                                                                                              | Input only          | 59         | 87         | M16        |

| TCK <sup>(2)</sup>   | JTAG clock                                                                                                                                                                                                              | Input only          | 60         | 88         | L15        |

| JCOMP <sup>(5)</sup> | JTAG compliance select                                                                                                                                                                                                  | Input only          | 84         | 123        | C10        |

|                      | Reset pin                                                                                                                                                                                                               |                     |            |            |            |

| RESET                | Bidirectional reset with Schmitt-Trigger characteristics and noise filter. This pin has medium drive strength. Output drive is open drain and must be terminated by an external resistor of value 1KOhm. <sup>(6)</sup> | Bidirectional       | 20         | 31         | P2         |

|                      | Test pin                                                                                                                                                                                                                |                     |            | -          |            |

| VPP TEST             | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                                                            |                     | 74         | 107        | D15        |

|                      |                                                                                                                                                                                                                         |                     |            |            |            |

1. This pad is configured for Fast (F) pad speed.

|   | Port<br>name |         |            | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |          |

|---|--------------|---------|------------|--------------------|---------|-----------|-----------------------|------------------------|-----------------------------|------------|------------|------------|----------|

|   |              | PCR     | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 25<br>pk |

| l |              |         | SIUL       | GPIO[42]           | ALT0    | GPIO[42]  |                       |                        |                             |            |            |            |          |

|   |              |         | DSPI_2     | CS2                | ALT1    | _         |                       |                        |                             |            |            |            |          |

|   | C[10]        | PCR[42] | FlexPWM_0  | A[3]               | ALT3    | A[3]      | PSMI[23];<br>PADSEL=1 |                        | М                           | S          | 78         | 111        | A1       |

|   |              |         | FlexPWM_0  | _                  | _       | FAULT[1]  | PSMI[17];<br>PADSEL=0 |                        |                             |            |            |            |          |

| Ì | C[11]        |         | SIUL       | GPIO[43]           | ALT0    | GPIO[43]  |                       |                        |                             |            |            | 80         |          |

|   |              | PCR[43] | eTimer_0   | ETC[4]             | ALT1    | ETC[4]    | PSMI[7];<br>PADSEL=1  |                        | М                           | S          | 55         |            | M1       |

|   |              |         | DSPI_2     | CS2                | ALT2    | _         |                       |                        |                             |            |            |            |          |

|   | C[12]        | PCR[44] | SIUL       | GPIO[44]           | ALT0    | GPIO[44]  | _                     |                        |                             |            | 56         | 82         | N15      |

|   |              |         | eTimer_0   | ETC[5]             | ALT1    | ETC[5]    | PSMI[8];<br>PADSEL=0  |                        | М                           | s          |            |            |          |

|   |              |         | DSPI_2     | CS3                | ALT2    | —         | _                     |                        |                             |            |            |            |          |

|   |              |         | SIUL       | GPIO[45]           | ALT0    | GPIO[45]  | —                     |                        |                             |            |            |            |          |

|   |              |         | eTimer_1   | ETC[1]             | ALT1    | ETC[1]    | PSMI[10];<br>PADSEL=0 |                        |                             |            |            |            |          |

|   | C[13]        | PCR[45] | CTU_0      | —                  | —       | EXT_IN    | PSMI[0];<br>PADSEL=0  | _                      | М                           | S          | 71         | 101        | F1       |

|   |              |         | FlexPWM_0  | _                  | _       | EXT_SYNC  | PSMI[15];<br>PADSEL=0 |                        |                             |            |            |            |          |

| Ì |              |         | SIUL       | GPIO[46]           | ALT0    | GPIO[46]  |                       |                        |                             |            |            |            |          |

|   | C[14]        | PCR[46] | eTimer_1   | ETC[2]             | ALT1    | ETC[2]    | PSMI[11];<br>PADSEL=1 |                        | М                           | S          | 72         | 103        | E1       |

|   |              |         | CTU_0      | EXT_TGR            | ALT2    |           | _                     | 1                      |                             |            |            |            |          |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

|      | Table 8. Pin muxing (continued) |            |                    |         |           |                       |                            |                             |            |            |            |            |

|------|---------------------------------|------------|--------------------|---------|-----------|-----------------------|----------------------------|-----------------------------|------------|------------|------------|------------|

| Port | PCR                             | Peripheral | Alternate          | Output  | Input     | Input mux             | Weak pull<br>config during | Pad<br>speed <sup>(1)</sup> |            |            | Pin #      |            |

| name | FUR                             | Penpheral  | output<br>function | mux sel | functions | select                | reset                      | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|      |                                 | SIUL       | GPIO[50]           | ALT0    | GPIO[50]  |                       |                            |                             |            |            |            |            |

| D[2] | PCR[50]                         | eTimer_1   | ETC[3]             | ALT2    | ETC[3]    | PSMI[12];<br>PADSEL=1 |                            | М                           | S          |            | 140        | C5         |

| D[2] | FCR[50]                         | FlexPWM_0  | X[3]               | ALT3    | X[3]      | PSMI[30];<br>PADSEL=0 |                            | IVI                         | 3          |            |            | 05         |

|      |                                 | FlexRay    | —                  | —       | CB_RX     | —                     |                            |                             |            |            |            |            |

|      |                                 | SIUL       | GPIO[51]           | ALT0    | GPIO[51]  | —                     |                            |                             |            |            |            |            |

|      | PCR[51]                         | FlexRay    | CB_TX              | ALT1    | _         | —                     |                            |                             |            |            |            |            |

| D[3] |                                 | eTimer_1   | ETC[4]             | ALT2    | ETC[4]    | PSMI[13];<br>PADSEL=1 | =1<br>}];                  | SYM                         | S          | 89         | 128        | A7         |

|      |                                 | FlexPWM_0  | A[3]               | ALT3    | A[3]      | PSMI[23];<br>PADSEL=2 |                            |                             |            |            |            |            |

|      |                                 | SIUL       | GPIO[52]           | ALT0    | GPIO[52]  | —                     |                            |                             |            |            |            |            |

|      |                                 | FlexRay    | CB_TR_EN           | ALT1    | _         | —                     |                            |                             |            |            |            |            |

| D[4] | PCR[52]                         | eTimer_1   | ETC[5]             | ALT2    | ETC[5]    | PSMI[14];<br>PADSEL=2 | _                          | SYM                         | S          | 90         | 129        | B7         |

|      |                                 | FlexPWM_0  | B[3]               | ALT3    | B[3]      | PSMI[27];<br>PADSEL=2 |                            |                             |            |            |            |            |

|      |                                 | SIUL       | GPIO[53]           | ALT0    | GPIO[53]  | _                     |                            |                             |            |            |            |            |

| D[5] | PCR[53]                         | DSPI_0     | CS3                | ALT1    | _         | _                     | ] _                        | М                           | S          | 22         | 33         | N3         |

|      |                                 | FlexPWM_0  |                    | _       | FAULT[2]  | PSMI[18];<br>PADSEL=0 |                            |                             |            |            |            |            |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

86/165

DocID15457 Rev 12

5

|                   |               |         |             |                     | Table 8. Pi | n muxing (cor        | ntinued)             |                         |            |                             |            |            |            |

|-------------------|---------------|---------|-------------|---------------------|-------------|----------------------|----------------------|-------------------------|------------|-----------------------------|------------|------------|------------|

| 1                 | Port          | PCR     | Peripheral  | Alternate<br>output | Output      | Input                | Input mux            | Weak pull config during |            | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |

|                   | name          | FUR     | Peripiteral | function            | mux sel     | functions            | select               | reset                   | SRC<br>= 1 | SRC<br>= 0                  | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|                   | E[4]          | PCR[68] | SIUL        | —                   | ALT0        | GPI[68]              | —                    |                         |            |                             |            | 42         | U4         |

|                   | ⊏[4]          | FCR[00] | ADC_0       |                     | —           | AN[7] <sup>(3)</sup> | —                    |                         | _          | _                           |            | 42         | 04         |

|                   |               | DCDIGOI | SIUL        |                     | ALT0        | GPI[69]              | —                    |                         |            |                             |            | 44         | Т5         |

|                   | E[5]          | PCR[69] | ADC_0       | _                   | —           | AN[8] <sup>(3)</sup> | —                    |                         | _          | _                           | _          | 44         | 15         |

|                   |               |         | SIUL        |                     | ALT0        | GPI[70]              | —                    |                         |            |                             |            | 46         | R6         |

|                   | E[6]          | PCR[70] | ADC_0       |                     | —           | AN[4] <sup>(3)</sup> | —                    |                         | _          | _                           |            | 40         | RO         |

| _                 | <b>C</b> (7)  | PCR[71] | SIUL        | _                   | ALT0        | GPI[71]              | —                    |                         |            |                             |            | 48         |            |

| Docl              | E[7]          |         | ADC_0       |                     | _           | AN[6] <sup>(3)</sup> | _                    |                         | _          | _                           |            | 48         | Т6         |

| DocID15457 Rev 12 |               | PCR[73] | SIUL        |                     | ALT0        | GPI[73]              | _                    |                         |            |                             |            | 61         | T10        |

| 457               | E[9]          |         | ADC_1       |                     | _           | AN[7] <sup>(3)</sup> | _                    |                         | _          | _                           |            | 01         | 110        |

| Rev               | E(40)         | PCR[74] | SIUL        |                     | ALT0        | GPI[74]              | _                    |                         |            |                             |            | 63         | T11        |

| 12                | E[10]         |         | ADC_1       |                     | _           | AN[8] <sup>(3)</sup> | _                    |                         | _          | _                           |            | 63         |            |

|                   | <b>F</b> [44] | 000/751 | SIUL        |                     | ALT0        | GPI[75]              | —                    |                         |            |                             |            | 65         | U11        |

|                   | E[11]         | PCR[75] | ADC_1       |                     | _           | AN[4] <sup>(3)</sup> | _                    |                         | _          | _                           |            | 65         |            |

|                   | E[10]         | DODIZEI | SIUL        |                     | ALT0        | GPI[76]              | _                    |                         |            |                             |            | 67         | T12        |

|                   | E[12]         | PCR[76] | ADC_1       |                     | _           | AN[6] <sup>(3)</sup> | _                    |                         | _          | _                           |            | 07         | 112        |

|                   |               |         | SIUL        | GPIO[77]            | ALT0        | GPIO[77]             | —                    |                         |            |                             |            |            |            |

|                   | E[13]         | PCR[77] | eTimer_0    | ETC[5]              | ALT1        | ETC[5]               | PSMI[8];<br>PADSEL=1 | ] _                     | М          | s                           | _          | 117        | D12        |

|                   |               |         | DSPI_2      | CS3                 | ALT2        | —                    | —                    |                         |            |                             |            |            |            |

|                   |               |         | SIUL        |                     | _           | EIRQ[25]             | _                    | 1                       |            |                             |            |            |            |

89/165

|                |      |          |            |                     | Table 8. Pi | n muxing (cor | ntinued)              |                                     |                             |            |            |            |            |

|----------------|------|----------|------------|---------------------|-------------|---------------|-----------------------|-------------------------------------|-----------------------------|------------|------------|------------|------------|

| <b>X</b>       | Port | PCR      | Peripheral | Alternate<br>output | Output      | Input         | Input mux<br>select   | Weak pull<br>config during<br>reset | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |            |

|                | name | FOR      |            | function            | mux sel     | functions     |                       |                                     | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|                |      |          | SIUL       | GPIO[129]           | ALT0        | GPIO[129]     | —                     |                                     |                             |            |            |            |            |

|                | I[1] | PCR[129] | eTimer_2   | ETC[1]              | ALT1        | ETC[1]        | PSMI[40];<br>PADSEL=1 | _                                   | М                           | S          | _          | _          | C12        |

|                |      |          | DSPI_0     | CS5                 | ALT2        | —             | —                     | ]                                   |                             |            |            |            |            |

|                |      |          | FlexPWM_1  | —                   | _           | FAULT[1]      | _                     |                                     |                             |            |            |            |            |

|                |      | PCR[130] | SIUL       | GPIO[130]           | ALT0        | GPIO[130]     | _                     |                                     |                             | S          | _          |            |            |

| J              | I[2] |          | eTimer_2   | ETC[2]              | ALT1        | ETC[2]        | PSMI[41];<br>PADSEL=1 |                                     | М                           |            |            | _          | F16        |

| DocID15457 Rev |      |          | DSPI_0     | CS6                 | ALT2        | _             | _                     |                                     |                             |            |            |            |            |

| 154            |      |          | FlexPWM_1  |                     | _           | FAULT[2]      |                       |                                     |                             |            |            |            |            |

| 7<br>D         |      |          | SIUL       | GPIO[131]           | ALT0        | GPIO[131]     | _                     |                                     |                             |            |            |            |            |

| ev 13          |      |          | eTimer_2   | ETC[3]              | ALT1        | ETC[3]        | PSMI[42];<br>PADSEL=1 |                                     |                             |            |            |            |            |

|                | I[3] | PCR[131] | DSPI_0     | CS7                 | ALT2        | _             |                       | 1 —                                 | М                           | S          | —          | —          | E17        |

|                |      | -        | CTU_0      | EXT_TGR             | ALT3        | _             |                       |                                     |                             |            |            |            |            |

|                |      |          | FlexPWM_1  | —                   | —           | FAULT[3]      |                       | 1                                   |                             |            |            |            |            |

|                | RDY  | PCR[132] | SIUL       | GPIO[132]           | ALT0        | GPIO[132]     |                       |                                     | F                           | 6          |            |            | K3         |

|                | RUY  |          | NPC        | RDY                 | ALT2        | —             | —                     | 1 —                                 | F                           | S          | _          |            |            |

1. Programmable via the SRC (Slew Rate Control) bit in the respective Pad Configuration Register; S = Slow, M = Medium, F = Fast, SYM = Symmetric (for FlexRay)

2. The default function of this pin out of reset is ALT1 (TDO).

3. Analog

Note:

97/165

Open Drain can be configured by the PCRn for all pins used as output (except FCCU\_F[0] and FCCU\_F[1]).

SPC56ELx, SPC564Lx

# **3 Electrical characteristics**

### 3.1 Introduction

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for this device.

This device is designed to operate at 120 MHz. The electrical specifications are preliminary and are from previous designs, design simulations, or initial evaluation. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after complete characterization and device qualifications have been completed.

The "Symbol" column of the electrical parameter and timings tables contains an additional column containing "SR", "CC", "P", "C", "T", or "D".

- "SR" identifies system requirements—conditions that must be provided to ensure normal device operation. An example is the input voltage of a voltage regulator.

- "CC" identifies controller characteristics—indicating the characteristics and timing of the signals that the chip provides.

- "P", "C", "T", or "D" apply only to controller characteristics—specifications that define normal device operation. They specify how each characteristic is guaranteed.

- P: parameter is guaranteed by production testing of each individual device.

- C: parameter is guaranteed by design characterization. Measurements are taken from a statistically relevant sample size across process variations.

- T: parameter is guaranteed by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values are shown in the typical ("typ") column are within this category.

- D: parameters are derived mainly from simulations.

## 3.2 Absolute maximum ratings

| Symbol                                                       |    | Parameter                                                                                      | Conditions | Min  | Max                     | Unit |

|--------------------------------------------------------------|----|------------------------------------------------------------------------------------------------|------------|------|-------------------------|------|

| V <sub>DD_HV_REG</sub>                                       | SR | 3.3 V voltage regulator supply voltage                                                         | _          | -0.3 | 4.5 <sup>(2), (3)</sup> | V    |

| V <sub>DD_HV_IOx</sub>                                       | SR | 3.3 V input/output supply voltage                                                              |            | -0.3 | 4.5 <sup>(2), (3)</sup> | V    |

| V <sub>SS_HV_IOx</sub>                                       | SR | Input/output ground voltage                                                                    |            | -0.1 | 0.1                     | V    |

| V <sub>DD_HV_FLA</sub>                                       | SR | 3.3 V flash supply voltage                                                                     |            | -0.3 | 4.5 <sup>(2), (3)</sup> | V    |

| V <sub>SS_HV_FLA</sub>                                       | SR | Flash memory ground                                                                            |            | -0.1 | 0.1                     | V    |

| V <sub>DD_HV_OSC</sub>                                       | SR | 3.3 V crystal oscillator amplifier supply voltage                                              | _          | -0.3 | 4.5 <sup>(2), (3)</sup> | V    |

| V <sub>SS_HV_OSC</sub>                                       | SR | 3.3 V crystal oscillator amplifier reference voltage                                           | _          | -0.1 | 0.1                     | V    |

| V <sub>DD_HV_ADR0</sub><br>(2)(3)<br>V <sub>DD_HV_ADR1</sub> | SR | 3.3 V / 5.0 V ADC_0 high reference<br>voltage<br>3.3 V / 5.0 V ADC_1 high reference<br>voltage | _          | -0.3 | 6.4 <sup>(2)</sup>      | v    |

| Table 9. Absolute maximum | ratings <sup>(1)</sup> |  |

|---------------------------|------------------------|--|

|---------------------------|------------------------|--|

| Symbol                                           |    | Parameter                                                                        | Conditions                     | Min <sup>(1)</sup> | Мах  | Unit |

|--------------------------------------------------|----|----------------------------------------------------------------------------------|--------------------------------|--------------------|------|------|

| V <sub>DD_HV_ADV</sub>                           | SR | 3.3 V ADC supply voltage                                                         | —                              | 3.0                | 3.63 | V    |

| V <sub>SS_HV_AD0</sub><br>V <sub>SS_HV_AD1</sub> | SR | ADC_0 ground and low reference voltage<br>ADC_1 ground and low reference voltage | _                              | 0                  | 0    | V    |

| V <sub>SS_HV_ADV</sub>                           | SR | 3.3 V ADC supply ground                                                          | —                              | 0                  | 0    | V    |

| V <sub>DD_LV,REGCOR</sub>                        | SR | Internal supply voltage                                                          | _                              | _                  | —    | ~    |

| V <sub>SS_LV_REGCOR</sub>                        | SR | Internal reference voltage                                                       | _                              | 0                  | 0    | V    |

| V <sub>DD_LV_CORx</sub> <sup>(2)</sup>           | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>           | SR | Internal reference voltage                                                       | —                              | 0                  | 0    | V    |

| V <sub>DD_LV_PLL</sub> <sup>(2)</sup>            | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_PLL</sub> <sup>(3)</sup>            | SR | Internal reference voltage                                                       | —                              | 0                  | 0    | V    |

| T <sub>A</sub>                                   | SR | Ambient temperature under bias                                                   | $f_{CPU} \leq 120 \text{ MHz}$ | -40                | 125  | °C   |

| TJ                                               | SR | Junction temperature under bias                                                  | —                              | -40                | 150  | °C   |

Table 10. Recommended operating conditions (3.3 V) (continued)

1. Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2.  $V_{DD\_HV\_ADR0}$  and  $V_{DD\_HV\_ADR1}$  cannot be operated at different voltages, and need to be supplied by the same voltage source.

3. VDD\_HV\_ADRx must always be applied and should be stable before LBIST starts. If this supply is not above its absolute minimum level, LBIST operations can fail.

4. Can be connected to emitter of external NPN. Low voltage supplies are not under user control. They are produced by an onchip voltage regulator.

For the device to function properly, the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter, if one is used.

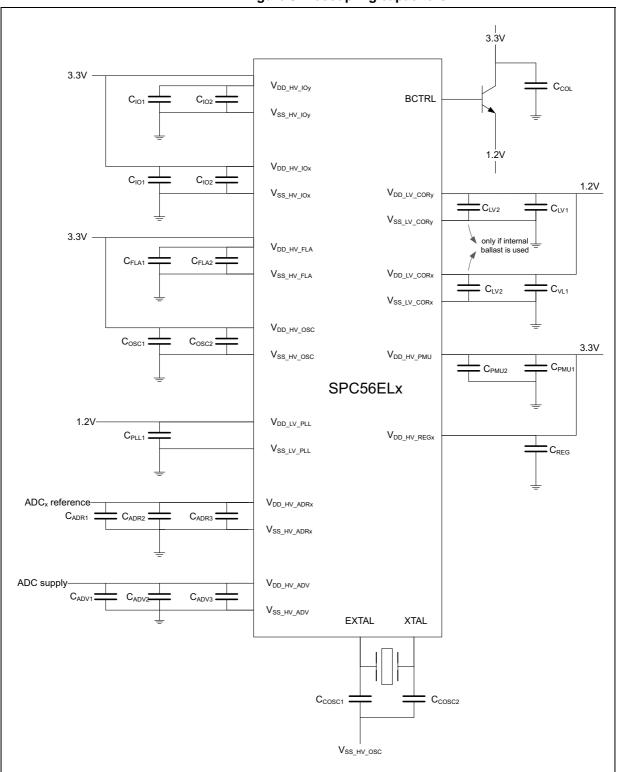

# 3.4 Decoupling capacitors

The internal voltage regulator requires an external NPN ballast and some additional decoupling capacitors. These capacitors shall be placed on the board as close as possible to the associated pin.

| Symbo            | 1                | Parameter                                 | Conditions <sup>(1)</sup>                                                                                                        |      | Unit               |      |      |

|------------------|------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

| Symbo            | Symbol Parameter |                                           | Conditions                                                                                                                       | Min  | Тур                | Max  | Unit |

| C <sub>COL</sub> | SR               | External decoupling / stability capacitor | Accuracy -50%/+35%.<br>Max ESR = 100 mΩ.                                                                                         |      | 20                 |      | μF   |

| C <sub>LV1</sub> | SR               | External decoupling / stability capacitor | Sum of $C_{LV1}$ placed close to $V_{DD}/V_{SS\_LV\_CORy}$ pairs <sup>(2)</sup> .                                                | 12µF |                    | 40µF | μF   |

| C <sub>LV2</sub> | SR               | External decoupling / stability capacitor | Sum of C <sub>LV2</sub> placed close to<br>V <sub>DD</sub> /V <sub>SS_LV_CORy</sub> pairs shall be<br>between 300 nF and 900 nF. |      | 100 <sup>(2)</sup> |      | nF   |

| Table | 11. | Decoupling | capacitors |

|-------|-----|------------|------------|

|-------|-----|------------|------------|

Figure 5. Decoupling capacitors

### Equation 2: $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

$\mathsf{R}_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $\mathsf{R}_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using *Equation 3*:

Equation 3  $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$T_T$ = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$ = thermal characterization parameter (°C/W)

$P_D$ = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### 3.5.1.1 References

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB on JEDEC site.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications," Electronic Packaging and Production, pp. 53–58, March 1998.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

- 2. With FM; the value does not include a possible +2% modulation

- 3. "Loss of Reference Frequency" window is the reference frequency range outside of which the FMPLL is in self clocked mode.

- Self clocked mode frequency is the frequency that the FMPLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- 5.  $f_{VCO}$  is the frequency at the output of the VCO; its range is 256–512 MHz.  $f_{SCM}$  is the self-clocked mode frequency (free running frequency); its range is 20–150 MHz.  $f_{SYS} = f_{VCO}$ +ODF

- 6. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this FMPLL, load capacitors should not exceed these limits.

- 7. This specification applies to the period required for the FMPLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 8. This value is determined by the crystal manufacturer and board design.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FMPLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

- 10. Proper PC board layout procedures must be followed to achieve specifications.

- 11. Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of  $C_{JITTER}$  and either  $f_{CS}$  or  $f_{DS}$  (depending on whether center spread or down spread modulation is enabled).

- 12. Modulation depth is attenuated from depth setting when operating at modulation frequencies above 50 kHz.

## 3.15 16 MHz RC oscillator electrical characteristics

| Symbol               | _ | Parameter                                                                                                                                   | Conditions -           |     | Unit |     |      |

|----------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| Symbol               | C | raiametei                                                                                                                                   | Conditions             | Min | Тур  | Max | Unit |

| f <sub>RC</sub>      | Ρ | RC oscillator frequency                                                                                                                     | T <sub>A</sub> = 25 °C | —   | 16   | —   | MHz  |

| $\Delta_{ m RCMVAR}$ | Ρ | Fast internal RC oscillator variation over temperature and supply with respect to $f_{RC}$ at $T_A = 25$ °C in high-frequency configuration | _                      | -6  | _    | 6   | %    |

#### Table 26. 16 MHz RC oscillator electrical characteristics

## 3.16 ADC electrical characteristics

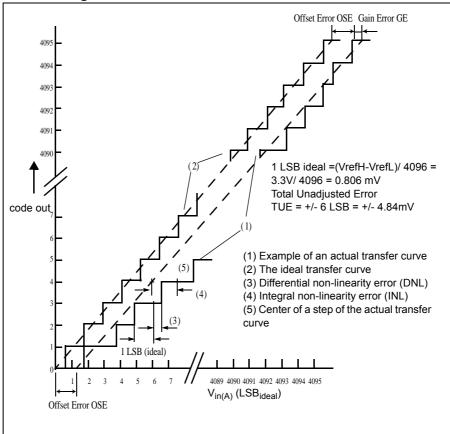

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Figure 9. ADC characteristics and error definitions

### 3.16.1 Input Impedance and ADC Accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2}$  + CS equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ}$  = 1 / (fS\*( $C_{p2}$ + $C_S$ )), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S$  +  $R_F$ , the external circuit must be designed to respect the *Equation 4*:

| Symbol                 |   | Parameter                                  | Conditions <sup>(1)</sup> Min   |      | Тур | Max | Unit |

|------------------------|---|--------------------------------------------|---------------------------------|------|-----|-----|------|

| IS1WWINJ               |   |                                            | (double ADC channel)            |      |     |     |      |

|                        | С | Max positive/negative injection            | Vref_ad0 - Vref_ad1  <<br>150mV | -3.6 | _   | 3.6 | mA   |

| SNR                    | Т | Signal-to-noise ratio                      | Vref = 3.3V                     | 67   | —   | _   | dB   |

| SNR                    | Т | Signal-to-noise ratio                      | Vref = 5.0V                     | 69   | —   | _   | dB   |

| THD                    | Т | Total harmonic distortion                  | —                               | -65  | —   | _   | dB   |

| SINAD                  | Т | Signal-to-noise and distortion             | —                               | 65   | —   | _   | dB   |

| ENOB                   | Т | Effective number of bits                   | —                               | 10.5 | —   | _   | bits |

| тис                    | т | Total unadjusted error for IS1WINJ (single | Without current injection       | -6   | —   | 6   | LSB  |

| TUE <sub>IS1WINJ</sub> | 1 | ADC channels)                              | With current injection          | -8   | —   | 8   | LSB  |

| TUE <sub>IS1WWI</sub>  | Ρ | Total unadjusted error for IS1WWINJ        | Without current injection       | -8   | —   | 8   | LSB  |

| NJ                     |   | (double ADC channels)                      | With current injection          | -10  | —   | 10  | LSB  |

Table 27. ADC conversion characteristics (continued)

1.  $T_J = -40$  to +150 °C, unless otherwise specified and analog input voltage from V<sub>AGND</sub> to V<sub>AREF</sub>.

2. AD\_CK clock is always half of the ADC module input clock defined via the auxiliary clock divider for the ADC.

3. This is the maximum frequency that the analog portion of the ADC can attain. A sustained conversion at this frequency is not possible.

- 4. During the sample time the input capacitance CS can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>sample</sub> depend on programming.

- 5. This parameter does not include the sample time Tsample, but only the time for determining the digital result.

- 6. See Figure 10.

- 7. For the 144-pin package

- 8. No missing codes

# 3.17 Flash memory electrical characteristics

#### Table 28. Flash memory program and erase electrical specifications

| No. | Symbol                   |      | Parameter                                         | <b>Тур</b><br>(1) | Initial<br>Max<br>(2) | Lifetime<br>Max <sup>(3)</sup> | Unit |

|-----|--------------------------|------|---------------------------------------------------|-------------------|-----------------------|--------------------------------|------|

| 1   | T <sub>DWPROGRAM</sub>   | *(4) | Double word (64 bits) program time <sup>(4)</sup> | 30                | —                     | 500                            | μs   |

| 2   | T <sub>PPROGRAM</sub>    | *(4) | Page(128 bits) program time <sup>(4)</sup>        | 40                | 160                   | 500                            | μs   |

| 3   | T <sub>16KPPERASE</sub>  | *(4) | 16 KB block pre-program and erase time            | 250               | 1000                  | 5000                           | ms   |

| 4   | T <sub>48KPPERASE</sub>  | *(4) | 48 KB block pre-program and erase time            | 400               | 1500                  | 5000                           | ms   |

| 5   | T <sub>64KPPERASE</sub>  | *(4) | 64 KB block pre-program and erase time            | 450               | 1800                  | 5000                           | ms   |

| 6   | T <sub>128KPPERASE</sub> | *(4) | 128 KB block pre-program and erase time           | 800               | 2600                  | 7500                           | ms   |

| 7   | T <sub>256KPPERASE</sub> | *(4) | 256 KB block pre-program and erase time           | 1400              | 5200                  | 15000                          | ms   |

1. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25°C. These values are characterized, but not tested.

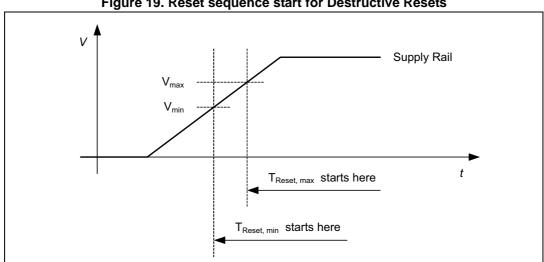

#### Figure 19. Reset sequence start for Destructive Resets

Table 35. Voltage Thresholds

| Variable name    | Value             |

|------------------|-------------------|

| V <sub>min</sub> | Refer to Table 20 |

| V <sub>max</sub> | Refer to Table 20 |

| Supply Rail      | VDD_HV_PMU        |

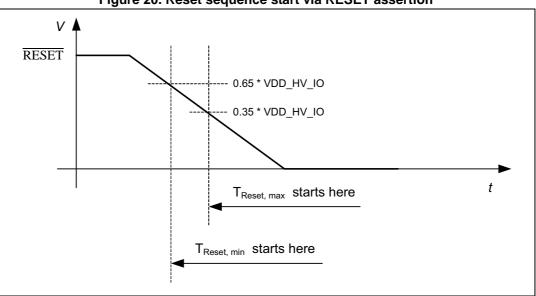

#### External reset via RESET 3.20.4.2

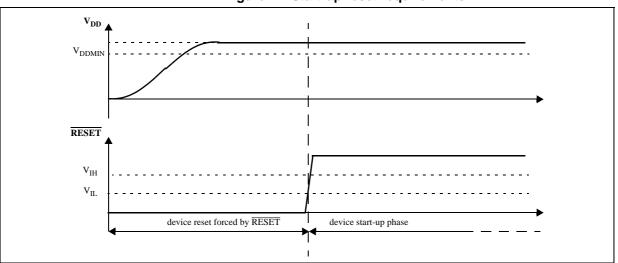

Figure 20 shows the voltage thresholds that determine the start of the reset sequences initiated by the assertion of RESET as specified in Table 34.

#### Figure 20. Reset sequence start via RESET assertion

Figure 22. Start-up reset requirements

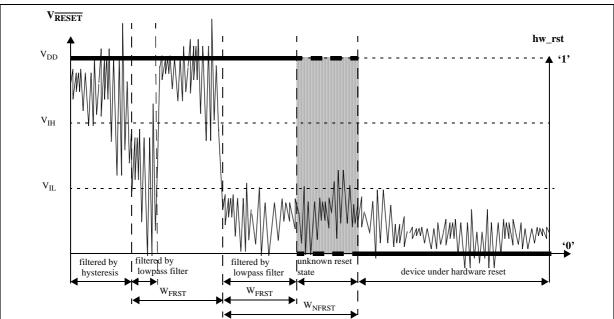

Figure 23. Noise filtering on reset signal

| Table 36. | RESET | electrical | characteristics |

|-----------|-------|------------|-----------------|

| No. | Symb               | ol | Parameter                                        | Conditions <sup>(1)</sup> | Min | Тур | Max | Unit |

|-----|--------------------|----|--------------------------------------------------|---------------------------|-----|-----|-----|------|

|     |                    |    |                                                  | C <sub>L</sub> = 25pF     | _   | —   | 12  |      |

| 1   | T <sub>tr</sub>    | D  | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 50pF     | _   | —   | 25  | ns   |

|     |                    |    |                                                  | C <sub>L</sub> = 100pF    | _   | —   | 40  |      |

| 2   | W <sub>FRST</sub>  | Ρ  | nRESET input filtered pulse                      | —                         | -   | —   | 40  | ns   |

| 3   | W <sub>NFRST</sub> | Р  | nRESET input not filtered pulse                  | _                         | 500 | _   | _   | ns   |

1.  $V_{DD}$  = 3.3 V  $\pm$  10%,  $T_{J}$  = –40 to +150 °C, unless otherwise specified.

# 3.21.5 External interrupt timing (IRQ pin)

### Table 40. External interrupt timing

| No. | Symb              | ol | Parameter                            | Conditions | Min | Max | Unit             |

|-----|-------------------|----|--------------------------------------|------------|-----|-----|------------------|

| 1   | t <sub>IPWL</sub> | D  | IRQ pulse width low                  | —          | 3   | —   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | D  | IRQ pulse width high                 | —          | 3   | —   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | D  | IRQ edge to edge time <sup>(1)</sup> | _          | 6   | —   | t <sub>CYC</sub> |

1. Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Sep-2013 | 10       | - Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 07-Feb-2014 | 11       | <ul> <li>Removed "TBC" symbol in <i>Table 9</i> and <i>Table 22</i></li> <li>Resolved some cross references.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 08-Jul-2015 | 12       | <ul> <li>Editorial and formatting changes throughout document.</li> <li><i>Chapter 1: Introduction:</i> <ul> <li>In <i>Table 1: SPC56ELx/SPC564Lx device summary</i> added the column for SPC56EL54 device</li> </ul> </li> <li><i>Chapter 3: Electrical characteristics:</i> <ul> <li>In <i>Table 9: Absolute maximum ratings</i>, added condition "Valid only for ADC pins" for V<sub>IN</sub> Symbol.</li> <li>Added Section 3.4: Decoupling capacitors.</li> <li><i>Figure 10: Input Equivalent Circuit:</i> changed "V<sub>DD</sub>" to "V<sub>REF</sub>" in Internal circuit scheme</li> <li>In <i>Table 32: Pad AC specifications (3.3 V, IPP_HVE = 0)</i> updated footnote 1 and footnote 2.</li> <li>Updated <i>Figure 13: Pad output delay</i></li> </ul> </li> </ul> |

| Table 45. Document revision history | Table 4 | 45. | Document | revision | history |

|-------------------------------------|---------|-----|----------|----------|---------|

|-------------------------------------|---------|-----|----------|----------|---------|