#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 57                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

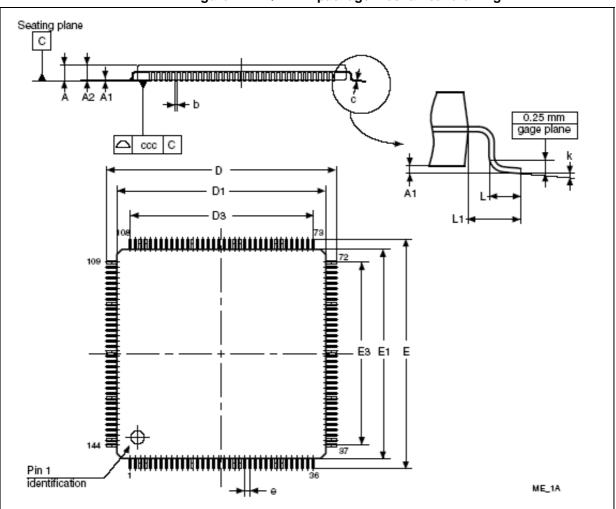

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l3ccfsr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1.5** Feature details

# 1.5.1 High-performance e200z4d core

The e200z4d Power Architecture<sup>®</sup> core provides the following features:

- 2 independent execution units, both supporting fixed-point and floating-point operations

- Dual issue 32-bit Power Architecture technology compliant

- 5-stage pipeline (IF, DEC, EX1, EX2, WB)

- In-order execution and instruction retirement

- Full support for Power Architecture instruction set and Variable Length Encoding (VLE)

- Mix of classic 32-bit and 16-bit instruction allowed

- Optimization of code size possible

- Thirty-two 64-bit general purpose registers (GPRs)

- Harvard bus (32-bit address, 64-bit data)

- I-Bus interface capable of one outstanding transaction plus one piped with no waiton-data return

- D-Bus interface capable of two transactions outstanding to fill AHB pipe

- I-cache and I-cache controller

- 4 KB, 256-bit cache line (programmable for 2- or 4-way)

- No data cache

- 16-entry MMU

- 8-entry branch table buffer

- Branch look-ahead instruction buffer to accelerate branching

- Dedicated branch address calculator

- 3 cycles worst case for missed branch

- Load/store unit

- Fully pipelined

- Single-cycle load latency

- Big- and little-endian modes supported

- Misaligned access support

- Single stall cycle on load to use

- Single-cycle throughput (2-cycle latency) integer 32 × 32 multiplication

- 4 14 cycles integer 32 × 32 division (average division on various benchmark of nine cycles)

- Single precision floating-point unit

- 1 cycle throughput (2-cycle latency) floating-point 32 × 32 multiplication

- Target 9 cycles (worst case acceptable is 12 cycles) throughput floating-point 32 × 32 division

- Special square root and min/max function implemented

- Signal processing support: APU-SPE 1.1

- Support for vectorized mode: as many as two floating-point instructions per clock

- Vectored interrupt support

- Reservation instruction to support read-modify-write constructs

The following functions are implemented:

- ECC encoding (32-bit boundary for data and complete address bus)

- ECC decoding (32-bit boundary and entire address)

- Address translation from the AHB protocol on the XBAR to the SRAM array

The platform SRAM controller is replicated for each processor.

# 1.5.9 Memory subsystem access time

Every memory access, that the CPU performs, requires at least one system clock cycle for the data phase of the access. Slower memories or peripherals may require additional data phase wait states. Additional data phase wait states may also occur if the slave being accessed is not parked on the requesting master in the crossbar.

*Table 2* shows the number of additional data phase wait states required for a range of memory accesses.

| AHB transfer              | Data phase<br>wait states | Description                                                                                                     |

|---------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|

| e200z4d instruction fetch | 0                         | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d instruction fetch | 3                         | Flash memory prefetch buffer miss (based on 4-cycle random flash array access time)                             |

| e200z4d data read         | 0–1                       | SRAM read                                                                                                       |

| e200z4d data write        | 0                         | SRAM 32-bit write                                                                                               |

| e200z4d data write        | 0                         | SRAM 64-bit write (executed as 2 x 32-bit writes)                                                               |

| e200z4d data write        | 0–2                       | SRAM 8-,16-bit write<br>(Read-modify-Write for ECC)                                                             |

| e200z4d flash memory read | 0                         | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d flash memory read | 3                         | Flash memory prefetch buffer miss (at 120 MHz; includes 1 cycle of program flash memory controller arbitration) |

### Table 2. Platform memory access time summary

# 1.5.10 Error Correction Status Module (ECSM)

The ECSM on this device manages the ECC configuration and reporting for the platform memories (flash memory and SRAM). It does not implement the actual ECC calculation. A detected error (double error for flash memory or SRAM) is also reported to the FCCU. The following errors and indications are reported into the ECSM dedicated registers:

- ECC error status and configuration for flash memory and SRAM

- ECC error reporting for flash memory

- ECC error reporting for SRAM

- ECC error injection for SRAM

# 1.5.11 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

# 1.5.12 Interrupt Controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other.

The INTC provides the following features:

- Duplicated periphery

- Unique 9-bit vector per interrupt source

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Priority elevation for shared resource

The INTC is replicated for each processor.

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid FMPLL jitter

### 1.5.27 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1 Rev. A

- 64 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as transmit or receive

- Message buffer size configurable

- Message filtering for all message buffers based on Frame ID, cycle count, and message ID

- Programmable acceptance filters for receive FIFO

- Message buffer header, status, and payload data stored in system memory (SRAM)

- Internal FlexRay memories have error detection and correction

| Pin # | Port/function | Peripheral | Output function | Input function |

|-------|---------------|------------|-----------------|----------------|

|       |               | SIUL       | GPIO[13]        | GPIO[13]       |

|       |               | FlexPWM_0  | B[2]            | B[2]           |

| 95    | A[13]         | DSPI_2     |                 | SIN            |

|       |               | FlexPWM_0  | _               | FAULT[0]       |

|       |               | SIUL       | _               | EIRQ[12]       |

|       |               | SIUL       | GPIO[22]        | GPIO[22]       |

| 96    | DIG           | MC_CGM     | clk_out         | —              |

| 90    | B[6]          | DSPI_2     | CS2             |                |

|       |               | SIUL       | _               | EIRQ[18]       |

| 97    | FCCU_F[1]     | FCCU       | F[1]            | F[1]           |

|       |               | SIUL       | GPIO[38]        | GPIO[38]       |

|       |               | DSPI_0     | SOUT            | —              |

| 98    | C[6]          | FlexPWM_0  | B[1]            | B[1]           |

|       |               | SSCM       | DEBUG[6]        | —              |

|       |               | SIUL       | —               | EIRQ[24]       |

|       |               | SIUL       | GPIO[14]        | GPIO[14]       |

| 99    | A [ 1 4 ]     | FlexCAN_1  | TXD             | —              |

| 99    | A[14]         | eTimer_1   | ETC[4]          | ETC[4]         |

|       |               | SIUL       | —               | EIRQ[13]       |

|       |               | SIUL       | GPIO[15]        | GPIO[15]       |

|       |               | eTimer_1   | ETC[5]          | ETC[5]         |

| 100   | A[15]         | FlexCAN_1  | —               | RXD            |

|       |               | FlexCAN_0  | —               | RXD            |

|       |               | SIUL       | —               | EIRQ[14]       |

Table 3. LQFP100 pin function summary (continued)

1.  $V_{PP\_TEST}$  should always be tied to ground (V\_{SS}) for normal operations.

| Pin # | Port/function | Peripheral | Output function | Input function |

|-------|---------------|------------|-----------------|----------------|

| 1     | NMI           |            | —               |                |

|       |               | SIUL       | GPIO[6]         | GPIO[6]        |

| 2     | A[6]          | DSPI_1     | SCK             | SCK            |

|       |               | SIUL       | —               | EIRQ[6]        |

| _                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •               | n summary (continue | •              |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|----------------|

| Pin #                                                                            | Port/function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Peripheral      | Output function     | Input function |

|                                                                                  | Pin #         Port/function           125         D[0]           126         V_DD_HV_IO           127         VSS_HV_IO           128         D[3]           129         D[4]           130         V_DD_HV_REG_2           131         V_DD_LV_COR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SIUL            | GPIO[48]            | GPIO[48]       |

| 125                                                                              | וסוס                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FlexRay         | CA_TX               | _              |

| 120                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | eTimer_1 ETC[1] |                     | ETC[1]         |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FlexPWM_0       | B[1]                | B[1]           |

| 126                                                                              | V <sub>DD_HV_IO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | _                   |                |

| 127                                                                              | V <sub>SS_HV_IO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                     |                |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIUL            | GPIO[51]            | GPIO[51]       |

| 100                                                                              | 0121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FlexRay         | CB_TX               | _              |

| 120                                                                              | D[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eTimer_1        | ETC[4]              | ETC[4]         |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FlexPWM_0       | A[3]                | A[3]           |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIUL            | GPIO[52]            | GPI0[52]       |

| 100                                                                              | DI4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FlexRay         | CB_TR_EN            |                |

| 129                                                                              | D[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eTimer_1        | ETC[5]              | ETC[5]         |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FlexPWM_0       | B[3]                | B[3]           |

| 130                                                                              | V <sub>DD_HV_REG_2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | _                   |                |

| 131                                                                              | V <sub>DD_LV_COR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                     |                |

| 132                                                                              | V <sub>SS_LV_COR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | —                   |                |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIUL            | GPIO[80]            | GPIO[80]       |

| 122                                                                              | FIOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FlexPWM_0       | A[1]                | A[1]           |

| 155                                                                              | F[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eTimer_0        | —                   | ETC[2]         |

|                                                                                  | D[0]<br>V <sub>DD_HV_I0</sub><br>V <sub>SS_HV_I0</sub><br>D[3]<br>D[4]<br>V <sub>DD_HV_REG_2</sub><br>V <sub>DD_LV_COR</sub><br>V <sub>SS_LV_COR</sub><br>F[0]<br>A[9]<br>V <sub>DD_LV_COR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SIUL            | —                   | EIRQ[28]       |

|                                                                                  | Port/function         Perip           D[0]         SI           Flex         eTim           VDD_HV_IO         Flex           VDD_HV_IO         SI           VSS_HV_IO         SI           D[3]         Flex           PI(4)         SI           PI(4)         Flex           PI(4)         SI           PI(4)         Flex           PI(4)         Flex           PI(4)         SI           PI(4)         Flex           PI(4)         SI           PI(4)         SI           PI(4)         Flex           PI(4)         Tim           PI(4)         Flex           PI(4)         Tim           PI(4)         Flex           PI(4)         Flex           PI(4)         Flex           PI(4)         Flex           PI(4)         Flex           PI(4)         PI(4)           PI(4)         PI(4)           PI(4)         PI(4)           PI(4)         PI(4)           PI(4)         PI(4)           PI(5)         PI(5)           PI(5)         PI(5) | SIUL            | GPIO[9]             | GPIO[9]        |

| 124                                                                              | A101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DSPI_2          | CS1                 | —              |

| 134                                                                              | A[A]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FlexPWM_0       | B[3]                | B[3]           |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FlexPWM_0       | —                   | FAULT[0]       |

| 135                                                                              | V <sub>DD_LV_COR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                     |                |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIUL            | GPIO[13]            | GPIO[13]       |

|                                                                                  | [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FlexPWM_0       | B[2]                | B[2]           |

| 136                                                                              | A[13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DSPI_2          | —                   | SIN            |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FlexPWM_0       | —                   | FAULT[0]       |

| 126<br>127<br>128<br>129<br>130<br>131<br>132<br>133<br>133<br>134<br>135<br>136 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIUL            | —                   | EIRQ[12]       |

| 137                                                                              | V <sub>SS_LV_COR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | —                   |                |

Table 4. LQFP144 pin function summary (continued)

| Table 5. LFBGA257 pin function summary (continued)                                                                                                                                                                                                      |                              |            |                 |                |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|-----------------|----------------|--|--|--|--|--|

| Pin #                                                                                                                                                                                                                                                   | Port/function                | Peripheral | Output function | Input function |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | SIUL       | GPIO[116]       | GPIO[116]      |  |  |  |  |  |

| L16                                                                                                                                                                                                                                                     | H[4]                         | FlexPWM_1  | X[0]            | X[0]           |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | eTimer_2   | ETC[0]          | ETC[0]         |  |  |  |  |  |

| 1 4 7                                                                                                                                                                                                                                                   | DIAL                         | SIUL       | GPIO[20]        |                |  |  |  |  |  |

| LI/                                                                                                                                                                                                                                                     | B[4]                         | JTAGC      | TDO             | _              |  |  |  |  |  |

| M1                                                                                                                                                                                                                                                      | V <sub>DD_HV_OSC</sub>       |            | _               |                |  |  |  |  |  |

| M2                                                                                                                                                                                                                                                      | V <sub>DD_HV_IO_RING</sub>   |            | _               |                |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | SIUL       | GPIO[56]        | GPIO[56]       |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | DSPI_1     | CS2             | _              |  |  |  |  |  |

| L16         L17         M1         M2         M3         M4         M6         M7         M8         M9         M10         M11         M12         M10         M11         M12         M14         M15         M16         M17         N12         N13 | D[8]                         | eTimer_1   | ETC[4]          | ETC[4]         |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | DSPI_0     | CS5             | _              |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | FlexPWM_0  | —               | FAULT[3]       |  |  |  |  |  |

| M4                                                                                                                                                                                                                                                      | Not connected                |            | _               |                |  |  |  |  |  |

| M6                                                                                                                                                                                                                                                      | V <sub>DD_LV</sub>           |            | _               |                |  |  |  |  |  |

| M7                                                                                                                                                                                                                                                      | V <sub>DD_LV</sub>           |            | _               |                |  |  |  |  |  |

| M8                                                                                                                                                                                                                                                      | V <sub>DD_LV</sub>           |            |                 |                |  |  |  |  |  |

| M9                                                                                                                                                                                                                                                      | V <sub>DD_LV</sub>           |            | _               |                |  |  |  |  |  |

| M10                                                                                                                                                                                                                                                     | V <sub>DD_LV</sub>           |            | _               |                |  |  |  |  |  |

| M11                                                                                                                                                                                                                                                     | V <sub>DD_LV</sub>           |            | _               |                |  |  |  |  |  |

| M12                                                                                                                                                                                                                                                     | V <sub>DD_LV</sub>           |            | —               |                |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | SIUL       | GPIO[43]        | GPIO[43]       |  |  |  |  |  |

| M14                                                                                                                                                                                                                                                     | C[11]                        | eTimer_0   | ETC[4]          | ETC[4]         |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | DSPI_2     | CS2             | —              |  |  |  |  |  |

| M15                                                                                                                                                                                                                                                     | B[5] -                       | SIUL       | GPIO[21]        | GPIO[21]       |  |  |  |  |  |

| IVI I J                                                                                                                                                                                                                                                 | B[3]                         | JTAGC      | _               | TDI            |  |  |  |  |  |

| M16                                                                                                                                                                                                                                                     | TMS                          |            | —               |                |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | SIUL       | GPIO[117]       | GPIO[117]      |  |  |  |  |  |

| M17                                                                                                                                                                                                                                                     | H[5]                         | FlexPWM_1  | A[0]            | A[0]           |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | DSPI_0     | CS4             | —              |  |  |  |  |  |

| N1                                                                                                                                                                                                                                                      | XTAL                         |            |                 |                |  |  |  |  |  |

| N2                                                                                                                                                                                                                                                      | V <sub>SS_HV_IO_RING</sub>   |            |                 |                |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | SIUL       | GPIO[53]        | GPIO[53]       |  |  |  |  |  |

| N3                                                                                                                                                                                                                                                      | D[5]                         | DSPI_0     | CS3             | _              |  |  |  |  |  |

|                                                                                                                                                                                                                                                         |                              | FlexPWM_0  | —               | FAULT[2]       |  |  |  |  |  |

| N4                                                                                                                                                                                                                                                      | V <sub>SS_LV_PLL0_PLL1</sub> |            |                 |                |  |  |  |  |  |

Table 5. LFBGA257 pin function summary (continued)

|                          | Supply                                                                                                                                                               |            | Pir        | า #                   |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------------------|

| Symbol                   | Description                                                                                                                                                          | 100<br>pkg | 144<br>pkg | 257<br>pkg            |

| V <sub>DD_HV_REG_1</sub> | VDD_HV_REG_1                                                                                                                                                         | 67         | 95         | H15                   |

| V <sub>SS_HV_FLA</sub>   | VSS_HV_FLA                                                                                                                                                           | 68         | 96         | J16                   |

| V <sub>DD_HV_FLA</sub>   | VDD_HV_FLA                                                                                                                                                           | 69         | 97         | H16                   |

| V <sub>DD_HV_IO</sub>    | VDD_HV_IO                                                                                                                                                            | 87         | 126        | VDD_HV <sup>(3)</sup> |

| V <sub>SS_HV_IO</sub>    | VSS_HV_IO                                                                                                                                                            | 88         | 127        | VSS_HV <sup>(4)</sup> |

| V <sub>DD_HV_REG_2</sub> | VDD_HV_REG_2                                                                                                                                                         | 91         | 130        | C7                    |

|                          | Power supply pins (1.2 V)                                                                                                                                            |            |            |                       |

| V <sub>SS_LV_COR</sub>   | VSS_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                      | 11         | 17         | VSS_HV <sup>(2)</sup> |

| V <sub>DD_LV_COR</sub>   | VDD_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest $V_{SS_LV_COR}$ pin.                      | 12         | 18         | VDD_LV <sup>(1)</sup> |

| V <sub>SS</sub> 1V2      | VSS_LV_PLL0_PLL1 /<br>1.2 V Decoupling pins for on-chip FMPLL modules. Decoupling<br>capacitor must be connected between this pin and V <sub>DD_LV_PLL</sub> .       | 24         | 35         | N4                    |

| V <sub>DD</sub> 1V2      | VDD_LV_PLL0_PLL1<br>Decoupling pins for on-chip FMPLL modules. Decoupling capacitor<br>must be connected between this pin and V <sub>SS_LV_PLL</sub> .               | 25         | 36         | P4                    |

| V <sub>DD_LV_COR</sub>   | VDD_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin.               | 28         | 39         | VDD_LV <sup>(1)</sup> |

| V <sub>SS_LV_COR</sub>   | VSS_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.               | 29         | 40         | VSS_LV <sup>(2)</sup> |

| V <sub>DD_LV_COR</sub>   | VDD_LV_COR<br>Decoupling pins for core logic and Regulator feedback. Decoupling<br>capacitor must be connected between this pins and V <sub>SS_LV_REGCOR</sub> .     | _          | 70         | VDD_LV <sup>(1)</sup> |

| V <sub>SS_LV_COR</sub>   | VSS_LV_REGCOR0<br>Decoupling pins for core logic and Regulator feedback. Decoupling<br>capacitor must be connected between this pins and V <sub>DD_LV_REGCOR</sub> . | _          | 71         | VSS_LV <sup>(2)</sup> |

| V <sub>DD_LV_COR</sub>   | VDD_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin.               | 65         | 93         | VDD_LV <sup>(1)</sup> |

| V <sub>SS_LV_COR</sub>   | VSS_LV_COR / 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV_COR\ pin.}$                   | 66         | 94         | VSS_LV <sup>(2)</sup> |

| V <sub>DD</sub> 1V2      | VDD_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                      | 92         | 131        | VDD_LV <sup>(1)</sup> |

| Table 6. | Supply | pins | (continued) |

|----------|--------|------|-------------|

|----------|--------|------|-------------|

| 78,               |               |                    |            |                     | Table 8. Pi | n muxing (cor | ntinued)              |                         |                             |            |            |            |            |  |

|-------------------|---------------|--------------------|------------|---------------------|-------------|---------------|-----------------------|-------------------------|-----------------------------|------------|------------|------------|------------|--|

| 78/165            | Port PCR name | Port BCB Barinhard | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull config during | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |            |  |

|                   |               | TOK                | renpherai  | function            | mux sel     | functions     | select                | reset                   | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 257<br>pkg |  |

|                   |               |                    | SIUL       | GPIO[11]            | ALT0        | GPIO[11]      | —                     |                         |                             |            |            |            |            |  |

|                   |               |                    | DSPI_2     | SCK                 | ALT1        | SCK           | PSMI[1];<br>PADSEL=1  |                         | м                           | s          | 82         | 120        |            |  |

|                   | A[11]         | PCR[11]            | FlexPWM_0  | A[0]                | ALT2        | A[0]          | PSMI[20];<br>PADSEL=0 | _                       |                             |            |            |            | D11        |  |

|                   |               |                    | FlexPWM_0  | A[2]                | ALT3        | A[2]          | PSMI[22];<br>PADSEL=0 |                         |                             |            |            |            |            |  |

|                   |               |                    | SIUL       | _                   | —           | EIRQ[10]      | —                     |                         |                             |            |            |            |            |  |

| Docl              |               |                    | SIUL       | GPIO[12]            | ALT0        | GPIO[12]      | —                     |                         |                             |            |            |            |            |  |

| D15               |               |                    | DSPI_2     | SOUT                | ALT1        | —             | —                     | M                       |                             |            |            |            |            |  |

| DocID15457 Rev 12 | A[12]         | PCR[12]            | FlexPWM_0  | A[2]                | ALT2        | A[2]          | PSMI[22];<br>PADSEL=1 |                         | — М                         | s          | 83         | 122        | A10        |  |

| v 12              |               |                    | FlexPWM_0  | B[2]                | ALT3        | B[2]          | PSMI[26];<br>PADSEL=0 |                         |                             |            |            |            |            |  |

|                   |               |                    | SIUL       | —                   | —           | EIRQ[11]      | —                     |                         |                             |            |            |            |            |  |

|                   |               |                    | SIUL       | GPIO[13]            | ALT0        | GPIO[13]      | —                     |                         |                             |            |            |            |            |  |

|                   |               |                    | FlexPWM_0  | B[2]                | ALT2        | B[2]          | PSMI[26];<br>PADSEL=1 |                         |                             |            |            |            |            |  |

|                   | A[13]         | PCR[13]            | DSPI_2     |                     | _           | SIN           | PSMI[2];<br>PADSEL=1  | _                       | М                           | s          | 95         | 136        | C6         |  |

|                   |               |                    | FlexPWM_0  | _                   | _           | FAULT[0]      | PSMI[16];<br>PADSEL=1 |                         |                             |            |            |            |            |  |

|                   |               |                    | SIUL       | _                   | —           | EIRQ[12]      | —                     |                         |                             |            |            |            |            |  |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

5

| Port                  |             | <b>D</b>   | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pa<br>spee | ad<br>əd <sup>(1)</sup> | Pin #      |            |          |   |

|-----------------------|-------------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-------------------------|------------|------------|----------|---|

| name                  | PCR         | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 25<br>pk |   |

| <b>C</b> [ <b>7</b> ] | PCR[87]     | SIUL       | GPIO[87]           | ALT0    | GPIO[87]  | —                     |                        | F          | S                       |            | 19         | J        |   |

| F[7]                  | PCR[07]     | NPC        | МСКО               | ALT2    | _         | _                     | _                      | Г          | 3                       | _          | 19         | J        |   |

| <b>E</b> [0]          |             | SIUL       | GPIO[88]           | ALT0    | GPIO[88]  | _                     |                        | F          | S                       |            | 20         | к        |   |

| F[8]                  | PCR[88]     | NPC        | MSEO[1]            | ALT2    | _         | _                     | _                      | Г          | 5                       | _          | 20         | ň        |   |

|                       |             | SIUL       | GPIO[89]           | ALT0    | GPIO[89]  | _                     |                        |            | F                       | S          |            | 22       | к |

| F[9]                  | PCR[89]     | NPC        | MSEO[0]            | ALT2    | _         | _                     |                        | Г          | 5                       | _          | 23         | ľ        |   |

|                       |             | SIUL       | GPIO[90]           | ALT0    | GPIO[90]  | _                     |                        | F          | <u>د</u>                |            | 24         |          |   |

| F[10]                 | PCR[90]     | NPC        | EVTO               | ALT2    | _         | _                     |                        | F          | S                       | _          | 24         | L1       |   |

| <b>F</b> [44]         |             | SIUL       | GPIO[91]           | ALT0    | GPIO[91]  | _                     |                        | М          | ¢                       |            | 25         |          |   |

| F[11]                 | PCR[91]     | NPC        | _                  | ALT2    | EVTI      | _                     |                        | IVI        | S                       | _          | 25         | L2       |   |

|                       |             | SIUL       | GPIO[92]           | ALT0    | GPIO[92]  | _                     |                        | — М        |                         |            |            |          |   |

| F[12]                 | PCR[92]     | eTimer_1   | ETC[3]             | ALT1    | ETC[3]    | PSMI[12];<br>PADSEL=2 |                        |            | S                       | _          | 106        | C,       |   |

|                       |             | SIUL       | _                  | _       | EIRQ[30]  | _                     |                        |            |                         |            |            |          |   |

|                       |             | SIUL       | GPIO[93]           | ALT0    | GPIO[93]  | —                     |                        |            |                         |            |            |          |   |

| F[13]                 | PCR[93]     | eTimer_1   | ETC[4]             | ALT1    | ETC[4]    | PSMI[13];<br>PADSEL=3 | M                      | М          | S                       | _          | 112        | B14      |   |