#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 96                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l5cbfqr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.13  | Main os  | scillator electrical characteristics       | 6 |

|-------|----------|--------------------------------------------|---|

| 3.14  |          | electrical characteristics                 |   |

| 3.15  |          |                                            |   |

|       |          | z RC oscillator electrical characteristics |   |

| 3.16  |          | ectrical characteristics                   |   |

|       | 3.16.1   | Input Impedance and ADC Accuracy 120       |   |

| 3.17  | Flash n  | nemory electrical characteristics 12       | 5 |

| 3.18  | SWG e    | lectrical characteristics 12               | 7 |

| 3.19  | AC spe   | cifications                                | 7 |

|       | 3.19.1   | Pad AC specifications                      | 7 |

| 3.20  | Reset s  | sequence                                   | 8 |

|       | 3.20.1   | Reset sequence duration 12                 | 8 |

|       | 3.20.2   | Reset sequence description 12              | 9 |

|       | 3.20.3   | Reset sequence trigger mapping 13          | 1 |

|       | 3.20.4   | Reset sequence — start condition           | 2 |

|       | 3.20.5   | External watchdog window134                | 4 |

| 3.21  | AC timi  | ng characteristics                         | 4 |

|       | 3.21.1   | RESET pin characteristics                  | 4 |

|       | 3.21.2   | WKUP/NMI timing                            | 6 |

|       | 3.21.3   | IEEE 1149.1 JTAG interface timing          | 6 |

|       | 3.21.4   | Nexus timing                               | 8 |

|       | 3.21.5   | External interrupt timing (IRQ pin)14      | 1 |

|       | 3.21.6   | DSPI timing                                | 2 |

| Packa | age cha  | racteristics                               | B |

| 4.1   | ECOPA    | ACK®                                       | 8 |

| 4.2   | Packag   | e mechanical data 14                       | 8 |

| Orde  | ring inf | ormation                                   | 3 |

| Povis | sion his | tory                                       | 4 |

4

5

6

The SRAM module provides the following features:

- System SRAM: 128 KB

- ECC on 32-bit word (syndrome of 7 bits)

- ECC covers SRAM bus address

- 1-bit error correction, 2-bit error detection

- Wait states:

- 1 wait state for frequencies =< 120 MHz</li>

- 0 wait states for frequencies =< 80 MHz</li>

## 1.5.7 Platform flash memory controller

The following list summarizes the key features of the flash memory controller:

- Single AHB port interface supports a 64-bit data bus. All AHB aligned and unaligned reads within the 32-bit container are supported. Only aligned word writes are supported.

- Array interfaces support a 128-bit read data bus and a 64-bit write data bus for each bank.

- Code flash (bank0) interface provides configurable read buffering and page prefetch support.

- Four page-read buffers (each 128 bits wide) and a prefetch controller support speculative reading and optimized flash access.

- Single-cycle read responses (0 AHB data-phase wait states) for hits in the buffers. The buffers implement a least-recently-used replacement algorithm to maximize performance.

- Programmable response for read-while-write sequences including support for stallwhile-write, optional stall notification interrupt, optional flash operation abort, and optional abort notification interrupt.

- Separate and independent configurable access timing (on a per bank basis) to support use across a wide range of platforms and frequencies.

- Support of address-based read access timing for emulation of other memory types.

- Support for reporting of single- and multi-bit error events.

- Typical operating configuration loaded into programming model by system reset.

The platform flash controller is replicated for each processor.

## 1.5.8 Platform Static RAM Controller (SRAMC)

The SRAMC module is the platform SRAM array controller, with integrated error detection and correction.

The main features of the SRAMC provide connectivity for the following interfaces:

- XBAR Slave Port (64-bit data path)

- ECSM (ECC Error Reporting, error injection and configuration)

- SRAM array

## 1.5.11 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

## 1.5.12 Interrupt Controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other.

The INTC provides the following features:

- Duplicated periphery

- Unique 9-bit vector per interrupt source

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Priority elevation for shared resource

The INTC is replicated for each processor.

| Pin # | Port/function                       | Peripheral | Output function | Input function |

|-------|-------------------------------------|------------|-----------------|----------------|

| 62    | V <sub>SS_HV_IO</sub>               |            | _               |                |

| 63    | V <sub>DD_HV_IO</sub>               |            | _               |                |

|       |                                     | SIUL       | GPIO[3]         | GPIO[3]        |

|       |                                     | eTimer_0   | ETC[3]          | ETC[3]         |

| 64    | A [0]                               | DSPI_2     | CS0             | CS0            |

| 64    | A[3]                                | FlexPWM_0  | B[3]            | B[3]           |

|       |                                     | MC_RGM     | —               | ABS[2]         |

|       |                                     | SIUL       | —               | EIRQ[3]        |

| 65    | V <sub>DD_LV_COR</sub>              |            | —               |                |

| 66    | V <sub>SS_LV_COR</sub>              |            | —               |                |

| 67    | V <sub>DD_HV_REG_1</sub>            |            | —               |                |

| 68    | V <sub>SS_HV_FLA</sub>              |            | —               |                |

| 69    | V <sub>DD_HV_FLA</sub>              |            | —               |                |

|       |                                     | SIUL       | GPIO[60]        | GPIO[60]       |

| 70    | D[12]                               | FlexPWM_0  | X[1]            | X[1]           |

|       |                                     | LINFlexD_1 | —               | RXD            |

|       |                                     | SIUL       | GPIO[45]        | GPIO[45]       |

| 71    | C[13]                               | eTimer_1   | ETC[1]          | ETC[1]         |

| 7.1   | 0[10]                               | CTU_0      | —               | EXT_IN         |

|       |                                     | FlexPWM_0  | —               | EXT_SYNC       |

|       |                                     | SIUL       | GPIO[46]        | GPIO[46]       |

| 72    | C[14]                               | eTimer_1   | ETC[2]          | ETC[2]         |

|       |                                     | CTU_0      | EXT_TGR         | _              |

|       |                                     | SIUL       | GPIO[62]        | GPIO[62]       |

| 73    | D[14]                               | FlexPWM_0  | B[1]            | B[1]           |

|       |                                     | eTimer_0   |                 | ETC[3]         |

| 74    | V <sub>PP_TEST</sub> <sup>(1)</sup> |            |                 |                |

|       |                                     | SIUL       | GPIO[4]         | GPIO[4]        |

|       |                                     | eTimer_1   | ETC[0]          | ETC[0]         |

| 75    | A[4]                                | DSPI_2     | CS1             | _              |

| 75    | <u>لي</u> اني                       | eTimer_0   | ETC[4]          | ETC[4]         |

|       |                                     | MC_RGM     | _               | FAB            |

|       |                                     | SIUL       | _               | EIRQ[4]        |

Table 3. LQFP100 pin function summary (continued)

| Table 3. LQFP100 pin function summary (continued) |                          |            |                 |                |  |  |  |  |

|---------------------------------------------------|--------------------------|------------|-----------------|----------------|--|--|--|--|

| Pin #                                             | Port/function            | Peripheral | Output function | Input function |  |  |  |  |

|                                                   |                          | SIUL       | GPIO[12]        | GPIO[12]       |  |  |  |  |

|                                                   |                          | DSPI_2     | SOUT            | —              |  |  |  |  |

| 83                                                | A[12]                    | FlexPWM_0  | A[2]            | A[2]           |  |  |  |  |

|                                                   |                          | FlexPWM_0  | B[2]            | B[2]           |  |  |  |  |

|                                                   |                          | SIUL       | EIRQ[11]        |                |  |  |  |  |

| 84                                                | JCOMP                    | _          | —               | JCOMP          |  |  |  |  |

|                                                   |                          | SIUL       | GPIO[47]        | GPIO[47]       |  |  |  |  |

|                                                   |                          | FlexRay    | CA_TR_EN        |                |  |  |  |  |

| 05                                                | 01451                    | eTimer_1   | ETC[0]          | ETC[0]         |  |  |  |  |

| 85                                                | C[15]                    | FlexPWM_0  | A[1]            | A[1]           |  |  |  |  |

|                                                   | -                        | CTU_0      | _               | EXT_IN         |  |  |  |  |

|                                                   |                          | FlexPWM_0  | _               | EXT_SYNC       |  |  |  |  |

|                                                   |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |  |  |  |

|                                                   |                          | FlexRay    | CA_TX           |                |  |  |  |  |

| 86                                                | D[0]                     | eTimer_1   | ETC[1]          | ETC[1]         |  |  |  |  |

|                                                   |                          | FlexPWM_0  | B[1]            | B[1]           |  |  |  |  |

| 87                                                | V <sub>DD_HV_IO</sub>    |            |                 |                |  |  |  |  |

| 88                                                | V <sub>SS_HV_IO</sub>    |            | _               |                |  |  |  |  |

|                                                   |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |  |  |  |

|                                                   | - Diol                   | FlexRay    | CB_TX           | _              |  |  |  |  |

| 89                                                | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |  |  |  |

|                                                   | -                        | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |

|                                                   |                          | SIUL       | GPIO[52]        | GPIO[52]       |  |  |  |  |

| 00                                                |                          | FlexRay    | CB_TR_EN        | _              |  |  |  |  |

| 90                                                | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |

|                                                   | -                        | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |

| 91                                                | V <sub>DD_HV_REG_2</sub> |            |                 |                |  |  |  |  |

| 92                                                | V <sub>DD_LV_COR</sub>   |            | _               |                |  |  |  |  |

| 93                                                | V <sub>SS_LV_COR</sub>   |            | _               |                |  |  |  |  |

|                                                   | _                        | SIUL       | GPIO[9]         | GPIO[9]        |  |  |  |  |

| 0.1                                               | 4 (0)                    | DSPI_2     | CS1             |                |  |  |  |  |

| 94                                                | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |

|                                                   |                          | FlexPWM_0  | _               | FAULT[0]       |  |  |  |  |

Table 3. LQFP100 pin function summary (continued)

| Table 4. LQFP144 pin function summary (continued) |                       |            |                 |                |  |  |  |  |

|---------------------------------------------------|-----------------------|------------|-----------------|----------------|--|--|--|--|

| Pin #                                             | Port/function         | Peripheral | Output function | Input function |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[49]        | GPIO[49]       |  |  |  |  |

| 3                                                 | D[4]                  | eTimer_1   | ETC[2]          | ETC[2]         |  |  |  |  |

| 3                                                 | D[1]                  | CTU_0      | EXT_TGR         | _              |  |  |  |  |

|                                                   |                       | FlexRay    | —               | CA_RX          |  |  |  |  |

|                                                   | FIA                   | SIUL       | GPIO[84]        | GPIO[84]       |  |  |  |  |

| 4                                                 | F[4]                  | NPC        | MDO[3]          |                |  |  |  |  |

| -                                                 | FIEL                  | SIUL       | GPIO[85]        | GPIO[85]       |  |  |  |  |

| 5                                                 | F[5]                  | NPC        | MDO[2]          | _              |  |  |  |  |

| 6                                                 | V <sub>DD_HV_IO</sub> |            |                 |                |  |  |  |  |

| 7                                                 | V <sub>SS_HV_IO</sub> |            | _               |                |  |  |  |  |

| •                                                 |                       | SIUL       | GPIO[86]        | GPIO[86]       |  |  |  |  |

| 8                                                 | F[6]                  | NPC        | MDO[1]          | _              |  |  |  |  |

| 9                                                 | MDO0                  |            |                 |                |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[7]         | GPIO[7]        |  |  |  |  |

| 10                                                | A[7]                  | DSPI_1     | SOUT            |                |  |  |  |  |

|                                                   |                       | SIUL       | _               | EIRQ[7]        |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[36]        | GPIO[36]       |  |  |  |  |

|                                                   |                       | DSPI_0     | CS0             | CS0            |  |  |  |  |

| 11                                                | C[4]                  | FlexPWM_0  | X[1]            | X[1]           |  |  |  |  |

|                                                   |                       | SSCM       | DEBUG[4]        | _              |  |  |  |  |

|                                                   |                       | SIUL       | —               | EIRQ[22]       |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[8]         | GPIO[8]        |  |  |  |  |

| 12                                                | A[8]                  | DSPI_1     | _               | SIN            |  |  |  |  |

|                                                   |                       | SIUL       | —               | EIRQ[8]        |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[37]        | GPIO[37]       |  |  |  |  |

|                                                   |                       | DSPI_0     | SCK             | SCK            |  |  |  |  |

| 13                                                | C[5]                  | SSCM       | DEBUG[5]        |                |  |  |  |  |

|                                                   |                       | FlexPWM_0  | _               | FAULT[3]       |  |  |  |  |

|                                                   |                       | SIUL       | _               | EIRQ[23]       |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[5]         | GPIO[5]        |  |  |  |  |

|                                                   |                       | DSPI_1     | CS0             | CS0            |  |  |  |  |

| 14                                                | A[5]                  | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |

|                                                   |                       | DSPI_0     | CS7             |                |  |  |  |  |

|                                                   |                       | SIUL       | _               | EIRQ[5]        |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

| Table 4. LQFP144 pin function summary (continued) |                        |            |                 |                |  |  |  |  |

|---------------------------------------------------|------------------------|------------|-----------------|----------------|--|--|--|--|

| Pin #                                             | Port/function          | Peripheral | Output function | Input function |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[104]       | GPIO[104]      |  |  |  |  |

|                                                   |                        | FlexRay    | DBG0            | —              |  |  |  |  |

| 81                                                | G[8]                   | DSPI_0     | CS1             | —              |  |  |  |  |

|                                                   |                        | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |

|                                                   |                        | SIUL       | —               | EIRQ[21]       |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[44]        | GPIO[44]       |  |  |  |  |

| 82                                                | C[12]                  | eTimer_0   | ETC[5]          | ETC[5]         |  |  |  |  |

|                                                   |                        | DSPI_2     | CS3             |                |  |  |  |  |

|                                                   | 0171                   | SIUL       | GPIO[103]       | GPIO[103]      |  |  |  |  |

| 83                                                | G[7]                   | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[2]         | GPIO[2]        |  |  |  |  |

|                                                   |                        | eTimer_0   | ETC[2]          | ETC[2]         |  |  |  |  |

|                                                   | 4.03                   | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |

| 84                                                | A[2]                   | DSPI_2     | _               | SIN            |  |  |  |  |

|                                                   |                        | MC_RGM     | _               | ABS[0]         |  |  |  |  |

|                                                   |                        | SIUL       | —               | EIRQ[2]        |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[101]       | GPIO[101]      |  |  |  |  |

| 85                                                | G[5]                   | FlexPWM_0  | X[3]            | X[3]           |  |  |  |  |

|                                                   |                        | DSPI_2     | CS3             | —              |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[21]        | GPIO[21]       |  |  |  |  |

| 86                                                | B[5]                   | JTAGC      | _               | TDI            |  |  |  |  |

| 87                                                | TMS                    |            | —               |                |  |  |  |  |

| 88                                                | ТСК                    |            | _               |                |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[20]        | GPIO[20]       |  |  |  |  |

| 89                                                | B[4]                   | JTAGC      | TDO             | _              |  |  |  |  |

| 90                                                | V <sub>SS_HV_IO</sub>  |            | _               |                |  |  |  |  |

| 91                                                | V <sub>DD_HV_IO</sub>  |            | _               |                |  |  |  |  |

|                                                   |                        | SIUL       | GPIO[3]         | GPIO[3]        |  |  |  |  |

|                                                   |                        | eTimer_0   | ETC[3]          | ETC[3]         |  |  |  |  |

|                                                   |                        | DSPI_2     | CS0             | CS0            |  |  |  |  |

| 92                                                | A[3]                   | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |

|                                                   |                        | MC_RGM     | —               | ABS[2]         |  |  |  |  |

|                                                   |                        | SIUL       | —               | EIRQ[3]        |  |  |  |  |

| 93                                                | V <sub>DD_LV_COR</sub> |            | <u> </u>        | 1              |  |  |  |  |

| 94                                                | V <sub>SS_LV_COR</sub> |            | _               |                |  |  |  |  |

|                                                   |                        |            |                 |                |  |  |  |  |

| Table 5. LFBGA257 pin function summary (continued) |                            |            |                 |                |  |  |  |  |  |

|----------------------------------------------------|----------------------------|------------|-----------------|----------------|--|--|--|--|--|

| Pin #                                              | Port/function              | Peripheral | Output function | Input function |  |  |  |  |  |

|                                                    |                            | SIUL       | GPIO[60]        | GPIO[60]       |  |  |  |  |  |

| G14                                                | D[12]                      | FlexPWM_0  | X[1]            | X[1]           |  |  |  |  |  |

|                                                    |                            | LINFlexD_1 | _               | RXD            |  |  |  |  |  |

| -                                                  |                            | SIUL       | GPIO[125]       | GPIO[125]      |  |  |  |  |  |

| G15                                                | H[13]                      | FlexPWM_1  | X[3]            | X[3]           |  |  |  |  |  |

|                                                    |                            | eTimer_2   | ETC[3]          | ETC[3]         |  |  |  |  |  |

|                                                    |                            | SIUL       | GPIO[121]       | GPIO[121]      |  |  |  |  |  |

| G16                                                | H[9]                       | FlexPWM_1  | B[1]            | B[1]           |  |  |  |  |  |

|                                                    |                            | DSPI_0     | CS7             | _              |  |  |  |  |  |

| G17                                                | CIEL                       | SIUL       | GPIO[102]       | GPIO[102]      |  |  |  |  |  |

| GI7                                                | G[6] -                     | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |  |

| 114                                                | 0[40]                      | SIUL       | GPIO[109]       | GPIO[109]      |  |  |  |  |  |

| H1                                                 | G[13] -                    | NPC        | MDO[10]         | _              |  |  |  |  |  |

| H2                                                 | V <sub>SS_HV_IO_RING</sub> |            | _               |                |  |  |  |  |  |

|                                                    |                            | SIUL       | GPIO[36]        | GPIO[36]       |  |  |  |  |  |

|                                                    |                            | DSPI_0     | CS0             | CS0            |  |  |  |  |  |

| H3                                                 | C[4]                       | FlexPWM_0  | X[1]            | X[1]           |  |  |  |  |  |

|                                                    |                            | SSCM       | DEBUG[4]        | _              |  |  |  |  |  |

|                                                    |                            | SIUL       | —               | EIRQ[22]       |  |  |  |  |  |

|                                                    |                            | SIUL       | GPIO[5]         | GPIO[5]        |  |  |  |  |  |

|                                                    |                            | DSPI_1     | CS0             | CS0            |  |  |  |  |  |

| H4                                                 | A[5]                       | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |  |

|                                                    |                            | DSPI_0     | CS7             | _              |  |  |  |  |  |

|                                                    |                            | SIUL       | —               | EIRQ[5]        |  |  |  |  |  |

| H6                                                 | V <sub>DD_LV</sub>         |            | _               |                |  |  |  |  |  |

| H7                                                 | V <sub>SS_LV</sub>         |            | _               |                |  |  |  |  |  |

| H8                                                 | V <sub>SS_LV</sub>         |            | _               |                |  |  |  |  |  |

| H9                                                 | V <sub>SS_LV</sub>         |            | _               |                |  |  |  |  |  |

| H10                                                | V <sub>SS_LV</sub>         |            |                 |                |  |  |  |  |  |

| H11                                                | V <sub>SS_LV</sub>         |            |                 |                |  |  |  |  |  |

| H12                                                | V <sub>DD_LV</sub>         |            |                 |                |  |  |  |  |  |

| H14                                                | V <sub>SS_LV</sub>         |            |                 |                |  |  |  |  |  |

| H15                                                | V <sub>DD_HV_REG_1</sub>   |            |                 |                |  |  |  |  |  |

| H16                                                | V <sub>DD_HV_FLA</sub>     |            |                 |                |  |  |  |  |  |

Table 5. LFBGA257 pin function summary (continued)

| Table 5. LFBGA257 pin function summary (continued)       Dia #     Dest(#unotion |                                                      |            |                 |                |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------|------------|-----------------|----------------|--|--|--|--|--|

| Pin #                                                                            | Port/function                                        | Peripheral | Output function | Input function |  |  |  |  |  |

| N14                                                                              | Not connected                                        |            | —               |                |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | GPIO[44]        | GPIO[44]       |  |  |  |  |  |

| N15                                                                              | C[12]                                                | eTimer_0   | ETC[5]          | ETC[5]         |  |  |  |  |  |

|                                                                                  |                                                      | DSPI_2     | CS3             | —              |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | GPIO[2]         | GPIO[2]        |  |  |  |  |  |

|                                                                                  |                                                      | eTimer_0   | ETC[2]          | ETC[2]         |  |  |  |  |  |

| N16                                                                              | 1010                                                 | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |  |

| NIO                                                                              | A[2] —                                               | DSPI_2     | —               | SIN            |  |  |  |  |  |

|                                                                                  |                                                      | MC_RGM     | —               | ABS[0]         |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | —               | EIRQ[2]        |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | GPIO[101]       | GPIO[101]      |  |  |  |  |  |

| N17                                                                              | G[5]                                                 | FlexPWM_0  | X[3]            | X[3]           |  |  |  |  |  |

|                                                                                  |                                                      | DSPI_2     | CS3             |                |  |  |  |  |  |

| P1                                                                               | V <sub>SS_HV_OSC</sub>                               |            | _               |                |  |  |  |  |  |

| P2                                                                               | RESET                                                |            | —               |                |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | GPIO[54]        | GPIO[54]       |  |  |  |  |  |

| P3                                                                               | D[6]                                                 | DSPI_0     | CS2             | —              |  |  |  |  |  |

| 15                                                                               | D[0]                                                 | FlexPWM_0  | X[3]            | X[3]           |  |  |  |  |  |

|                                                                                  |                                                      | FlexPWM_0  | —               | FAULT[1]       |  |  |  |  |  |

| P4                                                                               | V <sub>DD_LV_PLL0_PLL1</sub>                         |            |                 |                |  |  |  |  |  |

| P5                                                                               | $V_{\text{DD}\_\text{LV}\_\text{CORE}\_\text{RING}}$ |            | —               |                |  |  |  |  |  |

| P6                                                                               | $V_{SS\_LV\_CORE\_RING}$                             |            | —               |                |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | _               | GPIO[24]       |  |  |  |  |  |

| P7                                                                               | B[8]                                                 | eTimer_0   | _               | ETC[5]         |  |  |  |  |  |

|                                                                                  |                                                      | ADC_0      | —               | AN[1]          |  |  |  |  |  |

| P8                                                                               | Not connected                                        |            | _               |                |  |  |  |  |  |

| P9                                                                               | V <sub>SS_HV_IO_RING</sub>                           |            | _               |                |  |  |  |  |  |

| P10                                                                              | V <sub>DD_HV_IO_RING</sub>                           |            | —               |                |  |  |  |  |  |

|                                                                                  |                                                      | SIUL       | —               | GPIO[30]       |  |  |  |  |  |

| P11                                                                              | B[14] —                                              | eTimer_0   | —               | ETC[4]         |  |  |  |  |  |

|                                                                                  | נדיןס                                                | SIUL       | —               | EIRQ[19]       |  |  |  |  |  |

|                                                                                  |                                                      | ADC_1      |                 | AN[1]          |  |  |  |  |  |

| P12                                                                              | V <sub>DD_LV_CORE_RING</sub>                         |            | _               |                |  |  |  |  |  |

| P13                                                                              | V <sub>SS_LV_CORE_RING</sub>                         |            |                 |                |  |  |  |  |  |

| P14                                                                              | V <sub>DD_HV_IO_RING</sub>                           |            | _               |                |  |  |  |  |  |

Table 5. LFBGA257 pin function summary (continued)

|                   |       |         |            |                     | Table 8. Pi | n muxing (cor | tinued)               |                            |            |                               |            |            |            |  |  |  |  |  |

|-------------------|-------|---------|------------|---------------------|-------------|---------------|-----------------------|----------------------------|------------|-------------------------------|------------|------------|------------|--|--|--|--|--|

| 5                 | Port  | PCR     | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull<br>config during | Pa<br>spee | ad<br>ed <sup>(1)</sup> Pin # |            |            |            |  |  |  |  |  |

|                   | name  | FOR     | renpheral  | function            | mux sel     | functions     | select                | reset                      | SRC<br>= 1 | SRC<br>= 0                    | 100<br>pkg | 144<br>pkg | 257<br>pkg |  |  |  |  |  |

|                   |       |         | SIUL       | GPIO[14]            | ALT0        | GPIO[14]      | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         | FlexCAN_1  | TXD                 | ALT1        | —             | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   | A[14] | PCR[14] | eTimer_1   | ETC[4]              | ALT2        | ETC[4]        | PSMI[13];<br>PADSEL=0 |                            | — M        | S                             | 99         | 143        | B4         |  |  |  |  |  |

|                   |       |         | SIUL       | —                   | —           | EIRQ[13]      | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         | SIUL       | GPIO[15]            | ALT0        | GPIO[15]      | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

| D                 |       |         | eTimer_1   | ETC[5]              | ALT2        | ETC[5]        | PSMI[14];<br>PADSEL=1 | M                          | М          |                               | 100        | 144        |            |  |  |  |  |  |

| DocID15457 Rev 12 | A[15] | PCR[15] | FlexCAN_1  | _                   | _           | RXD           | PSMI[34];<br>PADSEL=0 |                            |            | M S                           |            |            | D3         |  |  |  |  |  |

| 157 Rev           |       |         | FlexCAN_0  | _                   | _           | RXD           | PSMI[33];<br>PADSEL=0 |                            |            |                               |            |            |            |  |  |  |  |  |

| v 12              |       |         | SIUL       | —                   | _           | EIRQ[14]      | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         |            |                     |             | Port B        |                       |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         | SIUL       | GPIO[16]            | ALT0        | GPIO[16]      | _                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         | FlexCAN_0  | TXD                 | ALT1        | _             | _                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   | B[0]  | PCR[16] | eTimer_1   | ETC[2]              | ALT2        | ETC[2]        | PSMI[11];<br>PADSEL=0 |                            | М          | M S                           | 76         | 109        | B15        |  |  |  |  |  |

|                   |       |         | SSCM       | DEBUG[0]            | ALT3        | _             | _                     |                            |            |                               |            |            |            |  |  |  |  |  |

|                   |       |         | SIUL       | _                   | —           | EIRQ[15]      | —                     |                            |            |                               |            |            |            |  |  |  |  |  |

Package pinouts and signal descriptions

| Port  | PCR      | Deninkenst | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pa<br>spe  | ad<br>ed <sup>(1)</sup> | Pin #      |            | Pin #    |  | Pin # |  |  |

|-------|----------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-------------------------|------------|------------|----------|--|-------|--|--|

| name  | PCR      | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 25<br>pk |  |       |  |  |

|       |          | SIUL       | GPIO[107]          | ALT0    | GPIO[107] | —                     |                        |            |                         |            |            |          |  |       |  |  |

| G[11] | PCR[107] | FlexRay    | DBG3               | ALT1    | _         | —                     | _                      | М          | S                       | _          | 75         | U        |  |       |  |  |

| 0[]   |          | FlexPWM_0  | —                  | _       | FAULT[3]  | PSMI[19];<br>PADSEL=2 |                        |            | C                       |            |            |          |  |       |  |  |

| G[12] | PCR[108] | SIUL       | GPIO[108]          | ALT0    | GPIO[108] | —                     |                        | F          | S                       |            |            | F        |  |       |  |  |

| G[12] | PCR[100] | NPC        | MDO[11]            | ALT2    | —         | —                     |                        | Г          | 5                       | _          |            |          |  |       |  |  |

| 0[40] | DCD[400] | SIUL       | GPIO[109]          | ALT0    | GPIO[109] | _                     |                        | F          | S                       |            |            | F        |  |       |  |  |

| G[13] | PCR[109] | NPC        | MDO[10]            | ALT2    | _         | _                     |                        | Г          | r S                     | _          |            |          |  |       |  |  |

| G[14] | PCR[110] | SIUL       | GPIO[110]          | ALT0    | GPIO[110] | _                     |                        | F          | S                       |            |            | A        |  |       |  |  |

| G[14] |          | NPC        | MDO[9]             | ALT2    | _         | —                     |                        | Г          | 3                       |            |            |          |  |       |  |  |

| G[15] | PCR[111] | SIUL       | GPIO[111]          | ALT0    | GPIO[111] | —                     |                        | F          | S                       |            |            |          |  |       |  |  |

| G[15] | FCR[11]  | NPC        | MDO[8]             | ALT2    | —         | _                     |                        | Г          | 3                       | _          |            | J2       |  |       |  |  |

|       |          |            | ·                  |         | Port H    |                       |                        |            |                         |            |            | •        |  |       |  |  |

| цюі   | PCR[112] | SIUL       | GPIO[112]          | ALT0    | GPIO[112] | —                     |                        | F          | S                       |            |            | A        |  |       |  |  |

| H[0]  | FCR[112] | NPC        | MDO[7]             | ALT2    | —         | _                     |                        | Г          | 3                       | _          |            |          |  |       |  |  |

| H[1]  | PCR[113] | SIUL       | GPIO[113]          | ALT0    | GPIO[113] | —                     |                        | F          | S                       |            |            | F        |  |       |  |  |

| пы    | FCR[113] | NPC        | MDO[6]             | ALT2    | —         | —                     |                        | Г          | 3                       | _          | _          |          |  |       |  |  |

| H[2]  | PCR[114] | SIUL       | GPIO[114]          | ALT0    | GPIO[114] | —                     |                        | F          | S                       |            |            |          |  | A     |  |  |

| пլ∠ј  | FCR[114] | NPC        | MDO[5]             | ALT2    | —         | —                     |                        | Г          | 3                       | _          |            |          |  |       |  |  |

| H[3]  | PCR[115] | SIUL       | GPIO[115]          | ALT0    | GPIO[115] | —                     |                        | F          | S                       |            | _          | 0        |  |       |  |  |

|       | FUR[110] | NPC        | MDO[4]             | ALT2    | _         | _                     | ] —                    |            | 3                       |            | —          | G1       |  |       |  |  |

Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

| Symbol                |                                                  | Parameter                                                 | Conditions              | Value | Unit |

|-----------------------|--------------------------------------------------|-----------------------------------------------------------|-------------------------|-------|------|

| P                     | D Thermal resistance junction-to-ambient natural |                                                           | Single layer board – 1s | 46    | °C/W |

| $R_{	extsf{	heta}JA}$ | D                                                | convection <sup>(2)</sup>                                 | Four layer board – 2s2p | 26    | 0/11 |

| Б                     | Thermal resistance, junction-to-ambient forced   |                                                           | Single layer board – 1s | 37    | °C/W |

| $R_{	hetaJMA}$        | D                                                | convection at 200 ft/min                                  | Four layer board – 2s2p | 22    | 0/11 |

| $R_{\theta JB}$       | D                                                | Thermal resistance junction-to-board <sup>(3)</sup>       | —                       | 13    | °C/W |

| $R_{\thetaJC}$        | D                                                | Thermal resistance junction-to-case <sup>(4)</sup>        | —                       | 8     | °C/W |

| $\Psi_{JT}$           | D                                                | Junction-to-package-top natural convection <sup>(5)</sup> | —                       | 2     | °C/W |

Table 14. Thermal characteristics for LFBGA257 package<sup>(1)</sup>

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Junction-to-Ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

3. Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

4. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

### Equation 1: $T_J = T_A + (R_{\theta JA} \times P_D)$

where:

T<sub>A</sub>= ambient temperature for the package (<sup>o</sup>C)

$R_{\theta JA}$ = junction to ambient thermal resistance (°C/W)

$P_D$ = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

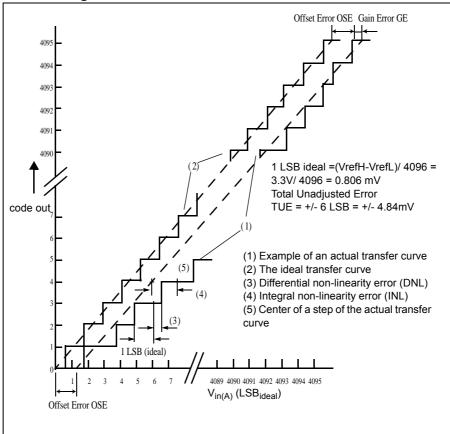

Figure 9. ADC characteristics and error definitions

## 3.16.1 Input Impedance and ADC Accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2}$  + CS equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ}$  = 1 / (fS\*( $C_{p2}$ + $C_S$ )), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S$  +  $R_F$ , the external circuit must be designed to respect the *Equation 4*:

| No.     | Symbol            |    | Parameter                                     | Conditions | T <sub>Reset</sub> |      |                    | Unit |

|---------|-------------------|----|-----------------------------------------------|------------|--------------------|------|--------------------|------|

| NO. Sym |                   | 01 | Falameter                                     | Conditions | Min                | Тур  | Max <sup>(1)</sup> | Onic |

| 1       | T <sub>DRB</sub>  | СС | Destructive Reset Sequence, BIST enabled      |            | 28                 | 34   | 39                 | ms   |

| 2       | T <sub>DR</sub>   | СС | Destructive Reset Sequence, BIST disabled     | —          | 500                | 4200 | 5000               | μS   |

| 3       | T <sub>ERLB</sub> | СС | External Reset Sequence Long, BIST<br>enabled |            | 28                 | 32   | 37                 | ms   |

| 4       | T <sub>FRL</sub>  | СС | Functional Reset Sequence Long                | —          | 35                 | 150  | 400                | μs   |

| 5       | T <sub>FRS</sub>  | СС | Functional Reset Sequence Short               | —          | 1                  | 4    | 10                 | μs   |

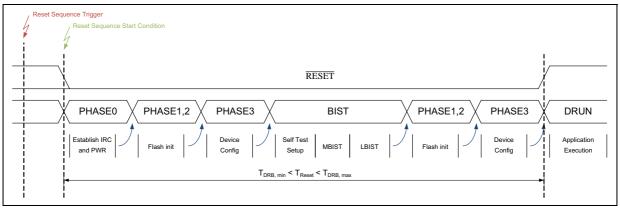

### Table 33. RESET sequences

1. The maximum value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET by an external reset generator.

## 3.20.2 Reset sequence description

The figures in this section show the internal states of the chip during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in *Table 33*. The start point and end point conditions as well as the reset trigger mapping to the different reset sequences are specified in *Section 3.20.3*.

With the beginning of DRUN mode the first instruction is fetched and executed. At this point application execution starts and the internal reset sequence is finished.

The figures below show the internal states of the chip during the execution of the reset sequence and the possible states of the signal pin RESET.

Note: RESET is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the chip internal reset circuitry. A high level on this pin can only be generated by an external pull up resistor which is strong enough to overdrive the weak internal pull down resistor. The rising edge on RESET in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in table Table 33 are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET asserted low beyond the last PHASE3.

### Figure 14. Destructive Reset Sequence, BIST enabled

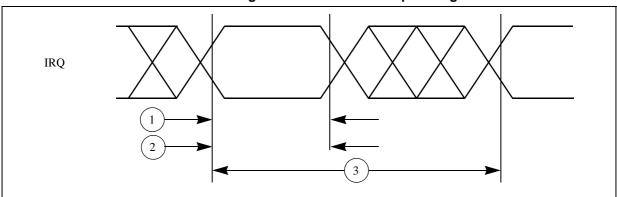

## Figure 31. External interrupt timing

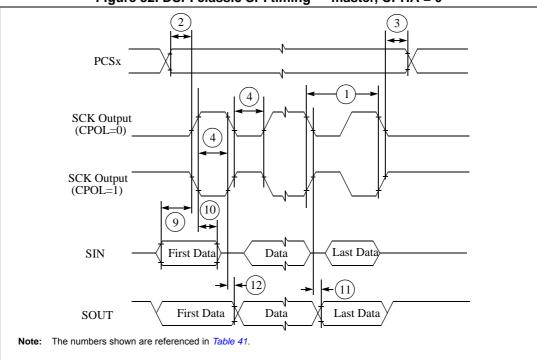

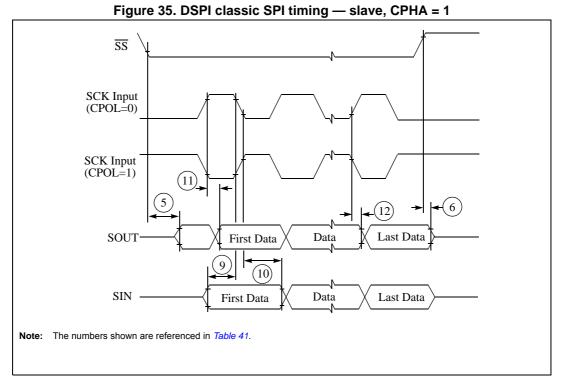

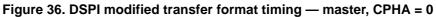

# 3.21.6 DSPI timing

|     |                      |    | la.                                                                   | ble 41. DSPI timing                    |                          |                          | 1    |  |

|-----|----------------------|----|-----------------------------------------------------------------------|----------------------------------------|--------------------------|--------------------------|------|--|

| No. | Symb                 | ol | Parameter                                                             | Conditions                             | Min                      | Max                      | Unit |  |

|     |                      | D  |                                                                       | Master (MTFE = 0)                      | 62                       | —                        |      |  |

| 1   | t <sub>SCK</sub>     | D  | DSPI cycle time                                                       | Slave (MTFE = 0)                       | 62                       | —                        | ns   |  |

|     |                      | D  |                                                                       | Slave Receive Only Mode <sup>(1)</sup> | 16                       | —                        |      |  |

| 2   | t <sub>CSC</sub>     | D  | PCS to SCK delay                                                      | —                                      | 16                       | —                        | ns   |  |

| 3   | t <sub>ASC</sub>     | D  | After SCK delay                                                       | —                                      | 16                       | —                        | ns   |  |

| 4   | t <sub>SDC</sub>     | D  | SCK duty cycle                                                        | —                                      | t <sub>SCK</sub> /2 - 10 | t <sub>SCK</sub> /2 + 10 | ns   |  |

| 5   | t <sub>A</sub>       | D  | Slave access time                                                     | SS active to SOUT valid                | —                        | 40                       | ns   |  |

| 6   | t <sub>DIS</sub>     | D  | Slave SOUT disable time         SS inactive to SOUT High-Z or invalid |                                        | _                        | 10                       | ns   |  |

| 7   | t <sub>PCSC</sub>    | D  | PCSx to PCSS time —                                                   |                                        | 13                       | —                        | ns   |  |

| 8   | t <sub>PASC</sub>    | D  | PCSS to PCSx time —                                                   |                                        | 13                       | —                        | ns   |  |

|     |                      |    | Data setup time for inputs                                            | Master (MTFE = 0)                      | 20                       | —                        |      |  |

| 9   | ÷                    | D  |                                                                       | Slave                                  | 2                        | —                        | 20   |  |

| 9   | t <sub>sui</sub>     |    |                                                                       | Master (MTFE = 1, CPHA = 0)            | 5                        | —                        | ns   |  |

|     |                      |    |                                                                       | Master (MTFE = 1, CPHA = 1)            | 20                       | —                        |      |  |

|     |                      |    |                                                                       | Master (MTFE = 0)                      | -5                       | —                        |      |  |

| 10  | 10 t <sub>HI</sub> E | D  | Data hold time for inputs                                             | Slave                                  | 4                        | —                        | -    |  |

| 10  |                      |    |                                                                       | Master (MTFE = 1, CPHA = 0)            | 11                       | —                        | ns   |  |

|     |                      |    |                                                                       | Master (MTFE = 1, CPHA = 1)            | -5                       | —                        |      |  |

|     | 11 +                 |    |                                                                       | Master (MTFE = 0)                      | —                        | 4                        | ns   |  |

| 11  |                      | D  | Data valid (after SCK edge)                                           | Slave                                  | _                        | 23                       |      |  |

|     | t <sub>suo</sub>     |    | Dala vallu (aller SUR euge)                                           | Master (MTFE = 1, CPHA = 0)            | _                        | 12                       | 115  |  |

|     |                      |    |                                                                       | Master (MTFE = 1, CPHA = 1)            | _                        | 4                        |      |  |

# Table 41. DSPI timing

| No. | Symb                 | ol | Parameter                  | Conditions                  | Min | Мах | Unit |

|-----|----------------------|----|----------------------------|-----------------------------|-----|-----|------|

|     |                      |    |                            | Master (MTFE = 0)           | -2  | —   |      |

| 12  | 12 t <sub>HO</sub> D | П  | Data hold time for outputs | Slave                       | 6   | —   | 20   |

| 12  |                      |    |                            | Master (MTFE = 1, CPHA = 0) | 6   | —   | ns   |

|     |                      |    |                            | Master (MTFE = 1, CPHA = 1) | -2  | —   |      |

### Table 41. DSPI timing (continued)

1. Slave Receive Only Mode can operate at a maximum frequency of 60 MHz. In this mode, the DSPI can receive data on SIN, but no valid data is transmitted on SOUT.

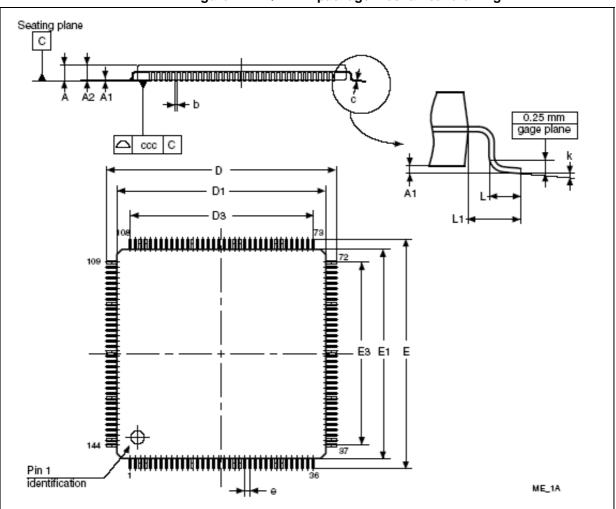

## Figure 42. LQFP144 package mechanical drawing

### Table 43. LQFP144 mechanical data

| Symbol |      | mm   |      |        | inches <sup>(1)</sup> |        |  |

|--------|------|------|------|--------|-----------------------|--------|--|

| Symbol | Тур  | Min  | Мах  | Тур    | Min                   | Max    |  |

| А      |      |      | 1.6  |        |                       | 0.0630 |  |

| A1     |      | 0.05 | 0.15 |        | 0.0020                | 0.0059 |  |

| A2     | 1.4  | 1.35 | 1.45 | 0.0551 | 0.0531                | 0.0571 |  |

| b      | 0.22 | 0.17 | 0.27 | 0.0087 | 0.0067                | 0.0106 |  |

| с      |      | 0.09 | 0.2  |        | 0.0035                | 0.0079 |  |

| D      | 22   | 21.8 | 22.2 | 0.8661 | 0.8583                | 0.8740 |  |

| D1     | 20   | 19.8 | 20.2 | 0.7874 | 0.7795                | 0.7953 |  |

| D3     | 17.5 |      |      | 0.6890 |                       |        |  |

| E      | 22   | 21.8 | 22.2 | 0.8661 | 0.8583                | 0.8740 |  |

| E1     | 20   | 19.8 | 20.2 | 0.7874 | 0.7795                | 0.7953 |  |

| Date        | Revision         | Table 45. Document revision history                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23-Nov-2010 | 5<br>(continued) | In the "BCP68 board schematic example" figure, removed the resistor at the base of the BCP68 transistor.<br>In the "DC electrical characteristics" table:<br>– Changed the guarantee parameter for I <sub>INJ</sub> (was P, is T).<br>– Added a specification for input leakage current for shared ADC input-only ports.<br>Revised the "Flash memory module life" table.<br>In the "FMPLL electrical characteristics" table, revised the footnote defining $f_{SCM}$ and $f_{VCO}$ .<br>In the "Main oscillator electrical characteristics" table:<br>– Changed the max specification for $g_{mXOSCHS}$ (was 11.8 mA/V, is 13.25 mA/V).<br>– Revised the conditions for $T_{XOSCHSSU}$ .<br>In the 'RC oscillator electrical characteristics" table, deleted the specification for $\Delta_{RCMTRIM}$ .<br>Revised the "ADC conversion characteristics" table.<br>In the "RESET pin characteristics" section, changed "nRSTIN" to "RESET".<br>Added the "Reset sequence" section.<br>Revised the footnotes in the "Nexus debug port timing" table.<br>Added the mechanical drawing for the 100-pin package.<br>In the "Order codes" table, added a footnote about frequency modulation to the "Speed (MH4)" column                                                                                                                                                                                                              |

| 23-Mar-2011 | 6                | <ul> <li>"Speed (MHz)" column heading.</li> <li>Editorial changes.</li> <li>In the "Document overview" section, added information about how content specific to silicon versions ("cut1" and "cut2") is presented.</li> <li>In the isometric miniature package drawings on the front page, removed the third dimension.</li> <li>Changed Symbol from P to D for "Conversion Time" in "ADC conversion characteristics" table.</li> <li>Added classification symbol "D" to seven entries in "Voltage regulator electrical specifications" table.</li> <li>Removed irrelevant FlexCAN specs.</li> <li>Updated Table "Voltage Thresholds" to reference values specified in Table "Voltage Regulator Electrical Specifications".</li> <li>RDY pin added for cut2.</li> <li>In the "System pins" table, added a footnote about the MDO0 pad speed.</li> <li>Updated Rsw1 values.</li> <li>Added AC Test Timing Conditions to the "AC timing characteristics" section.</li> <li>Added a statement on the first page describing cut1 versus cut2.</li> <li>Moved the first paragraph from the "Description" section to the beginning of the "Document overview" section.</li> <li>Changed pad speed from "M" to "SYM" for FlexRay pins in the "Pin Muxing" table and added this pad type to the footnote.</li> <li>Moved the newly added device current specification entries from the "DC electrical characteristics" table.</li> </ul> |

Table 45. Document revision history

|                     | Table 45. Document revision history |         |  |  |  |  |

|---------------------|-------------------------------------|---------|--|--|--|--|

| Date                | Revision                            | Changes |  |  |  |  |

| Date<br>23-Mar-2011 | Revision<br>6<br>(continued)        |         |  |  |  |  |

Table 45. Document revision history