#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 96                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l5cbfsy |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.5.13 System clocks and clock generation

The following list summarizes the system clock and clock generation on this device:

- Lock status continuously monitored by lock detect circuitry

- Loss-of-clock (LOC) detection for reference and feedback clocks

- On-chip loop filter (for improved electromagnetic interference performance and fewer external components required)

- Programmable output clock divider of system clock (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and as many as three eTimer modules running on an auxiliary clock independent from system clock (with max frequency 120 MHz)

- On-chip crystal oscillator with automatic level control

- Dedicated internal 16 MHz internal RC oscillator for rapid start-up

- Supports automated frequency trimming by hardware during device startup and by user application

- Auxiliary clock domain for motor control periphery (FlexPWM, eTimer, CTU, ADC, and SWG)

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- As many as 8 chip select lines available, depending on package and pin multiplexing

- 4 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering as many as 5 transfers on the transmit and receive side

- Queueing operation possible through use of the eDMA

- General purpose I/O functionality on pins when not used for SPI

### 1.5.30 FlexPWM

The pulse width modulator module (FlexPWM) contains four PWM channels, each of which is configured to control a single half-bridge power stage. Two modules are included on LFBGA257 devices; on the LQFP144 package, only one module is present. Additionally, four fault input channels are provided per FlexPWM module.

This PWM is capable of controlling most motor types, including:

- AC induction motors (ACIM)

- Permanent Magnet AC motors (PMAC)

- Brushless (BLDC) and brush DC motors (BDC)

- Switched (SRM) and variable reluctance motors (VRM)

- Stepper motors

A FlexPWM module implements the following features:

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- Maximum operating frequency as high as 120 MHz

- Clock source not modulated and independent from system clock (generated via secondary FMPLL)

- Fine granularity control for enhanced resolution of the PWM period

- PWM outputs can operate as complementary pairs or independent channels

- Ability to accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

### 1.5.40 Voltage regulator / Power Management Unit (PMU)

The on-chip voltage regulator module provides the following features:

- Single external rail required

- Single high supply required: nominal 3.3 V both for packaged and Known Good Die option

- Packaged option requires external ballast transistor due to reduced dissipation capacity at high temperature but can use embedded transistor if power dissipation is maintained within package dissipation capacity (lower frequency of operation)

- Known Good Die option uses embedded ballast transistor as dissipation capacity is increased to reduce system cost

- All I/Os are at same voltage as external supply (3.3 V nominal)

- Duplicated Low-Voltage Detectors (LVD) to guarantee proper operation at all stages (reset, configuration, normal operation) and, to maximize safety coverage, one LVD can be tested while the other operates (on-line self-testing feature)

## 1.5.41 Built-In Self-Test (BIST) capability

This device includes the following protection against latent faults:

- Boot-time Memory Built-In Self-Test (MBIST)

- Boot-time scan-based Logic Built-In Self-Test (LBIST)

- Run-time ADC Built-In Self-Test (BIST)

- Run-time Built-In Self Test of LVDs

|      | 1                          | 2                         | 3                            | 4                            | 5                          | 6                          | 7                            | 8                            | 9                           | 10                         | 11                         | 12                         | 13                         | 14                         | 15                           | 16                         | 17                        |

|------|----------------------------|---------------------------|------------------------------|------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|------------------------------|----------------------------|---------------------------|

| А    | V <sub>SS_HV_I</sub><br>0  | V <sub>SS_HV_I</sub><br>0 | V <sub>DD_HV_</sub><br>IO    | H[2]                         | H[0]                       | G[14]                      | D[3]                         | C[15]                        | V <sub>DD_HV_</sub><br>IO   | A[12]                      | H[10]                      | H[14]                      | A[10]                      | B[2]                       | C[10]                        | V <sub>SS_HV_I</sub><br>0  | V <sub>SS_HV_I</sub><br>0 |

| В    | V <sub>SS_HV_I</sub><br>0  | V <sub>SS_HV_I</sub><br>0 | B[6]                         | A[14]                        | F[3]                       | A[9]                       | D[4]                         | D[0]                         | V <sub>SS_HV_I</sub><br>0   | H[12]                      | E[15]                      | E[14]                      | B[3]                       | F[13]                      | B[0]                         | V <sub>DD_HV_</sub><br>IO  | V <sub>SS_HV_I</sub>      |

| С    | V <sub>DD_HV_</sub><br>IO  | NC <sup>(1)</sup>         | V <sub>SS_HV_I</sub><br>0    | FCCU_F<br>[1]                | D[2]                       | A[13]                      | V <sub>DD_HV_</sub><br>REG_2 | V <sub>DD_HV_</sub><br>REG_2 | I[0]                        | JCOMP                      | H[11]                      | I[1]                       | F[14]                      | B[1]                       | V <sub>SS_HV_I</sub><br>0    | A[4]                       | F[12]                     |

| D    | F[5]                       | F[4]                      | A[15]                        | C[6]                         | V <sub>SS_LV_</sub><br>COR | V <sub>DD_LV_</sub><br>cor | F[0]                         | V <sub>DD_HV_</sub><br>IO    | V <sub>SS_HV_I</sub><br>0   | NC                         | A[11]                      | E[13]                      | F[15]                      | V <sub>DD_HV_</sub><br>IO  | V <sub>PP</sub><br>_test     | D[14]                      | G[3]                      |

| Е    | MDO0                       | F[6]                      | D[1]                         | NMI                          |                            |                            |                              |                              |                             |                            |                            |                            |                            | NC                         | C[14]                        | G[2]                       | I[3]                      |

| F    | H[1]                       | G[12]                     | A[7]                         | A[8]                         |                            | V <sub>DD_LV_</sub><br>COR | V <sub>DD_LV_</sub><br>cor   | V <sub>DD_LV_</sub><br>cor   | V <sub>DD_LV_</sub><br>cor  | V <sub>DD_LV_</sub><br>cor | V <sub>DD_LV_</sub><br>cor | V <sub>DD_LV_</sub><br>cor |                            | NC                         | C[13]                        | I[2]                       | G[4]                      |

| G    | H[3]                       | V <sub>DD_HV_</sub><br>IO | C[5]                         | A[6]                         |                            | V <sub>DD_LV_</sub><br>COR | V <sub>SS_LV_</sub><br>COR   | V <sub>SS_LV_</sub><br>COR   | V <sub>SS_LV_</sub><br>COR  | V <sub>SS_LV_</sub><br>COR | V <sub>SS_LV_</sub><br>COR | V <sub>DD_LV_</sub><br>COR |                            | D[12]                      | H[13]                        | H[9]                       | G[6]                      |

| н    | G[13]                      | V <sub>SS_HV_I</sub>      | C[4]                         | A[5]                         |                            | V <sub>DD_LV</sub>         | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>          | V <sub>SS_LV</sub>         | V <sub>SS_LV</sub>         | V <sub>DD_LV</sub>         |                            | V <sub>SS_LV</sub>         | V <sub>DD_HV_</sub><br>REG_1 | V <sub>DD_HV_</sub><br>FLA | H[6]                      |

| J    | F[7]                       | G[15]                     | V <sub>DD_HV_</sub><br>REG_0 | V <sub>DD_HV_</sub><br>REG_0 |                            | V <sub>DD_LV</sub>         | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>          | V <sub>SS_LV</sub>         | V <sub>SS_LV</sub>         | V <sub>DD_LV</sub>         |                            | V <sub>DD_LV</sub>         | V <sub>DD_HV_</sub><br>REG_1 | V <sub>SS_HV_</sub>        | H[15]                     |

| к    | F[9]                       | F[8]                      |                              | C[7]                         |                            | V <sub>DD_LV</sub>         | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>          | V <sub>SS_LV</sub>         | V <sub>SS_LV</sub>         | V <sub>DD_LV</sub>         |                            | NC                         | H[8]                         | H[7]                       | A[3]                      |

| L    | F[10]                      | F[11]                     | D[9]                         | NC                           |                            | V <sub>DD_LV</sub>         | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>           | V <sub>SS_LV</sub>          | V <sub>SS_LV</sub>         | V <sub>SS_LV</sub>         | V <sub>DD_LV</sub>         |                            | NC                         | тск                          | H[4]                       | B[4]                      |

| М    | V <sub>DD_HV_</sub><br>osc | V <sub>DD_HV_</sub><br>IO | D[8]                         | NC                           |                            | V <sub>DD_LV</sub>         | V <sub>DD_LV</sub>           | V <sub>DD_LV</sub>           | V <sub>DD_LV</sub>          | V <sub>DD_LV</sub>         | V <sub>DD_LV</sub>         | V <sub>DD_LV</sub>         |                            | C[11]                      | B[5]                         | TMS                        | H[5]                      |

| Ν    | XTAL                       | V <sub>SS_HV_I</sub><br>0 | D[5]                         | V <sub>SS_LV_</sub><br>PLL   |                            |                            |                              |                              |                             |                            |                            |                            |                            | NC                         | C[12]                        | A[2]                       | G[5]                      |

| Ρ    | V <sub>SS_HV_</sub><br>osc | RESET                     | D[6]                         | V <sub>DD_LV_</sub><br>PLL   | V <sub>DD_LV_</sub><br>cor | V <sub>SS_LV_</sub><br>COR | B[8]                         | NC                           | V <sub>SS_HV_I</sub><br>0   | V <sub>DD_HV_</sub><br>IO  | B[14]                      | V <sub>DD_LV_</sub><br>cor | V <sub>SS_LV_</sub><br>COR | V <sub>DD_HV_</sub><br>IO  | G[10]                        | G[8]                       | G[7]                      |

| R    | EXTAL                      | FCCU<br>_F[0]             | V <sub>SS_HV_I</sub><br>0    | D[7]                         | B[7]                       | E[6]                       | V <sub>DD_HV_</sub><br>ADR0  | B[10]                        | V <sub>DD_HV_</sub><br>ADR1 | B[13]                      | B[15]                      | C[0]                       | BCTRL                      | A[1]                       | V <sub>SS_HV_I</sub><br>0    | D[11]                      | G[9]                      |

| т    | V <sub>SS_HV_I</sub><br>0  | V <sub>DD_HV_</sub><br>IO | NC                           | C[1]                         | E[5]                       | E[7]                       | V <sub>SS_HV_</sub><br>ADR0  | B[11]                        | V <sub>SS_HV_</sub><br>ADR1 | E[9]                       | E[10]                      | E[12]                      | E[0]                       | A[0]                       | D[10]                        | V <sub>DD_HV_</sub><br>IO  | V <sub>SS_HV_I</sub><br>0 |

| U    | V <sub>SS_HV_I</sub><br>0  | V <sub>SS_HV_I</sub><br>0 | NC                           | E[4]                         | C[2]                       | E[2]                       | B[9]                         | B[12]                        | V <sub>DD_HV_</sub><br>ADV  | V <sub>SS_HV_</sub><br>ADV | E[11]                      | NC                         | NC                         | V <sub>DD_HV_</sub><br>PMU | G[11]                        | V <sub>SS_HV_I</sub><br>0  | V <sub>SS_HV_I</sub><br>0 |

| 1    | 1                          | 2                         | 3                            | 4                            | 5                          | 6<br>ally pot              | 7                            | 8<br>stad to d               | 9                           | 10                         | 11                         | 12                         | 13                         | 14                         | 15                           | 16                         | 17                        |

| 1. 1 | NC = No                    | n conne                   | ecteu (tr                    | ie più is                    | s priysic                  | ally not                   | connec                       |                              | anyunng                     | y on the                   | uevice                     | ).                         |                            |                            |                              |                            |                           |

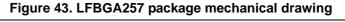

### Figure 4. SPC56ELx/SPC564Lx LFBGA257 pinout (top view)

*Table 3, Table 4*, and *Table 5* provide the pin function summaries for the 100-pin, 144-pin, and 257-pin packages, respectively, listing all the signals multiplexed to each pin.

| Table 4. LQFP144 pin function summary (continued) |                       |            |                 |                |  |  |  |  |  |  |  |  |

|---------------------------------------------------|-----------------------|------------|-----------------|----------------|--|--|--|--|--|--|--|--|

| Pin #                                             | Port/function         | Peripheral | Output function | Input function |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[49]        | GPIO[49]       |  |  |  |  |  |  |  |  |

| 3                                                 | D[4]                  | eTimer_1   | ETC[2]          | ETC[2]         |  |  |  |  |  |  |  |  |

| 3                                                 | D[1]                  | CTU_0      | EXT_TGR         | _              |  |  |  |  |  |  |  |  |

|                                                   |                       | FlexRay    | —               | CA_RX          |  |  |  |  |  |  |  |  |

|                                                   | FIA                   | SIUL       | GPIO[84]        | GPIO[84]       |  |  |  |  |  |  |  |  |

| 4                                                 | F[4]                  | NPC        | MDO[3]          |                |  |  |  |  |  |  |  |  |

| -                                                 | FIEL                  | SIUL       | GPIO[85]        | GPIO[85]       |  |  |  |  |  |  |  |  |

| 5                                                 | F[5]                  | NPC        | MDO[2]          | _              |  |  |  |  |  |  |  |  |

| 6                                                 | V <sub>DD_HV_IO</sub> |            |                 |                |  |  |  |  |  |  |  |  |

| 7                                                 | V <sub>SS_HV_IO</sub> |            | _               |                |  |  |  |  |  |  |  |  |

| •                                                 |                       | SIUL       | GPIO[86]        | GPIO[86]       |  |  |  |  |  |  |  |  |

| 8                                                 | F[6]                  | NPC        | MDO[1]          | _              |  |  |  |  |  |  |  |  |

| 9                                                 | MDO0                  |            |                 |                |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[7]         | GPIO[7]        |  |  |  |  |  |  |  |  |

| 10                                                | A[7]                  | DSPI_1     | SOUT            |                |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | _               | EIRQ[7]        |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[36]        | GPIO[36]       |  |  |  |  |  |  |  |  |

|                                                   |                       | DSPI_0     | CS0             | CS0            |  |  |  |  |  |  |  |  |

| 11                                                | C[4]                  | FlexPWM_0  | X[1]            | X[1]           |  |  |  |  |  |  |  |  |

|                                                   |                       | SSCM       | DEBUG[4]        | _              |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | —               | EIRQ[22]       |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[8]         | GPIO[8]        |  |  |  |  |  |  |  |  |

| 12                                                | A[8]                  | DSPI_1     | _               | SIN            |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | —               | EIRQ[8]        |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[37]        | GPIO[37]       |  |  |  |  |  |  |  |  |

|                                                   |                       | DSPI_0     | SCK             | SCK            |  |  |  |  |  |  |  |  |

| 13                                                | C[5]                  | SSCM       | DEBUG[5]        |                |  |  |  |  |  |  |  |  |

|                                                   |                       | FlexPWM_0  | _               | FAULT[3]       |  |  |  |  |  |  |  |  |

|                                                   | -                     | SIUL       | _               | EIRQ[23]       |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | GPIO[5]         | GPIO[5]        |  |  |  |  |  |  |  |  |

|                                                   |                       | DSPI_1     | CS0             | CS0            |  |  |  |  |  |  |  |  |

| 14                                                | A[5]                  |            |                 | ETC[5]         |  |  |  |  |  |  |  |  |

|                                                   |                       | DSPI_0     | CS7             | —              |  |  |  |  |  |  |  |  |

|                                                   |                       | SIUL       | _               | EIRQ[5]        |  |  |  |  |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

| Iable 4. LQFP144 pin function summary (continued)           Dia #         Destruction |                          |            |                 |                |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--------------------------|------------|-----------------|----------------|--|--|--|--|--|--|--|--|

| Pin #                                                                                 | Port/function            | Peripheral | Output function | Input function |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |  |  |  |  |  |  |  |

| 125                                                                                   | D[0]                     | FlexRay    | CA_TX           | _              |  |  |  |  |  |  |  |  |

| 120                                                                                   |                          | eTimer_1   | ETC[1]          | ETC[1]         |  |  |  |  |  |  |  |  |

|                                                                                       |                          | FlexPWM_0  | B[1]            |                |  |  |  |  |  |  |  |  |

| 126                                                                                   | V <sub>DD_HV_IO</sub>    |            | _               |                |  |  |  |  |  |  |  |  |

| 127                                                                                   | V <sub>SS_HV_IO</sub>    |            |                 |                |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |  |  |  |  |  |  |  |

| 128                                                                                   | 0121                     | FlexRay    | CB_TX           | _              |  |  |  |  |  |  |  |  |

| 120                                                                                   | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |  |  |  |  |  |  |  |

|                                                                                       |                          | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[52]        | GPI0[52]       |  |  |  |  |  |  |  |  |

| 100                                                                                   | DI4                      | FlexRay    | CB_TR_EN        |                |  |  |  |  |  |  |  |  |

| 129                                                                                   | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |  |  |  |  |

|                                                                                       |                          | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |  |  |  |  |

| 130                                                                                   | V <sub>DD_HV_REG_2</sub> |            | _               |                |  |  |  |  |  |  |  |  |

| 131                                                                                   | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |  |

| 132                                                                                   | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[80]        | GPIO[80]       |  |  |  |  |  |  |  |  |

| 133                                                                                   | FIOI                     | FlexPWM_0  | A[1]            | A[1]           |  |  |  |  |  |  |  |  |

| 155                                                                                   | F[0]                     | eTimer_0   | —               | ETC[2]         |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | —               | EIRQ[28]       |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[9]         | GPIO[9]        |  |  |  |  |  |  |  |  |

| 134                                                                                   | A101                     | DSPI_2     | CS1             | —              |  |  |  |  |  |  |  |  |

| 134                                                                                   | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |  |  |  |  |

|                                                                                       |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |  |

| 135                                                                                   | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | GPIO[13]        | GPIO[13]       |  |  |  |  |  |  |  |  |

|                                                                                       | [                        | FlexPWM_0  | B[2]            | B[2]           |  |  |  |  |  |  |  |  |

| 136                                                                                   | A[13]                    | DSPI_2     | —               | SIN            |  |  |  |  |  |  |  |  |

|                                                                                       |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |  |

|                                                                                       |                          | SIUL       | —               | EIRQ[12]       |  |  |  |  |  |  |  |  |

| 137                                                                                   | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

| Table 5. LFBGA257 pin function summary (continued) |                                     |                |                 |                |  |  |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------|----------------|-----------------|----------------|--|--|--|--|--|--|--|

| Pin #                                              | Port/function                       | Peripheral     | Output function | Input function |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[15]        | GPIO[15]       |  |  |  |  |  |  |  |

|                                                    |                                     | eTimer_1       | ETC[5]          | ETC[5]         |  |  |  |  |  |  |  |

| D3                                                 | A[15]                               | FlexCAN_1      | —               | RXD            |  |  |  |  |  |  |  |

|                                                    |                                     | FlexCAN_0      | —               | RXD            |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | —               | EIRQ[14]       |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[38]        | GPIO[38]       |  |  |  |  |  |  |  |

|                                                    |                                     | DSPI_0         | SOUT            | _              |  |  |  |  |  |  |  |

| D4                                                 | C[6]                                | FlexPWM_0      | B[1]            | B[1]           |  |  |  |  |  |  |  |

|                                                    |                                     | SSCM           | DEBUG[6]        | _              |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | _               | EIRQ[24]       |  |  |  |  |  |  |  |

| D5                                                 | V <sub>SS_LV_CORE_RING</sub>        |                | _               |                |  |  |  |  |  |  |  |

| D6                                                 | V <sub>DD_LV_CORE_RING</sub>        |                | _               |                |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[80]        | GPIO[80]       |  |  |  |  |  |  |  |

| D7                                                 |                                     | FlexPWM_0 A[1] |                 | A[1]           |  |  |  |  |  |  |  |

| D7                                                 | F[0] —                              | eTimer_0 —     |                 | ETC[2]         |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | _               | EIRQ[28]       |  |  |  |  |  |  |  |

| D8                                                 | V <sub>DD_HV_IO_RING</sub>          |                | _               |                |  |  |  |  |  |  |  |

| D9                                                 | V <sub>SS_HV_IO_RING</sub>          |                | _               |                |  |  |  |  |  |  |  |

| D10                                                | Not connected                       |                | _               |                |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[11]        | GPIO[11]       |  |  |  |  |  |  |  |

|                                                    |                                     | DSPI_2         | SCK             | SCK            |  |  |  |  |  |  |  |

| D11                                                | A[11]                               | FlexPWM_0      | A[0]            | A[0]           |  |  |  |  |  |  |  |

|                                                    |                                     | FlexPWM_0      | A[2]            | A[2]           |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL —         |                 | EIRQ[10]       |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[77]        | GPIO[77]       |  |  |  |  |  |  |  |

| D10                                                | <b>F</b> [40]                       | eTimer_0       | ETC[5]          | ETC[5]         |  |  |  |  |  |  |  |

| D12                                                | E[13] —                             | DSPI_2         | CS3             | _              |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | _               | EIRQ[25]       |  |  |  |  |  |  |  |

| D40                                                | F(4.5)                              | SIUL           | GPIO[95]        | GPIO[95]       |  |  |  |  |  |  |  |

| D13                                                | F[15] —                             | LINFlexD_1     | —               | RXD            |  |  |  |  |  |  |  |

| D14                                                | V <sub>DD_HV_IO_RING</sub>          |                | ·               |                |  |  |  |  |  |  |  |

| D15                                                | V <sub>PP_TEST</sub> <sup>(1)</sup> |                | _               |                |  |  |  |  |  |  |  |

|                                                    |                                     | SIUL           | GPIO[62]        | GPIO[62]       |  |  |  |  |  |  |  |

| D16                                                | D[14]                               | FlexPWM_0      | B[1]            | B[1]           |  |  |  |  |  |  |  |

|                                                    |                                     | eTimer_0       | —               | ETC[3]         |  |  |  |  |  |  |  |

Table 5. LFBGA257 pin function summary (continued)

92/165

DocID15457 Rev 12

| Port          |          | <b>_</b>   | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            |                 |

|---------------|----------|------------|--------------------|---------|-----------|-----------------------|------------------------|-----------------------------|------------|------------|------------|-----------------|

| name          | PCR      | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 257<br>pkg      |

|               |          |            |                    |         | FCCU      |                       |                        |                             |            |            |            |                 |

| FCCU_<br>F[0] | _        | FCCU       | F[0]               | ALT0    | F[0]      | _                     | _                      | S                           | S          | 27         | 38         | R2              |

| FCCU_<br>F[1] | _        | FCCU       | F[1]               | ALT0    | F[1]      | _                     | _                      | S                           | S          | 97         | 141        | C4              |

|               | <u> </u> |            |                    | L       | Port G    | •                     |                        |                             |            |            |            |                 |

|               |          | SIUL       | GPIO[98]           | ALT0    | GPIO[98]  |                       |                        |                             |            |            | 102        |                 |

| G[2]          | PCR[98]  | FlexPWM_0  | X[2]               | ALT1    | X[2]      | PSMI[29];<br>PADSEL=1 |                        | М                           | S          | _          |            | E1              |

|               |          | DSPI_1     | CS1                | ALT2    |           |                       |                        |                             |            |            |            |                 |

|               |          | SIUL       | GPIO[99]           | ALT0    | GPIO[99]  | _                     |                        |                             |            | _          | 104        |                 |

| G[3]          | PCR[99]  | FlexPWM_0  | A[2]               | ALT1    | A[2]      | PSMI[22];<br>PADSEL=2 |                        | М                           | S          |            |            | D1 <sup>-</sup> |

|               |          | eTimer_0   | _                  | _       | ETC[4]    | PSMI[7];<br>PADSEL=3  |                        |                             |            |            |            |                 |

|               |          | SIUL       | GPIO[100]          | ALT0    | GPIO[100] | _                     |                        |                             |            |            |            |                 |

| G[4]          | PCR[100] | FlexPWM_0  | B[2]               | ALT1    | B[2]      | PSMI[26];<br>PADSEL=2 |                        | М                           | s          | _          | 100        | F1 <sup>-</sup> |

|               |          | eTimer_0   | _                  | _       | ETC[5]    | PSMI[8];<br>PADSEL=3  |                        |                             |            |            |            |                 |

|               |          | SIUL       | GPIO[101]          | ALT0    | GPIO[101] |                       |                        |                             |            |            |            | N17             |

| G[5]          | PCR[101] | FlexPWM_0  | X[3]               | ALT1    | X[3]      | PSMI[30];<br>PADSEL=2 | _                      | М                           | S          | _          | 85         |                 |

|               |          | DSPI 2     | CS3                | ALT2    | _         | _                     | 1                      |                             |            |            |            |                 |

| Cumh              |    | Deveneter                                    | Conditions <sup>(1)</sup>                                  |     | Unit |     |      |

|-------------------|----|----------------------------------------------|------------------------------------------------------------|-----|------|-----|------|

| Symbo             | DI | Parameter                                    | Conditions                                                 | Min | Тур  | Max | Unit |

| C <sub>PMU1</sub> | SR | External decoupling /<br>stability capacitor | Accuracy -50%/+35%.                                        |     | 10   |     | μF   |

| C <sub>PMU2</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 100  |     | nF   |

| C <sub>REG</sub>  | SR | External decoupling /<br>stability capacitor | Accuracy -50%/+35%.                                        |     | 20   |     | μF   |

| C <sub>IO1</sub>  | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 100  |     | nF   |

| C <sub>IO2</sub>  | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 470  |     | pF   |

| C <sub>FLA1</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 100  |     | nF   |

| C <sub>FLA2</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 10   |     | nF   |

| C <sub>OSC1</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 100  |     | nF   |

| C <sub>OSC2</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.                                        |     | 10   |     | nF   |

| C <sub>PLL1</sub> | SR | External decoupling /<br>stability capacitor |                                                            | 22  |      | 100 | nF   |

| C <sub>ADR1</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Ceramic capacitor.                  |     | 10   |     | nF   |

| C <sub>ADR2</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Ceramic capacitor.                  |     | 47   |     | nF   |

| C <sub>ADR3</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Electrolytic or tantalum capacitor. |     | 1    |     | μF   |

| C <sub>ADV1</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Ceramic capacitor.                  |     | 10   |     | nF   |

| C <sub>ADV2</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Ceramic capacitor.                  |     | 47   |     | nF   |

| C <sub>ADV3</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Electrolytic or tantalum capacitor. |     | 1    |     | μF   |

1. Capacitors shall be placed as close as possible to the respective pads.

2. Total ESR considering all decoupling capacitor close to the  $V_{DD}/V_{SS\_LV\_CORy}$  pairs shall be between 1 m $\Omega$  and 100 m $\Omega$ .

# 3.6 Electromagnetic Interference (EMI) characteristics

The characteristics in *Table 16* were measured using:

- Device configuration, test conditions, and EM testing per standard IEC61967-2

- Supply voltage of 3.3 V DC

- Ambient temperature of 25 °C

The configuration information referenced in Table 16 is explained in Table 15.

| Table 15. EMI configuration summary |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Configuration name                  | Description                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Configuration A                     | <ul> <li>High emission = all pads have max slew rate, LVDS pads running at 40 MHz</li> <li>Oscillator frequency = 40 MHz</li> <li>System bus frequency = 80 MHz</li> <li>No PLL frequency modulation</li> <li>IEC level I (≤ 36 dBµV)</li> </ul>                                                    |  |  |  |  |  |  |  |

| Configuration B                     | $\begin{array}{l} - \mbox{ Reference emission = pads use min, mid and max slew rates, LVDS pads disabled} \\ - \mbox{ Oscillator frequency = 40 MHz} \\ - \mbox{ System bus frequency = 80 MHz} \\ - \mbox{ 2\% PLL frequency modulation} \\ - \mbox{ IEC level } K(\leq 30 \ dB\mu V) \end{array}$ |  |  |  |  |  |  |  |

|                  |                 | Table 1            | 6. EMI emission testing specification              | ons |     |     |      |  |

|------------------|-----------------|--------------------|----------------------------------------------------|-----|-----|-----|------|--|

| Symb             | ymbol Parameter |                    | Conditions                                         | Min | Тур | Max | Unit |  |

|                  |                 |                    | Configuration A; frequency range<br>150 kHz–50 MHz | _   | 16  | _   |      |  |

|                  |                 |                    | Configuration A; frequency range 50–<br>150 MHz    | _   | 16  | _   |      |  |

|                  |                 |                    | Configuration A; frequency range 150–<br>500 MHz   | _   | 32  | _   |      |  |

| M                | сс              | Radiated emissions | Configuration A; frequency range 500–<br>1000 MHz  | _   | 25  | _   | dBµV |  |

| V <sub>EME</sub> | CC              | Radiated emissions | Configuration B; frequency range 50–<br>150 MHz    | _   | 15  | _   | υσμν |  |

|                  |                 |                    | Configuration B; frequency range 50–<br>150 MHz    | _   | 21  | _   |      |  |

|                  |                 | 500 M<br>Config    | Configuration B; frequency range 150–<br>500 MHz   | _   | 30  | _   |      |  |

|                  |                 |                    | Configuration B; frequency range 500–<br>1000 MHz  | _   | 24  | _   |      |  |

EMC testing was performed and documented according to these standards: [IEC61508-2-7.4.5.1.b, IEC61508-2-7.2.3.2.e, IEC61508-2-Table-A.17 (partially), IEC61508-2-Table-B.5(partially),SRS2110]

- 2. "SR" parameter values must not exceed the absolute maximum ratings shown in *Table 9*.

- 3. The max input voltage on the ADC pins is the ADC reference voltage VDD\_HV\_ADRx.

- 4. Measured values are applicable to all modes of the pad i.e. IBE = 0/1 and / or APC= 0/1.

# 3.11 Supply current characteristics

Current consumption data is given in *Table 22*. These specifications are design targets and are subject to change per device characterization.

| Symbol                                                            |   | Parameter            | Conditions <sup>(1)</sup>                                                                                                  | Min | Тур | Мах                                      | Unit |  |

|-------------------------------------------------------------------|---|----------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------|------|--|

| IDD_LV_FULL                                                       | т | Operating current    | 1.2 V supplies<br>T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                                | _   | _   | 50 mA+<br>2.18 mA*f <sub>CPU</sub> [MHz] | mA   |  |

| + IDD_LV_PLL                                                      |   |                      | 1.2 V supplies<br>T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                               | _   | _   | 80 mA+<br>2.50 mA*f <sub>CPU</sub> [MHz] | ША   |  |

| IDD LV TYP                                                        | т | Operating current    | 1.2 V supplies<br>T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                                | _   | _   | 26 +<br>2.10 mA*f <sub>CPU</sub> [MHz]   | mA   |  |

| I <sub>DD_LV_TYP</sub><br>+ I <sub>DD_LV_PLL</sub> <sup>(2)</sup> |   |                      | 1.2 V supplies<br>T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                               | _   | _   | 41 mA+<br>2.30 mA*f <sub>CPU</sub> [MHz] | ШA   |  |

| IDD_LV_BIST                                                       | т | Or and the automatic | 1.2 V supplies during<br>LBIST (full LBIST<br>configuration)<br>$T_J = 25 °C$<br>$V_{DD_LV_COR} = 1.32 V$                  | _   | _   | 250                                      |      |  |

| + I <sub>DD_LV_PLL</sub>                                          | 1 | Operating current    | 1.2 V supplies during<br>LBIST (full LBIST<br>configuration)<br>$T_J = 150 \text{ °C}$<br>$V_{DD_LV_COR} = 1.32 \text{ V}$ | _   | _   | 290                                      | mA   |  |

| I <sub>DD_LV_TYP</sub><br>+ I <sub>DD_LV_PLL</sub> (2)            | P | Operating current    | 1.2 V supplies<br>T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V<br>LSM mode                                    | _   | _   | 279                                      | mA   |  |

| T 'DD_LV_PLL'                                                     |   |                      | $T_J$ = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V<br>LSM mode                                                              | _   | —   | 318                                      | mA   |  |

Table 22. Current consumption characteristics

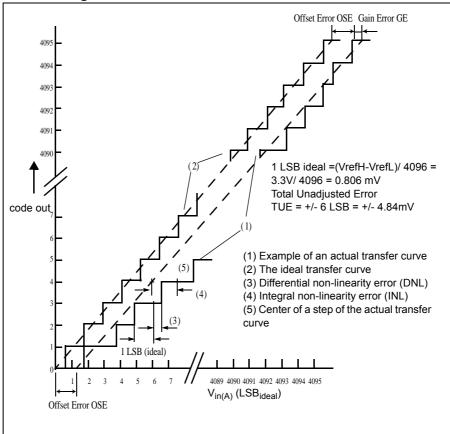

Figure 9. ADC characteristics and error definitions

# 3.16.1 Input Impedance and ADC Accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2}$  + CS equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ}$  = 1 / (fS\*( $C_{p2}$ + $C_S$ )), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S$  +  $R_F$ , the external circuit must be designed to respect the *Equation 4*:

#### **Electrical characteristics**

- Initial Max program and erase times provide guidance for time-out limits used in the factory and apply for <100

program/erase cycles, nominal supply values and operation at 25°C. These values are verified at production test.</li>

- 3. Lifetime Max program and erase times apply across the voltage, temperature, and cycling range of product life. These values are characterized, but not tested.

- 4. Program times are actual hardware programming times and do not include software overhead.

| Symbol            |   | Parameter                                                                                                   |     | Unit |     |      |

|-------------------|---|-------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                   |   | Falainetei                                                                                                  | Min | Тур  | Max | onic |

| T <sub>RES</sub>  | D | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1<br>until DONE goes low                             | —   | —    | 100 | ns   |

| T <sub>DONE</sub> | D | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared | _   | _    | 5   | ns   |

| T <sub>PSRT</sub> | D | Time between program suspend resume and the next program suspend request. <sup>(1)</sup>                    | 100 | _    | _   | μs   |

| T <sub>ESRT</sub> | D | Time between erase suspend resume and the next erase suspend request. <sup>(2)</sup>                        | 10  |      |     | ms   |

### Table 29. Flash memory timing

Repeated suspends at a high frequency may result in the operation timing out, and the flash module will respond by completing the operation with a fail code (MCR[PEG] = 0), or the operation not able to finish (MCR[DONE] = 1 during Program operation). The minimum time between suspends to ensure this does not occur is T<sub>PSRT</sub>.

If Erase suspend rate is less than T<sub>ESRT</sub>, an increase of slope voltage ramp occurs during erase pulse. This improves erase time but reduces cycling figure due to overstress.

| No. | Symbol        |          | Parameter                                                                                                                                                                                      |               | Value         |         | Unit   |

|-----|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------|--------|

| NO. | Symbol        |          | raiametei                                                                                                                                                                                      | Minimum       | Typical       | Maximum | Unit   |

| 1   | P/E           | C 4      | lumber of program/erase cycles per block for 16 KB,<br>8 KB, and 64 KB blocks over the operating<br>emperature range <sup>(1)</sup>                                                            | 100000        | _             | _       | cycles |

| 2   | P/E           | Ca       | Jumber of program/erase cycles per block for 128 KB<br>and 256 KB blocks over the operating temperature<br>ange <sup>(1)</sup>                                                                 | 1000          | 100000<br>(2) | _       | cycles |

| 3   | Retenti<br>on | C B<br>B | Ainimum data retention at 85 °C average ambient<br>emperature <sup>(3)</sup><br>Blocks with 0–1,000 P/E cycles<br>Blocks with 1,001–10,000 P/E cycles<br>Blocks with 10,001–100,000 P/E cycles | 20<br>10<br>5 |               |         | years  |

### Table 30. Flash memory module life

1. Operating temperature range is T<sub>J</sub> from –40 °C to 150 °C. Typical endurance is evaluated at 25 °C.

2. Typical P/E cycles is 100,000 cycles for 128 KB and 256 KB blocks.

3. Ambient temperature averaged over duration of application, not to exceed product operating temperature range.

# **3.18 SWG electrical characteristics**

| O much a l | Demonster                             | Value   |         |         |  |  |  |  |  |

|------------|---------------------------------------|---------|---------|---------|--|--|--|--|--|

| Symbol     | Parameter                             | Minimum | Typical | Maximum |  |  |  |  |  |

| Т          | Input clock                           | 12 MHz  | 16 MHz  | 20 MHz  |  |  |  |  |  |

| Т          | Frequency Range                       | 1 kHz   | _       | 50 kHz  |  |  |  |  |  |

| Т          | Peak to Peak <sup>(1)</sup>           | 0.4 V   | _       | 2.0V    |  |  |  |  |  |

| Т          | Peak to Peak variation <sup>(2)</sup> | -6%     | _       | 6%      |  |  |  |  |  |

| Т          | Common Mode <sup>(3)</sup>            | —       | 1.3 V   | _       |  |  |  |  |  |

| Т          | Common Mode variation                 | -6%     | _       | 6%      |  |  |  |  |  |

| Т          | SiNAD <sup>(4)</sup>                  | 45 dB   | _       |         |  |  |  |  |  |

| Г          | Load C                                | 25 pF   |         | 100 pF  |  |  |  |  |  |

| Г          | Load I                                | 0 μΑ    | _       | 100 µA  |  |  |  |  |  |

| Т          | ESD Pad Resistance <sup>(5)</sup>     | 230 Ω   |         | 360 Ω   |  |  |  |  |  |

#### Table 31. SPC56XL60/54 SWG Specifications

1. Peak to Peak value is measured with no R or I load.

2. Peak to Peak excludes noise, SiNAD must be considered.

3. Common mode value is measured with no R or I load.

4. SiNAD is measured at Max Peak to Peak voltage.

5. Internal device routing resistance. ESD pad resistance is in series and must be considered for max Peak to Peak voltages, depending on application I load and/or R load.

# 3.19 AC specifications

# 3.19.1 Pad AC specifications

Table 32. Pad AC specifications  $(3.3 \text{ V}, \text{IPP}_\text{HVE} = 0)^{(1)}$

|     | Pad    |      | Tswitchon <sup>(1)</sup> (ns) |     | Rise/Fall <sup>(2)</sup><br>(ns) |     | Frequency<br>(MHz) |     | Current slew <sup>(3)</sup><br>(mA/ns) |     |     | Load |      |     |               |     |

|-----|--------|------|-------------------------------|-----|----------------------------------|-----|--------------------|-----|----------------------------------------|-----|-----|------|------|-----|---------------|-----|

| No. |        |      | Min                           | Тур | Max                              | Min | Тур                | Max | Min                                    | Тур | Max | Min  | Тур  | Max | drive<br>(pF) |     |

|     |        |      | 3                             |     | 40                               | _   |                    | 40  | _                                      |     | 4   | 0.01 | _    | 2   | 25            |     |

| 1   | Slow   | Slow | т                             | 3   |                                  | 40  | _                  |     | 50                                     | _   |     | 2    | 0.01 | _   | 2             | 50  |

|     | 310W   | '    | 3                             |     | 40                               | _   |                    | 75  | _                                      |     | 2   | 0.01 | _    | 2   | 100           |     |

|     |        |      | 3                             | —   | 40                               | _   |                    | 100 | _                                      | —   | 2   | 0.01 | _    | 2   | 200           |     |

|     |        |      | 1                             | —   | 15                               | _   | —                  | 12  | _                                      | —   | 40  | 2.5  | _    | 7   | 25            |     |

| 2   | Medium | т    | 1                             | —   | 15                               | _   | —                  | 25  | _                                      | —   | 20  | 2.5  | _    | 7   | 50            |     |

| 2   |        |      | 1                             | —   | 15                               | —   | —                  | 40  | —                                      | —   | 13  | 2.5  | _    | 7   | 100           |     |

|     |        |      |                               | 1   | _                                | 15  | _                  |     | 70                                     | _   |     | 7    | 2.5  | _   | 7             | 200 |

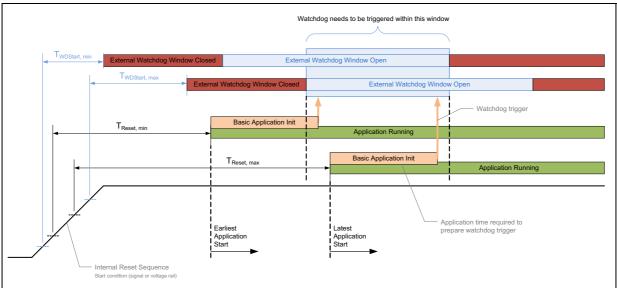

# 3.20.5 External watchdog window

If the application design requires the use of an external watchdog the data provided in Section 3.20 can be used to determine the correct positioning of the trigger window for the external watchdog. *Figure 21* shows the relationships between the minimum and the maximum duration of a given reset sequence and the position of an external watchdog trigger window.

# 3.21 AC timing characteristics

AC Test Timing Conditions: Unless otherwise noted, all test conditions are as follows:

- TJ = -40 to 150 °C

- Supply voltages as specified in Table 10

- Input conditions: All Inputs: tr, tf = 1 ns

- Output Loading: All Outputs: 50 pF

# 3.21.1 **RESET** pin characteristics

The SPC56ELx/SPC564Lx implements a dedicated bidirectional RESET pin.

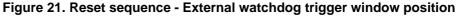

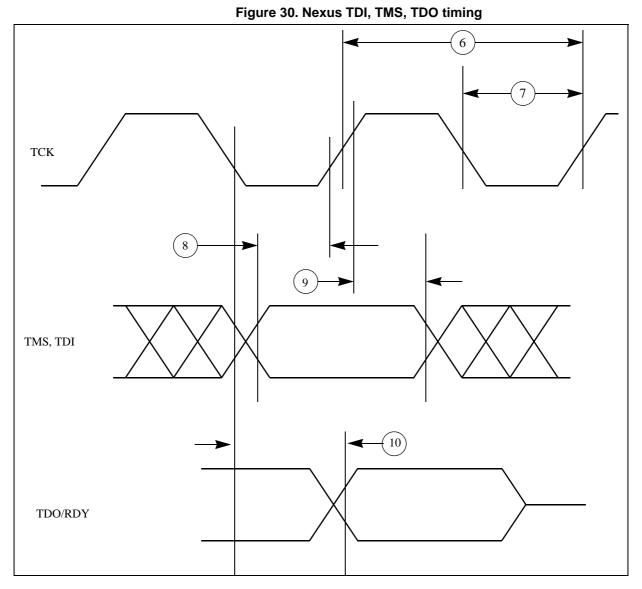

Figure 29. Nexus Double Data Rate (DDR) Mode output timing

# 3.21.5 External interrupt timing (IRQ pin)

### Table 40. External interrupt timing

| No. | Symb              | ol | Parameter                            | Conditions | Min | Max | Unit             |

|-----|-------------------|----|--------------------------------------|------------|-----|-----|------------------|

| 1   | t <sub>IPWL</sub> | D  | IRQ pulse width low                  | —          | 3   | _   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | D  | IRQ pulse width high                 | —          | 3   | —   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | D  | IRQ edge to edge time <sup>(1)</sup> | _          | 6   | _   | t <sub>CYC</sub> |

1. Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

51

| Querra ha e l |      | mm   |      | inches <sup>(1)</sup> |        |        |  |  |  |

|---------------|------|------|------|-----------------------|--------|--------|--|--|--|

| Symbol        | Тур  | Min  | Max  | Тур                   | Min    | Max    |  |  |  |

| E3            | 17.5 |      |      | 0.6890                |        |        |  |  |  |

| е             | 0.5  |      |      | 0.0197                |        |        |  |  |  |

| L             | 0.6  | 0.45 | 0.75 | 0.0236                | 0.0177 | 0.0295 |  |  |  |

| L1            | 1    |      |      | 0.0394                |        |        |  |  |  |

| k             | 3.5° | 0.0° | 7.0° | 3.5°                  | 0.0°   | 7.0°   |  |  |  |

| Tolerance     |      | mm   |      |                       | inches |        |  |  |  |

| CCC           |      | 0.08 |      | 0.0031                |        |        |  |  |  |

Table 43. LQFP144 mechanical data (continued)

1. Values in inches are converted from mm and rounded to four decimal digits.

DocID15457 Rev 12

| Date        | Revision         | Table 45. Document revision history                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23-Nov-2010 | 5<br>(continued) | In the "BCP68 board schematic example" figure, removed the resistor at the base of the BCP68 transistor.<br>In the "DC electrical characteristics" table:<br>– Changed the guarantee parameter for I <sub>INJ</sub> (was P, is T).<br>– Added a specification for input leakage current for shared ADC input-only ports.<br>Revised the "Flash memory module life" table.<br>In the "FMPLL electrical characteristics" table, revised the footnote defining $f_{SCM}$ and $f_{VCO}$ .<br>In the "Main oscillator electrical characteristics" table:<br>– Changed the max specification for $g_{mXOSCHS}$ (was 11.8 mA/V, is 13.25 mA/V).<br>– Revised the conditions for $T_{XOSCHSSU}$ .<br>In the 'RC oscillator electrical characteristics" table, deleted the specification for $\Delta_{RCMTRIM}$ .<br>Revised the "ADC conversion characteristics" table.<br>In the "RESET pin characteristics" section, changed "nRSTIN" to "RESET".<br>Added the "Reset sequence" section.<br>Revised the footnotes in the "Nexus debug port timing" table.<br>Added the mechanical drawing for the 100-pin package.<br>In the "Order codes" table, added a footnote about frequency modulation to the "Speed (MH4)" column                                                                                                                                                                                                              |

| 23-Mar-2011 | 6                | <ul> <li>"Speed (MHz)" column heading.</li> <li>Editorial changes.</li> <li>In the "Document overview" section, added information about how content specific to silicon versions ("cut1" and "cut2") is presented.</li> <li>In the isometric miniature package drawings on the front page, removed the third dimension.</li> <li>Changed Symbol from P to D for "Conversion Time" in "ADC conversion characteristics" table.</li> <li>Added classification symbol "D" to seven entries in "Voltage regulator electrical specifications" table.</li> <li>Removed irrelevant FlexCAN specs.</li> <li>Updated Table "Voltage Thresholds" to reference values specified in Table "Voltage Regulator Electrical Specifications".</li> <li>RDY pin added for cut2.</li> <li>In the "System pins" table, added a footnote about the MDO0 pad speed.</li> <li>Updated Rsw1 values.</li> <li>Added AC Test Timing Conditions to the "AC timing characteristics" section.</li> <li>Added a statement on the first page describing cut1 versus cut2.</li> <li>Moved the first paragraph from the "Description" section to the beginning of the "Document overview" section.</li> <li>Changed pad speed from "M" to "SYM" for FlexRay pins in the "Pin Muxing" table and added this pad type to the footnote.</li> <li>Moved the newly added device current specification entries from the "DC electrical characteristics" table.</li> </ul> |

Table 45. Document revision history

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|