### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 96                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                |                                                                          |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

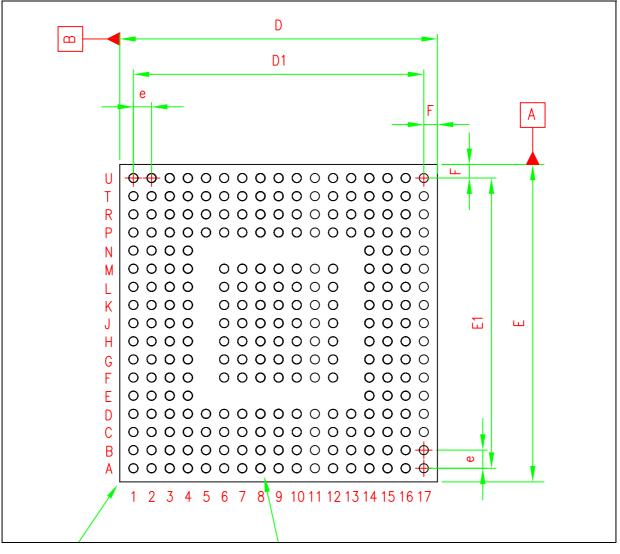

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l5cbosr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the devices.

This document provides electrical specifications, pin assignments, and package diagrams for the SPC56ELx/SPC564Lx series of microcontroller units (MCUs). For functional characteristics, see the SPC56ELx/SPC564Lx Microcontroller Reference Manual. For use of the SPC56ELx/SPC564Lx in a fail-safe system according to safety standard ISO26262, see the Safety Application Guide for SPCEL60.

# 1.2 Description

The SPC56ELx/SPC564Lx series microcontrollers are system-on-chip devices that are built on Power Architecture technology and contain enhancements that improve the architecture's fit in embedded applications, include additional instruction support for digital signal processing (DSP) and integrate technologies such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system.

The SPC56ELx/SPC564Lx family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address electrical hydraulic power steering (EHPS), electric power steering (EPS) and airbag applications. The advanced and cost-efficient host processor core of the SPC56ELx/SPC564Lx automotive controller family complies with the Power Architecture embedded category. It operates at speeds as high as 120 MHz and offers high-performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users' implementations.

|          | Table 1. SPC30ELX/SPC304LX device summary (continued)              |                           |           |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------|---------------------------|-----------|--|--|--|--|--|--|

|          | Feature                                                            | SPC56EL60                 | SPC56EL54 |  |  |  |  |  |  |

| Temperat | Temperature range (junction)                                       | $-40$ to 150 $^{\circ}$ C |           |  |  |  |  |  |  |

| ure      | Ambient temperature range using external ballast transistor (LQFP) | -40 to 125 °C             |           |  |  |  |  |  |  |

### Table 1. SPC56ELx/SPC564Lx device summary (continued)

1. The third eTimer (eTimer\_2) is available with external I/O access only in the BGA package, on the LQFP package eTimer\_2 is available internally only without any external I/O access.

2. The second FlexPWM module is available only in the BGA package.

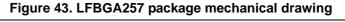

3. LBGA257 available only as development package.

# 1.4 Block diagram

Figure 1 shows a top-level block diagram of the SPC56ELx/SPC564Lx device.

The SRAM module provides the following features:

- System SRAM: 128 KB

- ECC on 32-bit word (syndrome of 7 bits)

- ECC covers SRAM bus address

- 1-bit error correction, 2-bit error detection

- Wait states:

- 1 wait state for frequencies =< 120 MHz</li>

- 0 wait states for frequencies =< 80 MHz</li>

### 1.5.7 Platform flash memory controller

The following list summarizes the key features of the flash memory controller:

- Single AHB port interface supports a 64-bit data bus. All AHB aligned and unaligned reads within the 32-bit container are supported. Only aligned word writes are supported.

- Array interfaces support a 128-bit read data bus and a 64-bit write data bus for each bank.

- Code flash (bank0) interface provides configurable read buffering and page prefetch support.

- Four page-read buffers (each 128 bits wide) and a prefetch controller support speculative reading and optimized flash access.

- Single-cycle read responses (0 AHB data-phase wait states) for hits in the buffers. The buffers implement a least-recently-used replacement algorithm to maximize performance.

- Programmable response for read-while-write sequences including support for stallwhile-write, optional stall notification interrupt, optional flash operation abort, and optional abort notification interrupt.

- Separate and independent configurable access timing (on a per bank basis) to support use across a wide range of platforms and frequencies.

- Support of address-based read access timing for emulation of other memory types.

- Support for reporting of single- and multi-bit error events.

- Typical operating configuration loaded into programming model by system reset.

The platform flash controller is replicated for each processor.

### 1.5.8 Platform Static RAM Controller (SRAMC)

The SRAMC module is the platform SRAM array controller, with integrated error detection and correction.

The main features of the SRAMC provide connectivity for the following interfaces:

- XBAR Slave Port (64-bit data path)

- ECSM (ECC Error Reporting, error injection and configuration)

- SRAM array

The following functions are implemented:

- ECC encoding (32-bit boundary for data and complete address bus)

- ECC decoding (32-bit boundary and entire address)

- Address translation from the AHB protocol on the XBAR to the SRAM array

The platform SRAM controller is replicated for each processor.

### 1.5.9 Memory subsystem access time

Every memory access, that the CPU performs, requires at least one system clock cycle for the data phase of the access. Slower memories or peripherals may require additional data phase wait states. Additional data phase wait states may also occur if the slave being accessed is not parked on the requesting master in the crossbar.

*Table 2* shows the number of additional data phase wait states required for a range of memory accesses.

| AHB transfer              | Data phase<br>wait states | Description                                                                                                     |

|---------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|

| e200z4d instruction fetch | 0                         | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d instruction fetch | 3                         | Flash memory prefetch buffer miss (based on 4-cycle random flash array access time)                             |

| e200z4d data read         | 0–1                       | SRAM read                                                                                                       |

| e200z4d data write        | 0                         | SRAM 32-bit write                                                                                               |

| e200z4d data write        | 0                         | SRAM 64-bit write (executed as 2 x 32-bit writes)                                                               |

| e200z4d data write        | 0–2                       | SRAM 8-,16-bit write<br>(Read-modify-Write for ECC)                                                             |

| e200z4d flash memory read | 0                         | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d flash memory read | 3                         | Flash memory prefetch buffer miss (at 120 MHz; includes 1 cycle of program flash memory controller arbitration) |

### Table 2. Platform memory access time summary

# 1.5.10 Error Correction Status Module (ECSM)

The ECSM on this device manages the ECC configuration and reporting for the platform memories (flash memory and SRAM). It does not implement the actual ECC calculation. A detected error (double error for flash memory or SRAM) is also reported to the FCCU. The following errors and indications are reported into the ECSM dedicated registers:

- ECC error status and configuration for flash memory and SRAM

- ECC error reporting for flash memory

- ECC error reporting for SRAM

- ECC error injection for SRAM

# 1.5.13 System clocks and clock generation

The following list summarizes the system clock and clock generation on this device:

- Lock status continuously monitored by lock detect circuitry

- Loss-of-clock (LOC) detection for reference and feedback clocks

- On-chip loop filter (for improved electromagnetic interference performance and fewer external components required)

- Programmable output clock divider of system clock (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and as many as three eTimer modules running on an auxiliary clock independent from system clock (with max frequency 120 MHz)

- On-chip crystal oscillator with automatic level control

- Dedicated internal 16 MHz internal RC oscillator for rapid start-up

- Supports automated frequency trimming by hardware during device startup and by user application

- Auxiliary clock domain for motor control periphery (FlexPWM, eTimer, CTU, ADC, and SWG)

The SWT module is replicated for each processor.

# **1.5.21** Fault Collection and Control Unit (FCCU)

The FCCU module has the following features:

- Redundant collection of hardware checker results

- Redundant collection of error information and latch of faults from critical modules on the device

- Collection of self-test results

- Configurable and graded fault control

- Internal reactions (no internal reaction, IRQ, Functional Reset, Destructive Reset, or Safe mode entered)

- External reaction (failure is reported to the external/surrounding system via configurable output pins)

# 1.5.22 System Integration Unit Lite (SIUL)

The SIUL controls MCU reset configuration, pad configuration, external interrupt, general purpose I/O (GPIO), internal peripheral multiplexing, and system reset operation. The reset configuration block contains the external pin boot configuration logic. The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

The SIU provides the following features:

- Centralized pad control on a per-pin basis

- Pin function selection

- Configurable weak pull-up/down

- Configurable slew rate control (slow/medium/fast)

- Hysteresis on GPIO pins

- Configurable automatic safe mode pad control

- Input filtering for external interrupts

# 1.5.23 Non-Maskable Interrupt (NMI)

The non-maskable interrupt with de-glitching filter supports high-priority core exceptions.

# 1.5.24 Boot Assist Module (BAM)

The BAM is a block of read-only memory with hard-coded content. The BAM program is executed only if serial booting mode is selected via boot configuration pins.

The BAM provides the following features:

- Enables booting via serial mode (FlexCAN or LINFlex-UART)

- Supports programmable 64-bit password protection for serial boot mode

- Supports serial bootloading of either Power Architecture code (default) or VLE code

- Automatic switch to serial boot mode if internal flash memory is blank or invalid

# 1.5.25 System Status and Configuration Module (SSCM)

The SSCM on this device features the following:

- System configuration and status

- Debug port status and debug port enable

- Multiple boot code starting locations out of reset through implementation of search for valid Reset Configuration Half Word

- Sets up the MMU to allow user boot code to execute as either Power Architecture code (default) or as VLE code out of flash memory

- Triggering of device self-tests during reset phase of device boot

### 1.5.26 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1Mbit/s

- 32 message buffers of 0 to 8 bytes data length

- Each message buffer configurable as receive or transmit buffer, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

|       |                            | GAZ57 pin function | on summary (continu | •              |  |

|-------|----------------------------|--------------------|---------------------|----------------|--|

| Pin # | Port/function              | Peripheral         | Output function     | Input function |  |

|       |                            | SIUL               | GPIO[128]           | GPIO[128]      |  |

| C9    | 1(0)                       | eTimer_2           | ETC[0]              | ETC[0]         |  |

| Ca    | I[0]                       | DSPI_0             | CS4                 | _              |  |

|       |                            | FlexPWM_1          | —                   | FAULT[0]       |  |

| C10   | JCOMP                      | _                  | —                   | JCOMP          |  |

| 011   | 11[44]                     | SIUL               | GPIO[123]           | GPIO[123]      |  |

| C11   | H[11] -                    | FlexPWM_1          | A[2]                | A[2]           |  |

|       |                            | SIUL               | GPIO[129]           | GPIO[129]      |  |

| 040   | 1541                       | eTimer_2           | ETC[1]              | ETC[1]         |  |

| C12   | I[1] -                     | DSPI_0             | CS5                 | _              |  |

|       |                            | FlexPWM_1          | _                   | FAULT[1]       |  |

| 040   | <b>F</b> [4,4]             | SIUL               | GPIO[94]            | GPIO[94]       |  |

| C13   | F[14]                      | LINFlexD_1         | TXD                 |                |  |

|       |                            | SIUL               | GPIO[17]            | GPI0[17]       |  |

|       |                            | eTimer_1           | ETC[3]              | ETC[3]         |  |

| 014   | D[4]                       | SSCM               | DEBUG[1]            | —              |  |

| C14   | B[1] -                     | FlexCAN_0          | _                   | RXD            |  |

|       |                            | FlexCAN_1          | —                   | RXD            |  |

|       |                            | SIUL               | —                   | EIRQ[16]       |  |

| C15   | V <sub>SS_HV_IO_RING</sub> |                    |                     |                |  |

|       |                            | SIUL               | GPIO[4]             | GPIO[4]        |  |

|       |                            | eTimer_1           | ETC[0]              | ETC[0]         |  |

| C16   | 0[4]                       | DSPI_2             | CS1                 | _              |  |

| 010   | A[4]                       | eTimer_0           | ETC[4]              | ETC[4]         |  |

|       |                            | MC_RGM             | —                   | FAB            |  |

|       |                            | SIUL               | —                   | EIRQ[4]        |  |

|       |                            | SIUL               | GPIO[92]            | GPI0[92]       |  |

| C17   | F[12]                      | eTimer_1           | ETC[3]              | ETC[3]         |  |

|       |                            | SIUL               | —                   | EIRQ[30]       |  |

| D4    | FIEL                       | SIUL               | GPIO[85]            | GPIO[85]       |  |

| D1    | F[5] -                     | NPC                | MDO[2]              | _              |  |

| 20    | E[4]                       | SIUL               | GPIO[84]            | GPIO[84]       |  |

| D2    | F[4] -                     | NPC                | MDO[3]              | _              |  |

Table 5. LFBGA257 pin function summary (continued)

|                              | GAZ57 pin function                                                                                                                                                         | Jii Sullillary (Colluind                                                                                                                                                                                                                                                                                                                                                  | ieu)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port/function                | Peripheral                                                                                                                                                                 | Output function                                                                                                                                                                                                                                                                                                                                                           | Input function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              | SIUL                                                                                                                                                                       | GPIO[99]                                                                                                                                                                                                                                                                                                                                                                  | GPIO[99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| G[3]                         | FlexPWM_0                                                                                                                                                                  | A[2]                                                                                                                                                                                                                                                                                                                                                                      | A[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | eTimer_0                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                         | ETC[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MDO0                         |                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | SIUL                                                                                                                                                                       | GPIO[86]                                                                                                                                                                                                                                                                                                                                                                  | GPIO[86]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| F[0]                         | NPC                                                                                                                                                                        | MDO[1]                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | SIUL                                                                                                                                                                       | GPIO[49]                                                                                                                                                                                                                                                                                                                                                                  | GPIO[49]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                              | eTimer_1                                                                                                                                                                   | ETC[2]                                                                                                                                                                                                                                                                                                                                                                    | ETC[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | CTU_0                                                                                                                                                                      | EXT_TGR                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | FlexRay                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                         | CA_RX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NMI                          |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Not connected                |                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | SIUL                                                                                                                                                                       | GPIO[46]                                                                                                                                                                                                                                                                                                                                                                  | GPIO[46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C[14]                        | eTimer_1                                                                                                                                                                   | ETC[2]                                                                                                                                                                                                                                                                                                                                                                    | ETC[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | CTU_0                                                                                                                                                                      | EXT_TGR                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | SIUL                                                                                                                                                                       | GPIO[98]                                                                                                                                                                                                                                                                                                                                                                  | GPIO[98]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| G[2]                         | FlexPWM_0                                                                                                                                                                  | X[2]                                                                                                                                                                                                                                                                                                                                                                      | X[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | DSPI_1                                                                                                                                                                     | CS1                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | SIUL                                                                                                                                                                       | GPIO[131]                                                                                                                                                                                                                                                                                                                                                                 | GPIO[131]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              | eTimer_2                                                                                                                                                                   | ETC[3]                                                                                                                                                                                                                                                                                                                                                                    | ETC[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I[3]                         | DSPI_0                                                                                                                                                                     | CS7                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | CTU_0                                                                                                                                                                      | EXT_TGR                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | FlexPWM_1                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                         | FAULT[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11743                        | SIUL                                                                                                                                                                       | GPIO[113]                                                                                                                                                                                                                                                                                                                                                                 | GPIO[113]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              | NPC                                                                                                                                                                        | MDO[6]                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0/401                        | SIUL                                                                                                                                                                       | GPIO[108]                                                                                                                                                                                                                                                                                                                                                                 | GPIO[108]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| G[12] -                      | NPC                                                                                                                                                                        | MDO[11]                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | SIUL                                                                                                                                                                       | GPIO[7]                                                                                                                                                                                                                                                                                                                                                                   | GPIO[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A[7]                         | DSPI_1                                                                                                                                                                     | SOUT                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | SIUL                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                         | EIRQ[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | SIUL                                                                                                                                                                       | GPIO[8]                                                                                                                                                                                                                                                                                                                                                                   | GPIO[8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A[8]                         | DSPI_1                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                         | SIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | SIUL                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                         | EIRQ[8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>DD_LV_CORE_RING</sub> |                                                                                                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              |                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |