### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 96                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l5cbosy |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1.5** Feature details

## 1.5.1 High-performance e200z4d core

The e200z4d Power Architecture<sup>®</sup> core provides the following features:

- 2 independent execution units, both supporting fixed-point and floating-point operations

- Dual issue 32-bit Power Architecture technology compliant

- 5-stage pipeline (IF, DEC, EX1, EX2, WB)

- In-order execution and instruction retirement

- Full support for Power Architecture instruction set and Variable Length Encoding (VLE)

- Mix of classic 32-bit and 16-bit instruction allowed

- Optimization of code size possible

- Thirty-two 64-bit general purpose registers (GPRs)

- Harvard bus (32-bit address, 64-bit data)

- I-Bus interface capable of one outstanding transaction plus one piped with no waiton-data return

- D-Bus interface capable of two transactions outstanding to fill AHB pipe

- I-cache and I-cache controller

- 4 KB, 256-bit cache line (programmable for 2- or 4-way)

- No data cache

- 16-entry MMU

- 8-entry branch table buffer

- Branch look-ahead instruction buffer to accelerate branching

- Dedicated branch address calculator

- 3 cycles worst case for missed branch

- Load/store unit

- Fully pipelined

- Single-cycle load latency

- Big- and little-endian modes supported

- Misaligned access support

- Single stall cycle on load to use

- Single-cycle throughput (2-cycle latency) integer 32 × 32 multiplication

- 4 14 cycles integer 32 × 32 division (average division on various benchmark of nine cycles)

- Single precision floating-point unit

- 1 cycle throughput (2-cycle latency) floating-point 32 × 32 multiplication

- Target 9 cycles (worst case acceptable is 12 cycles) throughput floating-point 32 × 32 division

- Special square root and min/max function implemented

- Signal processing support: APU-SPE 1.1

- Support for vectorized mode: as many as two floating-point instructions per clock

- Vectored interrupt support

- Reservation instruction to support read-modify-write constructs

# 1.5.25 System Status and Configuration Module (SSCM)

The SSCM on this device features the following:

- System configuration and status

- Debug port status and debug port enable

- Multiple boot code starting locations out of reset through implementation of search for valid Reset Configuration Half Word

- Sets up the MMU to allow user boot code to execute as either Power Architecture code (default) or as VLE code out of flash memory

- Triggering of device self-tests during reset phase of device boot

### 1.5.26 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1Mbit/s

- 32 message buffers of 0 to 8 bytes data length

- Each message buffer configurable as receive or transmit buffer, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid FMPLL jitter

### 1.5.27 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1 Rev. A

- 64 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as transmit or receive

- Message buffer size configurable

- Message filtering for all message buffers based on Frame ID, cycle count, and message ID

- Programmable acceptance filters for receive FIFO

- Message buffer header, status, and payload data stored in system memory (SRAM)

- Internal FlexRay memories have error detection and correction

|       |                        | •                  | on summary (continue | •              |

|-------|------------------------|--------------------|----------------------|----------------|

| Pin # | Port/function          | Peripheral         | Output function      | Input function |

| 68    | E[0]                   | SIUL               |                      | GPIO[64]       |

|       | <b>–</b> [م]           | ADC_1              | _                    | AN[5]          |

| 69    | BCTRL                  |                    | _                    |                |

| 70    | $V_{DD_LV_COR}$        |                    | _                    |                |

| 71    | $V_{SS_LV_COR}$        |                    | —                    |                |

| 72    | V <sub>DD_HV_PMU</sub> |                    | —                    |                |

|       |                        | SIUL               | GPIO[0]              | GPIO[0]        |

| 73    | 101                    | eTimer_0           | ETC[0]               | ETC[0]         |

| 73    | A[0]                   | DSPI_2             | SCK                  | SCK            |

|       |                        | SIUL               | —                    | EIRQ[0]        |

|       |                        | SIUL               | GPIO[1]              | GPIO[1]        |

| 74    | A [ 4 ]                | eTimer_0           | ETC[1]               | ETC[1]         |

| 74    | A[1]                   | DSPI_2             | SOUT                 |                |

|       |                        | SIUL               | _                    | EIRQ[1]        |

|       |                        | SIUL               | GPIO[107]            | GPIO[107]      |

| 75    | G[11]                  | G[11] FlexRay DBG3 |                      |                |

|       |                        | FlexPWM_0          | _                    | FAULT[3]       |

|       |                        | SIUL               | GPIO[58]             | GPIO[58]       |

| 76    | D[10]                  | FlexPWM_0          | A[0]                 | A[0]           |

|       |                        | eTimer_0           | _                    | ETC[0]         |

|       |                        | SIUL               | GPIO[106]            | GPIO[106]      |

| 77    | 01401                  | FlexRay            | DBG2                 |                |

| 77    | G[10]                  | DSPI_2             | CS3                  |                |

|       |                        | FlexPWM_0          | _                    | FAULT[2]       |

|       |                        | SIUL               | GPIO[59]             | GPIO[59]       |

| 78    | D[11]                  | FlexPWM_0          | B[0]                 | B[0]           |

|       |                        | eTimer_0           | _                    | ETC[1]         |

|       |                        | SIUL               | GPIO[105]            | GPIO[105]      |

|       |                        | FlexRay            | DBG1                 |                |

| 79    | G[9]                   | DSPI_1             | CS1                  |                |

|       |                        | FlexPWM_0          | —                    | FAULT[1]       |

|       |                        | SIUL               | —                    | EIRQ[29]       |

|       |                        | SIUL               | GPIO[43]             | GPIO[43]       |

| 80    | C[11]                  | eTimer_0           | ETC[4]               | ETC[4]         |

|       |                        | DSPI_2             | CS2                  |                |

|       | 1                      |                    |                      |                |

Table 4. LQFP144 pin function summary (continued)

|       |                        |            | n summary (continu | -              |

|-------|------------------------|------------|--------------------|----------------|

| Pin # | Port/function          | Peripheral | Output function    | Input function |

|       |                        | SIUL       | GPIO[104]          | GPIO[104]      |

|       |                        | FlexRay    | DBG0               | —              |

| 81    | G[8]                   | DSPI_0     | CS1                | —              |

|       |                        | FlexPWM_0  | —                  | FAULT[0]       |

|       |                        | SIUL       | —                  | EIRQ[21]       |

|       |                        | SIUL       | GPIO[44]           | GPIO[44]       |

| 82    | C[12]                  | eTimer_0   | ETC[5]             | ETC[5]         |

|       |                        | DSPI_2     | CS3                |                |

|       | 0171                   | SIUL       | GPIO[103]          | GPIO[103]      |

| 83    | G[7]                   | FlexPWM_0  | B[3]               | B[3]           |

|       |                        | SIUL       | GPIO[2]            | GPIO[2]        |

|       |                        | eTimer_0   | ETC[2]             | ETC[2]         |

|       | 4.03                   | FlexPWM_0  | A[3]               | A[3]           |

| 84    | A[2]                   | DSPI_2     | _                  | SIN            |

|       |                        | MC_RGM     | _                  | ABS[0]         |

|       |                        | SIUL       | —                  | EIRQ[2]        |

|       |                        | SIUL       | GPIO[101]          | GPIO[101]      |

| 85    | G[5]                   | FlexPWM_0  | X[3]               | X[3]           |

|       |                        | DSPI_2     | CS3                | —              |

|       |                        | SIUL       | GPIO[21]           | GPIO[21]       |

| 86    | B[5]                   | JTAGC      | _                  | TDI            |

| 87    | TMS                    |            | —                  |                |

| 88    | ТСК                    |            | _                  |                |

|       |                        | SIUL       | GPIO[20]           | GPIO[20]       |

| 89    | B[4]                   | JTAGC      | TDO                | _              |

| 90    | V <sub>SS_HV_IO</sub>  |            | _                  |                |

| 91    | V <sub>DD_HV_IO</sub>  |            | _                  |                |

|       |                        | SIUL       | GPIO[3]            | GPIO[3]        |

|       |                        | eTimer_0   | ETC[3]             | ETC[3]         |

|       |                        | DSPI_2     | CS0                | CS0            |

| 92    | A[3]                   | FlexPWM_0  | B[3]               | B[3]           |

|       |                        | MC_RGM     | —                  | ABS[2]         |

|       |                        | SIUL       | —                  | EIRQ[3]        |

| 93    | V <sub>DD_LV_COR</sub> |            | <u> </u>           | 1              |

| 94    | V <sub>SS_LV_COR</sub> |            | _                  |                |

|       |                        |            |                    |                |

| Iable 4. LQFP144 pin function summary (continued)           Bin #         Port/function         Input function |                          |            |                 |                |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|--------------------------|------------|-----------------|----------------|--|--|--|--|--|--|--|--|

| Pin #                                                                                                          | Port/function            | Peripheral | Output function | Input function |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |  |  |  |  |  |  |  |

| 125                                                                                                            | D[0]                     | FlexRay    | CA_TX           | _              |  |  |  |  |  |  |  |  |

| 120                                                                                                            |                          | eTimer_1   | ETC[1]          | ETC[1]         |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | FlexPWM_0  | B[1]            | B[1]           |  |  |  |  |  |  |  |  |

| 126                                                                                                            | V <sub>DD_HV_IO</sub>    |            | _               |                |  |  |  |  |  |  |  |  |

| 127                                                                                                            | V <sub>SS_HV_IO</sub>    |            |                 |                |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |  |  |  |  |  |  |  |

| 128                                                                                                            | 0121                     | FlexRay    | CB_TX           | _              |  |  |  |  |  |  |  |  |

| 120                                                                                                            | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | FlexPWM_0  | A[3]            | A[3]           |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[52]        | GPI0[52]       |  |  |  |  |  |  |  |  |

| 100                                                                                                            | DI4                      | FlexRay    | CB_TR_EN        |                |  |  |  |  |  |  |  |  |

| 129                                                                                                            | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | FlexPWM_0  |                 |                |  |  |  |  |  |  |  |  |

| 130                                                                                                            | V <sub>DD_HV_REG_2</sub> |            | _               |                |  |  |  |  |  |  |  |  |

| 131                                                                                                            | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |  |

| 132                                                                                                            | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[80]        | GPIO[80]       |  |  |  |  |  |  |  |  |

| 133                                                                                                            | FIOI                     | FlexPWM_0  | A[1]            | A[1]           |  |  |  |  |  |  |  |  |

| 155                                                                                                            | F[0]                     | eTimer_0   | —               | ETC[2]         |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | —               | EIRQ[28]       |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[9]         | GPIO[9]        |  |  |  |  |  |  |  |  |

| 134                                                                                                            | A101                     | DSPI_2     | CS1             | —              |  |  |  |  |  |  |  |  |

| 134                                                                                                            | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |  |

| 135                                                                                                            | V <sub>DD_LV_COR</sub>   |            |                 |                |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | GPIO[13]        | GPIO[13]       |  |  |  |  |  |  |  |  |

|                                                                                                                | [                        | FlexPWM_0  | B[2]            | B[2]           |  |  |  |  |  |  |  |  |

| 136                                                                                                            | A[13]                    | DSPI_2     | —               | SIN            |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | FlexPWM_0  | —               | FAULT[0]       |  |  |  |  |  |  |  |  |

|                                                                                                                |                          | SIUL       | —               | EIRQ[12]       |  |  |  |  |  |  |  |  |

| 137                                                                                                            | V <sub>SS_LV_COR</sub>   |            | —               |                |  |  |  |  |  |  |  |  |

Table 4. LQFP144 pin function summary (continued)

|         | Table 5. LFE                 | BGA257 pin functio | on summary (continu | ied)           |

|---------|------------------------------|--------------------|---------------------|----------------|

| Pin #   | Port/function                | Peripheral         | Output function     | Input function |

|         |                              | SIUL               | GPIO[116]           | GPIO[116]      |

| L16     | H[4]                         | FlexPWM_1          | X[0]                | X[0]           |

|         |                              | eTimer_2           | ETC[0]              | ETC[0]         |

| L17     | DIAL                         | SIUL               | GPIO[20]            | GPIO[20]       |

| LI/     | B[4]                         | JTAGC              | TDO                 | _              |

| M1      | V <sub>DD_HV_OSC</sub>       |                    | _                   |                |

| M2      | V <sub>DD_HV_IO_RING</sub>   |                    | _                   |                |

|         |                              | SIUL               | GPIO[56]            | GPIO[56]       |

|         |                              | DSPI_1             | CS2                 | _              |

| M3      | D[8]                         | eTimer_1           | ETC[4]              | ETC[4]         |

|         |                              | DSPI_0             | CS5                 | _              |

|         |                              | FlexPWM_0          | —                   | FAULT[3]       |

| M4      | Not connected                |                    | _                   |                |

| M6      | V <sub>DD_LV</sub>           |                    | _                   |                |

| M7      | V <sub>DD_LV</sub>           |                    | _                   |                |

| M8      | V <sub>DD_LV</sub>           |                    |                     |                |

| M9      | V <sub>DD_LV</sub>           |                    | _                   |                |

| M10     | V <sub>DD_LV</sub>           |                    | _                   |                |

| M11     | V <sub>DD_LV</sub>           |                    | _                   |                |

| M12     | V <sub>DD_LV</sub>           |                    | —                   |                |

|         |                              | SIUL               | GPIO[43]            | GPIO[43]       |

| M14     | C[11]                        | eTimer_0           | ETC[4]              | ETC[4]         |

|         |                              | DSPI_2             | CS2                 | —              |

| M15     | B[5] -                       | SIUL               | GPIO[21]            | GPIO[21]       |

| IVI I J | B[3]                         | JTAGC              | _                   | TDI            |

| M16     | TMS                          |                    | —                   |                |

|         |                              | SIUL               | GPIO[117]           | GPIO[117]      |

| M17     | H[5]                         | FlexPWM_1          | A[0]                | A[0]           |

|         |                              | DSPI_0             | CS4                 | —              |

| N1      | XTAL                         |                    |                     |                |

| N2      | V <sub>SS_HV_IO_RING</sub>   |                    |                     |                |

|         |                              | SIUL               | GPIO[53]            | GPIO[53]       |

| N3      | D[5]                         | DSPI_0             | CS3                 | _              |

|         |                              | FlexPWM_0          | —                   | FAULT[2]       |

| N4      | V <sub>SS_LV_PLL0_PLL1</sub> |                    |                     |                |

Table 5. LFBGA257 pin function summary (continued)

|      |        |            |                     | Table   | e 8. Pin muxin | g                     |                         |                             |            |            |            |          |  |

|------|--------|------------|---------------------|---------|----------------|-----------------------|-------------------------|-----------------------------|------------|------------|------------|----------|--|

| Port | PCR    | Peripheral | Alternate<br>output | Output  | Input          | Input mux             | Weak pull config during | Pad<br>speed <sup>(1)</sup> |            | Pin #      |            | ŧ        |  |

| name | FCK    | renpilerai | function            | mux sel | functions      | select                | reset                   | SRC<br>= 1                  | SRC<br>= 0 | 100<br>pkg | 144<br>pkg | 25<br>pk |  |

|      |        |            |                     |         | Port A         |                       |                         |                             |            |            |            |          |  |

|      |        | SIUL       | GPIO[0]             | ALT0    | GPIO[0]        | _                     |                         |                             |            |            |            |          |  |

| A[0] | PCR[0] | eTimer_0   | ETC[0]              | ALT1    | ETC[0]         | PSMI[35];<br>PADSEL=0 | — — M                   | М                           | S          | 51         | 73         | T1       |  |

| A[0] | FCR[0] | DSPI_2     | SCK                 | ALT2    | SCK            | PSMI[1];<br>PADSEL=0  |                         | IVI                         | 3          | 51         |            |          |  |

|      |        | SIUL       | —                   |         |                |                       |                         |                             |            |            |            |          |  |

|      |        | SIUL       | GPIO[1]             | ALT0    | GPIO[1]        | —                     |                         |                             |            |            |            |          |  |

| A[1] | PCR[1] | eTimer_0   | ETC[1]              | ALT1    | ETC[1]         | PSMI[36];<br>PADSEL=0 |                         | М                           | s          | 52         | 74         | R1       |  |

|      |        | DSPI_2     | SOUT                | ALT2    | _              | —                     |                         |                             |            |            |            |          |  |

|      |        | SIUL       | —                   | —       | EIRQ[1]        | —                     |                         |                             |            |            |            |          |  |

|      |        | SIUL       | GPIO[2]             | ALT0    | GPIO[2]        | —                     |                         |                             |            |            |            |          |  |

|      |        | eTimer_0   | ETC[2]              | ALT1    | ETC[2]         | PSMI[37];<br>PADSEL=0 | -                       |                             |            |            |            |          |  |

| A[2] | PCR[2] | FlexPWM_0  | A[3]                | ALT3    | A[3]           | PSMI[23];<br>PADSEL=0 | Pull down               | М                           | s          | 57         | 84         | N1       |  |

|      |        | DSPI_2     | _                   | _       | SIN            | PSMI[2];<br>PADSEL=0  | 2];                     |                             |            |            |            |          |  |

|      | l l    | MC_RGM     | —                   | —       | ABS[0]         | —                     |                         |                             |            |            |            |          |  |

|      |        | SIUL       |                     | _       | EIRQ[2]        | _                     |                         |                             |            |            |            |          |  |

SPC56ELX, SPC564LX

Package pinouts and signal descriptions

75/165

|             |        |            |                     | Table 8. Pi | n muxing (cor | ntinued)              |                         |            |                         |            |            |          |

|-------------|--------|------------|---------------------|-------------|---------------|-----------------------|-------------------------|------------|-------------------------|------------|------------|----------|

| Port        | PCR    | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull config during | Pa<br>spe  | ad<br>ed <sup>(1)</sup> |            | Pin #      |          |

| name        | PCR    | Peripheral | function            | mux sel     | functions     | select                | reset                   | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 25<br>pk |

|             |        | SIUL       | GPIO[3]             | ALT0        | GPIO[3]       | —                     |                         |            |                         |            |            |          |

|             |        | eTimer_0   | ETC[3]              | ALT1        | ETC[3]        | PSMI[38];<br>PADSEL=0 |                         |            |                         |            |            |          |

| A[3]        | PCR[3] | DSPI_2     | CS0                 | ALT2        | CS0           | PSMI[3];<br>PADSEL=0  | Pull down               | М          | S                       | 64         | 92         | K1       |

| , [0]       |        | FlexPWM_0  | B[3]                | ALT3        | B[3]          | PSMI[27];<br>PADSEL=0 |                         |            |                         |            |            |          |

|             |        | MC_RGM     | _                   | —           | ABS[2]        | —                     |                         |            |                         |            |            |          |

|             |        | SIUL       | _                   | —           | EIRQ[3]       | —                     | ]                       |            |                         |            |            |          |

|             |        | SIUL       | GPIO[4]             | ALT0        | GPIO[4]       | _                     |                         |            |                         |            |            |          |

|             |        | eTimer_1   | ETC[0]              | ALT1        | ETC[0]        | PSMI[9];<br>PADSEL=0  |                         |            |                         |            | 108        |          |

| A [ 4]      | DOD[4] | DSPI_2     | CS1                 | ALT2        |               | _                     |                         |            | S                       | 75         |            | C1       |

| A[4]        | PCR[4] | eTimer_0   | ETC[4]              | ALT3        | ETC[4]        | PSMI[7];<br>PADSEL=0  | - Pull down             | М          | 5                       | 75         |            |          |

|             |        | MC_RGM     | _                   | —           | FAB           | —                     |                         |            |                         |            |            |          |

|             |        | SIUL       | _                   | _           | EIRQ[4]       | —                     |                         |            |                         |            |            |          |

|             |        | SIUL       | GPIO[5]             | ALT0        | GPIO[5]       | _                     |                         |            |                         |            |            |          |

|             |        | DSPI_1     | CS0                 | ALT1        | CS0           | —                     |                         |            |                         |            |            | H4       |

| A[5] PCR[5] | PCR[5] | eTimer_1   | ETC[5]              | ALT2        | ETC[5]        | PSMI[14];<br>PADSEL=0 |                         | М          | S                       | 8          | 14         |          |

|             | DSPI_0 | CS7        | ALT3                | —           | —             | ]                     |                         |            |                         |            |            |          |

|             |        | SIUL       |                     | _           | EIRQ[5]       | _                     | ]                       |            |                         |            |            |          |

# Package pinouts and signal descriptions

SPC56ELx, SPC564Lx

5

|                   |       |         |            |                     | Table 8. Pi | n muxing (cor | tinued)               |                            |            |                         |            |            |            |

|-------------------|-------|---------|------------|---------------------|-------------|---------------|-----------------------|----------------------------|------------|-------------------------|------------|------------|------------|

| 5                 | Port  | PCR     | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull<br>config during | Pa<br>spee | ad<br>ed <sup>(1)</sup> | Pin #      |            |            |

|                   | name  | FOR     | renpheral  | function            | mux sel     | functions     | select                | reset                      | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|                   |       |         | SIUL       | GPIO[14]            | ALT0        | GPIO[14]      | —                     |                            |            |                         |            |            |            |

|                   |       |         | FlexCAN_1  | TXD                 | ALT1        | —             | —                     |                            |            |                         |            |            |            |

|                   | A[14] | PCR[14] | eTimer_1   | ETC[4]              | ALT2        | ETC[4]        | PSMI[13];<br>PADSEL=0 |                            | М          | S                       | 99         | 143        | B4         |

|                   |       |         | SIUL       | —                   | —           | EIRQ[13]      | —                     |                            |            |                         |            |            |            |

|                   |       | PCR[15] | SIUL       | GPIO[15]            | ALT0        | GPIO[15]      | —                     |                            |            |                         |            |            |            |

| D                 |       |         | eTimer_1   | ETC[5]              | ALT2        | ETC[5]        | PSMI[14];<br>PADSEL=1 |                            |            |                         |            |            |            |

| DocID15457 Rev 12 | A[15] |         | FlexCAN_1  | _                   | _           | RXD           | PSMI[34];<br>PADSEL=0 |                            | М          | S                       | 100        | 144        | D3         |

| 157 Rev           |       |         | FlexCAN_0  | _                   | _           | RXD           | PSMI[33];<br>PADSEL=0 |                            |            |                         |            |            |            |

| v 12              |       |         | SIUL       | —                   | _           | EIRQ[14]      | —                     |                            |            |                         |            |            |            |

|                   |       |         |            |                     |             | Port B        |                       |                            |            |                         |            |            |            |

|                   |       |         | SIUL       | GPIO[16]            | ALT0        | GPIO[16]      | _                     |                            |            |                         |            |            |            |

|                   |       |         | FlexCAN_0  | TXD                 | ALT1        | _             | _                     |                            |            |                         |            |            |            |

|                   | B[0]  | PCR[16] | eTimer_1   | ETC[2]              | ALT2        | ETC[2]        | PSMI[11];<br>PADSEL=0 |                            | М          | S                       | 76         | 109        | B15        |

|                   |       |         | SSCM       | DEBUG[0]            | ALT3        | _             | _                     |                            |            |                         |            |            |            |

|                   |       |         | SIUL       | _                   | —           | EIRQ[15]      | —                     |                            |            |                         |            |            |            |

Package pinouts and signal descriptions

|               |         |            |                     | Table 8. Pi | n muxing (cor | ntinued)              |                         |            |                         |            |            |            |  |  |  |

|---------------|---------|------------|---------------------|-------------|---------------|-----------------------|-------------------------|------------|-------------------------|------------|------------|------------|--|--|--|

| Port          | PCR     | Peripheral | Alternate<br>output | Output      | Input         | Input mux             | Weak pull config during | Pa<br>spee | ad<br>ed <sup>(1)</sup> |            | Pin #      |            |  |  |  |

| name          | POR     | renpheral  | function            | mux sel     | functions     | select                | reset                   | SRC<br>= 1 | SRC<br>= 0              | 100<br>pkg | 144<br>pkg | 257<br>pkg |  |  |  |

|               |         | SIUL       | GPIO[36]            | ALT0        | GPIO[36]      | —                     |                         |            |                         |            |            |            |  |  |  |

|               |         | DSPI_0     | CS0                 | ALT1        | CS0           | —                     |                         |            |                         |            |            |            |  |  |  |

| C[4]          | PCR[36] | FlexPWM_0  | X[1]                | ALT2        | X[1]          | PSMI[28];<br>PADSEL=0 | _                       | М          | S                       | 5          | 11         | H3         |  |  |  |

|               |         | SSCM       | DEBUG[4]            | ALT3        | —             | —                     |                         |            |                         |            |            |            |  |  |  |

|               |         | SIUL       | —                   | —           | EIRQ[22]      | _                     |                         |            |                         |            |            |            |  |  |  |

|               |         | SIUL       | GPIO[37]            | ALT0        | GPIO[37]      | _                     |                         |            |                         |            |            |            |  |  |  |

|               |         | DSPI_0     | SCK                 | ALT1        | SCK           | _                     |                         |            |                         |            |            |            |  |  |  |

| C[5]          | PCR[37] | SSCM       | DEBUG[5]            | ALT3        | _             | _                     | 1 _                     | М          | S                       | 7          | 13         | G          |  |  |  |

| 0[0]          |         | FlexPWM_0  | _                   | _           | FAULT[3]      | PSMI[19];<br>PADSEL=0 |                         |            | 0                       |            |            | 00         |  |  |  |

|               |         | SIUL       | —                   | _           | EIRQ[23]      | _                     |                         |            |                         |            |            |            |  |  |  |

|               |         | SIUL       | GPIO[38]            | ALT0        | GPIO[38]      | —                     |                         |            |                         |            |            |            |  |  |  |

|               |         | DSPI_0     | SOUT                | ALT1        | _             | _                     |                         |            |                         |            |            |            |  |  |  |

| C[6]          | PCR[38] | FlexPWM_0  | B[1]                | ALT2        | B[1]          | PSMI[25];<br>PADSEL=0 | _                       | М          | S                       | 98         | 142        | D4         |  |  |  |

|               |         | SSCM       | DEBUG[6]            | ALT3        |               | _                     |                         |            |                         |            |            |            |  |  |  |

|               |         | SIUL       | _                   | _           | EIRQ[24]      | _                     |                         |            |                         |            |            |            |  |  |  |

|               |         | SIUL       | GPIO[39]            | ALT0        | GPIO[39]      | _                     |                         |            |                         |            |            |            |  |  |  |

| C[7]          | PCR[39] | FlexPWM_0  | A[1]                | ALT2        | A[1]          | PSMI[21];<br>PADSEL=0 |                         | MS         | S                       | 9          | 15         | K4         |  |  |  |

| C[7]   PCR[39 |         | SSCM       | DEBUG[7]            | ALT3        | —             | —                     | ]                       |            |                         |            |            |            |  |  |  |

|               |         | DSPI_0     | _                   | _           | SIN           |                       | 1                       |            |                         |            |            |            |  |  |  |

SPC56ELX, SPC564LX

Package pinouts and signal descriptions

33/165

| Symbol                                           |    | Parameter                                                                        | Conditions                     | Min <sup>(1)</sup> | Мах  | Unit |

|--------------------------------------------------|----|----------------------------------------------------------------------------------|--------------------------------|--------------------|------|------|

| V <sub>DD_HV_ADV</sub>                           | SR | 3.3 V ADC supply voltage                                                         | —                              | 3.0                | 3.63 | V    |

| V <sub>SS_HV_AD0</sub><br>V <sub>SS_HV_AD1</sub> | SR | ADC_0 ground and low reference voltage<br>ADC_1 ground and low reference voltage | _                              | 0                  | 0    | V    |

| V <sub>SS_HV_ADV</sub>                           | SR | 3.3 V ADC supply ground                                                          | —                              | 0                  | 0    | V    |

| V <sub>DD_LV, REGCOR</sub>                       | SR | Internal supply voltage                                                          | _                              | _                  | —    | ~    |

| V <sub>SS_LV_REGCOR</sub>                        | SR | Internal reference voltage                                                       | reference voltage —            |                    | 0    | V    |

| V <sub>DD_LV_CORx</sub> <sup>(2)</sup>           | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>           | SR | Internal reference voltage                                                       | —                              | 0                  | 0    | V    |

| V <sub>DD_LV_PLL</sub> <sup>(2)</sup>            | SR | Internal supply voltage                                                          | —                              |                    | —    | V    |

| V <sub>SS_LV_PLL</sub> <sup>(3)</sup>            | SR | Internal reference voltage                                                       | — 0 0                          |                    | 0    | V    |

| T <sub>A</sub>                                   | SR | Ambient temperature under bias                                                   | $f_{CPU} \leq 120 \text{ MHz}$ | -40                | 125  | °C   |

| TJ                                               | SR | Junction temperature under bias                                                  | —                              | -40                | 150  | °C   |

Table 10. Recommended operating conditions (3.3 V) (continued)

1. Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2.  $V_{DD\_HV\_ADR0}$  and  $V_{DD\_HV\_ADR1}$  cannot be operated at different voltages, and need to be supplied by the same voltage source.

3. VDD\_HV\_ADRx must always be applied and should be stable before LBIST starts. If this supply is not above its absolute minimum level, LBIST operations can fail.

4. Can be connected to emitter of external NPN. Low voltage supplies are not under user control. They are produced by an onchip voltage regulator.

For the device to function properly, the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter, if one is used.

# 3.4 Decoupling capacitors

The internal voltage regulator requires an external NPN ballast and some additional decoupling capacitors. These capacitors shall be placed on the board as close as possible to the associated pin.

| Symbo            | 1  | Parameter                                    | Conditions <sup>(1)</sup>                                                                                                        |      | Unit               |      |      |

|------------------|----|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

| Symbo            | 1  | Farameter                                    | Conditions                                                                                                                       | Min  | Тур                | Max  | Unit |

| C <sub>COL</sub> | SR | External decoupling / stability capacitor    | Accuracy -50%/+35%.<br>Max ESR = 100 mΩ.                                                                                         |      | 20                 |      | μF   |

| C <sub>LV1</sub> | SR | External decoupling /<br>stability capacitor | Sum of $C_{LV1}$ placed close to $V_{DD}/V_{SS_LV_CORy}$ pairs <sup>(2)</sup> .                                                  | 12µF |                    | 40µF | μF   |

| C <sub>LV2</sub> | SR | External decoupling / stability capacitor    | Sum of C <sub>LV2</sub> placed close to<br>V <sub>DD</sub> /V <sub>SS_LV_CORy</sub> pairs shall be<br>between 300 nF and 900 nF. |      | 100 <sup>(2)</sup> |      | nF   |

| Table | 11. | Decoupling | capacitors |

|-------|-----|------------|------------|

|-------|-----|------------|------------|

| Symbol                                                            |   | Parameter                                         | Conditions <sup>(1)</sup>                                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|---|---------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                                                                   |   |                                                   | 1.2V supplies<br>Tj=105°C<br>V <sub>DD_LV_COR</sub> = 1.2V<br>LSM mode                    | _   | _   | 275 | mA   |

| I <sub>DD_LV_TYP</sub> +<br>I <sub>DD_LV_PLL</sub> <sup>(2)</sup> | Т | Operating current                                 | 1.2V supplies<br>Tj=125°C<br>V <sub>DD_LV_COR</sub> = 1.2V<br>LSM mode                    | _   |     | 299 | mA   |

| I <sub>DD_LV_TYP</sub> +<br>I <sub>DD_LV_PLL</sub> <sup>(2)</sup> |   | Operating current                                 | 1.2V supplies<br>Tj=105°C<br>V <sub>DD_LV_COR</sub> = 1.2V<br>DPM Mode                    |     | _   | 189 | mA   |

|                                                                   | т |                                                   | 1.2V supplies<br>Tj=125°C<br>V <sub>DD_LV_COR</sub> = 1.2V<br>DPM Mode                    | _   | _   | 214 | mA   |

|                                                                   |   |                                                   | 1.2V supplies<br>Tj=150°C<br>V <sub>DD_LV_COR</sub> = 1.2V<br>DPM Mode                    | _   | _   | 235 | mA   |

|                                                                   | т | Operating current<br>in V <sub>DD</sub> STOP mode | T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                 | _   | _   | 20  |      |

|                                                                   | т |                                                   | T <sub>J</sub> = 55 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                 | _   | _   | 57  | mA   |

|                                                                   | Ρ |                                                   | T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                |     | _   | 105 |      |

|                                                                   | т |                                                   | T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                 | _   | _   | 25  |      |

| I <sub>DD_LV_HALT</sub>                                           | т | Operating current<br>in V <sub>DD</sub> HALT mode | T <sub>J</sub> = 55 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                 | _   | _   | 64  | mA   |

|                                                                   | Ρ |                                                   | T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                | —   | _   | 115 |      |

| IDD_HV_ADC <sup>(3),</sup>                                        | т | Operating current                                 | $T_J = 150 \degree C$<br>120 MHz<br>ADC operating at<br>60 MHz<br>$V_{DD_HV_ADC} = 3.6 V$ | _   | _   | 10  | mA   |

Table 22. Current consumption characteristics (continued)

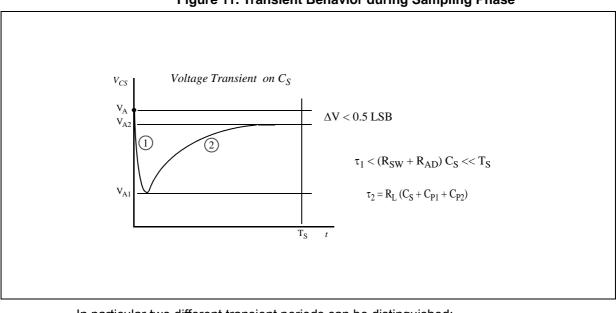

### Figure 11. Transient Behavior during Sampling Phase

In particular two different transient periods can be distinguished:

• A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

### **Equation 5**

$$\tau_1 = (\mathbf{R}_{SW} + \mathbf{R}_{AD}) \bullet \frac{\mathbf{C}_P \bullet \mathbf{C}_S}{\mathbf{C}_P + \mathbf{C}_S}$$

*Equation 5* can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \bullet C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

### **Equation 7**

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

• A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance  $R_L$ : again considering the worst case in which  $C_{P2}$

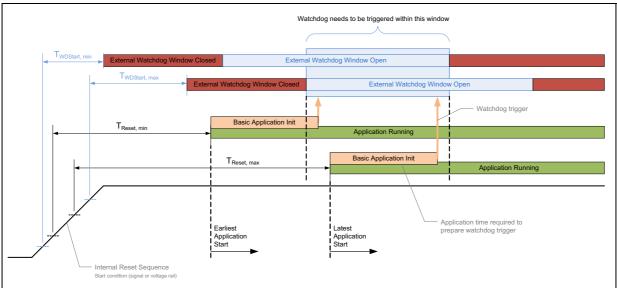

# 3.20.5 External watchdog window

If the application design requires the use of an external watchdog the data provided in Section 3.20 can be used to determine the correct positioning of the trigger window for the external watchdog. *Figure 21* shows the relationships between the minimum and the maximum duration of a given reset sequence and the position of an external watchdog trigger window.

# 3.21 AC timing characteristics

AC Test Timing Conditions: Unless otherwise noted, all test conditions are as follows:

- TJ = -40 to 150 °C

- Supply voltages as specified in Table 10

- Input conditions: All Inputs: tr, tf = 1 ns

- Output Loading: All Outputs: 50 pF

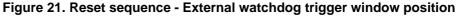

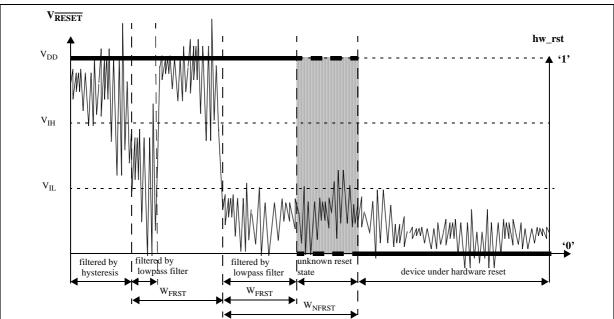

# 3.21.1 **RESET** pin characteristics

The SPC56ELx/SPC564Lx implements a dedicated bidirectional RESET pin.

Figure 22. Start-up reset requirements

Figure 23. Noise filtering on reset signal

| Table 36. | RESET | electrical | characteristics |

|-----------|-------|------------|-----------------|

| No. | Symb               | ol | Parameter                                        | Conditions <sup>(1)</sup> | Min | Тур | Max | Unit |

|-----|--------------------|----|--------------------------------------------------|---------------------------|-----|-----|-----|------|

|     |                    |    | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 25pF     | _   | —   | 12  |      |

| 1   | T <sub>tr</sub>    | D  |                                                  | C <sub>L</sub> = 50pF     | _   | —   | 25  | ns   |

|     |                    |    |                                                  | C <sub>L</sub> = 100pF    | _   | —   | 40  |      |

| 2   | W <sub>FRST</sub>  | Ρ  | nRESET input filtered pulse                      | —                         | -   | —   | 40  | ns   |

| 3   | W <sub>NFRST</sub> | Р  | nRESET input not filtered pulse                  | _                         | 500 | _   | _   | ns   |

1.  $V_{DD}$  = 3.3 V  $\pm$  10%,  $T_{J}$  = –40 to +150 °C, unless otherwise specified.

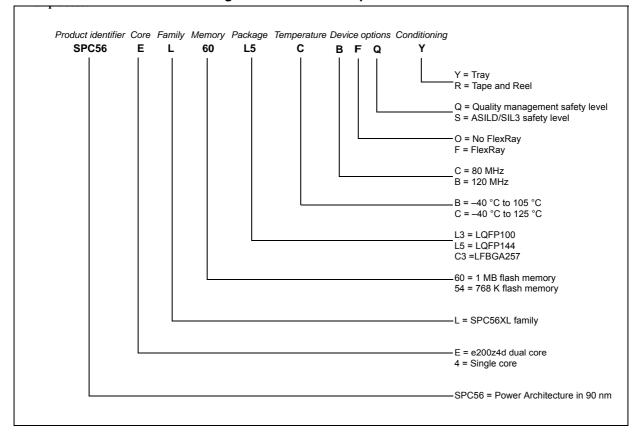

# 5 Ordering information

### Figure 44. Commercial product code structure

| Date        | Table 45. Document revision history       Date     Revision       Changes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date        | Revision                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 23-Nov-2010 | 5<br>(continued)                                                          | In the "BCP68 board schematic example" figure, removed the resistor at the base of the BCP68 transistor.<br>In the "DC electrical characteristics" table:<br>– Changed the guarantee parameter for I <sub>INJ</sub> (was P, is T).<br>– Added a specification for input leakage current for shared ADC input-only ports.<br>Revised the "Flash memory module life" table.<br>In the "FMPLL electrical characteristics" table, revised the footnote defining $f_{SCM}$ and $f_{VCO}$ .<br>In the "Main oscillator electrical characteristics" table:<br>– Changed the max specification for $g_{mXOSCHS}$ (was 11.8 mA/V, is 13.25 mA/V).<br>– Revised the conditions for $T_{XOSCHSSU}$ .<br>In the 'RC oscillator electrical characteristics" table, deleted the specification for $\Delta_{RCMTRIM}$ .<br>Revised the "ADC conversion characteristics" table.<br>In the "RESET pin characteristics" section, changed "nRSTIN" to "RESET".<br>Added the "Reset sequence" section.<br>Revised the footnotes in the "Nexus debug port timing" table.<br>Added the mechanical drawing for the 100-pin package.<br>In the "Order codes" table, added a footnote about frequency modulation to the "Speed (MH4)" column                                                                                                                                                                                                              |  |  |

| 23-Mar-2011 | 6                                                                         | <ul> <li>"Speed (MHz)" column heading.</li> <li>Editorial changes.</li> <li>In the "Document overview" section, added information about how content specific to silicon versions ("cut1" and "cut2") is presented.</li> <li>In the isometric miniature package drawings on the front page, removed the third dimension.</li> <li>Changed Symbol from P to D for "Conversion Time" in "ADC conversion characteristics" table.</li> <li>Added classification symbol "D" to seven entries in "Voltage regulator electrical specifications" table.</li> <li>Removed irrelevant FlexCAN specs.</li> <li>Updated Table "Voltage Thresholds" to reference values specified in Table "Voltage Regulator Electrical Specifications".</li> <li>RDY pin added for cut2.</li> <li>In the "System pins" table, added a footnote about the MDO0 pad speed.</li> <li>Updated Rsw1 values.</li> <li>Added AC Test Timing Conditions to the "AC timing characteristics" section.</li> <li>Added a statement on the first page describing cut1 versus cut2.</li> <li>Moved the first paragraph from the "Description" section to the beginning of the "Document overview" section.</li> <li>Changed pad speed from "M" to "SYM" for FlexRay pins in the "Pin Muxing" table and added this pad type to the footnote.</li> <li>Moved the newly added device current specification entries from the "DC electrical characteristics" table.</li> </ul> |  |  |

Table 45. Document revision history

| Date        | Revision     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01-Aug-2012 | 8<br>(cont.) | <ul> <li>In <i>Table 20: Voltage regulator electrical specifications</i>, changed the "Digital supply high voltage detector upper threshold low limit (After a destructive reset initialization phase completion)" from 1.43V to 1.38V.</li> <li>Added <i>Table 20: Voltage regulator electrical specifications</i>.</li> <li>Updated the IDD values in <i>Table 22: Current consumption characteristics</i>. Changed conditions text from "1.2 supplies during LBIST (full LBIST configuration)" to "1.2 V supplies" for all the IDD parameters except IDD_LV_BIST+IDD_LV_PLL. Added footnote in "Conditions" for the DPM mode.</li> <li>Removed Cut references from the whole document.</li> <li>In <i>Table 27: ADC conversion characteristics</i>, changed the sampling frequency value from '1 MHz' to '983.6 KHz'.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31-Jul-2013 | 9            | <ul> <li>Updated Table 20: Voltage regulator electrical specifications (Voltage regulator electrical specifications)</li> <li>Added Digital supply low voltage detector lower threshold and Digital supply low voltage detector upper threshold</li> <li>Updated Main High Voltage Power-Low Voltage Detection value to 2.93 V</li> <li>Replaced IEC with ISO26262 in <i>Section 1.1: Document overview</i>,</li> <li>Table 1 (SPC56XL60/54 device summary)-removed KGD</li> <li>Table 26 (16 MHz RC oscillator electrical characteristics) modified fRC values</li> <li>Updated Table 28 (Flash memory program and erase electrical specifications)</li> <li>Updated Table 27 (ADC conversion characteristics)-tconv to teval and associated footnote</li> <li>Updated Table 21 (DC electrical characteristics)</li> <li>added VIH footnote</li> <li>Updated Table 20 (Voltage regulator electrical specifications)-combined ESR of external capacitor values</li> <li>Updated Table 20 (Voltage regulator electrical specifications)-combined ESR of external capacitor values</li> <li>Updated Table 20 (Voltage regulator electrical specifications)-combined ESR of external capacitor values</li> <li>Updated Injection current information in Table 21 (DC electrical characteristics)-linu), Table 9 (Absolute maximum ratings)-footnote 4</li> <li>Updated Table 22 (Current consumption characteristics) for the following:</li> <li>specified oscillator bypass mode and crystal oscillator mode</li> <li>Updated STOP and HALT mode values</li> <li>Added IDD_HV_PMU</li> <li>footnote 2, footnote 3</li> <li>Added footnote to Section 5: Ordering information</li> <li>Edit changes to Section 3: 6: Electromagnetic Interference (EMI) characteristics</li> <li>Updated Equation 11.</li> </ul> |