#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 96                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el60l5ccosr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    | Feature                                           | SPC56EL60                                                                    | SPC56EL54            |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------|----------------------|

|                    | Interrupt Controller (INTC)                       | 16 interrupt levels,                                                         | replicated module    |

|                    | Periodic Interrupt Timer (PIT)                    | 1 × 4 cł                                                                     | nannels              |

|                    | System Timer Module (STM)                         | 1 × 4 channels, r                                                            | eplicated module     |

|                    | Software Watchdog Timer (SWT)                     | Yes, replica                                                                 | ted module           |

|                    | eDMA                                              | 16 channels, re                                                              | plicated module      |

|                    | FlexRay                                           | 1 × 64 message bu                                                            | uffers, dual channel |

|                    | FlexCAN                                           | 2 × 32 mess                                                                  | sage buffers         |

| Modules            | LINFlexD (UART and LIN with DMA support)          | 2                                                                            | 2                    |

| moduleo            | Clock out                                         | Ye                                                                           | es                   |

|                    | Fault Collection and Control Unit (FCCU)          | Ye                                                                           | es                   |

|                    | Cross Triggering Unit (CTU)                       | Ye                                                                           | es                   |

|                    | eTimer                                            | 3 × 6 channels <sup>(1)</sup>                                                |                      |

|                    | FlexPWM                                           | 2 Module 4 × (2 + 1) channels <sup>(2)</sup>                                 |                      |

|                    | Analog-to-Digital Converter (ADC)                 | 2 × 12-bit ADC, 16 channels per ADC<br>(3 internal, 4 shared and 9 external) |                      |

|                    | Sine Wave Generator (SWG)                         | 32 p                                                                         | point                |

|                    | Deserial Serial Peripheral Interface              | 3 × DSPI                                                                     |                      |

|                    | (DSPI)                                            | as many as 8                                                                 | 3 chip selects       |

| Modules<br>(cont.) | Cyclic Redundancy Checker (CRC)<br>unit           | Ye                                                                           | es                   |

| (0011.)            | Junction temperature sensor<br>(TSENS)            | Yes, replica                                                                 | ted module           |

|                    | Digital I/Os                                      | ≥ ′                                                                          | 16                   |

| Supply             | Device power supply                               | 3.3 V with integrated byp<br>External ballast transisto                      |                      |

| -                  | Analog reference voltage                          | 3.0 V – 3.6 V ar                                                             | nd 4.5 V – 5.5 V     |

|                    | Frequency-modulated phase-<br>locked loop (FMPLL) | 2                                                                            | 2                    |

| Clocking           | Internal RC oscillator                            | 16 M                                                                         | MHz                  |

|                    | External crystal oscillator                       | 4 – 40                                                                       | ) MHz                |

| Debug              | Nexus                                             | Leve                                                                         | el 3+                |

| Packages           | LQFP                                              |                                                                              | pins<br>pins         |

|                    | LBGA <sup>(3)</sup>                               | LBG/                                                                         | A257                 |

Table 1. SPC56ELx/SPC564Lx device summary (continued)

|          | Table 1. SPC30ELX/SPC304LX device summary (continued)              |                           |           |  |

|----------|--------------------------------------------------------------------|---------------------------|-----------|--|

|          | Feature                                                            | SPC56EL60                 | SPC56EL54 |  |

| Temperat | Temperature range (junction)                                       | $-40$ to 150 $^{\circ}$ C |           |  |

| ure      | Ambient temperature range using external ballast transistor (LQFP) | -40 to                    | 125 °C    |  |

# Table 1. SPC56ELx/SPC564Lx device summary (continued)

1. The third eTimer (eTimer\_2) is available with external I/O access only in the BGA package, on the LQFP package eTimer\_2 is available internally only without any external I/O access.

2. The second FlexPWM module is available only in the BGA package.

3. LBGA257 available only as development package.

# 1.4 Block diagram

Figure 1 shows a top-level block diagram of the SPC56ELx/SPC564Lx device.

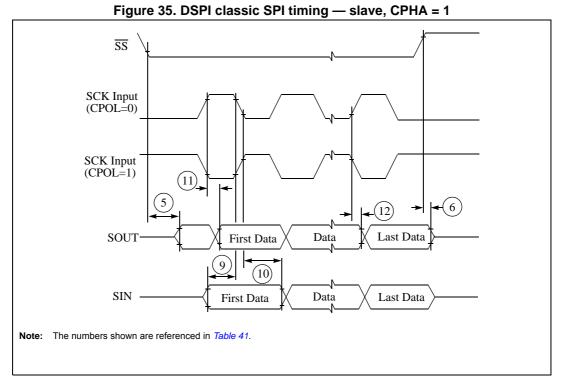

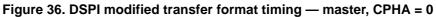

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- As many as 8 chip select lines available, depending on package and pin multiplexing

- 4 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering as many as 5 transfers on the transmit and receive side

- Queueing operation possible through use of the eDMA

- General purpose I/O functionality on pins when not used for SPI

# 1.5.30 FlexPWM

The pulse width modulator module (FlexPWM) contains four PWM channels, each of which is configured to control a single half-bridge power stage. Two modules are included on LFBGA257 devices; on the LQFP144 package, only one module is present. Additionally, four fault input channels are provided per FlexPWM module.

This PWM is capable of controlling most motor types, including:

- AC induction motors (ACIM)

- Permanent Magnet AC motors (PMAC)

- Brushless (BLDC) and brush DC motors (BDC)

- Switched (SRM) and variable reluctance motors (VRM)

- Stepper motors

A FlexPWM module implements the following features:

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- Maximum operating frequency as high as 120 MHz

- Clock source not modulated and independent from system clock (generated via secondary FMPLL)

- Fine granularity control for enhanced resolution of the PWM period

- PWM outputs can operate as complementary pairs or independent channels

- Ability to accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

| Pin # | Port/function          | Peripheral | Output function | Input function |

|-------|------------------------|------------|-----------------|----------------|

| 48    | V <sub>DD_LV_COR</sub> |            | —               |                |

| 49    | V <sub>SS_LV_COR</sub> |            | —               |                |

| 50    | V <sub>DD_HV_PMU</sub> |            | _               |                |

|       |                        | SIUL       | GPIO[0]         | GPIO[0]        |

|       |                        | eTimer_0   | ETC[0]          | ETC[0]         |

| 51    | A[0]                   | DSPI_2     | SCK             | SCK            |

|       |                        | SIUL       | _               | EIRQ[0]        |

|       |                        | SIUL       | GPIO[1]         | GPIO[1]        |

|       |                        | eTimer_0   | ETC[1]          | ETC[1]         |

| 52    | A[1]                   | DSPI_2     | SOUT            | _              |

|       |                        | SIUL       | _               | EIRQ[1]        |

|       |                        | SIUL       | GPIO[58]        | GPIO[58]       |

| 53    | D[10]                  | FlexPWM_0  | A[0]            | A[0]           |

|       |                        | eTimer_0   | _               | ETC[0]         |

|       |                        | SIUL       | GPIO[59]        | GPIO[59]       |

| 54    | D[11]                  | FlexPWM_0  | B[0]            | B[0]           |

|       | -                      | eTimer_0   | _               | ETC[1]         |

|       |                        | SIUL       | GPIO[43]        | GPIO[43]       |

| 55    | C[11]                  | eTimer_0   | ETC[4]          | ETC[4]         |

|       | -                      | DSPI_2     | CS2             |                |

|       |                        | SIUL       | GPIO[44]        | GPIO[44]       |

| 56    | C[12]                  | eTimer_0   | ETC[5]          | ETC[5]         |

|       |                        | DSPI_2     | CS3             | _              |

|       |                        | SIUL       | GPIO[2]         | GPIO[2]        |

|       | -                      | eTimer_0   | ETC[2]          | ETC[2]         |

|       | 4 (0)                  | FlexPWM_0  | A[3]            | A[3]           |

| 57    | A[2]                   | DSPI_2     | _               | SIN            |

|       | -                      | MC_RGM     | _               | ABS[0]         |

|       |                        | SIUL       | _               | EIRQ[2]        |

| 50    | DIC                    | SIUL       | GPIO[21]        | GPIO[21]       |

| 58    | B[5]                   | JTAGC      | _               | TDI            |

| 59    | TMS                    |            |                 |                |

| 60    | тск                    |            |                 |                |

| 64    | D[4]                   | SIUL       | GPIO[20]        | GPIO[20]       |

| 61    | B[4] -                 | JTAGC      | TDO             | —              |

Table 3. LQFP100 pin function summary (continued)

| Table 3. LQFP100 pin function summary (continued) |                          |            |                 |                |  |  |

|---------------------------------------------------|--------------------------|------------|-----------------|----------------|--|--|

| Pin #                                             | Port/function            | Peripheral | Output function | Input function |  |  |

|                                                   |                          | SIUL       | GPIO[12]        | GPIO[12]       |  |  |

|                                                   |                          | DSPI_2     | SOUT            | —              |  |  |

| 83                                                | A[12]                    | FlexPWM_0  | A[2]            | A[2]           |  |  |

|                                                   |                          | FlexPWM_0  | B[2]            | B[2]           |  |  |

|                                                   |                          | SIUL       | —               | EIRQ[11]       |  |  |

| 84                                                | JCOMP                    | _          | —               | JCOMP          |  |  |

|                                                   |                          | SIUL       | GPIO[47]        | GPIO[47]       |  |  |

|                                                   |                          | FlexRay    | CA_TR_EN        |                |  |  |

| 05                                                | 01451                    | eTimer_1   | ETC[0]          | ETC[0]         |  |  |

| 85                                                | C[15]                    | FlexPWM_0  | A[1]            | A[1]           |  |  |

|                                                   | -                        | CTU_0      | _               | EXT_IN         |  |  |

|                                                   |                          | FlexPWM_0  | _               | EXT_SYNC       |  |  |

|                                                   |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |  |

|                                                   | D[0]                     | FlexRay    | CA_TX           |                |  |  |

| 86                                                |                          | eTimer_1   | ETC[1]          | ETC[1]         |  |  |

|                                                   |                          | FlexPWM_0  | B[1]            | B[1]           |  |  |

| 87                                                | V <sub>DD_HV_IO</sub>    |            |                 |                |  |  |

| 88                                                | V <sub>SS_HV_IO</sub>    |            | _               |                |  |  |

|                                                   |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |  |

|                                                   | - Diol                   | FlexRay    | CB_TX           | _              |  |  |

| 89                                                | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |  |

|                                                   | -                        | FlexPWM_0  | A[3]            | A[3]           |  |  |

|                                                   |                          | SIUL       | GPIO[52]        | GPIO[52]       |  |  |

| 00                                                |                          | FlexRay    | CB_TR_EN        | _              |  |  |

| 90                                                | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |  |

|                                                   | -                        | FlexPWM_0  | B[3]            | B[3]           |  |  |

| 91                                                | V <sub>DD_HV_REG_2</sub> |            |                 |                |  |  |

| 92                                                | V <sub>DD_LV_COR</sub>   |            | _               |                |  |  |

| 93                                                | V <sub>SS_LV_COR</sub>   |            | _               |                |  |  |

|                                                   | _                        | SIUL       | GPIO[9]         | GPIO[9]        |  |  |

| 0.1                                               | 4 (0)                    | DSPI_2     | CS1             |                |  |  |

| 94                                                | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |  |

|                                                   |                          | FlexPWM_0  | _               | FAULT[0]       |  |  |

Table 3. LQFP100 pin function summary (continued)

| Pin #  | Port/function            | Peripheral | n summary (continue<br>Output function | Input function |

|--------|--------------------------|------------|----------------------------------------|----------------|

| 1 11 # | 1 of a failed of f       | _          | -                                      |                |

|        |                          | SIUL       | GPIO[39]                               | GPIO[39]       |

| 15     | C[7]                     | FlexPWM_0  | A[1]                                   | A[1]           |

|        |                          | SSCM       | DEBUG[7]                               |                |

|        |                          | DSPI_0     | —                                      | SIN            |

| 16     | V <sub>DD_HV_REG_0</sub> |            | _                                      |                |

| 17     | V <sub>SS_LV_COR</sub>   |            | _                                      |                |

| 18     | V <sub>DD_LV_COR</sub>   |            | _                                      |                |

| 19     | F[7]                     | SIUL       | GPIO[87]                               | GPIO[87]       |

| 15     | .[,]                     | NPC        | МСКО                                   | _              |

| 20     | <b>E</b> [0]             | SIUL       | GPIO[88]                               | GPIO[88]       |

| 20     | F[8]                     | NPC        | MSEO[1]                                | _              |

| 21     | V <sub>DD_HV_IO</sub>    |            |                                        |                |

| 22     | V <sub>SS_HV_IO</sub>    |            | —                                      |                |

|        |                          | SIUL       | GPIO[89]                               | GPIO[89]       |

| 23     | F[9]                     | NPC        | MSEO[0]                                |                |

|        |                          | SIUL       | GPIO[90]                               | GPIO[90]       |

| 24     | F[10]                    | NPC        | EVTO                                   |                |

|        |                          | SIUL       | GPIO[91]                               | GPIO[91]       |

| 25     | F[11]                    | NPC        | _                                      | EVTI           |

|        |                          | SIUL       | GPIO[57]                               | GPIO[57]       |

| 26     | D[9]                     | FlexPWM_0  | X[0]                                   | X[0]           |

| 20     | 5[0]                     | LINFlexD 1 | TXD                                    | ,(0]           |

| 27     | N/                       |            | TAD                                    |                |

| 28     | V <sub>DD_HV_OSC</sub>   |            |                                        |                |

| 20     | V <sub>SS_HV_OSC</sub>   |            |                                        |                |

| -      | XTAL                     |            |                                        |                |

| 30     | EXTAL                    |            | _                                      |                |

| 31     | RESET                    |            | _                                      |                |

|        |                          | SIUL       | GPIO[56]                               | GPIO[56]       |

|        |                          | DSPI_1     | CS2                                    | —              |

| 32     | D[8]                     | eTimer_1   | ETC[4]                                 | ETC[4]         |

|        |                          | DSPI_0     | CS5                                    |                |

|        |                          | FlexPWM_0  | —                                      | FAULT[3]       |

|        |                          | SIUL       | GPIO[53]                               | GPIO[53]       |

| 33     | D[5]                     | DSPI_0     | CS3                                    |                |

|        |                          | FlexPWM_0  | —                                      | FAULT[2]       |

Table 4. LQFP144 pin function summary (continued)

|       | Table 4. LQ                  | (FP144 pin function | n summary (continu | ed)            |

|-------|------------------------------|---------------------|--------------------|----------------|

| Pin # | Port/function                | Peripheral          | Output function    | Input function |

|       |                              | SIUL                | GPIO[54]           | GPIO[54]       |

| 24    | DIG                          | DSPI_0              | CS2                | —              |

| 34    | D[6]                         | FlexPWM_0           | X[3]               | X[3]           |

|       |                              | FlexPWM_0           | _                  | FAULT[1]       |

| 35    | V <sub>SS_LV_PLL0_PLL1</sub> |                     |                    |                |

| 36    | V <sub>DD_LV_PLL0_PLL1</sub> |                     | _                  |                |

|       |                              | SIUL                | GPIO[55]           | GPIO[55]       |

| 07    |                              | DSPI_1              | CS3                |                |

| 37    | D[7] -                       | DSPI_0              | CS4                |                |

|       | -                            | SWG                 | analog output      |                |

| 38    | FCCU_F[0]                    | FCCU                | F[0]               | F[0]           |

| 39    | V <sub>DD_LV_COR</sub>       |                     | —                  |                |

| 40    | V <sub>SS_LV_COR</sub>       |                     | _                  |                |

|       |                              | SIUL                | —                  | GPIO[33]       |

| 41    | C[1]                         | ADC_0               | _                  | AN[2]          |

|       |                              | SIUL                | _                  | GPIO[68]       |

| 42    | E[4] -                       | ADC_0               | _                  | AN[7]          |

|       |                              | SIUL                | _                  | GPIO[23]       |

| 43    | B[7]                         | LINFlexD_0          | _                  | RXD            |

|       |                              | ADC_0               | _                  | AN[0]          |

|       |                              | SIUL                | _                  | GPIO[69]       |

| 44    | E[5] -                       | ADC_0               | _                  | AN[8]          |

|       |                              | SIUL                | _                  | GPIO[34]       |

| 45    | C[2]                         | ADC_0               | _                  | AN[3]          |

|       |                              | SIUL                | _                  | GPIO[70]       |

| 46    | E[6]                         | ADC_0               | _                  | AN[4]          |

|       |                              | SIUL                | _                  | GPIO[24]       |

| 47    | B[8]                         | eTimer_0            |                    | ETC[5]         |

|       | -                            | ADC_0               |                    | AN[1]          |

| 40    |                              | SIUL                | —                  | GPIO[71]       |

| 48    | E[7] -                       | ADC_0               | —                  | AN[6]          |

| 10    | FIG                          | SIUL                | _                  | GPIO[66]       |

| 49    | E[2] -                       | ADC_0               | —                  | AN[5]          |

| 50    | V <sub>DD_HV_ADR0</sub>      |                     |                    | 1              |

| 51    | V <sub>SS_HV_ADR0</sub>      |                     | _                  |                |

|       |                              |                     |                    |                |

Table 4. LQFP144 pin function summary (continued)

| Table 4. LQFP144 pin function summary (continued) |                          |            |                 |                |  |

|---------------------------------------------------|--------------------------|------------|-----------------|----------------|--|

| Pin #                                             | Port/function            | Peripheral | Output function | Input function |  |

|                                                   |                          | SIUL       | GPIO[48]        | GPIO[48]       |  |

| 125                                               | D[0]                     | FlexRay    | CA_TX           | _              |  |

| 120                                               |                          | eTimer_1   | ETC[1]          | ETC[1]         |  |

|                                                   |                          | FlexPWM_0  | B[1]            | B[1]           |  |

| 126                                               | V <sub>DD_HV_IO</sub>    | —          |                 |                |  |

| 127                                               | V <sub>SS_HV_IO</sub>    |            |                 |                |  |

|                                                   |                          | SIUL       | GPIO[51]        | GPIO[51]       |  |

| 128                                               | 0121                     | FlexRay    | CB_TX           | _              |  |

| 120                                               | D[3]                     | eTimer_1   | ETC[4]          | ETC[4]         |  |

|                                                   |                          | FlexPWM_0  | A[3]            | A[3]           |  |

|                                                   |                          | SIUL       | GPIO[52]        | GPI0[52]       |  |

| 100                                               | DI4                      | FlexRay    | CB_TR_EN        |                |  |

| 129                                               | D[4]                     | eTimer_1   | ETC[5]          | ETC[5]         |  |

|                                                   |                          | FlexPWM_0  | B[3]            | B[3]           |  |

| 130                                               | V <sub>DD_HV_REG_2</sub> |            | _               |                |  |

| 131                                               | V <sub>DD_LV_COR</sub>   |            |                 |                |  |

| 132                                               | V <sub>SS_LV_COR</sub>   |            | —               |                |  |

|                                                   |                          | SIUL       | GPIO[80]        | GPIO[80]       |  |

| 133                                               | F[0]                     | FlexPWM_0  | A[1]            | A[1]           |  |

| 155                                               |                          | eTimer_0   | —               | ETC[2]         |  |

|                                                   |                          | SIUL       | —               | EIRQ[28]       |  |

|                                                   |                          | SIUL       | GPIO[9]         | GPIO[9]        |  |

| 134                                               | A101                     | DSPI_2     | CS1             | —              |  |

| 134                                               | A[9]                     | FlexPWM_0  | B[3]            | B[3]           |  |

|                                                   |                          | FlexPWM_0  | —               | FAULT[0]       |  |

| 135                                               | V <sub>DD_LV_COR</sub>   |            |                 |                |  |

|                                                   |                          | SIUL       | GPIO[13]        | GPIO[13]       |  |

|                                                   | [                        | FlexPWM_0  | B[2]            | B[2]           |  |

| 136                                               | A[13]                    | DSPI_2     | —               | SIN            |  |

|                                                   |                          | FlexPWM_0  | —               | FAULT[0]       |  |

|                                                   |                          | SIUL       | —               | EIRQ[12]       |  |

| 137                                               | V <sub>SS_LV_COR</sub>   |            | —               |                |  |

Table 4. LQFP144 pin function summary (continued)

|       | Table 5. LFE               | BGAZOI PIN functio | on summary (continu | lea)           |

|-------|----------------------------|--------------------|---------------------|----------------|

| Pin # | Port/function              | Peripheral         | Output function     | Input function |

|       |                            | SIUL               | GPIO[79]            | GPIO[79]       |

| B11   | E[15]                      | DSPI_0             | CS1                 | —              |

|       |                            | SIUL               | —                   | EIRQ[27]       |

|       |                            | SIUL               | GPIO[78]            | GPIO[78]       |

| B12   | E[14]                      | eTimer_1           | ETC[5]              | ETC[5]         |

|       |                            | SIUL               | —                   | EIRQ[26]       |

|       |                            | SIUL               | GPIO[19]            | GPIO[19]       |

| B13   | B[3]                       | SSCM               | DEBUG[3]            | —              |

|       |                            | LINFlexD_0         | —                   | RXD            |

|       |                            | SIUL               | GPIO[93]            | GPIO[93]       |

| B14   | F[13]                      | eTimer_1           | ETC[4]              | ETC[4]         |

|       |                            | SIUL               | —                   | EIRQ[31]       |

|       |                            | SIUL               | GPIO[16]            | GPIO[16]       |

|       | B[0]                       | FlexCAN_0          | TXD                 | —              |

| B15   |                            | eTimer_1           | ETC[2]              | ETC[2]         |

|       |                            | SSCM               | DEBUG[0]            | —              |

|       |                            | SIUL               | —                   | EIRQ[15]       |

| B16   | V <sub>DD_HV_IO_RING</sub> |                    | _                   |                |

| B17   | V <sub>SS_HV_IO_RING</sub> |                    | _                   |                |

| C1    | V <sub>DD_HV_IO_RING</sub> |                    | _                   |                |

| C2    | Not connected              |                    | —                   |                |

| C3    | V <sub>SS_HV_IO_RING</sub> |                    | _                   |                |

| C4    | FCCU_F[1]                  | FCCU               | F[1]                | F[1]           |

|       |                            | SIUL               | GPIO[50]            | GPIO[50]       |

| C5    | וניוס                      | eTimer_1           | ETC[3]              | ETC[3]         |

| 05    | D[2] -                     | FlexPWM_0          | X[3]                | X[3]           |

|       |                            | FlexRay            | —                   | CB_RX          |

|       |                            | SIUL               | GPIO[13]            | GPIO[13]       |

|       |                            | FlexPWM_0          | B[2]                | B[2]           |

| C6    | A[13]                      | DSPI_2             |                     | SIN            |

|       | [ [                        | FlexPWM_0          | _                   | FAULT[0]       |

|       |                            | SIUL               | -                   | EIRQ[12]       |

| C7    | V <sub>DD_HV_REG_2</sub>   |                    | _                   |                |

|       | V <sub>DD_HV_REG_2</sub>   |                    |                     |                |

Table 5. LFBGA257 pin function summary (continued)

|       | Table 5. LFBGA257 pin function summary (continued) |            |                 |                |  |  |  |

|-------|----------------------------------------------------|------------|-----------------|----------------|--|--|--|

| Pin # | Port/function                                      | Peripheral | Output function | Input function |  |  |  |

|       |                                                    | SIUL       | GPIO[128]       | GPIO[128]      |  |  |  |

| C9    | 1(0)                                               | eTimer_2   | ETC[0]          | ETC[0]         |  |  |  |

| Ca    | I[0] -                                             | DSPI_0     | CS4             | _              |  |  |  |

|       |                                                    | FlexPWM_1  | —               | FAULT[0]       |  |  |  |

| C10   | JCOMP                                              | _          | —               | JCOMP          |  |  |  |

| 011   | 11[44]                                             | SIUL       | GPIO[123]       | GPIO[123]      |  |  |  |

| C11   | H[11] -                                            | FlexPWM_1  | A[2]            | A[2]           |  |  |  |

|       |                                                    | SIUL       | GPIO[129]       | GPIO[129]      |  |  |  |

| 040   | 1541                                               | eTimer_2   | ETC[1]          | ETC[1]         |  |  |  |

| C12   | I[1] -                                             | DSPI_0     | CS5             | _              |  |  |  |

|       |                                                    | FlexPWM_1  | _               | FAULT[1]       |  |  |  |

| 040   | <b>FI4 4</b> 1                                     | SIUL       | GPIO[94]        | GPIO[94]       |  |  |  |

| C13   | F[14]                                              | LINFlexD_1 | TXD             |                |  |  |  |

|       |                                                    | SIUL       | GPIO[17]        | GPI0[17]       |  |  |  |

|       | B[1]                                               | eTimer_1   | ETC[3]          | ETC[3]         |  |  |  |

| 014   |                                                    | SSCM       | DEBUG[1]        | —              |  |  |  |

| C14   |                                                    | FlexCAN_0  | _               | RXD            |  |  |  |

|       |                                                    | FlexCAN_1  | —               | RXD            |  |  |  |

|       |                                                    | SIUL       | —               | EIRQ[16]       |  |  |  |

| C15   | V <sub>SS_HV_IO_RING</sub>                         |            |                 |                |  |  |  |

|       |                                                    | SIUL       | GPIO[4]         | GPIO[4]        |  |  |  |

|       |                                                    | eTimer_1   | ETC[0]          | ETC[0]         |  |  |  |

| C16   | 0[4]                                               | DSPI_2     | CS1             | _              |  |  |  |

| 010   | A[4]                                               | eTimer_0   | ETC[4]          | ETC[4]         |  |  |  |

|       |                                                    | MC_RGM     | —               | FAB            |  |  |  |

|       |                                                    | SIUL       | —               | EIRQ[4]        |  |  |  |

|       |                                                    | SIUL       | GPIO[92]        | GPI0[92]       |  |  |  |

| C17   | F[12]                                              | eTimer_1   | ETC[3]          | ETC[3]         |  |  |  |

|       |                                                    | SIUL       | —               | EIRQ[30]       |  |  |  |

| D4    | FIEL                                               | SIUL       | GPIO[85]        | GPIO[85]       |  |  |  |

| D1    | F[5] -                                             | NPC        | MDO[2]          | _              |  |  |  |

| 20    | E[4]                                               | SIUL       | GPIO[84]        | GPIO[84]       |  |  |  |

| D2    | F[4] -                                             | NPC        | MDO[3]          | _              |  |  |  |

Table 5. LFBGA257 pin function summary (continued)

|                     | Supply                                                                                                                                                                                 |            |            |                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------------------|

| Symbol              | Description                                                                                                                                                                            | 100<br>pkg | 144<br>pkg | 257<br>pkg            |

| V <sub>SS</sub> 1V2 | VSS_LV_COR<br>Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                                        | 93         | 132        | VSS_LV <sup>(2)</sup> |

| V <sub>DD</sub> 1V2 | $\label{eq:VDD_LV_COR} VDD_LV_COR / \\ Decoupling pins for core logic. Decoupling capacitor must be \\ connected between these pins and the nearest V_{DD_LV_COR} pin. \\ \end{array}$ | _          | 135        | VDD_LV <sup>(1)</sup> |

| V <sub>SS</sub> 1V2 | VSS_LV_COR / Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV_COR}$ pin.                                            | _          | 137        | VSS_LV <sup>(2)</sup> |

#### Table 6. Supply pins (continued)

1. VDD\_LV balls are tied together on the LFBGA257 substrate.

2. VSS\_LV balls are tied together on the LFBGA257 substrate.

3. VDD\_HV balls are tied together on the LFBGA257 substrate.

4. VSS\_HV balls are tied together on the LFBGA257 substrate.

# 2.3 System pins

### Table 7. System pins

|                      |                                                                                                                                                                                                                         |                     | Pin #      |            |            |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|------------|------------|

| Symbol               | Description                                                                                                                                                                                                             | Direction           | 100<br>pkg | 144<br>pkg | 257<br>pkg |

|                      | Dedicated pins                                                                                                                                                                                                          |                     |            |            |            |

| MDO0 <sup>(1)</sup>  | Nexus Message Data Output — line                                                                                                                                                                                        | Output only         | —          | 9          | E1         |

| NMI <sup>(2)</sup>   | Non Maskable Interrupt                                                                                                                                                                                                  | Input only          | 1          | 1          | E4         |

| XTAL                 | Input for oscillator amplifier circuit and internal clock generator                                                                                                                                                     | Input only          | 18         | 29         | N1         |

| EXTAL <sup>(3)</sup> | Oscillator amplifier output                                                                                                                                                                                             | Input/Output<br>(4) | 19         | 30         | R1         |

| TMS <sup>(2)</sup>   | JTAG state machine control                                                                                                                                                                                              | Input only          | 59         | 87         | M16        |

| TCK <sup>(2)</sup>   | JTAG clock                                                                                                                                                                                                              | Input only          | 60         | 88         | L15        |

| JCOMP <sup>(5)</sup> | JTAG compliance select                                                                                                                                                                                                  | Input only          | 84         | 123        | C10        |

|                      | Reset pin                                                                                                                                                                                                               |                     |            |            |            |

| RESET                | Bidirectional reset with Schmitt-Trigger characteristics and noise filter. This pin has medium drive strength. Output drive is open drain and must be terminated by an external resistor of value 1KOhm. <sup>(6)</sup> | Bidirectional       | 20         | 31         | P2         |

|                      | Test pin                                                                                                                                                                                                                |                     |            |            |            |

| VPP TEST             | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                                                            |                     | 74         | 107        | D15        |

|                      |                                                                                                                                                                                                                         |                     |            |            |            |

1. This pad is configured for Fast (F) pad speed.

|             |        |            |                     | Table   | e 8. Pin muxin       | g                     |                         |            |                             |            |            |          |   |

|-------------|--------|------------|---------------------|---------|----------------------|-----------------------|-------------------------|------------|-----------------------------|------------|------------|----------|---|

| Port        | PCR    | Peripheral | Alternate<br>output | Output  | Input                | Input mux             | Weak pull config during |            | Pad<br>speed <sup>(1)</sup> |            | Pin #      |          |   |

| name        | FCK    | renpilerai | function            | mux sel | functions            | select                | reset                   | SRC<br>= 1 | SRC<br>= 0                  | 100<br>pkg | 144<br>pkg | 25<br>pk |   |

|             |        |            |                     | •       | Port A               |                       |                         |            |                             |            |            |          |   |

|             |        | SIUL       | GPIO[0]             | ALT0    | GPIO[0]              | _                     |                         |            |                             |            |            |          |   |

| A[0] PCR[0] | DCD[0] | eTimer_0   | ETC[0]              | ALT1    | ETC[0]               | PSMI[35];<br>PADSEL=0 | -                       | - M        |                             | S          | 51         | 73       | т |

|             | DSPI_2 | SCK        | ALT2                | SCK     | PSMI[1];<br>PADSEL=0 |                       |                         | IVI        | 5 51                        | 51         | 73         | T14      |   |

|             |        | SIUL       | —                   | _       | EIRQ[0]              | —                     |                         |            |                             |            |            |          |   |

| A[1] PCR[1] |        | SIUL       | GPIO[1]             | ALT0    | GPIO[1]              | —                     |                         |            |                             |            | 74         | R14      |   |

|             | PCR[1] | eTimer_0   | ETC[1]              | ALT1    | ETC[1]               | PSMI[36];<br>PADSEL=0 | — М                     | М          | S                           | 52         |            |          |   |

|             | DSPI_2 | SOUT       | ALT2                | _       | —                    |                       |                         |            |                             |            |            |          |   |

|             | SIUL   | —          | —                   | EIRQ[1] | —                    |                       |                         |            |                             |            |            |          |   |

|             |        | SIUL       | GPIO[2]             | ALT0    | GPIO[2]              | —                     |                         |            |                             |            |            |          |   |

|             |        | eTimer_0   | ETC[2]              | ALT1    | ETC[2]               | PSMI[37];<br>PADSEL=0 | <br>Pull down M         |            | S                           | 57         | 84         | N16      |   |

|             | PCR[2] | FlexPWM_0  | A[3]                | ALT3    | A[3]                 | PSMI[23];<br>PADSEL=0 |                         | М          |                             |            |            |          |   |

|             |        | DSPI_2     | —                   | _       | SIN                  | PSMI[2];<br>PADSEL=0  |                         |            |                             |            |            |          |   |

|             |        | MC_RGM     | _                   | —       | ABS[0]               | —                     | ]                       |            |                             |            |            |          |   |

|             |        | SIUL       |                     | _       | EIRQ[2]              | _                     |                         |            |                             |            |            |          |   |

SPC56ELX, SPC564LX

75/165

Package pinouts and signal descriptions

### Equation 2: $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

$\mathsf{R}_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $\mathsf{R}_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using *Equation 3*:

Equation 3  $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$T_T$ = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$ = thermal characterization parameter (°C/W)

$P_D$ = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### 3.5.1.1 References

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB on JEDEC site.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications," Electronic Packaging and Production, pp. 53–58, March 1998.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

SPC56XL60/54 makes a transition from HPREG1 to HPREG2. This transition is dynamic. Once HPREG2 is fully operational, the controller part of HPREG1 is switched off.

The following bipolar transistors are supported:

- BCP68 from ON Semiconductor

- BCX68 from Infineon

| Symbol              | Parameter                                              | Value              | Unit |

|---------------------|--------------------------------------------------------|--------------------|------|

| -                   | - diameter                                             | Taluo              | •    |

| h <sub>FE</sub> (β) | DC current gain (Beta)                                 | 85 - 375           | —    |

| P <sub>D</sub>      | Maximum power dissipation @ $T_A$ =25°C <sup>(1)</sup> | 1.5                | W    |

| I <sub>CMaxDC</sub> | Maximum peak collector current                         | 1.0                | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage (Max)          | 600 <sup>(2)</sup> | mV   |

| V <sub>BE</sub>     | Base-to-emitter voltage (Max)                          | 1.0                | V    |

#### Table 19. Characteristics

1. Derating factor 12mW/degC.

2. Adjust resistor at bipolar transistor collector for 3.3V to avoid VCE<VCE<sub>SAT</sub>.

The recommended external ballast transistor is the bipolar transistor BCP68 with the gain range of 85 up to 375 (for IC=500mA, VCE=1V) provided by several suppliers. This includes the gain variations BCP68-10, BCP68-16 and BCP68-25. The most important parameters for the interoperability with the integrated voltage regulator are the DC current gain (hFE) and the temperature coefficient of the gain (XTB). While the specified gain range of most BCP68 vendors is the same, there are slight variations in the temperature coefficient parameter. SPC56XL60/54 Voltage regulator operation was simulated against the typical variation on temperature coefficient and against the specified gain range to have a robust design.

| Sym               | bol | Parameter                                                         | Conditions                                                                                                          | Min | Тур | Max | Unit |

|-------------------|-----|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>ext</sub>  |     | External decoupling/<br>stability capacitor                       | Min, max values shall be<br>granted with respect to<br>tolerance, voltage,<br>temperature, and aging<br>variations. | 12  | _   | 40  | μF   |

|                   | SR  | Combined ESR of external capacitor                                | _                                                                                                                   | 1   | _   | 100 | mΩ   |

|                   | SR  | Number of pins for<br>external decoupling/<br>stability capacitor | _                                                                                                                   | 5   | _   | _   | _    |

| C <sub>V1V2</sub> | SR  | Total capacitance on 1.2 V pins                                   | Ceramic capacitors,<br>taking into account<br>tolerance, aging, voltage<br>and temperature<br>variation             | 300 | _   | 900 | nF   |

| t <sub>SU</sub>   |     | Start-up time after main supply stabilization                     | $C_{load}$ = 10 µF × 4                                                                                              | _   | _   | 2.5 | ms   |

| Table 20. \ | Voltage regulator | electrical | specifications |

|-------------|-------------------|------------|----------------|

|-------------|-------------------|------------|----------------|

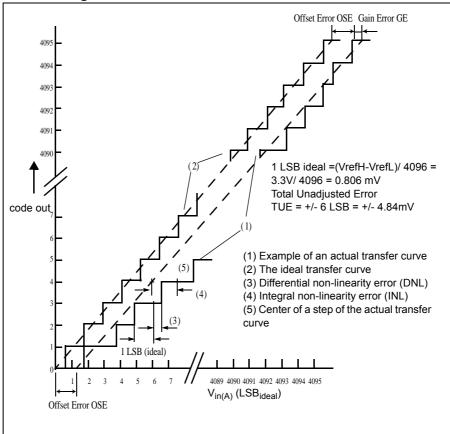

Figure 9. ADC characteristics and error definitions

# 3.16.1 Input Impedance and ADC Accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2}$  + CS equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ}$  = 1 / (fS\*( $C_{p2}$ + $C_S$ )), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S$  +  $R_F$ , the external circuit must be designed to respect the *Equation 4*:

|                                                                              |                                         | Reset<br>Sequence<br>End<br>Indication | Reset Sequence                                                      |                                                                      |                                                           |                                         |                                          |  |

|------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------|------------------------------------------|--|

| Reset<br>Sequence<br>Trigger                                                 | Reset<br>Sequence<br>Start<br>Condition |                                        | Destructive<br>Reset<br>Sequence,<br>BIST<br>enabled <sup>(1)</sup> | Destructive<br>Reset<br>Sequence,<br>BIST<br>disabled <sup>(1)</sup> | External<br>Reset<br>Sequence<br>Long,<br>BIST<br>enabled | Functional<br>Reset<br>Sequence<br>Long | Functional<br>Reset<br>Sequence<br>Short |  |

| All internal<br>functional reset<br>sources<br>configured for<br>long reset  | Sequence<br>starts with                 | Release of                             | cannot trigger                                                      |                                                                      | cannot<br>trigger                                         | triggers                                | cannot<br>trigger                        |  |

| All internal<br>functional reset<br>sources<br>configured for<br>short reset | internal reset<br>trigger               | RESET <sup>(7)</sup>                   | cannot trigger                                                      |                                                                      | cannot<br>trigger                                         | cannot<br>trigger                       | triggers                                 |  |

#### Table 34. Reset sequence trigger — reset sequence (continued)

1. Whether BIST is executed or not depends on the chip configuration data stored in the shadow sector of the NVM.

End of the internal reset sequence (as specified in Table 33) can only be observed by release of RESET if it is not held low

externally beyond the end of the internal sequence which would prolong the internal reset PHASE3 till RESET is released

externally.

- The assertion of RESET can only trigger a reset sequence if the device was running (RESET released) before. RESET

does not gate a Destructive Reset Sequence, BIST enabled or a Destructive Reset Sequence, BIST disabled. However, it

can prolong these sequences if RESET is held low externally beyond the end of the internal sequence (beyond PHASE3).

- 4. If RESET is configured for long reset (default) and if BIST is enabled via chip configuration data stored in the shadow sector of the NVM.

- 5. If RESET is configured for long reset (default) and if BIST is disabled via chip configuration data stored in the shadow sector of the NVM.

- 6. If RESET is configured for short reset

- 7. Internal reset sequence can only be observed by state of RESET if bidirectional RESET functionality is enabled for the functional reset source which triggered the reset sequence.

# 3.20.4 Reset sequence — start condition

The impact of the voltage thresholds on the starting point of the internal reset sequence becomes important if the voltage rails / signals ramp up with a very slow slew rate compared to the overall reset sequence duration.

#### 3.20.4.1 Destructive reset

*Figure 19* shows the voltage threshold that determines the start of the *Destructive Reset Sequence, BIST enabled* and the start for the *Destructive Reset Sequence, BIST disabled*.

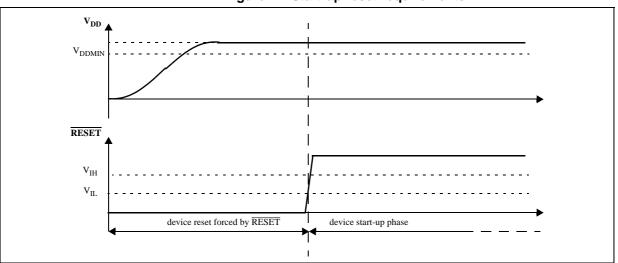

Figure 22. Start-up reset requirements

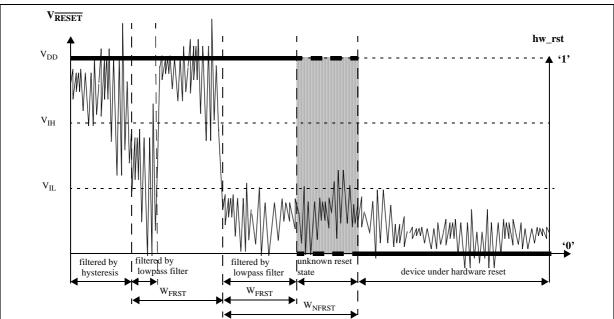

Figure 23. Noise filtering on reset signal

| Table 36. | RESET | electrical | characteristics |

|-----------|-------|------------|-----------------|

| No. | Symb               | ol | Parameter                                        | Conditions <sup>(1)</sup> | Min | Тур | Max | Unit |

|-----|--------------------|----|--------------------------------------------------|---------------------------|-----|-----|-----|------|

|     |                    |    |                                                  | C <sub>L</sub> = 25pF     | _   | —   | 12  |      |

| 1   | T <sub>tr</sub>    |    | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 50pF     | _   | —   | 25  | ns   |

|     |                    |    |                                                  | C <sub>L</sub> = 100pF    | _   | —   | 40  |      |

| 2   | W <sub>FRST</sub>  | Ρ  | nRESET input filtered pulse                      | —                         | -   | —   | 40  | ns   |

| 3   | W <sub>NFRST</sub> | Ρ  | nRESET input not filtered pulse                  | _                         | 500 | _   | _   | ns   |

1.  $V_{DD}$  = 3.3 V  $\pm$  10%,  $T_{J}$  = –40 to +150 °C, unless otherwise specified.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Jun-2010 | 4<br>(continued) | <ul> <li>In the "Main oscillator electrical characteristics" table, changed the maximum specification for g<sub>mXOSCHS</sub> (was 11 mA/V, is 11.8 mA/V).</li> <li>Revised the "ADC electrical characteristics" section. In the "ADC conversion characteristics" table:</li> <li>Changed the t<sub>ADC_S</sub> specification (was TBD, is minimum of 383 ns).</li> <li>Added the footnote "No missing codes" to the DNL specification.</li> <li>Added specifications for SNR, THD, SINAD, and ENOB.</li> <li>Revised the "Ordering information" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23-Nov-2010 | 5                | Editorial changes and improvements.<br>Revised the Overview section.<br>Replaced references to PowerPC with references to Power Architecture.<br>In the feature summary, changed "As much as 128 KB on-chip SRAM" to<br>"128 KB on-chip SRAM".<br>In the "Feature details" section:<br>– In the "On-chip SRAM with ECC" section, added information about required<br>RAM wait states.<br>– In the PIT section, deleted "32-bit counter for real time interrupt, clocked<br>from main external oscillator" (not supported on this device).<br>– In the flash-memory section, changed "16 KB Test" to "16 KB test sector",<br>revised the wait state information, and deleted the associated Review_Q&A<br>content.<br>– In the SRAM section, revised the wait state information.<br>In the 100-pin pinout diagram:<br>– Renamed pin 41 (was VDD_HV_ADV0_ADV1, is VDD_HV_ADV).<br>– Renamed pin 42 (was VSS_HV_ADV0_ADV1, is VDS_HV_ADV).<br>In the 144-pin pinout diagram:<br>– Renamed pin 58 (was VDD_HV_ADV0_ADV1, is VDS_HV_ADV).<br>– Renamed pin 58 (was VDD_HV_ADV0_ADV1, is VSS_HV_ADV).<br>Added the "LQFP100 pin function summary" table.<br>In the "LQFP144 pin function summary" table, for pin 39, changed V <sub>SS_LV_COR</sub><br>to V <sub>DD_LV_COR</sub> .<br>In the "Supply pins" table:<br>– Changed the description for V <sub>DD_LV_COR</sub> (was "Voltage regulator supply<br>voltage", is "Core logic supply").<br>– Changed the description for V <sub>DD_HV_PMU</sub> (was "Core regulator supply", is<br>"Voltage regulator supply").<br>In the "Pin muxing" table:<br>– In the "Pad speed" column headings, changed "SRC = 0" to "SRC = 1" and<br>"SRC = 1" to "SRC = 0"<br>– For port B[6], changed the pad speed for SRC=0 (was M, is F).<br>In the "Thermal characteristics" section, added meaningful values to the<br>thermal-characteristics tables.<br>Added the "SWG electrical specifications" section.<br>In the "Voltage regulator electrical characteristics" section, changed the table<br>title (was "HPREG1, HPREG2, Main LVDs, Digital HVD, and Digital LVD<br>electrical specifications", is "Voltage regulator electrical characteristics") and<br>revised the table. |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Sep-2013 | 10       | - Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |