Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are analyzared to

#### Details

⊡XFI

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                     |

| Applications            | Automotive                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                              |

| Program Memory Type     | FLASH (128kB)                                                                |

| Controller Series       | -                                                                            |

| RAM Size                | 6K x 8                                                                       |

| Interface               | LIN, SSI, UART                                                               |

| Number of I/O           | 10                                                                           |

| Voltage - Supply        | 5.5V ~ 28V                                                                   |

| Operating Temperature   | -40°C ~ 150°C                                                                |

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 48-VFQFN Exposed Pad                                                         |

| Supplier Device Package | PG-VQFN-48-31                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/tle9879qxa20xuma2 |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1.1 Abbreviations

The following acronyms and terms are used within this document. List see in Table 1.

| Table 1 Acronyms |                                                     |

|------------------|-----------------------------------------------------|

| Acronyms         | Name                                                |

| AHB              | Advanced High-Performance Bus                       |

| APB              | Advanced Peripheral Bus                             |

| CCU6             | Capture Compare Unit 6                              |

| CGU              | Clock Generation Unit                               |

| СМИ              | Cyclic Management Unit                              |

| СР               | Charge Pump for MOSFET driver                       |

| CSA              | Current Sense Amplifier                             |

| DPP              | Data Post Processing                                |

| ECC              | Error Correction Code                               |

| EEPROM           | Electrically Erasable Programmable Read Only Memory |

| EIM              | Exceptional Interrupt Measurement                   |

| FSM              | Finite State Machine                                |

| GPIO             | General Purpose Input Output                        |

| H-Bridge         | Half Bridge                                         |

| ICU              | Interrupt Control Unit                              |

| IEN              | Interrupt Enable                                    |

| IIR              | Infinite Impulse Response                           |

| LDM              | Load Instruction                                    |

| LDO              | Low DropOut voltage regulator                       |

| LIN              | Local Interconnect Network                          |

| LSB              | Least Significant Bit                               |

| LTI              | Lead Tip Inspection                                 |

| MCU              | Memory Control Unit                                 |

| MF               | Measurement Functions                               |

| MSB              | Most Significant Bit                                |

| MPU              | Memory Protection Unit                              |

| MRST             | Master Receive Slave Transmit                       |

| MTSR             | Master Transmit Slave Receive                       |

| MU               | Measurement Unit                                    |

| NMI              | Non Maskable Interrupt                              |

| NVIC             | Nested Vector Interrupt Controller                  |

| NVM              | Non-Volatile Memory                                 |

| OTP              | One Time Programmable                               |

| OSC              | Oscillator                                          |

| РВА              | Peripheral Bridge                                   |

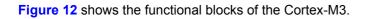

**ARM Cortex-M3 Core**

## 8.2 Introduction

The ARM Cortex-M3 processor is a leading 32-bit processor and provides a high-performance and cost-optimized platform for a broad range of applications including microcontrollers, automotive body systems and industrial control systems. Like the other Cortex family processors, the Cortex-M3 processor implements the Thumb<sup>®</sup>-2 instruction set architecture. With the optimized feature set the Cortex-M3 delivers 32-bit performance in an application space that is usually associated with 8- and 16-bit microcontrollers.

## 8.2.1 Block Diagram

Figure 12 Cortex-M3 Block Diagram

### Interrupt System

## Table 7NMI Interrupt Table

| Service Request            | Node | Description                                          |

|----------------------------|------|------------------------------------------------------|

| Oscillator Watchdog<br>NMI | NMI  | Oscillator Watchdog / MI_CLK Watchdog Timer Overflow |

| NVM Map Error NMI          | NMI  | NVM Map Error                                        |

| ECC Error NMI              | NMI  | RAM / NVM Uncorrectable ECC Error                    |

| Supply Prewarning NMI      | NMI  | Supply Prewarning                                    |

**GPIO Ports and Peripheral I/O**

## 14.3 TLE9879QXA20 Port Module

14.3.1 Port 0

## 14.3.1.1 Port 0 Functions

### Table 8 Port 0 Input/Output Functions

| Port Pin | Input/Output | Select | Connected Signal(s) | From/to Module  |

|----------|--------------|--------|---------------------|-----------------|

| P0.0     | Input        | GPI    | P0_DATA.P0          |                 |

|          |              | INP1   | SWCLK / TCK_0       | SW              |

|          |              | INP2   | T12HR_0             | CCU6            |

|          |              | INP3   | T4INA               | GPT12T4         |

|          |              | INP4   | T2_0                | Timer 2         |

|          |              | INP5   | _                   | -               |

|          |              | INP6   | EXINT2_3            | SCU             |

|          | Output       | GPO    | P0_DATA.P0          |                 |

|          |              | ALT1   | T3OUT               | GPT12T3         |

|          |              | ALT2   | EXF21_0             | Timer 21        |

|          |              | ALT3   | RXDO_2              | UART2           |

| P0.1     | Input        | GPI    | P0_DATA.P1          |                 |

|          |              | INP2   | T13HR_0             | CCU6            |

|          |              | INP3   | TxD1                | LIN_TxD         |

|          |              | INP4   | CAPINA              | GPT12CAP        |

|          |              | INP5   | T21_0               | Timer 21        |

|          |              | INP6   | T4INC               | GPT12T4         |

|          |              | INP7   | MRST_1_2            | SSC1            |

|          |              | INP8   | EXINT0_2            | SCU             |

|          | Output       | GPO    | P0_DATA.P1          |                 |

|          |              | ALT1   | TxD1                | UART1 / LIN_TxE |

|          |              | ALT2   | -                   | -               |

|          |              | ALT3   | T6OUT               | GPT12T6         |

**GPIO Ports and Peripheral I/O**

# 14.3.3 Port 2

## 14.3.3.1 Port 2 Functions

### Table 10 Port 2 Input Functions

| Port Pin | Input/Output | Select | Connected Signal(s) | From/to Module |  |

|----------|--------------|--------|---------------------|----------------|--|

| P2.0     | Input        | GPI    | P2_DATA.P0          |                |  |

|          |              | INP1   | CCPOS0_3            | CCU6           |  |

|          |              | INP2   | -                   | -              |  |

|          |              | INP3   | T12HR_2             | CCU6           |  |

|          |              | INP4   | EXINT0_0            | SCU            |  |

|          |              | INP5   | CC61_2              | CCU6           |  |

|          |              | ANALOG | AN0                 | ADC            |  |

|          |              |        | XTAL (in)           | XTAL           |  |

| P2.2     | Input        | GPI    | P2_DATA.P2          |                |  |

|          |              | INP1   | CCPOS2_3            | CCU6           |  |

|          |              | INP2   | T13HR_2             | CCU6           |  |

|          |              | INP3   | -                   |                |  |

|          |              | INP4   | CC62_2              | CCU6           |  |

|          |              | ANALOG | AN2                 | ADC            |  |

|          |              | OUT    | XTAL (out)          | XTAL           |  |

| P2.3     | Input        | GPI    | P2_DATA.P3          |                |  |

|          |              | INP1   | CCPOS1_0            | CCU6           |  |

|          |              | INP2   | CTRAP#_1            | CCU6           |  |

|          |              | INP3   | T21EX_2             | Timer 21       |  |

|          |              | INP4   | CC60_1              | CCU6           |  |

|          |              | INP5   | EXINT0_3            | SCU            |  |

|          |              | ANALOG | AN3                 | ADC            |  |

| P2.4     | Input        | GPI    | P2_DATA.P4          |                |  |

|          |              | INP1   | CTRAP#_0            | CCU6           |  |

|          |              | INP2   | T2EUDB              | GPT12T2        |  |

|          |              | INP3   | MRST_1_1            | SSC1           |  |

|          |              | INP4   | EXINT1_3            | SCU            |  |

|          |              | ANALOG | AN4                 | ADC            |  |

| P2.5     | Input        | GPI    | P2_DATA.P5          |                |  |

|          |              | INP1   | RXD2_1              | UART2          |  |

|          |              | INP2   | T3EUDB              | GPT12T3        |  |

|          |              | INP3   | MRST_2_1            | SSC2           |  |

|          |              | INP4   | T2_1                | Timer 2        |  |

|          |              | ANALOG | AN5                 | ADC            |  |

**Timer2 and Timer21**

# 16 Timer2 and Timer21

## 16.1 Features

- 16-bit auto-reload mode

- selectable up or down counting

- One channel 16-bit capture mode

## 16.2 Introduction

The timer modules are general-purpose 16-bit timers. Timer 2/21 can function as a timer or counter in each of its modes. As a timer, it counts with an input clock of  $f_{PCLK}/12$  (if prescaler is disabled). As a counter, Timer 2 counts 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is  $f_{PCLK}/24$  (if prescaler is disabled).

## 16.2.1 Timer2 and Timer21 Modes Overview

| Mode            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Auto-reload     | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmable reload value in register RC2</li> <li>Interrupt is generated with reload events.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Auto-reload     | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up         <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmable reload value in register RC2</li> </ul> </li> <li>Count down         <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by the start of the start counting from FFFF<sub>H</sub>, underflow condition</li> <li>Reload event triggered by the start counting from FFFF<sub>H</sub>, underflow condition</li> <li>Reload event triggered by the start counting from FFFF<sub>H</sub>, underflow condition</li> </ul> </li> </ul> |  |  |  |  |  |  |

| Channel capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated by reload or capture events</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

## Table 11 Timer2 and Timer21 Modes

Timer3

# 17 Timer3

## 17.1 Features

- 16-bit incremental timer/counter (counting up)

- Counting frequency up to  $f_{sys}$

- Selectable clock prescaler

- 6 modes of operation

- Interrupt up on overflow

- Interrupt on compare

## 17.2 Introduction

The possible applications for the timer include measuring the time interval between events, counting events and generating a signal at regular intervals.

Timer3 can function as timer or counter. When functioning as a timer, Timer3 is incremented in periods based on the MI\_CLK or LP\_CLK clock. When functioning as a counter, Timer3 is incremented in response to a 1-to-0 transition (falling edge) at its respective input. Timer3 can be configured in four different operating modes to use in a variety of applications, see **Table 12**.

Several operating modes can be used for different tasks such as the following:

- simple time measurement between two events

- triggering of the measuring unit upon PWM/CCU6 unit

- measurement of the 100kHz LP\_CLK2

## 17.3 Functional Description

Six modes of operation are provided to fulfill various tasks using this timer. In every mode the clocking source can be selected between MI\_CLK and LP\_CLK. A prescaler provides in addition capability to divide the selected clock source by 2, 4 or 8. The timer counts upwards, starting with the value in the timer count registers, until the maximum count value which depends on the selected mode of operation. Timer 3 provides two individual interrupts upon counter overflow, one for the low-byte and one for the high-byte counter register.

## 17.3.1 Timer3 Modes Overview

The following table provides an overview of the timer modes together with the reasonable configuration options in **Table 12**.

| Mode | Sub-<br>Mode    | Operation                                                                                                                                                                                                                                         |

|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | No Sub-<br>Mode | <b>13-bit Timer</b><br>The timer is essentially an 8-bit counter with a divide-by-32 prescaler.                                                                                                                                                   |

| 1    | а               | <b>16-bit Timer</b><br>The timer registers, TL3 and TH3, are concatenated to form a 16-bit counter.                                                                                                                                               |

| 1    | b               | <b>16-bit Timer triggered by an event</b><br>The timer registers, TL3 and TH3, are concatenated to form a 16-bit counter, which is<br>triggered by an event to enable a single shot measurement on a preset channel with the<br>measurement unit. |

|  | Table | 12 | Timer3 | Modes |

|--|-------|----|--------|-------|

|--|-------|----|--------|-------|

Timer3

| Mode | Sub-<br>Mode    | Operation                                                                                                                                                                                                                                                                                                            |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | No Sub-<br>Mode | <b>8-bit Timer with auto-reload</b><br>The timer register TL3 is reloaded with a user-defined 8-bit value in TH3 upon overflow.                                                                                                                                                                                      |

| 3    | а               | <b>Timer3 operates as two 8-bit timers</b><br>The timer registers TL3 and TH3, operate as two separate 8-bit counters.                                                                                                                                                                                               |

| 3    | b               | <b>Timer3 operates as Two 8-bit timers for clock measurement</b><br>The timer registers, TL3 and TH3 operate as two separate 8-bit counters. In this mode the LP_CLK2 Low Power Clock can be measured. TL3 acts as an edge counter for the clock edges and TH3 as a counter which counts the time between the edges. |

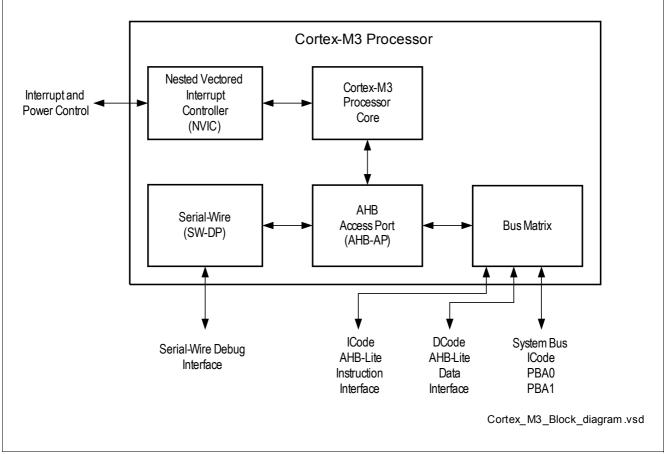

**LIN Transceiver**

## 20.2 Introduction

The LIN Module is a transceiver for the Local Interconnect Network (LIN) compliant to the LIN2.2 standard, backward compatible to LIN1.3, LIN2.0 and LIN2.1. It operates as a bus driver between the protocol controller and the physical network. The LIN bus is a single wire, bi-directional bus typically used for in-vehicle networks, using baud rates between 2.4 kBaud and 20 kBaud. Additionally baud rates up to 115.2 kBaud are implemented.

The LIN Module offers several different operation modes, including a LIN Sleep Mode and the LIN Normal Mode. The integrated slope control allows to use several data transmission rates with optimized EMC performance. For data transfer at the end of line, a Flash Mode up to 115.2 kBaud is implemented. This Flash Mode can be used for data transfer under special conditions for up to 250 kbit/s (in production environment, point-to-point communication with reduced wire length and limited supply voltage).

### VS $\Box$ LIN Transceiver V 30 k LIN\_CTRL\_STS CTRL Driver + TxD\_1 LIN-FSM Curr. Limit. + from UART STATUS TSD GND\_LIN STATUS Transmitter CTRL Filter RxD 1 to UART Receiver Filter LIN\_Wake Sleep Comparator Ó LIN Block Diagram Customer.vsd GND\_LIN

# 20.2.1 Block Diagram

Figure 23 LIN Transceiver Block Diagram

High-Speed Synchronous Serial Interface (SSC1/SSC2)

# 21 High-Speed Synchronous Serial Interface (SSC1/SSC2)

## 21.1 Features

- Master and Slave Mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: Least Significant Bit (LSB) or Most Significant Bit (MSB) shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a "receiver full" condition

- On an error condition (receive, phase, baud rate, transmission error)

# **TLE9879QXA20**

**Application Information**

# 28 Application Information

## 28.1 BLDC Driver

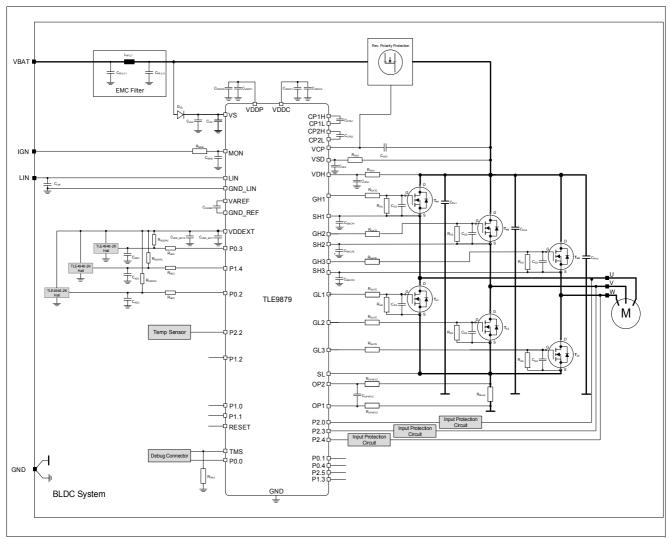

**Figure 32** shows the TLE9879QXA20 in an electric drive application setup controlling a BLDC motor. Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 32 Simplified Application Diagram Example

Note: This is a very simplified example of an application circuit and bill of materials. The function must be verified in the actual application.

**Application Information**

# 28.2 ESD Immunity According to IEC61000-4-2

Note: Tests for ESD immunity according to IEC61000-4-2 "Gun test" (150pF, 330 $\Omega$ ) has been performed. The results and test condition will be available in a test report.

Table 16ESD "Gun Test"

| Performed Test                           | Result | Unit | Remarks                      |

|------------------------------------------|--------|------|------------------------------|

| ESD at pin LIN, versus GND <sup>1)</sup> | > 6    | kV   | <sup>2)</sup> positive pulse |

| ESD at pin LIN, versus GND <sup>1)</sup> | < -6   | kV   | <sup>2)</sup> negative pulse |

1) ESD test "ESD GUN" is specified with external components; see application diagram:

C<sub>MON</sub> = 100 nF, R<sub>MON</sub> = 1 kΩ, C<sub>LIN</sub> = 220 pF, C<sub>VS</sub> = >20 µF ELCO + 100 nF ESR < 1 Ω, C<sub>VSD</sub> = 1 µF, R<sub>VSD</sub> = 2 Ω.

2) ESD susceptibility "ESD GUN" according to LIN EMC Test Specification, Section 4.3 (IEC 61000-4-2). To be tested by external test house (IBEE Zwickau)

# 29.2.5 Power Down Voltage Regulator (PMU Subblock) Parameters

The PMU Power Down voltage regulator consists of two subblocks:

- Power Down Pre regulator: VDD5VPD

- Power Down Core regulator: VDD1V5\_PD (Supply used for GPUDATAxy registers)

Both regulators are used as purely internal supplies. The following table contains all relevant parameters:

### Table 26Functional Range

| Parameter                | Symbol                    | Values |      | Unit | Note / Test Condition | Number |         |

|--------------------------|---------------------------|--------|------|------|-----------------------|--------|---------|

|                          |                           | Min.   | Тур. | Max. |                       |        |         |

| VDD1V5_PD                |                           |        |      |      |                       |        |         |

| Power-On Reset Threshold | $V_{\rm DD1V5_PD_}$ RSTTH | 1.2    | -    | 1.5  | V                     | 1)     | P_2.5.1 |

1) Not subject to production test, specified by design

- 1) The typical oscillator frequency is 5 MHz

- 2)  $V_{\text{DDC}} = 1.5 \text{ V}, T_{\text{j}} = 25^{\circ}\text{C}$

- 3) Not subject to production test, specified by design.

- 4) This parameter is valid for PLL operation with an external clock source and thus reflects the real PLL performance.

# 29.3.2 External Clock Parameters XTAL1, XTAL2

### Table 28Functional Range

$V_{\rm S}$  = 5.5 V to 28 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Parameter                                      | Symbol                |                         | Values |      | Unit | Note /<br>Test Condition              | Number  |

|------------------------------------------------|-----------------------|-------------------------|--------|------|------|---------------------------------------|---------|

|                                                |                       | Min.                    | Тур.   | Max. |      |                                       |         |

| Input voltage range limits for signal on XTAL1 | V <sub>IX1_SR</sub>   | -1.7 + V <sub>DDC</sub> | -      | 1.7  | V    | 2)                                    | P_3.2.1 |

| Input voltage (amplitude) on XTAL1             | V <sub>AX1_SR</sub>   | 0.3 x V <sub>DDC</sub>  | -      | -    | V    | <sup>3)</sup> Peak-to-peak<br>voltage | P_3.2.2 |

| XTAL1 input current                            | $I_{\rm IL}$          | -                       | -      | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$              | P_3.2.3 |

| Oscillator frequency                           | fosc                  | 4                       | -      | 24   | MHz  | Clock signal                          | P_3.2.4 |

| Oscillator frequency                           | fosc                  | 4                       | -      | 16   | MHz  | Crystal or<br>Resonator               | P_3.2.5 |

| High time                                      | <i>t</i> <sub>1</sub> | 6                       | -      | _    | ns   | -                                     | P_3.2.6 |

| Low time                                       | <i>t</i> <sub>2</sub> | 6                       | _      | _    | ns   | -                                     | P_3.2.7 |

| Rise time                                      | t <sub>3</sub>        | -                       | 8      | 8    | ns   | -                                     | P_3.2.8 |

| Fall time                                      | <i>t</i> <sub>4</sub> | _                       | 8      | 8    | ns   | -                                     | P_3.2.9 |

1) This parameter table is not subject to production test, specified by design.

2) Overload conditions must not occur on pin XTAL1.

3) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

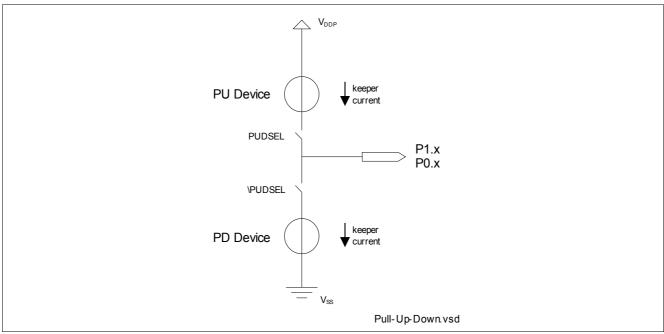

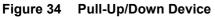

# 29.5 Parallel Ports (GPIO)

# 29.5.1 Description of Keep and Force Current

## Table 31 DC Characteristics Port0, Port1 (cont'd)

$V_{\rm S}$  = 5.5 V to 28 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                   | Symbol                  | Values                 |                            |                        |    | Note /                                                                                                                                                               | Number   |

|-----------------------------|-------------------------|------------------------|----------------------------|------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                             |                         | Min.                   | Тур.                       | Max.                   | 1  | Test Condition                                                                                                                                                       |          |

| Input low voltage           | V <sub>IL</sub>         | -0.3                   | -                          | 0.3 x V <sub>DDP</sub> | V  | $^{2)}4.5V \le V_{DDP} \le$<br>5.5V                                                                                                                                  | P_5.1.3  |

| Input low voltage           | $V_{\rm IL\_extend}$    | -0.3                   | 0.42 x<br>V <sub>DDP</sub> | -                      | V  | <sup>1)</sup> 2.6V ≤ V <sub>DDP</sub> ≤ 4.5V                                                                                                                         | P_5.1.17 |

| Input high voltage          | V <sub>IH</sub>         | 0.7 x V <sub>DDP</sub> | -                          | V <sub>DDP</sub> + 0.3 | V  | $^{2)}4.5V \le V_{DDP} \le 5.5V$                                                                                                                                     | P_5.1.4  |

| Input high voltage          | $V_{\rm IH\_extend}$    | -                      | 0.52 x<br>V <sub>DDP</sub> | V <sub>DDP</sub> + 0.3 | V  | $^{1)}2.6V \le V_{DDP} \le 4.5V$                                                                                                                                     | P_5.1.18 |

| Output low voltage          | V <sub>OL</sub>         | _                      | -                          | 1.0                    | V  | $^{(3) 4)} I_{OL} \leq I_{OLmax}$                                                                                                                                    | P_5.1.6  |

| Output low voltage          | V <sub>OL</sub>         | -                      | -                          | 0.4                    | V  | $^{(3)} S^{(5)} I_{OL} \leq I_{OLnom}$                                                                                                                               | P_5.1.7  |

| Output high voltage         | V <sub>OH</sub>         | V <sub>DDP</sub> - 1.0 | -                          | -                      | V  | $^{(3) 4)}I_{OH} \ge I_{OHmax}$                                                                                                                                      | P_5.1.8  |

| Output high voltage         | V <sub>OH</sub>         | V <sub>DDP</sub> - 0.4 | -                          | -                      | V  | $^{(3)} {}^{(5)} I_{OH} \ge I_{OHnom}$                                                                                                                               | P_5.1.9  |

| Input leakage current       | I <sub>OZ_extend1</sub> | -500                   | _                          | +500                   | nA | $\begin{array}{l} -40^{\circ}\mathrm{C} \leq T_{\mathrm{J}} \\ \leq 25^{\circ}\mathrm{C}, \\ 0.45 \; \mathrm{V} < V_{\mathrm{IN}} \\ < V_{\mathrm{DDP}} \end{array}$ | P_5.1.20 |

| Input leakage current       | I <sub>OZ1</sub>        | -5                     | _                          | +5                     | μA | $^{6)}$ 25°C <<br>$T_{J} \le$ 85°C,<br>0.45 V < $V_{IN}$<br>< $V_{DDP}$                                                                                              | P_5.1.10 |

| Input leakage current       | I <sub>OZ_extend2</sub> | -15                    | -                          | +15                    | μA | $85^{\circ}C < T_{J}$<br>$\leq 150^{\circ}C,$<br>$0.45 V < V_{IN}$<br>$< V_{DDP}$                                                                                    | P_5.1.11 |

| Pull level keep current     | $I_{PLK}$               | -200                   | -                          | +200                   | μA | <sup>7)</sup> $V_{\text{PIN}} ≥ V_{\text{IH}}$ (up)<br>$V_{\text{PIN}} ≤ V_{\text{IL}}$ (dn)                                                                         | P_5.1.12 |

| Pull level force current    | I <sub>PLF</sub>        | -1.5                   | -                          | +1.5                   | mA | <sup>7)</sup> $V_{\text{PIN}} \le V_{\text{IL}}$ (up)<br>$V_{\text{PIN}} \ge V_{\text{IH}}$ (dn)                                                                     | P_5.1.13 |

| Pin capacitance             | C <sub>IO</sub>         | -                      | -                          | 10                     | pF | 1)                                                                                                                                                                   | P_5.1.14 |

| Reset Pin Timing            | •                       |                        | - •                        |                        | +  | •                                                                                                                                                                    | •        |

| Reset Pin Input Filter Time | t <sub>filt_RESET</sub> | -                      | 5                          | -                      | μs | 1)                                                                                                                                                                   | P_5.1.19 |

|                             |                         | · · ·                  | 1                          | 1                      |    | L                                                                                                                                                                    | 1        |

1) Not subject to production test, specified by design.

2) Tested at  $V_{\text{DDP}}$  = 5V, specified for 4.5V <  $V_{\text{DDP}}$  < 5.5V.

3) The maximum deliverable output current of a port driver depends on the selected output driver mode. The limit for pin groups must be respected.

4) Tested at 4.9V <  $V_{\text{DDP}}$  < 5.1V,  $I_{\text{OL}}$  = 4mA,  $I_{\text{OH}}$  = -4mA, specified for 4.5V <  $V_{\text{DDP}}$  < 5.5V.

5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow GND$ ,  $V_{OH} \rightarrow V_{DDP}$ ). Tested at 4.9V <  $V_{DDP}$  < 5.1V,  $I_{OL}$  = 1mA,  $I_{OH}$  = -1mA.

## Table 35 Supply Voltage Signal Conditioning (cont'd)

$V_{\rm S}$  = 5.5 V to 28 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                                 | Values           |              |      | Unit | Note / Test Condition         | Number   |

|--------------------------------------------------------|----------------------------------------|------------------|--------------|------|------|-------------------------------|----------|

|                                                        |                                        | Min.             | n. Typ. Max. |      | 1    |                               |          |

| Charge Pump Voltage Me                                 | asurement V                            | ĊP               |              |      |      |                               |          |

| Input to output voltage attenuation: $V_{CP}$          | ATT <sub>VCP</sub>                     | -                | 0.023        | -    |      | -                             | P_8.1.56 |

| Nominal operating input voltage range $V_{\rm CP}$     | $V_{\rm CP,range}$                     | 2.5              | -            | 52   | V    | 1)                            | P_8.1.7  |

| Accuracy of $V_{CP}$ sense after calibration           | $\Delta V_{CP}$                        | -747             | -            | 747  | mV   | $V_{\rm S}$ = 5.5V to 18V     | P_8.1.62 |

| Monitoring Input Voltage                               | Measurement                            | V <sub>MON</sub> |              | 1    | 1    |                               | 1        |

| Input to output voltage attenuation: $V_{\rm MON}$     | ATT <sub>VMON</sub>                    | -                | 0.039        | -    |      | _                             | P_8.1.49 |

| Nominal operating input voltage range $V_{\rm MON}$    | $V_{\rm MON,range}$                    | 2.5              | -            | 31   | V    | 1)                            | P_8.1.8  |

| Accuracy of $V_{MON}$ sense after calibration          | $\Delta V_{MON}$                       | -440             | -            | 440  | mV   | $V_{\rm S}$ = 5.5V to 18V     | P_8.1.68 |

| Pad Supply Voltage Meas                                | surement $V_{\rm VD}$                  | DP               |              | 1    | 1    |                               | 1        |

| Input-to-output voltage attenuation: $V_{\text{DDP}}$  | ATT <sub>VDDP</sub>                    | -                | 0.164        | -    |      | -                             | P_8.1.33 |

| Nominal operating input voltage range $V_{\text{DDP}}$ | $V_{\rm DDP,range}$                    | 0                | -            | 7.50 | V    | 1)                            | P_8.1.50 |

| Accuracy of $V_{\text{DDP}}$ sense after calibration   | $\Delta V_{\text{DDP}_{\text{SENSE}}}$ | -105             | -            | 105  | mV   | $^{2)}V_{\rm S}$ = 5.5 to 18V | P_8.1.5  |

| 10-Bit ADC Reference Vo                                | ltage Measure                          | ment J           | AREF         | 1    | 1    |                               | 1        |

| Input to output voltage attenuation: $V_{\text{AREF}}$ | ATT <sub>VAREF</sub>                   | -                | 0.219        | -    |      | -                             | P_8.1.22 |

| Nominal operating input voltage range $V_{\sf AREF}$   | $V_{AREF,range}$                       | 0                | -            | 5.62 | V    | 1)                            | P_8.1.51 |

| Accuracy of $V_{\text{AREF}}$ sense after calibration  | $\Delta V_{AREF}$                      | -79              | -            | 79   | mV   | $V_{\rm S}$ = 5.5V to 18V     | P_8.1.48 |

| 8-Bit ADC Reference Volt                               | tage Measuren                          | nent $V_{\rm H}$ | BG           |      |      |                               |          |

| Input-to-output voltage attenuation: $V_{\rm BG}$      | ATT <sub>VBG</sub>                     | -                | 0.75         | -    |      | -                             | P_8.1.57 |

| Nominal operating input voltage range $V_{BG}$         | $V_{\rm BG,range}$                     | 0.8              | -            | 1.64 | V    | 1)                            | P_8.1.52 |

# 29.9 ADC1 Reference Voltage - VAREF

## 29.9.1 Electrical Characteristics VAREF

### Table 39 Electrical Characteristics VAREF

$V_{\rm S}$  = 5.5 V to 28 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol                | Values |      |      | Unit | Note / Test Condition                                                         | Number   |

|----------------------------------|-----------------------|--------|------|------|------|-------------------------------------------------------------------------------|----------|

|                                  |                       | Min.   | Тур. | Max. |      |                                                                               |          |

| Required buffer capacitance      | $C_{VAREF}$           | 0.1    | -    | 1    | μF   | ESR < 1Ω                                                                      | P_9.1.1  |

| Reference output voltage         | $V_{AREF}$            | 4.95   | 5    | 5.05 | V    | V <sub>S</sub> > 5.5V                                                         | P_9.1.2  |

| DC supply voltage rejection      | $DC_{PSRVAREF}$       | 30     | -    | -    | dB   | 1)                                                                            | P_9.1.3  |

| Supply voltage ripple rejection  | $AC_{PSRVAREF}$       | 26     | -    | -    | dB   | <sup>1)</sup> $V_{\rm S}$ = 13.5V; $f$ = 0 1KHz;<br>$V_{\rm r}$ = 2Vpp        | P_9.1.4  |

| Turn ON time                     | t <sub>so</sub>       | -      | -    | 200  | μs   | <sup>1)</sup> $C_{\text{ext}}$ = 100nF<br>PD_N to 99.9% of final value        | P_9.1.5  |

| Input resistance at VAREF<br>Pin | R <sub>IN,VAREF</sub> | -      | 100  | -    | kΩ   | <sup>1)</sup> input impedance in case of<br>VAREF is applied from<br>external | P_9.1.20 |

1) Not subject to production test, specified by design.

## Table 42 Electrical Characteristics MOSFET Driver (cont'd)

$V_{\rm S}$  = 5.5 V to 28 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol                 | Values |      |      | Unit | Note / Test Condition                                                                                                                                                                                                                       | Number    |

|--------------------------------------------|------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                            |                        | Min.   | Тур. | Max. |      |                                                                                                                                                                                                                                             |           |

| Resistor between SHx and GND               | R <sub>SHGN</sub>      | 30     | 40   | 50   | kΩ   | <sup>1)3)</sup> This resistance is the<br>resistance between GHx<br>and GND connected<br>through a diode to SHx. As<br>a consequence, the<br>voltage at SHx can rise up<br>to 0,6V typ. before it is<br>discharged through the<br>resistor. | P_12.1.10 |

| Low RDSON mode<br>(boosted discharge mode) | R <sub>onccp</sub>     | _      | 9    | 12   | Ω    | $V_{\text{VSD}}$ = 13.5 V,<br>$V_{\text{VCP}}$ = $V_{\text{VSD}}$ + 14.0 V;<br>$I_{\text{CHARGE}}$ = $I_{\text{DISCHG}}$ =<br>31(max); 50mA forced into<br>Gx, Sx grounded                                                                  | P_12.1.50 |

| Resistance between VDH and VSD             | I <sub>BSH</sub>       | -      | 4    | -    | kΩ   | 1)                                                                                                                                                                                                                                          | P_12.1.24 |

| Input propagation time (LS on)             | t <sub>P(ILN)min</sub> | -      | 1.5  | 3    | μs   | $^{1)}C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Charge}}$ =3(min),<br>25% of $V_{\text{Gxx1}}$                                                                                                                                                 | P_12.1.37 |

| Input propagation time (LS off)            | t <sub>P(ILF)min</sub> | -      | 1.5  | 3    | μs   | $^{1)}C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Discharge}}$ =3(min),<br>75% of $V_{\text{Gxx1}}$                                                                                                                                              | P_12.1.38 |

| Input propagation time (HS on)             | t <sub>P(IHN)min</sub> | -      | 1.5  | 3    | μs   | $^{1)}C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Charge}}$ =3(min)<br>25% of $V_{\text{Gxx1}}$                                                                                                                                                  | P_12.1.39 |

| Input propagation time (HS off)            | t <sub>P(IHF)min</sub> | -      | 1.5  | 3    | μs   | $^{1)}C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Disharge}}$ =3(min),<br>75% of $V_{\text{Gxx1}}$                                                                                                                                               | P_12.1.40 |

| Input propagation time (LS on)             | t <sub>P(ILN)max</sub> | -      | 200  | 350  | ns   | $C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Charge}}$ =31(max),<br>25% of $V_{\text{Gxx1}}$                                                                                                                                                     | P_12.1.26 |

| Input propagation time (LS off)            | t <sub>P(ILF)max</sub> | -      | 200  | 300  | ns   | $C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Discharge}}$ =31(max),<br>75% of $V_{\text{Gxx1}}$                                                                                                                                                  | P_12.1.27 |

| Input propagation time (HS on)             | t <sub>P(IHN)max</sub> | -      | 200  | 350  | ns   | $C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Charge}}$ =31(max),<br>25% of $V_{\text{Gxx1}}$                                                                                                                                                     | P_12.1.28 |

| Input propagation time (HS off)            | t <sub>P(IHF)max</sub> | -      | 200  | 300  | ns   | $C_{\text{Load}}$ = 10 nF,<br>$I_{\text{Discharge}}$ =31(max),<br>75% of $V_{\text{Gxx1}}$                                                                                                                                                  | P_12.1.29 |

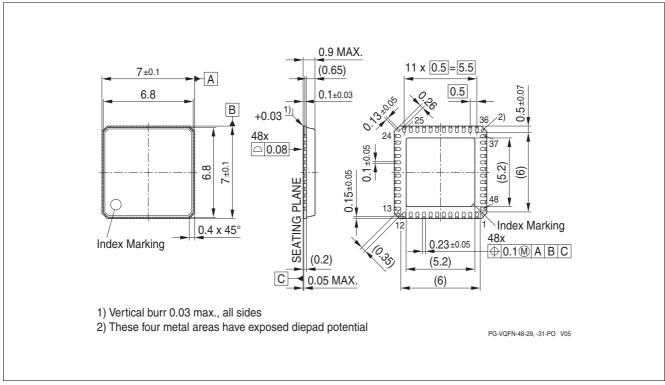

Package Outlines

# 30 Package Outlines

Figure 38 Package outline VQFN-48-31 (with LTI)

## Notes

- 1. You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

- 2. Dimensions in mm.