Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

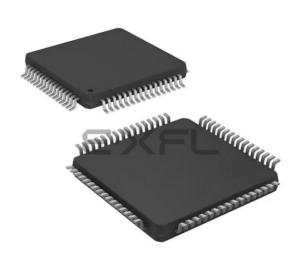

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | LCD, POR, PWM, WDT                                                        |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c923-04-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16C9XX DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C9XX Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C9XX family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**924. These devices have EPROM type memory and operate over the standard voltage range.

- 2. **LC**, as in PIC16**LC**924. These devices have EPROM type memory and operate over an extended voltage range.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERQUAD package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support the PIC16C9XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

## 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

## TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address            | Name    | Bit 7         | Bit 6               | Bit 5                   | Bit 4          | Bit 3        | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|---------------|---------------------|-------------------------|----------------|--------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 1             | ·       | •             |                     |                         |                |              | ·                |                |          | •                             |                           |

| 80h                | INDF    | Addressing    | this location       | uses conten             | ts of FSR to   | address data | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 81h                | OPTION  | RBPU          | INTEDG              | TOCS                    | T0SE           | PSA          | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 82h                | PCL     | Program Co    | ounter's (PC)       | Least Signif            | icant Byte     |              |                  |                |          | 0000 0000                     | 0000 0000                 |

| 83h                | STATUS  | IRP           | RP1                 | RP0                     | TO             | PD           | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 84h                | FSR     | Indirect data | a memory ad         | dress pointe            | r              |              |                  |                |          | XXXX XXXX                     | uuuu uuuu                 |

| 85h                | TRISA   | —             | _                   | PORTA Dat               | a Direction R  | egister      |                  |                |          | 11 1111                       | 11 1111                   |

| 86h                | TRISB   | PORTB Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 87h                | TRISC   | —             | _                   | PORTC Da                | ta Direction F | Register     |                  |                |          | 11 1111                       | 11 1111                   |

| 88h                | TRISD   | PORTD Dat     | a Direction F       | Register                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 89h                | TRISE   | PORTE Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 8Ah                | PCLATH  | —             | _                   | —                       | Write Buffer   | for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 8Bh                | INTCON  | GIE           | PEIE                | T0IE                    | INTE           | RBIE         | T0IF             | INTF           | RBIF     | 0000 000x                     | 0000 000u                 |

| 8Ch                | PIE1    | LCDIE         | ADIE <sup>(2)</sup> | —                       | _              | SSPIE        | CCP1IE           | TMR2IE         | TMR1IE   | 00 0000                       | 00 0000                   |

| 8Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 8Eh                | PCON    | —             | _                   | —                       | _              | _            | _                | POR            | —        | 0-                            | u-                        |

| 8Fh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 90h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | —                             | —                         |

| 91h                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 92h                | PR2     | Timer2 Peri   | od Register         |                         |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 93h                | SSPADD  | Synchronou    | is Serial Port      | (I <sup>2</sup> C mode) | Address Reg    | ister        |                  |                |          | 0000 0000                     | 0000 0000                 |

| 94h                | SSPSTAT | SMP           | CKE                 | D/Ā                     | Р              | S            | R/W              | UA             | BF       | 0000 0000                     | 0000 0000                 |

| 95h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 96h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 97h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 98h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 99h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 9Ah                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 9Bh                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | -                             | —                         |

| 9Ch                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | -                             | —                         |

| 9Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | —                             | —                         |

| 9Eh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 9Fh <sup>(1)</sup> | ADCON1  |               | —                   | _                       |                | _            | PCFG2            | PCFG1          | PCFG0    | 000                           | 000                       |

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0',

Note

shaded locations are unimplemented, read as '0'. 1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

These bits are reserved on the PIC16C923, always maintain these bits clear.

These pixels do not display, but can be used as general purpose RAM.

PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

## 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and external RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## FIGURE 4-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0       | R/W-0                                                                                                                                                                                                                                                                       | R/W-0      | R/W-0     | R/W-0                                    | R/W-0 | R/W-0 | R/W-x        |                                                                                                           |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|------------------------------------------|-------|-------|--------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                                                                                        | TOIE       | INTE      | RBIE                                     | TOIF  | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |

| bit 7:      |                                                                                                                                                                                                                                                                             |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 6:      | <ul> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all un-masked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul>                                                                                                          |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 5:      | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                                                                                                       |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 4:      | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                                                                                                    |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 3:      | 1 = Enabl                                                                                                                                                                                                                                                                   | les the RE | port char | upt Enable<br>nge interru<br>nge interru | pt    |       |              |                                                                                                           |  |  |  |

| bit 2:      | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                      |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 1:      |                                                                                                                                                                                                                                                                             |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| bit 0:      | <ul> <li>RBIF: RB Port Change Interrupt Flag bit</li> <li>1 = At least one of the RB7:RB4 pins changed state (see Section 5.2 to clear interrupt)</li> <li>0 = None of the RB7:RB4 pins have changed state</li> </ul>                                                       |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

| globa       | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. |            |           |                                          |       |       |              |                                                                                                           |  |  |  |

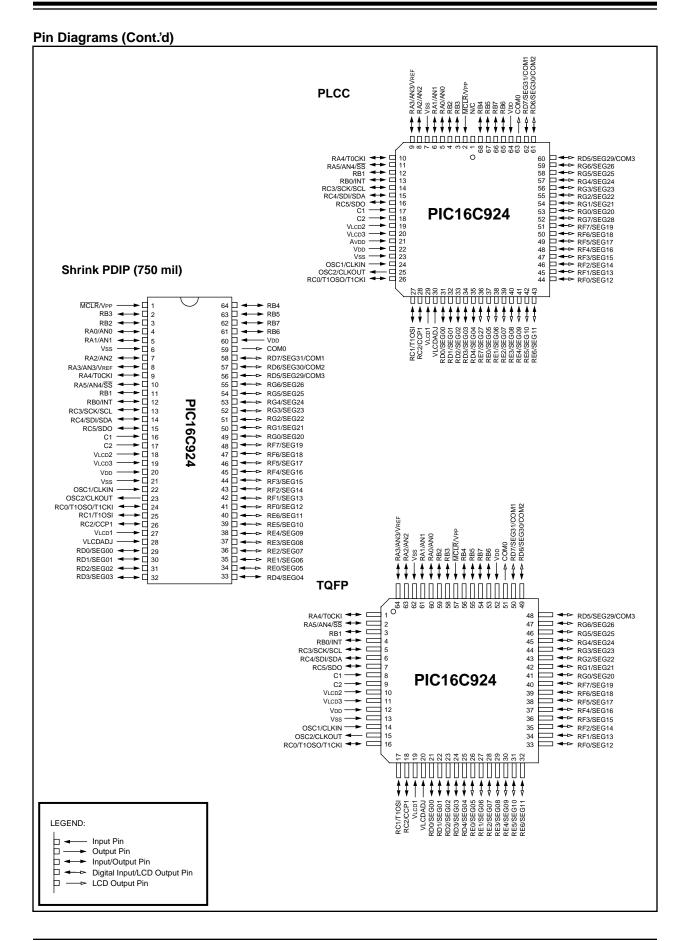

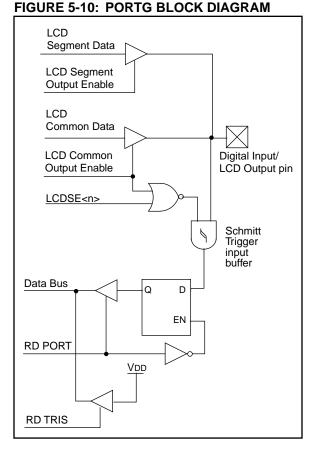

## 5.7 PORTG and TRISG Register

PORTG is an digital input only port. Each pin is multiplexed with an LCD segment driver. These pins have Schmitt Trigger input buffers.

- Note 1: On a Power-on Reset these pins are configured as LCD segment drivers.

- Note 2: To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

## EXAMPLE 5-7: INITIALIZING PORTG

BCF STATUS,RP0 ;Select Bank2 BSF STATUS,RP1 ; BCF LCDSE,SE27 ;Make all PORTG BCF LCDSE,SE20 ;and PORTE<7> ;digital inputs

## TABLE 5-13: PORTG FUNCTIONS

| Bit# | Buffer Type                                          | Function                                                            |  |  |  |  |  |

|------|------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| bit0 | ST                                                   | Digital input or Segment Driver20                                   |  |  |  |  |  |

| bit1 | ST                                                   | Digital input or Segment Driver21                                   |  |  |  |  |  |

| bit2 | ST                                                   | Digital input or Segment Driver22                                   |  |  |  |  |  |

| bit3 | ST                                                   | Digital input or Segment Driver23                                   |  |  |  |  |  |

| bit4 | ST                                                   | Digital input or Segment Driver24                                   |  |  |  |  |  |

| bit5 | ST                                                   | Digital input or Segment Driver25                                   |  |  |  |  |  |

| bit6 | ST                                                   | Digital input or Segment Driver26                                   |  |  |  |  |  |

| bit7 | ST                                                   | Digital input or Segment Driver28 (not available on 64-pin devices) |  |  |  |  |  |

|      | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6 | bit0STbit1STbit2STbit3STbit4STbit5STbit6ST                          |  |  |  |  |  |

Legend: ST = Schmitt Trigger input

## TABLE 5-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

| Address | Name  | Bit 7 | Bit 6                                                                                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------|

| 108h    | PORTG | RG7   | RG6                                                                                          | RG5   | RG4   | RG3   | RG2   | RG1   | RG0   | 0000 0000                     | 0000 0000                 |

| 188h    | TRISG | PORTG | ORTG Data Direction Control Register                                                         |       |       |       |       |       |       | 1111 1111                     | 1111 1111                 |

| 10Dh    | LCDSE | SE29  | SE29         SE27         SE20         SE16         SE12         SE9         SE5         SE0 |       |       |       |       |       |       | 1111 1111                     | 1111 1111                 |

Legend: Shaded cells are not used by PORTG.

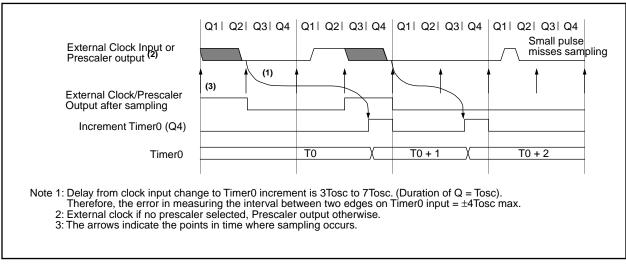

## 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

## 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

## 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

## FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

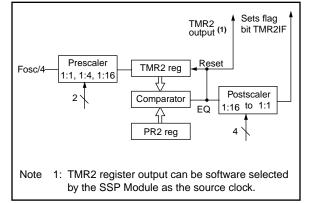

## 9.0 TIMER2 MODULE

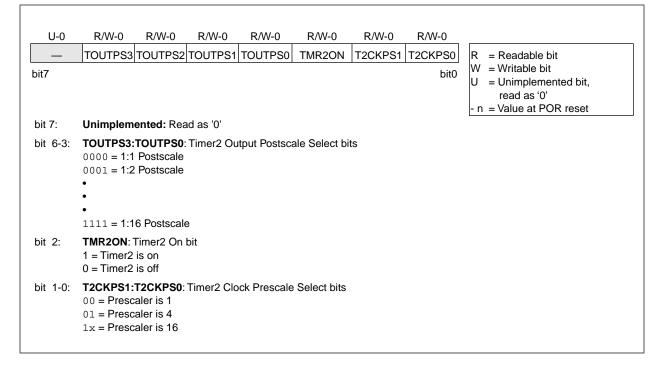

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16 (selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>)).

The Timer2 module has an 8-bit period register, PR2. TMR2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is set during RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register.

## 9.1 <u>Timer2 Prescaler and Postscaler</u>

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR Reset, or Watchdog Timer Reset)

TMR2 will not clear when T2CON is written.

## 9.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

| FIGURE 9-1: | TIMER2 BL | OCK DIAGRAM |

|-------------|-----------|-------------|

|             |           |             |

## FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

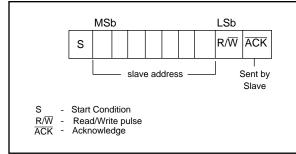

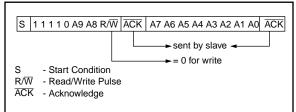

## 11.2.2 ADDRESSING I<sup>2</sup>C DEVICES

There are two address formats. The simplest is the 7-bit address format with a R/W bit (Figure 11-9). The more complex is the 10-bit address with a R/W bit (Figure 11-10). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

FIGURE 11-9: 7-BIT ADDRESS FORMAT

FIGURE 11-10: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

## 11.2.3 TRANSFER ACKNOWLEDGE

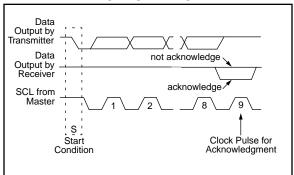

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-11). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-8).

#### FIGURE 11-11: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

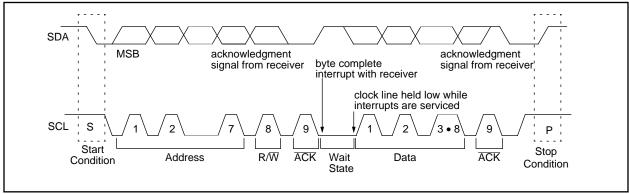

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-12. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

## FIGURE 11-12: DATA TRANSFER WAIT STATE

٦

## 11.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 11-19: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W=0         Receiving Data         ACK         Receiving Data           SDA           AT_XA6_XA5_XA4_XA3_XA2_XA1        ACK_D7_XD6_XD5_XD4_XD3_XD2_XD1_XD0 |                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                            | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u><br>Bit SSPOV is set because the SSPBUF register is still full.<br>ACK is not sent                                                                      |                                      |

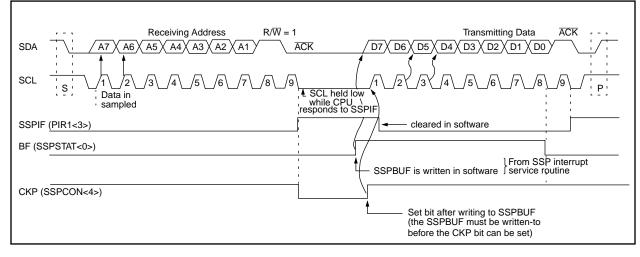

## 11.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-20). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

## FIGURE 11-20: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

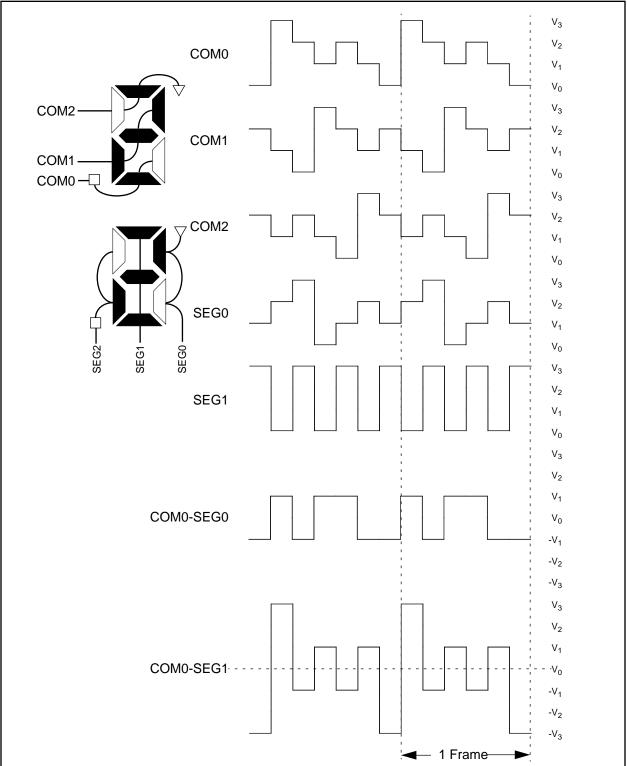

## 13.3 Pixel Control

## 13.3.1 LCDD (PIXEL DATA) REGISTERS

The pixel registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Table 13-4 shows the correlation of each bit in the LCDD registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

## FIGURE 13-10:GENERIC LCDD REGISTER LAYOUT

| R/W-x                                                                                                                | R/W-x        | R/W-x        | R/W-x        | R/W-x        | R/W-x        | R/W-x        | R/W-x        |                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------------------------------------|--|--|

| SEGs<br>COMc                                                                                                         | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | R =Readable bit<br>W =Writable bit |  |  |

| bit7 bit0 U =Unimplemented bit,<br>Read as '0'                                                                       |              |              |              |              |              |              |              |                                    |  |  |

| bit 7-0: <b>SEGsCOMc</b> : Pixel Data Bit for segment s and common c<br>1 = Pixel on (dark)<br>0 = Pixel off (clear) |              |              |              |              |              |              |              |                                    |  |  |

## 13.4.1 SEGMENT ENABLES

The LCDSE register is used to select the pin function for groups of pins. The selection allows each group of pins to operate as either LCD drivers or digital only pins. To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared.

If the pin is a digital I/O the corresponding TRIS bit controls the data direction. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

- **Note 1:** On a Power-on Reset these pins are configured as LCD drivers.

- Note 2: The LMUX1:LMUX0 takes precedence over the LCDSE bit settings for pins RD7, RD6 and RD5.

## EXAMPLE 13-1: STATIC MUX WITH 32 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2          |

|-------|--------------|-------------------------|

| BSF   | STATUS, RP1  | ;                       |

| BCF   | LCDCON,LMUX1 | ;Select Static MUX      |

| BCF   | LCDCON,LMUX0 | ;                       |

| MOVLW | OxFF         | ;Make PortD,E,F,G       |

| MOVWF | LCDSE        | ;LCD pins               |

|       |              | ; configure rest of LCD |

## EXAMPLE 13-2: 1/3 MUX WITH 13 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2                             |

|-------|--------------|--------------------------------------------|

| BSF   | STATUS, RP1  | ;                                          |

| BSF   | LCDCON,LMUX1 | ;Select 1/3 MUX                            |

| BCF   | LCDCON,LMUX0 | ;                                          |

| MOVLW | 0x87         | ;Make PORTD<7:0> &                         |

| MOVWF | LCDSE        | ;PORTE<6:0> LCD pins                       |

|       |              | ;configure rest of LCD                     |

| MOVLW | 0x87         | ;Make PORTD<7:0> &<br>;PORTE<6:0> LCD pins |

## FIGURE 13-12:LCDSE REGISTER (ADDRESS 10Dh)

| R/W-1  | R/W-1                                                                                              | R/W-1         | R/W-1       | R/W-1    | R/W-1    | R/W-1 | R/W-1        |                                    |  |  |

|--------|----------------------------------------------------------------------------------------------------|---------------|-------------|----------|----------|-------|--------------|------------------------------------|--|--|

| SE29   | SE27                                                                                               | SE20          | SE16        | SE12     | SE9      | SE5   | SE0          | R =Readable bit<br>W =Writable bit |  |  |

| bit7   |                                                                                                    |               |             |          |          |       | bit0         | U = Unimplemented bit,             |  |  |

|        |                                                                                                    |               |             |          |          |       |              | Read as '0'                        |  |  |

| bit 7: | <b>SE29</b> : Pin f                                                                                | unation and   | laat DD7    |          |          |       | /8F.000      | -n =Value at POR reset             |  |  |

| DIL 7. | 1 = pins har                                                                                       |               |             |          | EG31 - K |       | /3EG29       |                                    |  |  |

|        | 0 = pins har                                                                                       | ve digital Ir | nput functi | on       |          |       |              |                                    |  |  |

|        | The LMUX?                                                                                          |               |             |          |          |       | SE register. |                                    |  |  |

| bit 6: | <b>SE27</b> : Pin f<br>1 = pins hav                                                                |               |             |          | and RE7/ | SEG27 |              |                                    |  |  |

|        | 0 = pins has                                                                                       |               |             |          |          |       |              |                                    |  |  |

| bit 5: | SE20: Pin f                                                                                        | unction se    | lect RG6    | SEG26 ·  | - RG0/SE | G20   |              |                                    |  |  |

|        | 1 = pins ha                                                                                        |               |             |          |          |       |              |                                    |  |  |

|        | 0 = pins ha                                                                                        | •             | •           |          |          |       |              |                                    |  |  |

| bit 4: | <b>SE16</b> : Pin f<br>1 = pins ha                                                                 |               |             |          | RF4/SEC  | 516   |              |                                    |  |  |

|        | 0 = pins ha                                                                                        |               |             |          |          |       |              |                                    |  |  |

| bit 3: | SE12: Pin f                                                                                        | unction se    | lect RF3    | /SEG15 - | RF0/SEC  | G12   |              |                                    |  |  |

|        | 1 = pins har                                                                                       |               |             |          |          |       |              |                                    |  |  |

|        | 0 = pins har                                                                                       | •             | •           |          |          | 200   |              |                                    |  |  |

| bit 2: | <b>SE9</b> : Pin f<br>1 = pins ha                                                                  |               |             |          | RE4/SE   | 309   |              |                                    |  |  |

|        | 0 = pins har                                                                                       |               |             |          |          |       |              |                                    |  |  |

| bit 1: | SE5: Pin f                                                                                         |               |             |          | RE0/SE   | G05   |              |                                    |  |  |

|        | <ul> <li>1 = pins have LCD drive function</li> <li>0 = pins have digital Input function</li> </ul> |               |             |          |          |       |              |                                    |  |  |

| bit 0: | <b>SE0</b> : Pin f                                                                                 | •             | •           |          |          | 600   |              |                                    |  |  |

| DIL U. | 1 = pins har                                                                                       |               |             |          |          | 600   |              |                                    |  |  |

|        | 0 = pins ha                                                                                        |               |             |          |          |       |              |                                    |  |  |

|        |                                                                                                    |               |             |          |          |       |              |                                    |  |  |

| Register               | Applicable Devices |     | Power-on Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|------------------------|--------------------|-----|----------------|--------------------------|------------------------------------|

| LCDSE                  | 923                | 924 | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| LCDPS                  | 923                | 924 | 0000           | 0000                     | uuuu                               |

| LCDCON                 | 923                | 924 | 00-0 0000      | 00-0 0000                | uu-u uuuu                          |

| LCDD00<br>to<br>LCDD15 | 923                | 924 | XXXX XXXX      | นนนน นนนน                | սսսս սսսս                          |

| TRISF                  | 923                | 924 | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| TRISG                  | 923                | 924 | 1111 1111      | 1111 1111                | นนนน นนนน                          |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-5 for reset value for specific condition.

4: Bits PIE1<6> and PIR1<6> are reserved on the PIC16C923, always maintain these bits clear.

5: PORTA values when read.

# **17.0 ELECTRICAL CHARACTERISTICS**

| Absolute Maximum Ratings †                                                                                |                                      |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                            | 55°C to +125°C                       |

| Storage temperature                                                                                       | 65°C to +150°C                       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                        | 0.3V to (VDD + 0.3V)                 |

| Voltage on VDD with respect to Vss                                                                        | 0.3V to +7.5V                        |

| Voltage on MCLR with respect to Vss                                                                       | 0V to +14V                           |

| Voltage on RA4 with respect to Vss                                                                        | 0V to +14V                           |

| Total power dissipation (Note 1)                                                                          | 1.0W                                 |

| Maximum current out of Vss pin                                                                            | 300 mA                               |

| Maximum current into Vod pin                                                                              | 250 mA                               |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                              | ±20 mA                               |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                            | ±20 mA                               |

| Maximum output current sunk by any I/O pin                                                                | 10 mA                                |

| Maximum output current sourced by any I/O pin                                                             | 10 mA                                |

| Maximum current sunk by all Ports combined                                                                | 200 mA                               |

| Maximum current sourced by all Ports combined                                                             | 200 mA                               |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | - VOH) x IOH} + $\Sigma$ (VOI x IOL) |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C923-04<br>PIC16C924-04                                                                                                                                            | PIC16C923-08<br>PIC16C924-08                                                                                                                     | PIC16LC923-04<br>PIC16LC924-04                                                                                                                 | CL Devices                                                                                                                                       |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD:         4.0V to 6.0V           IDD:         5 mA max. at 5.5V           IPD:         21 μA max. at 4V           Freq:         4 MHz max.                           | VDD:         4.5V to 5.5V           IDD:         2.7 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4V           Freq:         4 MHz max. | VDD:         2.5V to 6.0V           IDD:         3.8 mA max. at 3.0V           IPD:         5 μA max. at 3V           Freq:         4 MHz max. | VDD:         2.5V to 6.0V           IDD:         5 mA max. at 5.5V           IPD:         21 μA max. at 4V           Freq:         4 MHz max.    |

| хт  | VDD:         4.0V to 6.0V           IDD:         5 mA max. at 5.5V           IPD:         21 μA max. at 4V           Freq:         4 MHz max.                           | VDD:         4.5V to 5.5V           IDD:         2.7 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4V           Freq:         4 MHz max. | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                                                      | VDD: 2.5V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                         |

| HS  | VDD:         4.5V to 5.5V           IDD:         3.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max.                      | VDD:         4.5V to 5.5V           IDD:         7 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         8 MHz max. | Do not use in HS mode                                                                                                                          | VDD:         4.5V to 5.5V           IDD:         7 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         8 MHz max. |

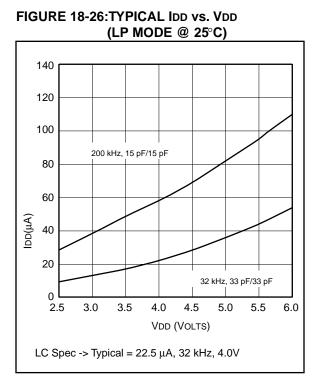

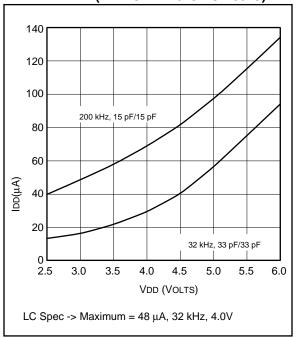

| LP  | VDD:         4.0V to 6.0V           IDD:         22.5 μA typ.           at 32 kHz, 4.0V           IPD:         1.5 μA typ. at 4.0V           Freq:         200 kHz max. | Do not use in LP mode                                                                                                                            | VDD: 2.5V to 6.0V<br>IDD: 30 μA max. at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max.                                           | VDD: 2.5V to 6.0V<br>IDD: 30 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max.                                          |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

## 17.1 DC Characteristics:

## PIC16C923/924-04 (Commercial, Industrial) PIC16C923/924-08 (Commercial, Industrial)

| DC | <b>CHARACTERISTICS</b> |  |

|----|------------------------|--|

|    |                        |  |

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C \leq TA \leq +85^{\circ}C$  for industrial and

$0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

| Param<br>No.  | Characteristic                                                   | Sym     | Min        | Тур† | Max        | Units  | Conditions                                                              |

|---------------|------------------------------------------------------------------|---------|------------|------|------------|--------|-------------------------------------------------------------------------|

| D001<br>D001A | Supply Voltage                                                   | Vdd     | 4.0<br>4.5 |      | 6.0<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                 |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | Vdr     | -          | 1.5  | -          | V      |                                                                         |

| D003          | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | VPOR    | -          | Vss  | -          | V      | See Power-on Reset section for details                                  |

| D004*         | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | SVDD    | 0.05       | -    | -          | V/ms   | (Note 6) See Power-on Reset section for details                         |

| D010          | Supply Current (Note 2)                                          | Idd     | -          | 2.7  | 5          | mA     | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)        |

| D011          |                                                                  |         | -          | 22.5 | 48         | μA     | LP osc configuration,<br>Fosc = $32 \text{ kHz}$ , VDD = $4.0 \text{V}$ |

| D012          |                                                                  |         | -          | 3.5  | 7          | mA     | HS osc configuration<br>Fosc = 8 MHz, VDD = 5.5V                        |

| D020          | Power-down Current<br>(Note 3)                                   | IPD     | -          | 1.5  | 21         | μΑ     | VDD = 4.0V                                                              |

|               | Module Differential Cur-<br>rent (Note 5)                        |         |            |      |            |        |                                                                         |

| D021          | Watchdog Timer                                                   | ∆IWDT   | -          | 6.0  | 20         | μA     | VDD = 4.0V                                                              |

| D022*         | LCD Voltage Generation<br>w/internal RC osc<br>enabled           | ∆ILCDRC | -          | 40   | 55         | μA     | VDD = 4.0V (Note 7)                                                     |

| D024*         | LCD Voltage Generation<br>w/Timer1 @ 32.768 kHz                  | ∆ILCDT1 | -          | 33   | 60         | μA     | VDD = 4.0V (Note 7)                                                     |

| D025*         | Timer1 oscillator                                                | ∆IT1osc | -          | 10.6 | 17         | μA     | VDD = 4.0V                                                              |

| D026*         | A/D Converter                                                    | ΔIAD    | -          | 1.0  | -          | μA     | A/D on, not converting                                                  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: PWRT must be enabled for slow ramps.

7:  $\Delta$ ILCDT1 and  $\Delta$ ILCDRC includes the current consumed by the LCD Module and the voltage generation circuitry. This does not include current dissipated by the LCD panel.

## TABLE 17-12:A/D CONVERTER CHARACTERISTICS: PIC16C924-04 (COMMERCIAL, INDUSTRIAL) PIC16LC924-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym                                  | Characteristic                                 |                     | Min       | Тур†       | Мах        | Units                                                                                                       | Conditions                                                                                   |

|--------------|--------------------------------------|------------------------------------------------|---------------------|-----------|------------|------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| A01          | NR                                   | Resolution                                     | -                   | _         | 8-bits     | bit        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |                                                                                              |

| A02          | EABS                                 | Total Absolute error                           |                     | _         | —          | <±1        | LSb                                                                                                         | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A03          | EIL                                  | Integral linearity error                       |                     | _         | —          | <±1        | LSb                                                                                                         | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A04          | EDL                                  | Differential linearity error                   |                     | _         | _          | <±1        | LSb                                                                                                         | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A05          | EFS                                  | Full scale error                               |                     | _         | _          | <±1        | LSb                                                                                                         | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A06          | EOFF                                 | Offset error                                   |                     | -         | _          | <±1        | LSb                                                                                                         | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A10          | —                                    | Monotonicity                                   |                     |           | guaranteed | —          | —                                                                                                           | $VSS \leq VAIN \leq VREF$                                                                    |

| A20          | Vref                                 | Reference voltage                              |                     | 3.0V      | —          | Vdd + 0.3  | V                                                                                                           |                                                                                              |

| A25          | VAIN                                 | Analog input voltage                           |                     | Vss - 0.3 | —          | Vref + 0.3 | V                                                                                                           |                                                                                              |

| A30          | ZAIN                                 | Recommended impedance of analog voltage source |                     | _         | _          | 10.0       | kΩ                                                                                                          |                                                                                              |

| A40          | IAD                                  | A/D conversion current                         | PIC16 <b>C</b> 924  | _         | 180        | —          | μΑ                                                                                                          | Average current consump-                                                                     |

|              |                                      | (VDD)                                          | PIC16 <b>LC</b> 924 | -         | 90         | —          | μΑ                                                                                                          | tion when A/D is on.<br>(Note 1)                                                             |

| A50          | A50 IREF VREF input current (Note 2) |                                                | 10                  | _         | 1000       | μA         | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 12.1. |                                                                                              |

|              |                                      |                                                |                     | _         | —          | 10         | μA                                                                                                          | During A/D Conversion cycle                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

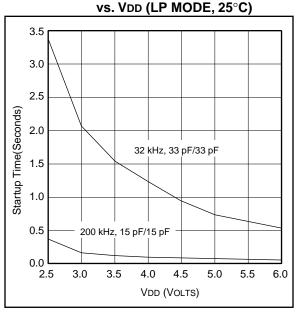

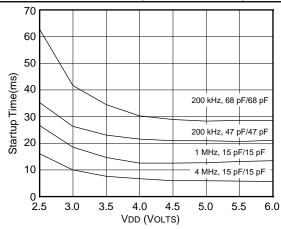

FIGURE 18-23: TYPICAL XTAL STARTUP TIME

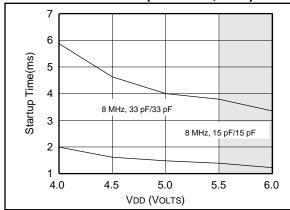

FIGURE 18-24:TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

FIGURE 18-25:TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

FIGURE 18-27:MAXIMUM IDD vs. VDD (LP MODE -40°C TO +85°C)

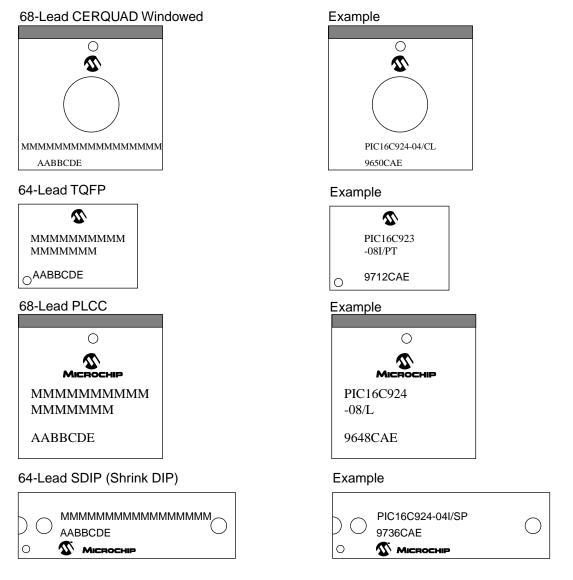

## 19.4 Package Marking Information

| Legend: | MMM<br>XXX<br>AA<br>BB<br>C                                                                                                                                                                                  | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calender year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A. |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | D1                                                                                                                                                                                                           | S = Tempe, Arizona, U.S.A.<br>Mask revision number for microcontroller                                                                                                                                                                                         |  |  |

|         | E                                                                                                                                                                                                            | Assembly code of the plant or country of origin in which part was assembled.                                                                                                                                                                                   |  |  |

| Note:   | In the event the full Microchip part number cannot be marked on one<br>line, it will be carried over to the next line thus limiting the number of<br>available characters for customer specific information. |                                                                                                                                                                                                                                                                |  |  |

|         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |  |  |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.