Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | LCD, POR, PWM, WDT                                                        |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c924-04-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

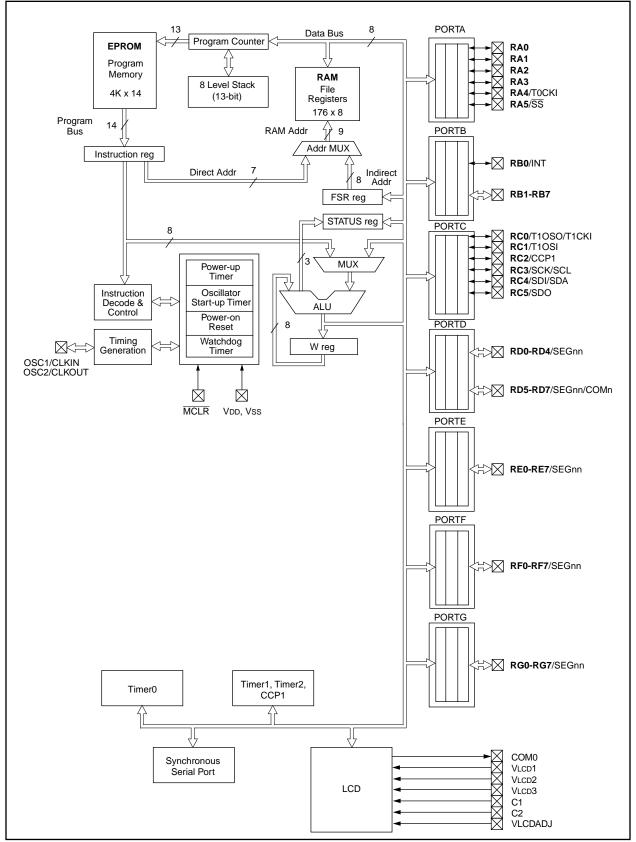

## FIGURE 3-1: PIC16C923 BLOCK DIAGRAM

## TABLE 3-1: PIC16C9XX PINOUT DESCRIPTION

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                       |

|-------------------|-------------|--------------|--------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 22          | 24           | 14           | I           | ST/CMOS        | Oscillator crystal input or external clock source input. This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.                                                 |

| OSC2/CLKOUT       | 23          | 25           | 15           | 0           | _              | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/VPP          | 1           | 2            | 57           | I/P         | ST             | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                                        |

|                   |             |              |              |             |                | PORTA is a bi-directional I/O port. The AN and VREF multi-<br>plexed functions are used by the PIC16C924 only.                                                                                                    |

| RA0/AN0           | 4           | 5            | 60           | I/O         | TTL            | RA0 can also be Analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 5           | 6            | 61           | I/O         | TTL            | RA1 can also be Analog input1.                                                                                                                                                                                    |

| RA2/AN2           | 7           | 8            | 63           | I/O         | TTL            | RA2 can also be Analog input2.                                                                                                                                                                                    |

| RA3/AN3/Vref      | 8           | 9            | 64           | I/O         | TTL            | RA3 can also be Analog input3 or A/D Voltage Reference.                                                                                                                                                           |

| RA4/T0CKI         | 9           | 10           | 1            | I/O         | ST             | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                           |

| RA5/AN4/SS        | 10          | 11           | 2            | I/O         | TTL            | RA5 can be the slave select for the synchronous serial port or Analog input4.                                                                                                                                     |

|                   |             |              |              |             |                | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                                                                                    |

| RB0/INT           | 12          | 13           | 4            | I/O         | TTL/ST         | RB0 can also be the external interrupt pin. This buffer<br>is a Schmitt Trigger input when configured as an exter-<br>nal interrupt.                                                                              |

| RB1               | 11          | 12           | 3            | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB2               | 3           | 4            | 59           | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB3               | 2           | 3            | 58           | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB4               | 64          | 68           | 56           | I/O         | TTL            | Interrupt on change pin.                                                                                                                                                                                          |

| RB5               | 63          | 67           | 55           | I/O         | TTL            | Interrupt on change pin.                                                                                                                                                                                          |

| RB6               | 61          | 65           | 53           | I/O         | TTL/ST         | Interrupt on change pin. Serial programming clock.<br>This buffer is a Schmitt Trigger input when used in<br>serial programming mode.                                                                             |

| RB7               | 62          | 66           | 54           | I/O         | TTL/ST         | Interrupt on change pin. Serial programming data<br>This buffer is a Schmitt Trigger input when used in<br>serial programming mode.                                                                               |

|                   |             |              |              |             |                | PORTC is a bi-directional I/O port.                                                                                                                                                                               |

| RC0/T1OSO/T1CKI   | 24          | 26           | 16           | I/O         | ST             | RC0 can also be the Timer1 oscillator output or<br>Timer1 clock input.                                                                                                                                            |

| RC1/T1OSI         | 25          | 27           | 17           | I/O         | ST             | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                      |

| RC2/CCP1          | 26          | 28           | 18           | I/O         | ST             | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                              |

| RC3/SCK/SCL       | 13          | 14           | 5            | I/O         | ST             | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                                |

| RC4/SDI/SDA       | 14          | 15           | 6            | I/O         | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).                                                                                                                                          |

| RC5/SDO           | 15          | 16           | 7            | I/O         | ST             | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                      |

| C1                | 16          | 17           | 8            | Р           |                | LCD Voltage Generation.                                                                                                                                                                                           |

| C2                | 17          | 18           | 9            | Р           |                | LCD Voltage Generation.                                                                                                                                                                                           |

| Legend: I = input | O = ou      | tput         |              | P = pow     | er<br>TL input | L = LCD Driver<br>ST = Schmitt Trigger input                                                                                                                                                                      |

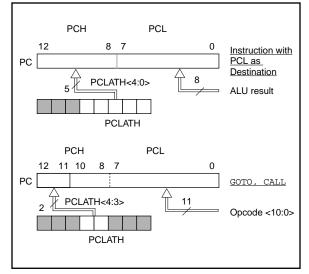

## 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-9 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-9: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

## 4.3.2 STACK

The PIC16CXXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 Program Memory Paging

PIC16C9XX devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: The PIC16C9XX ignores paging bit PCLATH<4>, which is used to access program memory pages 2 and 3. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

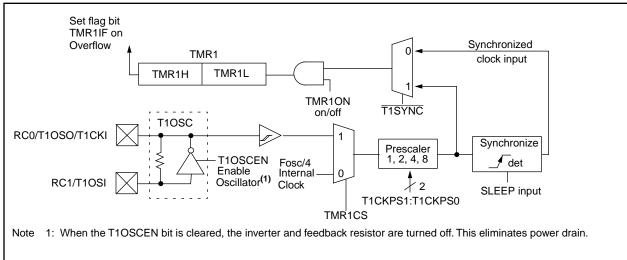

## 8.1 <u>Timer1 Operation in Timer Mode</u>

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

### 8.2 <u>Timer1 Operation in Synchronized</u> <u>Counter Mode</u>

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RC1/T1OSI when bit T1OSCEN is set or pin RC0/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

## FIGURE 8-2: TIMER1 BLOCK DIAGRAM

Г

## FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                           | R/W-0                                                                                                                                               | R/W-0                                                                                                                         | R/W-0                                                                                  | R/W-0                                                                | R/W-0                |                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                                        | SSPEN                                                                                                                                                           | CKP                                                                                                                                                 | SSPM3                                                                                                                         | SSPM2                                                                                  | SSPM1                                                                | SSPM0                | R = Readable bit                                                                                                  |

| bit7     |                                                                                                                                              |                                                                                                                                                                 |                                                                                                                                                     |                                                                                                                               |                                                                                        |                                                                      | bit0                 | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                              |

| bit 7:   | WCOL: We<br>1 = The SS<br>(must be c<br>0 = No col                                                                                           | SPBUF reg                                                                                                                                                       | jister is w                                                                                                                                         |                                                                                                                               | e it is still ti                                                                       | ransmitting                                                          | the previo           | us word                                                                                                           |

| bit 6:   | SSPOV: R                                                                                                                                     | eceive Ov                                                                                                                                                       | erflow Ind                                                                                                                                          | icator bit                                                                                                                    |                                                                                        |                                                                      |                      |                                                                                                                   |

|          | the data in<br>if only tran                                                                                                                  | byte is rece<br>SSPSR is<br>smitting da<br>tion (and t                                                                                                          | lost. Ove<br>ata, to avo                                                                                                                            | rflow can c<br>oid setting                                                                                                    | only occur<br>overflow.                                                                | in slave mo<br>In master i                                           | ode. The us          | revious data. In case of overflov<br>er must read the SSPBUF, eve<br>werflow bit is not set since eac<br>egister. |

|          | $\frac{\ln I^2 C \mod}{1 = A \text{ byte}}$<br>in transmit<br>0 = No over                                                                    | is received<br>mode. SS                                                                                                                                         |                                                                                                                                                     |                                                                                                                               |                                                                                        |                                                                      |                      | ous byte. SSPOV is a "don't care                                                                                  |

| bit 5:   | SSPEN: S                                                                                                                                     | ynchronou                                                                                                                                                       | s Serial F                                                                                                                                          | ort Enable                                                                                                                    | e bit                                                                                  |                                                                      |                      |                                                                                                                   |

|          | $0 = \text{Disable}$ $\frac{\ln l^2 C \mod l}{l + l^2}$                                                                                      | es serial po<br>es serial p<br><u>de</u><br>es the seria                                                                                                        | ort and co<br>al port and                                                                                                                           | nfigures th<br>configure                                                                                                      | nese pins                                                                              | as I/O port                                                          | pins as sei          | rt pins<br>rial port pins                                                                                         |

| bit 4:   | <b>CKP</b> : Cloc<br>In SPI mod<br>1 = Idle sta<br>0 = Idle sta<br>In $I^2$ C mod<br>SCK relea                                               | k Polarity S<br>de<br>ate for cloc<br>ate for cloc<br>de<br>se control                                                                                          | Select bit<br>k is a higł                                                                                                                           | n level                                                                                                                       | s must be                                                                              | properly c                                                           | onfigured a          | is input or output.                                                                                               |

|          | 1 = Enable<br>0 = Holds                                                                                                                      |                                                                                                                                                                 | clock stra                                                                                                                                          | tch) (Llead                                                                                                                   | to onsure                                                                              | , data sotu                                                          | n time)              |                                                                                                                   |

| bit 3-0: | SSPM3:S3<br>0000 = SP<br>0001 = SP<br>0010 = SP<br>0100 = SP<br>0100 = SP<br>0101 = SP<br>0110 = I <sup>2</sup> C<br>0111 = I <sup>2</sup> C | SPM0: Syr<br>Pl master m<br>Pl master m<br>Pl master m<br>Pl master m<br>Pl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo | achronous<br>node, cloc<br>node, cloc<br>node, cloc<br>de, clock<br>de, clock<br>de, clock<br>de, 7-bit a<br>de, 10-bit<br>controlle<br>de, 7-bit a | Serial Pol<br>k = Fosc/4<br>k = Fosc/6<br>k = TMR2<br>= SCK pin<br>= SCK pin<br>ddress<br>address<br>d master n<br>ddress wit | rt Mode Si<br>4<br>16<br>54<br>. SS pin ci<br>. SS pin ci<br>node (slav<br>th start an | elect bits<br>ontrol enal<br>ontrol disa<br>re idle)<br>d stop bit i | bled.<br>bled. SS ca |                                                                                                                   |

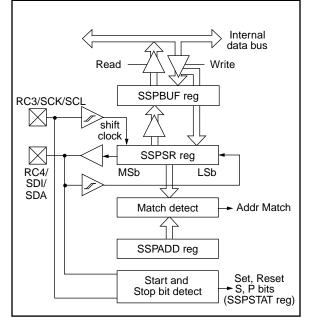

# 11.3 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

## FIGURE 11-18: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

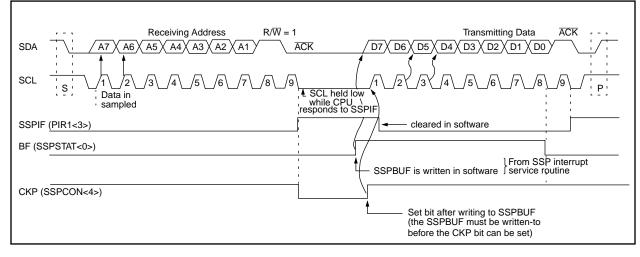

## 11.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-20). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

## FIGURE 11-20: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

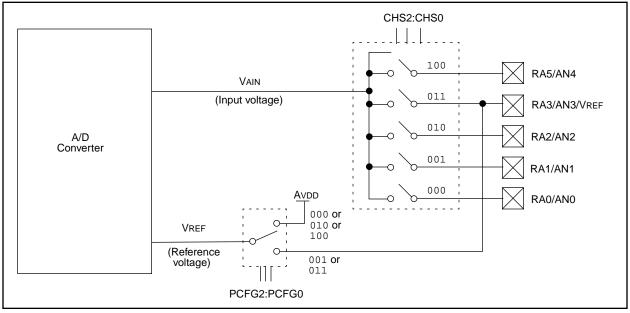

## FIGURE 12-3: A/D BLOCK DIAGRAM

## 12.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

## 12.6 <u>A/D Accuracy/Error</u>

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at <  $\pm$ 1 LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

The maximum pin leakage current is  $\pm$  1  $\mu A.$

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from TOSC, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

## 12.7 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

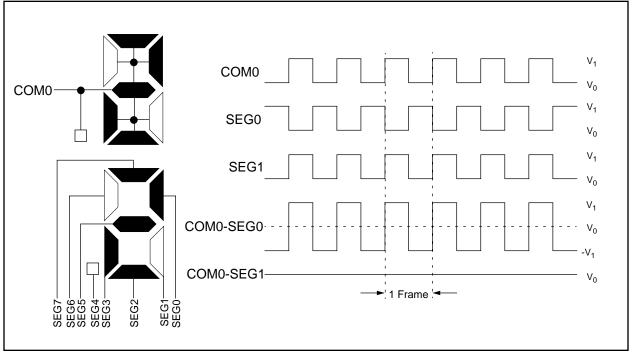

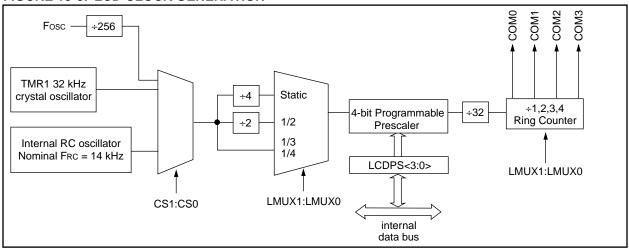

## 13.1 LCD Timing

The LCD module has 3 possible clock source inputs and supports static, 1/2, 1/3, and 1/4 multiplexing.

#### 13.1.1 TIMING CLOCK SOURCE SELECTION

The clock sources for the LCD timing generation are:

- Internal RC oscillator

- Timer1 oscillator

- System clock divided by 256

The first timing source is an internal RC oscillator which runs at a nominal frequency of 14 kHz. This oscillator provides a lower speed clock which may be used to continue running the LCD while the processor is in sleep. The RC oscillator will power-down when it is not selected or when the LCD module is disabled. The second source is the Timer1 external oscillator. This oscillator provides a lower speed clock which may be used to continue running the LCD while the processor is in sleep. It is assumed that the frequency provided on this oscillator will be 32 kHz. To use the Timer1 oscillator as a LCD module clock source, it is only necessary to set the T1OSCEN (T1CON<3>) bit.

The third source is the system clock divided by 256. This divider ratio is chosen to provide about 32 kHz output when the external oscillator is 8 MHz. The divider is not programmable. Instead the LCDPS register is used to set the LCD frame clock rate.

All of the clock sources are selected with bits CS1:CS0 (LCDCON<3:2>). Refer to Figure 13-1 for details of the register programming.

#### FIGURE 13-8: LCD CLOCK GENERATION

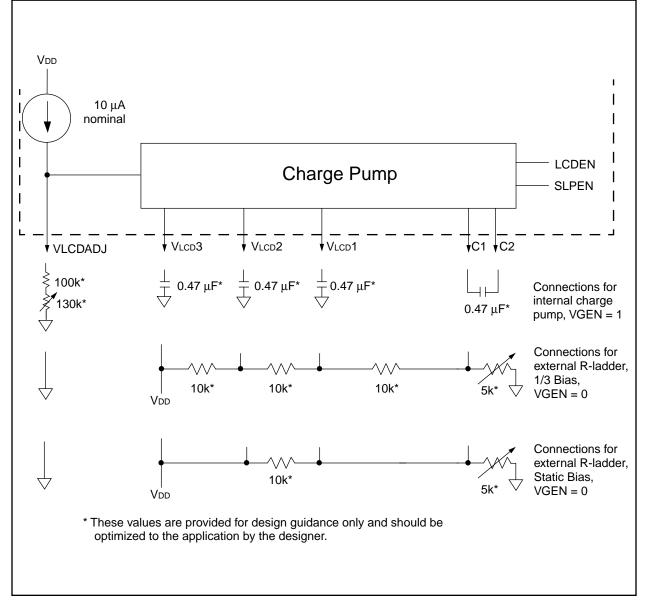

## 13.5 Voltage Generation

There are two methods for LCD voltage generation, internal charge pump, or external resistor ladder.

#### 13.5.1 CHARGE PUMP

The LCD charge pump is shown in Figure 13-13. The 1.0V - 2.3V regulator will establish a stable base voltage from the varying battery voltage. This regulator is adjustable through the range by connecting a variable external resistor from VLCDADJ to ground. The potentiometer provides contrast adjustment for the LCD. This base voltage is connected to VLCD1 on the charge pump. The charge pump boosts VLCD1 into VLCD2 =

$2*V_{LCD1}$  and  $V_{LCD3} = 3*V_{LCD1}$ . When the charge pump is not operating, Vlcd3 will be internally tied to VDD. See the Electrical Specifications section for charge pump capacitor and potentiometer values.

#### 13.5.2 EXTERNAL R-LADDER

The LCD module can also use an external resistor ladder (R-Ladder) to generate the LCD voltages. Figure 13-13 shows external connections for static and 1/3 bias. The VGEN (LCDCON<4>) bit must be cleared to use an external R-Ladder.

## FIGURE 13-13:CHARGE PUMP AND RESISTOR LADDER

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16CXXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

## FIGURE 14-1: CONFIGURATION WORD

| CP1 C    | CP0 CP1                                                                                | CP0                                            | CP1                                         | CP0                          | —                  | —   | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|----------|----------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|------------------------------|--------------------|-----|-----|-----|-------|------|-------|-------|-----------|--------|

| oit13    |                                                                                        |                                                |                                             |                              |                    |     |     |     |       |      |       | bit0  | Address   | 2007h  |

|          | <b>CP1:CP0</b><br>11 = Code<br>10 = Uppe<br>01 = Uppe<br>00 = All m<br><b>Unimpler</b> | e protec<br>er half o<br>er 3/4 of<br>nemory i | tion off<br>f progra<br>f progra<br>is code | am mer<br>Im merr<br>protect | nory co<br>10ry co | •   |     |     |       |      |       |       |           |        |

| oit 3:   | <b>PWRTE</b> : F<br>1 = PWRT<br>0 = PWRT                                               | r disable                                      | ed                                          | r Enabl                      | e bit              |     |     |     |       |      |       |       |           |        |

| oit 2:   | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                                                  | enabled                                        |                                             | Enable                       | bit                |     |     |     |       |      |       |       |           |        |

| bit 1-0: | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (                            | oscillato<br>oscillato<br>oscillator           | r<br>r<br>r                                 | or Sele                      | ction bi           | its |     |     |       |      |       |       |           |        |

#### 14.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.8 for details on SLEEP mode.

#### 14.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 7.0)

#### 14.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

#### 14.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 14-1 stores and restores the STATUS, W, and PCLATH registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the ISR code.

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### EXAMPLE 14-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP         | ;Copy W to TEMP register, could be bank one or zero     |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| BCF    | STATUS, IRP    | ;Return to Bank 0                                       |

| MOVF   | FSR, W         | ;Copy FSR to W                                          |

| MOVWF  | FSR_TEMP       | ;Copy FSR from W to FSR_TEMP                            |

| :      |                |                                                         |

| :(ISR) |                |                                                         |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | Restore PCLATH                                          |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

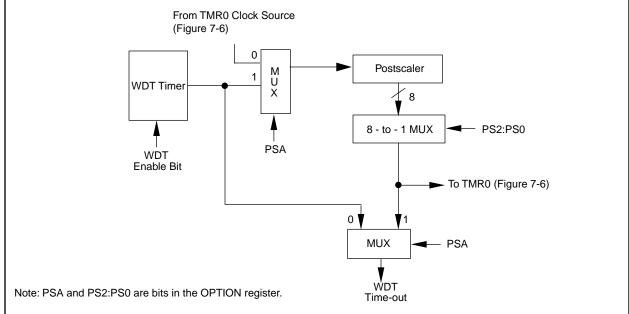

## 14.7 <u>Watchdog Timer (WDT)</u>

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 14.1).

#### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 14-16:WATCHDOG TIMER BLOCK DIAGRAM

## FIGURE 14-17:SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------------|-------|--------|-------|-------|----------------------|-------|-------|-------|

| 2007h     | Config. bits | (1)   | (1)    | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h, 181h | OPTION       | RBPU  | INTEDG | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 14-1 for operation of these bits.

# 15.1 Instruction Descriptions

| ADDLW             | Add Lite                                                                                                                | ral and \           | N               |               |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                      | DDLW                | k               |               |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                         | 55                  |                 |               |  |  |  |  |  |

| Operation:        | $(W) + k \to (W)$                                                                                                       |                     |                 |               |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                |                     |                 |               |  |  |  |  |  |

| Encoding:         | 11                                                                                                                      | 111x                | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |                     |                 |               |  |  |  |  |  |

| Words:            | 1                                                                                                                       |                     |                 |               |  |  |  |  |  |

| Cycles:           | 1                                                                                                                       |                     |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                      | Q2                  | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                                                                                                  | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example:          | ADDLW                                                                                                                   | 0x15                |                 |               |  |  |  |  |  |

|                   | Before In<br>After Inst                                                                                                 | W =                 | 0x10            |               |  |  |  |  |  |

|                   |                                                                                                                         | W =                 | 0x25            |               |  |  |  |  |  |

| ADDWF             | Add W a                                                                                                                                                                   | nd f                                  |                 |                      |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|----------------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                                        | DDWF                                  | f,d             |                      |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                            | $0 \le f \le 127$<br>$d \in [0,1]$    |                 |                      |  |  |  |  |  |  |

| Operation:        | (W) + (f)                                                                                                                                                                 | (W) + (f) $\rightarrow$ (destination) |                 |                      |  |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                  |                                       |                 |                      |  |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                                  | dfff            | ffff                 |  |  |  |  |  |  |

| Description:      | Add the contents of the W register with<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |                                       |                 |                      |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                         |                                       |                 |                      |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                                       |                 |                      |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                                    | Q3              | Q4                   |  |  |  |  |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f'               | Process<br>data | Write to destination |  |  |  |  |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                                  | 0               |                      |  |  |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =                          | 0x17<br>0xC2    |                      |  |  |  |  |  |  |

W =

FSR =

0xD9

0xC2

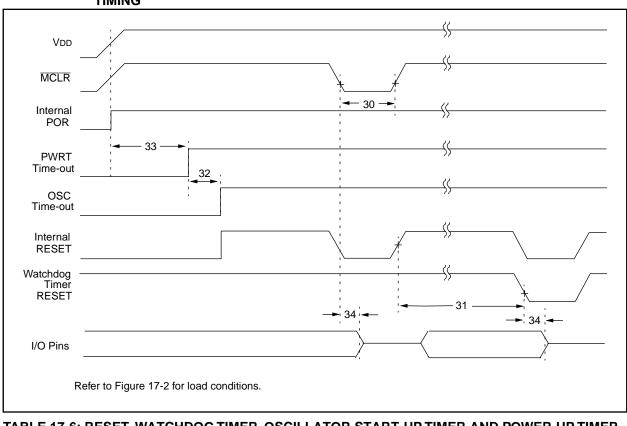

## FIGURE 17-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Мах | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | —   | μs    |                          |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | —     | Tosc = OSC1 period       |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No. | Sym                   | Characteristic                                                        | Min                | Тур†            | Max | Units | Conditions |  |

|--------------|-----------------------|-----------------------------------------------------------------------|--------------------|-----------------|-----|-------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү                | —               | _   | ns    |            |  |

| 71*          | TscH                  | SCK input high time (slave Continuous mode)                           |                    | 1.25Tcy +<br>30 | —   | —     | ns         |  |

| 71A*         |                       |                                                                       | Single Byte        | 40              | _   | _     | ns         |  |

| 72*          | TscL                  | SCK input low time (slave mode)                                       |                    |                 | —   | —     | ns         |  |

| 72A*         |                       | Single Byte                                                           |                    | 40              |     |       |            |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input                                          | 50                 | —               | _   | ns    |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to                                        | 50                 | —               | —   | ns    |            |  |

| 75*          | TdoR                  | SDO data output rise time                                             | _                  | 10              | 25  | ns    |            |  |

| 76*          | TdoF                  | SDO data output fall time                                             |                    | —               | 10  | 25    | ns         |  |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-imped                                            | ance               | 10              | —   | 50    | ns         |  |

| 78*          | TscR                  | SCK output rise time (master                                          | <sup>r</sup> mode) | —               | 10  | 25    | ns         |  |

| 79*          | TscF                  | SCK output fall time (master                                          | mode)              | —               | 10  | 25    | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after S                                         | SCK edge           | —               | —   | 50    | ns         |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SC                                           | CK edge            | Тсү             | —   | —     | ns         |  |

| 82*          | TssL2doV              | SDO data output valid after 5                                         | SS↓ edge           | _               | _   | 50    | ns         |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                    | 1.5Tcy + 40     | _   | _     | ns         |  |

| 84*          | Tb2b                  | Delay between consecutive b                                           | oytes              | 1.5TCY + 40     | _   | _     | ns         |  |

### **TABLE 17-9: SPI MODE REQUIREMENTS**

\* Characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

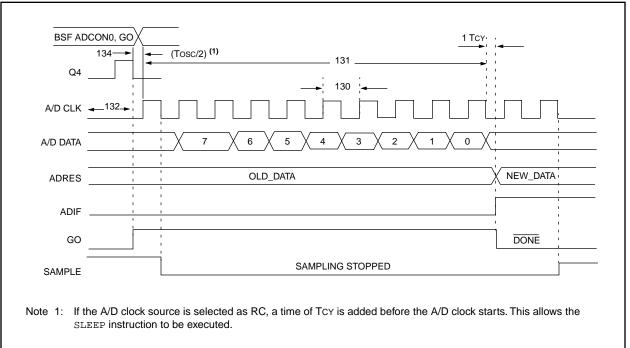

#### FIGURE 17-14:A/D CONVERSION TIMING

## TABLE 17-13:A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                     |                              | Min   | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|------------------------------------|------------------------------|-------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                   | PIC16 <b>C</b> 924           | 1.6   | —        | —   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                       |

|              |      |                                    | PIC16 <b>LC</b> 924          | 2.0   | —        | —   | μs    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                    | PIC16 <b>C</b> 924           | 2.0   | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                    | PIC16 <b>LC</b> 924          | 3.0   | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (not i<br>(Note 1) | ncluding S/H time)           | _     | 9.5      | _   | TAD   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                   | cquisition time              |       | 20       | _   | μs    |                                                                                                                                                                                                                               |

|              |      |                                    |                              | 5*    | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start              |                              | _     | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TcY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from conve               | $rt \rightarrow sample time$ | 1.5 § | —        |     | TAD   |                                                                                                                                                                                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 12.1 for min conditions.

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| RE: Reader Response                                                                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                         |  |

| From: Name                                                                                                                                                                                                                                              |  |

| Company                                                                                                                                                                                                                                                 |  |

| Address                                                                                                                                                                                                                                                 |  |

| City / State / ZIP / Country                                                                                                                                                                                                                            |  |

| Telephone: () - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - |  |

| Would you like a reply?YN                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                         |  |

| Device: PIC16C9XX Literature Number: DS30444E                                                                                                                                                                                                           |  |

| Questions:                                                                                                                                                                                                                                              |  |

| 1. What are the best features of this document?                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 2. How does this document meet your hardware and software development needs?                                                                                                                                                                            |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 3. Do you find the organization of this data sheet easy to follow? If not, why?                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 4. What additions to the data sheet do you think would enhance the structure and subject?                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                         |  |

| 5. What deletions from the data sheet could be made without affecting the overall usefulness?                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 6. Is there any incorrect or misleading information (what and where)?                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 7. How would you improve this document?                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                         |  |

| 8. How would you improve our software, systems, and silicon products?                                                                                                                                                                                   |  |