Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | LCD, POR, PWM, WDT                                                        |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 68-LCC (J-Lead)                                                           |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c924-04i-l |

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the peripheral interrupts.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

Note:

# FIGURE 4-7: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0 | R/W-0               | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|---------------------|-----|-----|-------|--------|--------|--------|

| LCDIF | ADIF <sup>(1)</sup> | _   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit7  |                     |     |     |       |        |        | bit0   |

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'

- n = Value at POR reset

bit 7: LCDIF: LCD Interrupt Flag bit

1 = LCD interrupt occurred (must be cleared in software)

0 = LCD interrupt did not occur

bit 6: **ADIF**: A/D Converter Interrupt Flag bit<sup>(1)</sup>

1 = An A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complete

bit 5-4: Unimplemented: Read as '0'

bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit

1 = The transmission/reception is complete (must be cleared in software)

0 = Waiting to transmit/receive

bit 2: CCP1IF: CCP1 Interrupt Flag bit

Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

**PWM Mode**

Unused in this mode

bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

Note 1: Bit ADIF is reserved on the PIC16C923, always maintain this bit clear.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

# EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

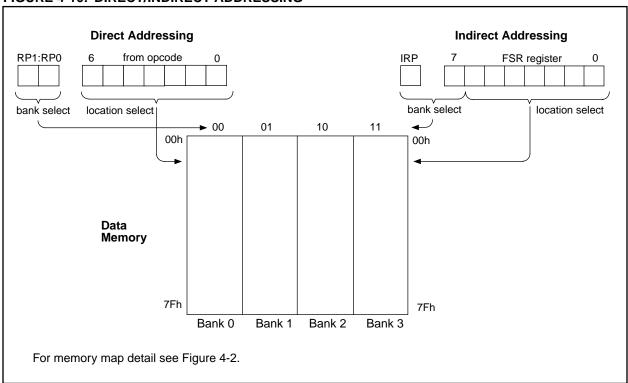

# 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register (FSR). Reading the INDF register itself indirectly (FSR = '0') will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-10.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

### **EXAMPLE 4-2: INDIRECT ADDRESSING**

```

movlw

0 \times 20

;initialize pointer

;to RAM

movwf FSR

NEXT

clrf

INDF

;clear INDF register

incf

FSR,F ;inc pointer

btfss FSR,4 ;all done?

NEXT

;no clear next

goto

CONTINUE

;yes continue

```

### FIGURE 4-10: DIRECT/INDIRECT ADDRESSING

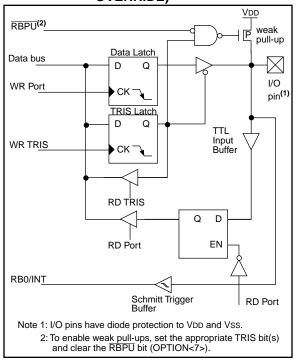

## 5.3 PORTC and TRISC Register

PORTC is an 6-bit bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### **EXAMPLE 5-3: INITIALIZING PORTC**

```

BCF

STATUS, RPO ; Select BankO

BCF

STATUS, RP1

CLRF

PORTC

; Initialize PORTC

BSF

STATUS, RPO ;

MOVLW

0xCF

; Value used to

; initialize data

; direction

MOVWF TRISC

; Set RC<3:0> as inputs

; RC<5:4> as outputs

; RC<7:6> always read 0

```

FIGURE 5-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**TABLE 5-5: PORTC FUNCTIONS**

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input                        |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                               |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture input/Compare output/PWM output                               |

| RC3/SCK/SCL     | bit3 | ST          | Input/output port pin or the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 | ST          | Input/output port pin or the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data out                                      |

Legend: ST = Schmitt Trigger input

# TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6 | Bit 5                                 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|-------|---------------------------------------|-------|-------|-------|---------|---------|-------------------------------|---------------------------|

| 07h     | PORTC | _     | _     | RC5                                   | RC4   | RC3   | RC2   | RC1     | RC0     | xx xxxx                       | uu uuuu                   |

| 87h     | TRISC | _     | _     | PORTC Data Direction Control Register |       |       |       | 11 1111 | 11 1111 |                               |                           |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTC.

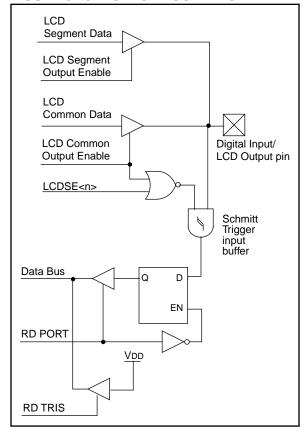

# 5.7 PORTG and TRISG Register

PORTG is an digital input only port. Each pin is multiplexed with an LCD segment driver. These pins have Schmitt Trigger input buffers.

**Note 1:** On a Power-on Reset these pins are configured as LCD segment drivers.

Note 2: To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

# **EXAMPLE 5-7: INITIALIZING PORTG**

BCF STATUS,RP0 ;Select Bank2

BSF STATUS,RP1 ;

BCF LCDSE,SE27 ;Make all PORTG

BCF LCDSE,SE20 ;and PORTE<7>;digital inputs

# FIGURE 5-10: PORTG BLOCK DIAGRAM

### **TABLE 5-13: PORTG FUNCTIONS**

| Name      | Bit# | Buffer Type | Function                                                            |

|-----------|------|-------------|---------------------------------------------------------------------|

| RG0/SEG20 | bit0 | ST          | Digital input or Segment Driver20                                   |

| RG1/SEG21 | bit1 | ST          | Digital input or Segment Driver21                                   |

| RG2/SEG22 | bit2 | ST          | Digital input or Segment Driver22                                   |

| RG3/SEG23 | bit3 | ST          | Digital input or Segment Driver23                                   |

| RG4/SEG24 | bit4 | ST          | Digital input or Segment Driver24                                   |

| RG5/SEG25 | bit5 | ST          | Digital input or Segment Driver25                                   |

| RG6/SEG26 | bit6 | ST          | Digital input or Segment Driver26                                   |

| RG7/SEG28 | bit7 | ST          | Digital input or Segment Driver28 (not available on 64-pin devices) |

Legend: ST = Schmitt Trigger input

# TABLE 5-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

| Address | Name  | Bit 7   | Bit 6      | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|---------|------------|-------|-----------|-----------|-------|-------|-------|-------------------------------|---------------------------|

| 108h    | PORTG | RG7     | RG6        | RG5   | RG4       | RG3       | RG2   | RG1   | RG0   | 0000 0000                     | 0000 0000                 |

| 188h    | TRISG | PORTG I | Data Direc |       | 1111 1111 | 1111 1111 |       |       |       |                               |                           |

| 10Dh    | LCDSE | SE29    | SE27       | SE20  | SE16      | SE12      | SE9   | SE5   | SE0   | 1111 1111                     | 1111 1111                 |

Legend: Shaded cells are not used by PORTG.

# 6.0 OVERVIEW OF TIMER MODULES

Each module can generate an interrupt to indicate that an event has occurred (e.g. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

#### 6.1 Timer0 Overview

The Timer0 module is a simple 8-bit timer/counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 when prescaler assigned to Watchdog timer, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 6.2 Timer1 Overview

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit capture or the 16-bit compare and must be synchronized to the device. Timer1 oscillator is also one of the clock sources for the LCD module.

#### 6.3 Timer2 Overview

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the clock source for the Syn-

chronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

### 6.4 CCP Overview

The CCP module can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPR1H:CCPR1L register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCP1 pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPR1H:CCPR1L register pair. When a match occurs an interrupt can be generated, and the output pin CCP1 can be forced to given state (High or Low), TMR1 can be reset and start A/D conversion. This depends on the control bits CCP1M3:CCP1M0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPR1H:CCPR1L<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCP1 pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCP1 pin (if an output) will be forced high.

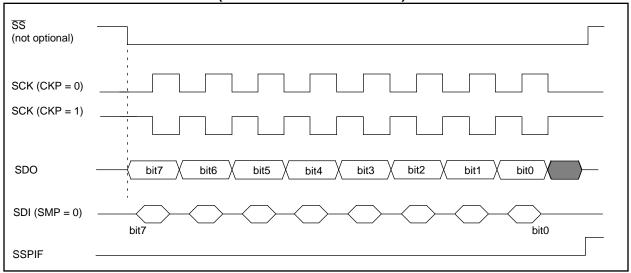

# FIGURE 11-7: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

# TABLE 11-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                 | Name    | Bit 7   | Bit 6               | Bit 5      | Bit 4                                 | Bit 3        | Bit 2   | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|---------|---------|---------------------|------------|---------------------------------------|--------------|---------|--------|--------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                | TOIE       | INTE                                  | RBIE         | TOIF    | INTF   | RBIF   | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1    | LCDIF   | ADIF <sup>(1)</sup> | _          | _                                     | SSPIF        | CCP1IF  | TMR2IF | TMR1IF | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1    | LCDIE   | ADIE <sup>(1)</sup> | _          | _                                     | SSPIE        | CCP1IE  | TMR2IE | TMR1IE | 00 0000                       | 00 0000                   |

| 13h                     | SSPBUF  | Synchro | nous Serial         | Port Recei | ve Buffer/Tr                          | ansmit Reg   | ister   |        |        | xxxx xxxx                     | uuuu uuuu                 |

| 14h                     | SSPCON  | WCOL    | SSPOV               | SSPEN      | CKP                                   | SSPM3        | SSPM2   | SSPM1  | SSPM0  | 0000 0000                     | 0000 0000                 |

| 85h                     | TRISA   | _       | _                   | PORTA Da   | ata Direction                         | n Control Re | egister |        |        | 11 1111                       | 11 1111                   |

| 87h                     | TRISC   | _       | _                   | PORTC D    | PORTC Data Direction Control Register |              |         |        |        | 11 1111                       | 11 1111                   |

| 94h                     | SSPSTAT | SMP     | CKE                 | D/Ā        | Р                                     | S            | R/W     | UA     | BF     | 0000 0000                     | 0000 0000                 |

d: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

1: Bits ADIE and ADIF are reserved on the PIC16C923, always maintain these bits clear.

# 11.2 I<sup>2</sup>C™ Overview

This section provides an overview of the Inter-Integrated Circuit (I<sup>2</sup>C) bus, with Section 11.3 discussing the operation of the SSP module in I<sup>2</sup>C mode.

The I<sup>2</sup>C bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. An enhanced specification, or fast mode is not supported. This device will communicate with fast mode devices if attached to the same bus.

The I<sup>2</sup>C interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXXX software. Table 11-2 defines some of the I<sup>2</sup>C bus terminology. For additional information on the I<sup>2</sup>C interface specification, refer to the Philips document "The I<sup>2</sup>C bus and how to use it." #939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the I<sup>2</sup>C bus is limited only by the maximum bus loading specification of 400 pF.

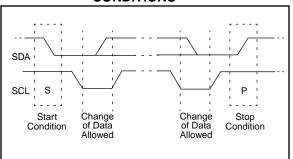

# 11.2.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. Figure 11-8 shows the START and STOP conditions. The master generates these conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

FIGURE 11-8: START AND STOP CONDITIONS

TABLE 11-2: I<sup>2</sup>C BUS TERMINOLOGY

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

#### 11.3.2 MASTER MODE

Master mode of operation is supported, in firmware, using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP and START bits will toggle based on the start and stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle with both the S and P bits clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- · STOP condition

- · Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.3.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP and START bits will toggle based on the start and stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSP-STAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, they are:

- Address Transfer

- · Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an  $\overline{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

# TABLE 11-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                 | Name    | Bit 7       | Bit 6               | Bit 5                   | Bit 4         | Bit 3       | Bit 2  | Bit 1   | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|---------|-------------|---------------------|-------------------------|---------------|-------------|--------|---------|---------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE         | PEIE                | TOIE                    | INTE          | RBIE        | TOIF   | INTF    | RBIF    | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1    | LCDIF       | ADIF <sup>(1)</sup> | -                       | _             | SSPIF       | CCP1IF | TMR2IF  | TMR1IF  | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1    | LCDIE       | ADIE <sup>(1)</sup> |                         | _             | SSPIE       | CCP1IE | TMR2IE  | TMR1IE  | 00 0000                       | 00 0000                   |

| 13h                     | SSPBUF  | Synchronous | Serial Po           | t Receive I             | Buffer/Tran   | smit Regist | ter    |         |         | xxxx xxxx                     | uuuu uuuu                 |

| 93h                     | SSPADD  | Synchronous | Serial Po           | t (I <sup>2</sup> C mod | e) Address    | Register    |        |         |         | 0000 0000                     | 0000 0000                 |

| 14h                     | SSPCON  | WCOL        | SSPOV               | SSPEN                   | CKP           | SSPM3       | SSPM2  | SSPM1   | SSPM0   | 0000 0000                     | 0000 0000                 |

| 94h                     | SSPSTAT | SMP         | CKE                 | D/Ā                     | Р             | S           | R/W    | UA      | BF      | 0000 0000                     | 0000 0000                 |

| 87h                     | TRISC   | _           | -                   | PORTC D                 | ata Direction | on Control  |        | 11 1111 | 11 1111 |                               |                           |

Legend: x = unknown, u = unchanged,  $- = unimplemented read as '0'. Shaded cells are not used by SSP in <math>I^2C$  mode.

Note 1: Bits ADIE and ADIF are reserved on the PIC16C923, always maintain these bits clear.

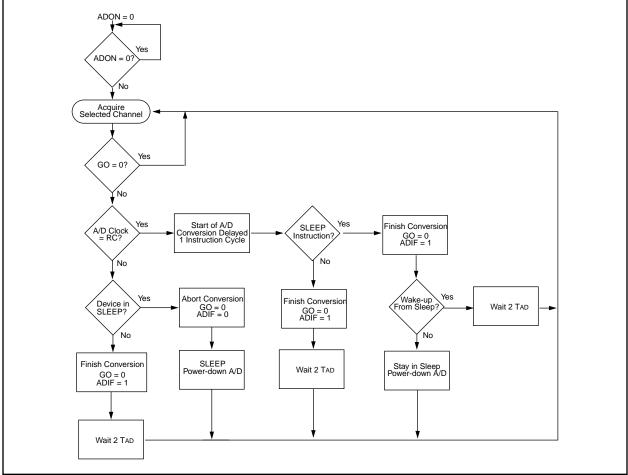

### 12.4 A/D Conversions

Example 12-2 show how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RAO pin (channel0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### **EXAMPLE 12-2: DOING AN A/D CONVERSION**

```

BCF

STATUS, RP1

; Select Bank1

STATUS, RP0

BSF

ADCON1

CLRF

; Configure A/D inputs

BSF

PIE1, ADIE

; Enable A/D interrupts

; Select Bank0

BCF

STATUS, RP0

MOVLW

0xC1

; RC Clock, A/D is on, Channel 0 is selected

MOVWF

ADCON0

; Clear A/D interrupt flag bit

BCF

PIR1, ADIF

INTCON, PEIE

BSF

; Enable peripheral interrupts

BSF

INTCON, GIE

; Enable all interrupts

Ensure that the required acquisition time for the selected input channel has elapsed.

Then the conversion may be started.

BSF

ADCON0, GO

; Start A/D Conversion

:

; The ADIF bit will be set and the {\tt GO/DONE} bit

; is cleared upon completion of the A/D Conversion.

```

FIGURE 12-6: FLOWCHART OF A/D OPERATION

**TABLE 12-2: SUMMARY OF A/D REGISTERS**

| Address                 | Name   | Bit 7   | Bit 6       | Bit 5                                 | Bit 4 | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other Resets |

|-------------------------|--------|---------|-------------|---------------------------------------|-------|-------|---------|--------|--------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE     | PEIE        | TOIE                                  | INTE  | RBIE  | TOIF    | INTF   | RBIF   | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1   | LCDIF   | ADIF        |                                       | _     | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1   | LCDIE   | ADIE        | 1                                     | 1     | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 00 0000                       | 00 0000                   |

| 1Eh                     | ADRES  | A/D Res | ult Registe | r                                     |       |       |         |        |        | xxxx xxxx                     | uuuu uuuu                 |

| 1Fh                     | ADCON0 | ADCS1   | ADCS0       | CHS2                                  | CHS1  | CHS0  | GO/DONE | (1)    | ADON   | 0000 0000                     | 0000 0000                 |

| 9Fh                     | ADCON1 | _       | 1           | 1                                     | 1     | _     | PCFG2   | PCFG1  | PCFG0  | 000                           | 000                       |

| 05h                     | PORTA  | _       | _           | RA5                                   | RA4   | RA3   | RA2     | RA1    | RA0    | 0x 0000                       | 0u 0000                   |

| 85h                     | TRISA  | _       | _           | PORTA Data Direction Control Register |       |       |         |        |        | 11 1111                       | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bit1 of ADCON0 is reserved, always maintain this bit clear.

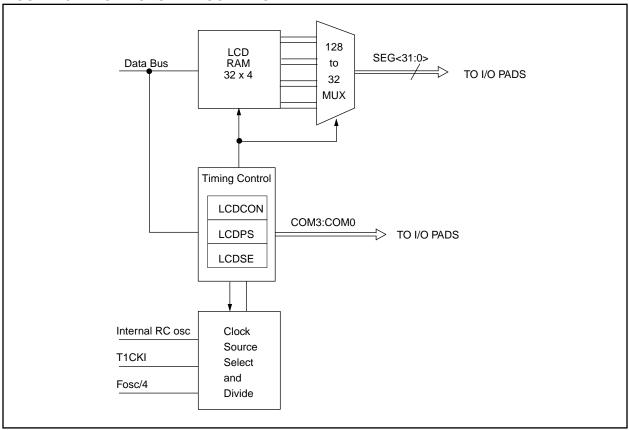

FIGURE 13-2: LCD MODULE BLOCK DIAGRAM

# FIGURE 13-3: LCDPS REGISTER (ADDRESS 10Eh)

| U-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------|-----|-----|-----|-------|-------|-------|-------|

| _    | _   | _   | _   | LP3   | LP2   | LP1   | LP0   |

| bit7 |     |     |     |       |       |       | bit0  |

R =Readable bit

W =Writable bit U =Unimplemented bit, Read as '0' -n =Value at POR reset

bit 7-4: Unimplemented, read as '0'

bit 3-0: LP3:LP0: Frame Clock Prescale Selection bits

| LMUX1:LMUX0 | Multiplex | Frame Frequency =                    |

|-------------|-----------|--------------------------------------|

| 00          | Static    | Clock source / (128 * (LP3:LP0 + 1)) |

| 01          | 1/2       | Clock source / (128 * (LP3:LP0 + 1)) |

| 10          | 1/3       | Clock source / (96 * (LP3:LP0 + 1))  |

| 11          | 1/4       | Clock source / (128 * (LP3:LP0 + 1)) |

#### 13.4.1 SEGMENT ENABLES

The LCDSE register is used to select the pin function for groups of pins. The selection allows each group of pins to operate as either LCD drivers or digital only pins. To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared.

If the pin is a digital I/O the corresponding TRIS bit controls the data direction. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

**Note 1:** On a Power-on Reset these pins are configured as LCD drivers.

Note 2: The LMUX1:LMUX0 takes precedence over the LCDSE bit settings for pins RD7, RD6 and RD5.

# EXAMPLE 13-1: STATIC MUX WITH 32 SEGMENTS

BCF STATUS,RP0 ;Select Bank 2

BSF STATUS,RP1 ;

BCF LCDCON,LMUX1 ;Select Static MUX

BCF LCDCON,LMUX0 ;

MOVLW 0xFF ;Make PortD,E,F,G

MOVWF LCDSE ;LCD pins

. . . ; configure rest of LCD

# EXAMPLE 13-2: 1/3 MUX WITH 13 SEGMENTS

BCF STATUS,RP0 ;Select Bank 2

BSF STATUS,RP1 ;

BSF LCDCON,LMUX1 ;Select 1/3 MUX

BCF LCDCON,LMUX0 ;

MOVLW 0x87 ;Make PORTD<7:0> &

MOVWF LCDSE ;PORTE<6:0> LCD pins

. . . . ;configure rest of LCD

## FIGURE 13-12:LCDSE REGISTER (ADDRESS 10Dh)

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SE29  | SE27  | SE20  | SE16  | SE12  | SE9   | SE5   | SE0   |

| bit7  |       |       |       |       |       |       | bit0  |

R =Readable bit

W =Writable bit

U =Unimplemented bit,

Read as '0'

-n =Value at POR reset

bit 7: SE29: Pin function select RD7/COM1/SEG31 - RD5/COM3/SEG29

1 = pins have LCD drive function

0 = pins have digital Input function

The LMUX1:LMUX0 setting takes precedence over the LCDSE register.

bit 6: SE27: Pin function select RG7/SEG28 and RE7/SEG27

1 = pins have LCD drive function

0 = pins have digital Input function

bit 5: SE20: Pin function select RG6/SEG26 - RG0/SEG20

1 = pins have LCD drive function

0 = pins have digital Input function

bit 4: SE16: Pin function select RF7/SEG19 - RF4/SEG16

1 = pins have LCD drive function

0 = pins have digital Input function

bit 3: **SE12**: Pin function select RF3/SEG15 - RF0/SEG12

1 = pins have LCD drive function

0 = pins have digital Input function

bit 2: SE9: Pin function select RE6/SEG11 - RE4/SEG09

1 = pins have LCD drive function

0 = pins have digital Input function

bit 1: SE5: Pin function select RE3/SEG08 - RE0/SEG05

1 = pins have LCD drive function

0 = pins have digital Input function

bit 0: SE0: Pin function select RD4/SEG04 - RD0/SEG00

1 = pins have LCD drive function

0 = pins have digital I/O function

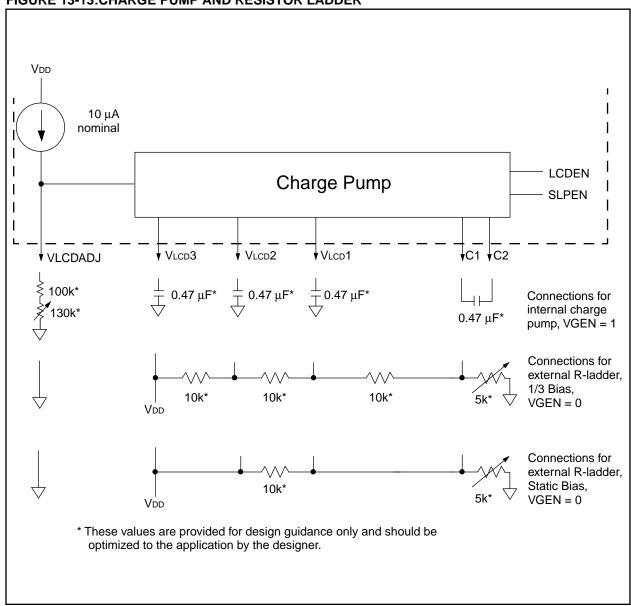

# 13.5 <u>Voltage Generation</u>

There are two methods for LCD voltage generation, internal charge pump, or external resistor ladder.

#### 13.5.1 CHARGE PUMP

The LCD charge pump is shown in Figure 13-13. The 1.0V - 2.3V regulator will establish a stable base voltage from the varying battery voltage. This regulator is adjustable through the range by connecting a variable external resistor from VLCDADJ to ground. The potentiometer provides contrast adjustment for the LCD. This base voltage is connected to VLCD1 on the charge pump. The charge pump boosts VLCD1 into VLCD2 =

$2^* \text{VLcd1}$  and  $\text{VLcd3} = 3^* \text{VLcd1}.$  When the charge pump is not operating, Vlcd3 will be internally tied to Vdd. See the Electrical Specifications section for charge pump capacitor and potentiometer values.

### 13.5.2 EXTERNAL R-LADDER

The LCD module can also use an external resistor ladder (R-Ladder) to generate the LCD voltages. Figure 13-13 shows external connections for static and 1/3 bias. The VGEN (LCDCON<4>) bit must be cleared to use an external R-Ladder.

# FIGURE 13-13: CHARGE PUMP AND RESISTOR LADDER

TABLE 14-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | TO | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | 1  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown

TABLE 14-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset                          | 000h                  | 0000 1uuu          | u-               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Applicable Devices |     | Power-on Reset         | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |  |

|----------|--------------------|-----|------------------------|--------------------------|------------------------------------|--|

| W        | 923                | 924 | xxxx xxxx              | uuuu uuuu                | uuuu uuuu                          |  |

| INDF     | 923                | 924 | N/A                    | N/A                      | N/A                                |  |

| TMR0     | 923                | 924 | xxxx xxxx              | uuuu uuuu                | uuuu uuuu                          |  |

| PCL      | 923                | 924 | 0000h                  | 0000h                    | PC + 1 <sup>(2)</sup>              |  |

| STATUS   | 923                | 924 | 0001 1xxx              | 000q quuu <b>(3)</b>     | uuuq quuu(3)                       |  |

| FSR      | 923                | 924 | xxxx xxxx              | uuuu uuuu                | uuuu uuuu                          |  |

| PORTA    | 923                | 924 | xx xxxx                | uu uuuu                  | uu uuuu                            |  |

| PORTA    | 923                | 924 | 0x 0000 <sup>(5)</sup> | 0u 0000 <sup>(5)</sup>   | uu uuuu                            |  |

| PORTB    | 923                | 924 | xxxx xxxx              | uuuu uuuu                | uuuu uuuu                          |  |

| PORTC    | 923                | 924 | xx xxxx                | uu uuuu                  | uu uuuu                            |  |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 14-5 for reset value for specific condition.

- 4: Bits PIE1<6> and PIR1<6> are reserved on the PIC16C923, always maintain these bits clear.

- 5: PORTA values when read.

## 15.0 INSTRUCTION SET SUMMARY

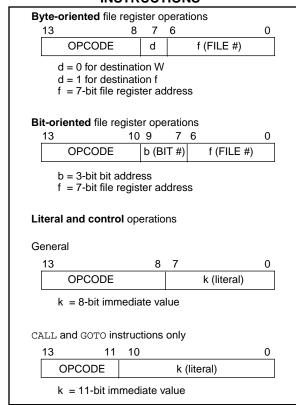

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists byte-oriented, bit-oriented, and literal and control operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

#### **TABLE 15-1: OPCODE FIELD DESCRIPTIONS**

| Field         | Description                                                                                                                                                         |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                |  |  |  |  |  |  |

| W             | Working register (accumulator)                                                                                                                                      |  |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                           |  |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                               |  |  |  |  |  |  |

| x             | Don't care location (= 0 or 1) The assembler will generate code with $x=0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |  |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                        |  |  |  |  |  |  |

| label         | Label name                                                                                                                                                          |  |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                        |  |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                     |  |  |  |  |  |  |

| PCLATH        | Program Counter High Latch                                                                                                                                          |  |  |  |  |  |  |

| GIE           | Global Interrupt Enable bit                                                                                                                                         |  |  |  |  |  |  |

| WDT           | Watchdog Timer/Counter                                                                                                                                              |  |  |  |  |  |  |

| TO            | Time-out bit                                                                                                                                                        |  |  |  |  |  |  |

| PD            | Power-down bit                                                                                                                                                      |  |  |  |  |  |  |

| dest          | Destination either the W register or the specified register file location                                                                                           |  |  |  |  |  |  |

| []            | Options                                                                                                                                                             |  |  |  |  |  |  |

| ( )           | Contents                                                                                                                                                            |  |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                         |  |  |  |  |  |  |

| <>            | Register bit field                                                                                                                                                  |  |  |  |  |  |  |

| €             | In the set of                                                                                                                                                       |  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                 |  |  |  |  |  |  |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# PIC16C9XX

**TABLE 15-2: PIC16CXXX INSTRUCTION SET**

| Mnemonic,<br>Operands                  |       | Description                  | Cycles |     | 14-Bit | Opcode | •    | Status   | Notes |

|----------------------------------------|-------|------------------------------|--------|-----|--------|--------|------|----------|-------|

|                                        |       |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |       |                              |        |     |        |        |      |          |       |

| ADDWF                                  | f, d  | Add W and f                  | 1      | 00  | 0111   |        | ffff | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d  | AND W with f                 | 1      | 00  | 0101   |        | ffff | Z        | 1,2   |

| CLRF                                   | f     | Clear f                      | 1      | 0.0 | 0001   | lfff   |      | Z        | 2     |

| CLRW                                   | -     | Clear W                      | 1      | 00  | 0001   | 0xxx   |      | Z        |       |

| COMF                                   | f, d  | Complement f                 | 1      | 0.0 | 1001   |        | ffff | Z        | 1,2   |

| DECF                                   | f, d  | Decrement f                  | 1      | 00  | 0011   |        | ffff | Z        | 1,2   |

| DECFSZ                                 | f, d  | Decrement f, Skip if 0       | 1(2)   | 0.0 | 1011   | dfff   |      |          | 1,2,3 |

| INCF                                   | f, d  | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ                                 | f, d  | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF                                  | f, d  | Inclusive OR W with f        | ì      | 00  | 0100   |        | ffff | Z        | 1,2   |

| MOVF                                   | f, d  | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF                                  | f     | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          | ,     |

| NOP                                    | -     | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF                                    | f, d  | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF                                    | f, d  | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | C        | 1,2   |

| SUBWF                                  | f, d  | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d  | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff | -, -,    | 1,2   |

| XORWF                                  | f, d  | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIEN                              |       | LE REGISTER OPERATIONS       |        |     |        |        |      |          |       |

| BCF                                    | f, b  | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF                                    | f, b  | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC                                  | f, b  | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS                                  | f, b  | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A                              | ND CO | NTROL OPERATIONS             | •      | •   |        |        |      |          |       |

| ADDLW                                  | k     | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW                                  | k     | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL                                   | k     | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT                                 | -     | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO                                   | k     | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW                                  | k     | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW                                  | k     | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE                                 | -     | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW                                  | k     | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN                                 | -     | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP                                  | -     | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW                                  | k     | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW                                  | k     | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   |      | Z        |       |

| NI-1- 4 1A                             |       |                              |        |     |        | -1     |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BSF               | Bit Set f                                              |                         |                 |                       |  |  |  |  |

|-------------------|--------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [label] BSF f,b                                        |                         |                 |                       |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$                   |                         |                 |                       |  |  |  |  |

| Operation:        | 1 → (f <b< td=""><td>&gt;)</td><td></td><td></td></b<> | >)                      |                 |                       |  |  |  |  |

| Status Affected:  | None                                                   |                         |                 |                       |  |  |  |  |

| Encoding:         | 01                                                     | 01bb                    | bfff            | ffff                  |  |  |  |  |

| Description:      | Bit 'b' in register 'f' is set.                        |                         |                 |                       |  |  |  |  |

| Words:            | 1                                                      |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                                                      |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                                     | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode                                                 | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | BSF                                                    | FLAG_F                  | REG, 7          |                       |  |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x0A                  |                         |                 |                       |  |  |  |  |

After Instruction

$FLAG_REG = 0x8A$

| BTFSC             | Bit Test, Skip if Clear                                                                                                                                                                                              |                      |                  |                  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--|--|--|--|

| Syntax:           | [label] BTFSC f,b                                                                                                                                                                                                    |                      |                  |                  |  |  |  |  |

| Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                                    |                      |                  |                  |  |  |  |  |

| Operation:        | skip if (f<                                                                                                                                                                                                          | b>) = 0              |                  |                  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                 |                      |                  |                  |  |  |  |  |

| Encoding:         | 01                                                                                                                                                                                                                   | 10bb                 | bfff             | ffff             |  |  |  |  |

| Description:      | If bit 'b' in register 'f' is '1' then the next instruction is executed.  If bit 'b', in register 'f', is '0' then the next instruction is discarded, and a NOP is executed instead, making this a 2Tcy instruction. |                      |                  |                  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                    |                      |                  |                  |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                 |                      |                  |                  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                   | Q2                   | Q3               | Q4               |  |  |  |  |

|                   | Decode                                                                                                                                                                                                               | Read<br>register 'f' | Process<br>data  | No-<br>Operation |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                             | le)                  |                  |                  |  |  |  |  |

|                   | Q1                                                                                                                                                                                                                   | Q2                   | Q3               | Q4               |  |  |  |  |

|                   | No-<br>Operation                                                                                                                                                                                                     | No-<br>Operation     | No-<br>Operation | No-<br>Operation |  |  |  |  |

| Example           | mple HERE BTFSC FLAG,1 FALSE GOTO PROCESS_CODE TRUE •                                                                                                                                                                |                      |                  |                  |  |  |  |  |

|                   | Before Instruction PC = address HERE After Instruction                                                                                                                                                               |                      |                  |                  |  |  |  |  |

|                   | if FLAG<1> = 0, PC = address TRUE if FLAG<1>=1, PC = address FALSE                                                                                                                                                   |                      |                  |                  |  |  |  |  |

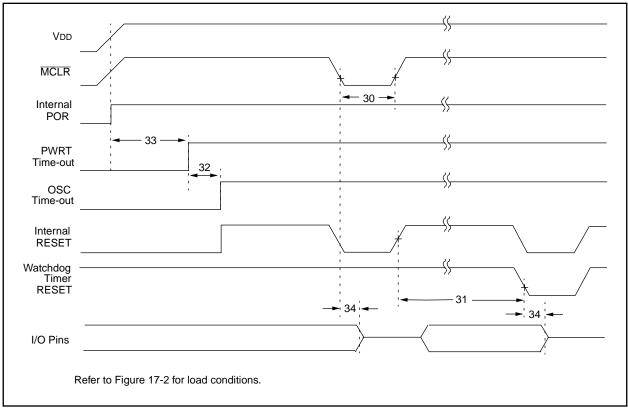

FIGURE 17-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

TABLE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                        |

|---------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    |                                                   |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C                          |

| 32            | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                |

| 33*           | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34            | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                                                   |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# **TABLE 17-9: SPI MODE REQUIREMENTS**

| Param<br>No. | Sym                   | Characteristic                          |                                          | Min             | Typ† | Max | Units | Conditions |

|--------------|-----------------------|-----------------------------------------|------------------------------------------|-----------------|------|-----|-------|------------|

| 70*          | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input               |                                          | Tcy             | _    | _   | ns    |            |

| 71*          | TscH                  | SCK input high time (slave mode)        | Continuous                               | 1.25Tcy +<br>30 | _    | _   | ns    |            |

| 71A*         |                       |                                         | Single Byte                              | 40              | _    | _   | ns    |            |

| 72*          | TscL                  | SCK input low time (slave mode)         | SCK input low time (slave Continuous     |                 | _    | _   | ns    |            |

| 72A*         |                       |                                         |                                          |                 |      |     |       |            |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input            | Setup time of SDI data input to SCK edge |                 | _    | _   | ns    |            |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge |                                          | 50              | _    | _   | ns    |            |

| 75*          | TdoR                  | SDO data output rise time               |                                          |                 | 10   | 25  | ns    |            |

| 76*          | TdoF                  | SDO data output fall time               |                                          | _               | 10   | 25  | ns    |            |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-imped              | ance                                     | 10              | _    | 50  | ns    |            |

| 78*          | TscR                  | SCK output rise time (master            | mode)                                    | _               | 10   | 25  | ns    |            |

| 79*          | TscF                  | SCK output fall time (master            | mode)                                    | _               | 10   | 25  | ns    |            |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after S           | SCK edge                                 | _               | _    | 50  | ns    |            |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge       |                                          | Tcy             | _    | _   | ns    |            |

| 82*          | TssL2doV              | SDO data output valid after SS↓ edge    |                                          | _               | _    | 50  | ns    |            |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                     |                                          | 1.5Tcy + 40     | _    | _   | ns    |            |

| 84*          | Tb2b                  | Delay between consecutive b             | ytes                                     | 1.5Tcy + 40     |      | _   | ns    |            |

Characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

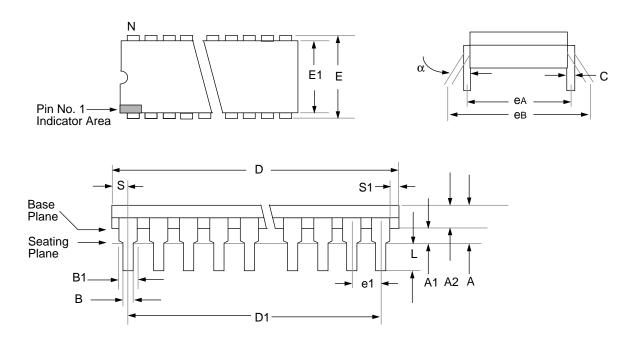

# 19.2 64-Lead Plastic Dual In-line (750 mil)

| Package Group: Plastic Dual In-Line (PLA) |       |             |           |       |       |           |  |  |  |

|-------------------------------------------|-------|-------------|-----------|-------|-------|-----------|--|--|--|

|                                           |       | Millimeters |           |       |       |           |  |  |  |

| Symbol                                    | Min   | Max         | Notes     | Min   | Max   | Notes     |  |  |  |

| α                                         | 0°    | 15°         |           | 0°    | 15°   |           |  |  |  |

| Α                                         | _     | 5.08        |           | _     | 0.200 |           |  |  |  |

| A1                                        | 0.51  | _           |           | 0.020 | _     |           |  |  |  |

| A2                                        | 3.38  | 4.27        |           | 0.133 | 0.168 |           |  |  |  |

| В                                         | 0.38  | 0.56        |           | 0.015 | 0.022 |           |  |  |  |

| B1                                        | .076  | 1.27        | Typical   | 0.030 | 0.050 | Typical   |  |  |  |

| С                                         | 0.20  | 0.30        | Typical   | 0.008 | 0.012 | Typical   |  |  |  |

| D                                         | 57.40 | 57.91       |           | 2.260 | 2.280 |           |  |  |  |

| D1                                        | 55.12 | 55.12       | Reference | 2.170 | 2.170 | Reference |  |  |  |

| Е                                         | 19.05 | 19.69       |           | 0.750 | 0.775 |           |  |  |  |

| E1                                        | 16.76 | 17.27       |           | 0.660 | 0.680 |           |  |  |  |

| e1                                        | 1.73  | 1.83        | Typical   | 0.068 | 0.072 | Typical   |  |  |  |

| eA                                        | 19.05 | 19.05       | Reference | 0.750 | 0.750 | Reference |  |  |  |

| eB                                        | 19.05 | 21.08       |           | 0.750 | 0.830 |           |  |  |  |

| L                                         | 3.05  | 3.43        |           | 0.120 | 0.135 |           |  |  |  |

| N                                         | 64    | 64          |           | 64    | 64    |           |  |  |  |

| S                                         | 1.19  | _           |           | 0.047 | _     |           |  |  |  |

| S1                                        | 0.686 | _           |           | 0.027 | _     |           |  |  |  |