Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | LCD, POR, PWM, WDT                                                       |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 176 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

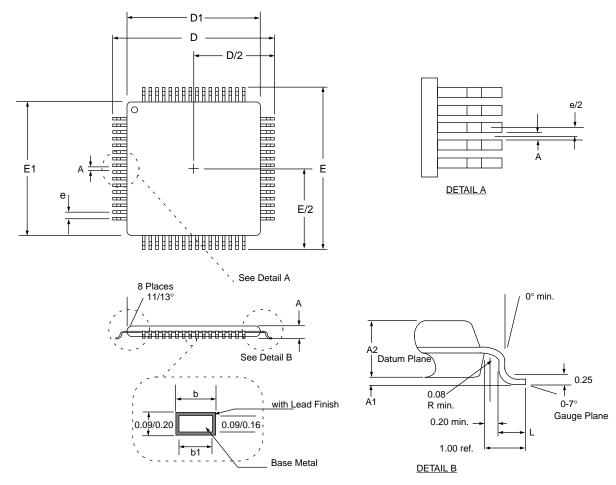

| Package / Case             | 68-LCC (J-Lead)                                                          |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c924-08-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address            | Name    | Bit 7                                                                                            | Bit 6                                                                       | Bit 5          | Bit 4          | Bit 3          | Bit 2           | Bit 1        | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------|----------------|----------------|-----------------|--------------|---------|-------------------------------|---------------------------|

| Bank 0             |         |                                                                                                  |                                                                             |                |                |                |                 |              |         |                               |                           |

| 00h                | INDF    | F Addressing this location uses contents of FSR to address data memory (not a physical register) |                                                                             |                |                |                |                 |              |         |                               | 0000 0000                 |

| 01h                | TMR0    | Timer0 mod                                                                                       | dule's register                                                             |                |                |                |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 02h                | PCL     | Program Co                                                                                       | ounter's (PC)                                                               | Least Signifi  | cant Byte      |                |                 |              |         | 0000 0000                     | 0000 0000                 |

| 03h                | STATUS  | IRP                                                                                              | RP1                                                                         | RP0            | TO             | PD             | Z               | DC           | С       | 0001 1xxx                     | 000q quuu                 |

| 04h                | FSR     | Indirect dat                                                                                     | a memory ad                                                                 | dress pointe   | r              |                |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 05h                | PORTA   | _                                                                                                | _                                                                           | PORTA Dat      | a Latch wher   | n written: POI | RTA pins whe    | en read      |         | (4)                           | (4)                       |

| 06h                | PORTB   | PORTB Da                                                                                         | ta Latch whe                                                                | n written: PO  | RTB pins wh    | en read        |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 07h                | PORTC   | _                                                                                                | _                                                                           | PORTC Dat      | a Latch whe    | n written: PO  | RTC pins wh     | en read      |         | xx xxxx                       | uu uuuu                   |

| 08h                | PORTD   | PORTD Da                                                                                         | ta Latch whe                                                                | n written: PO  | RTD pins wh    | ien read       |                 |              |         | 0000 0000                     | 0000 0000                 |

| 09h                | PORTE   | PORTE pin                                                                                        | s when read                                                                 |                |                |                |                 |              |         | 0000 0000                     | 0000 0000                 |

| 0Ah                | PCLATH  | _                                                                                                | _                                                                           | _              | Write Buffer   | for the uppe   | r 5 bits of the | e Program Co | ounter  | 0 0000                        | 0 0000                    |

| 0Bh                | INTCON  | GIE                                                                                              | PEIE                                                                        | TOIE           | INTE           | RBIE           | T0IF            | INTF         | RBIF    | 0000 000x                     | 0000 000u                 |

| 0Ch                | PIR1    | LCDIF                                                                                            | ADIF <sup>(2)</sup>                                                         | _              | _              | SSPIF          | CCP1IF          | TMR2IF       | TMR1IF  | 00 0000                       | 00 0000                   |

| 0Dh                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 | •            | •       | _                             | _                         |

| 0Eh                | TMR1L   | Holding reg                                                                                      | lolding register for the Least Significant Byte of the 16-bit TMR1 register |                |                |                |                 |              |         |                               | uuuu uuuu                 |

| 0Fh                | TMR1H   | Holding reg                                                                                      | ister for the N                                                             | lost Significa | ant Byte of th | e 16-bit TMR   | 1 register      |              |         | xxxx xxxx                     | uuuu uuuu                 |

| 10h                | T1CON   | _                                                                                                | _                                                                           | T1CKPS1        | T1CKPS0        | T1OSCEN        | T1SYNC          | TMR1CS       | TMR10N  | 00 0000                       | uu uuuu                   |

| 11h                | TMR2    | Timer2 mod                                                                                       | dule's register                                                             |                |                |                |                 |              |         | 0000 0000                     | 0000 0000                 |

| 12h                | T2CON   | —                                                                                                | TOUTPS3                                                                     | TOUTPS2        | TOUTPS1        | TOUTPS0        | TMR2ON          | T2CKPS1      | T2CKPS0 | -000 0000                     | -000 0000                 |

| 13h                | SSPBUF  | Synchronou                                                                                       | us Serial Port                                                              | Receive Buf    | fer/Transmit   | Register       |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 14h                | SSPCON  | WCOL                                                                                             | SSPOV                                                                       | SSPEN          | CKP            | SSPM3          | SSPM2           | SSPM1        | SSPM0   | 0000 0000                     | 0000 0000                 |

| 15h                | CCPR1L  | Capture/Co                                                                                       | mpare/PWM                                                                   | Register (LS   | B)             |                |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 16h                | CCPR1H  | Capture/Co                                                                                       | mpare/PWM                                                                   | Register (MS   | SB)            |                |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 17h                | CCP1CON | _                                                                                                | _                                                                           | CCP1X          | CCP1Y          | CCP1M3         | CCP1M2          | CCP1M1       | CCP1M0  | 00 0000                       | 00 0000                   |

| 18h                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | _                         |

| 19h                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | —                         |

| 1Ah                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | _                         |

| 1Bh                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | _                         |

| 1Ch                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | _                         |

| 1Dh                | _       | Unimpleme                                                                                        | nted                                                                        |                |                |                |                 |              |         | _                             | _                         |

| 1Eh <sup>(1)</sup> | ADRES   | A/D Result                                                                                       | Register                                                                    |                |                |                |                 |              |         | XXXX XXXX                     | uuuu uuuu                 |

| 1Fh <sup>(1)</sup> | ADCON0  | ADCS1                                                                                            | ADCS0                                                                       | CHS2           | CHS1           | CHS0           | GO/DONE         | (5)          | ADON    | 0000 0000                     | 0000 0000                 |

### TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY

${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0', Legend: shaded locations are unimplemented, read as '0'.

1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'. Note

2: These bits are reserved on the PIC16C923, always maintain these bits clear.

3: These pixels do not display, but can be used as general purpose RAM.

4: PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

5: Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

## TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address            | Name    | Bit 7         | Bit 6               | Bit 5                   | Bit 4          | Bit 3        | Bit 2            | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|---------------|---------------------|-------------------------|----------------|--------------|------------------|--------|--------|-------------------------------|---------------------------|

| Bank 1             | ·       | •             |                     |                         |                |              | ·                |        |        | •                             |                           |

| 80h                | INDF    | Addressing    | this location       | 0000 0000               | 0000 0000      |              |                  |        |        |                               |                           |

| 81h                | OPTION  | RBPU          | INTEDG              | TOCS                    | T0SE           | PSA          | PS2              | PS1    | PS0    | 1111 1111                     | 1111 1111                 |

| 82h                | PCL     | Program Co    | ounter's (PC)       | Least Signif            | icant Byte     |              |                  |        |        | 0000 0000                     | 0000 0000                 |

| 83h                | STATUS  | IRP           | RP1                 | RP0                     | TO             | PD           | Z                | DC     | С      | 0001 1xxx                     | 000q quuu                 |

| 84h                | FSR     | Indirect data | a memory ad         | dress pointe            | r              |              |                  |        |        | XXXX XXXX                     | uuuu uuuu                 |

| 85h                | TRISA   | —             | _                   | PORTA Dat               | a Direction R  | egister      |                  |        |        | 11 1111                       | 11 1111                   |

| 86h                | TRISB   | PORTB Dat     | a Direction R       | legister                |                |              |                  |        |        | 1111 1111                     | 1111 1111                 |

| 87h                | TRISC   | —             | _                   | PORTC Da                | ta Direction F | Register     |                  |        |        | 11 1111                       | 11 1111                   |

| 88h                | TRISD   | PORTD Dat     | a Direction F       | Register                |                |              |                  |        |        | 1111 1111                     | 1111 1111                 |

| 89h                | TRISE   | PORTE Dat     | a Direction R       | legister                |                |              |                  |        |        | 1111 1111                     | 1111 1111                 |

| 8Ah                | PCLATH  | —             | _                   | —                       | Write Buffer   | for the uppe | er 5 bits of the | e PC   |        | 0 0000                        | 0 0000                    |

| 8Bh                | INTCON  | GIE           | PEIE                | T0IE                    | INTE           | RBIE         | T0IF             | INTF   | RBIF   | 0000 000x                     | 0000 000u                 |

| 8Ch                | PIE1    | LCDIE         | ADIE <sup>(2)</sup> | —                       | _              | SSPIE        | CCP1IE           | TMR2IE | TMR1IE | 00 0000                       | 00 0000                   |

| 8Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | _                         |

| 8Eh                | PCON    | —             | _                   | —                       | _              | _            | _                | POR    | —      | 0-                            | u-                        |

| 8Fh                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | _                         |

| 90h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | —                             | —                         |

| 91h                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | _                         |

| 92h                | PR2     | Timer2 Peri   | od Register         |                         |                |              |                  |        |        | 1111 1111                     | 1111 1111                 |

| 93h                | SSPADD  | Synchronou    | is Serial Port      | (I <sup>2</sup> C mode) | Address Reg    | ister        |                  |        |        | 0000 0000                     | 0000 0000                 |

| 94h                | SSPSTAT | SMP           | CKE                 | D/Ā                     | Р              | S            | R/W              | UA     | BF     | 0000 0000                     | 0000 0000                 |

| 95h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | —                         |

| 96h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | —                         |

| 97h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | —                         |

| 98h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | —                         |

| 99h                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | —                         |

| 9Ah                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | _                         |

| 9Bh                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | -                             | —                         |

| 9Ch                | —       | Unimpleme     | nted                |                         |                |              |                  |        |        | -                             | —                         |

| 9Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | -                             | —                         |

| 9Eh                | _       | Unimpleme     | nted                |                         |                |              |                  |        |        | _                             | _                         |

| 9Fh <sup>(1)</sup> | ADCON1  |               | —                   | _                       |                | _            | PCFG2            | PCFG1  | PCFG0  | 000                           | 000                       |

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0',

Note

shaded locations are unimplemented, read as '0'. 1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

These bits are reserved on the PIC16C923, always maintain these bits clear.

These pixels do not display, but can be used as general purpose RAM.

PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

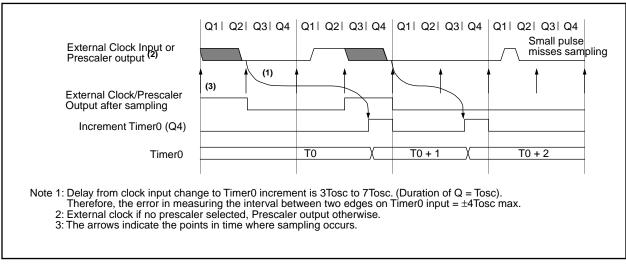

## 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

## FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

## PIC16C9XX

NOTES:

## 10.0 CAPTURE/COMPARE/PWM (CCP) MODULE

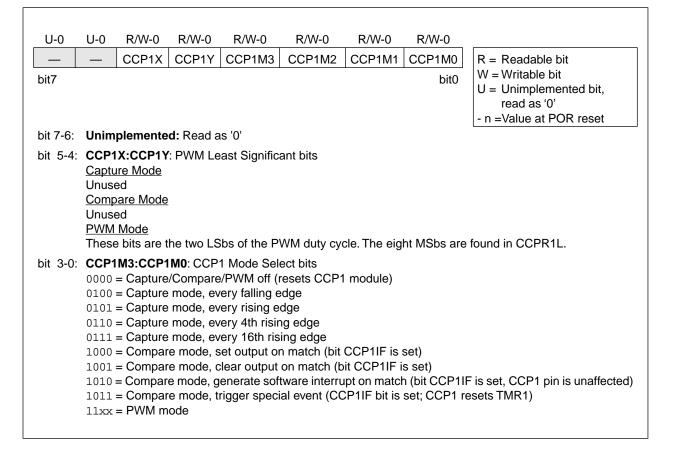

The CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM master/slave duty cycle register. Table 10-1 shows the timer resources used by the CCP module.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All three are readable and writable.

Figure 10-1 shows the CCP1CON register.

## FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)

For use of the CCP module, refer to the *Embedded Control Handbook*, "Using the CCP Modules" (AN594).

### TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

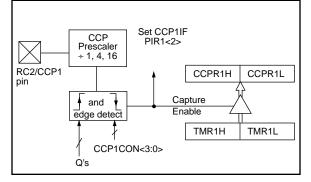

## 10.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an      |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | output, a write to the port can cause a cap- |  |  |  |  |  |

|       | ture condition.                              |  |  |  |  |  |

## FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep enable bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; | Turn CCP module off   |

|-------|-------------|---|-----------------------|

| MOVLW | NEW_CAPT_PS | ; | Load the W reg with   |

|       |             | ; | the new prescaler     |

|       |             | ; | mode value and CCP ON |

| MOVWF | CCP1CON     | ; | Load CCP1CON with     |

|       |             | ; | this value            |

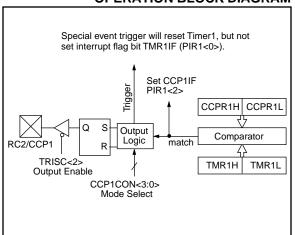

## 10.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, a compare interrupt is also generated.

## FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 11.3.2 MASTER MODE

Master mode of operation is supported, in firmware, using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP and START bits will toggle based on the start and stop conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle with both the S and P bits clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.3.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP and START bits will toggle based on the start and stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSP-STAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, they are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                 | Name    | Bit 7       | Bit 6                                | Bit 5                    | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|---------|-------------|--------------------------------------|--------------------------|-------------|------------|--------|--------|--------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE         | PEIE                                 | TOIE                     | INTE        | RBIE       | TOIF   | INTF   | RBIF   | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1    | LCDIF       | ADIF <sup>(1)</sup>                  | _                        | _           | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1    | LCDIE       | ADIE <sup>(1)</sup>                  | _                        | _           | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 00 0000                       | 00 0000                   |

| 13h                     | SSPBUF  | Synchronous | s Serial Po                          | rt Receive I             | Buffer/Tran | smit Regis | ter    |        |        | xxxx xxxx                     | uuuu uuuu                 |

| 93h                     | SSPADD  | Synchronous | s Serial Po                          | rt (I <sup>2</sup> C mod | e) Address  | Register   |        |        |        | 0000 0000                     | 0000 0000                 |

| 14h                     | SSPCON  | WCOL        | SSPOV                                | SSPEN                    | CKP         | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000                     | 0000 0000                 |

| 94h                     | SSPSTAT | SMP         | CKE                                  | D/Ā                      | Р           | S          | R/W    | UA     | BF     | 0000 0000                     | 0000 0000                 |

| 87h                     | TRISC   | —           | ORTC Data Direction Control Register |                          |             |            |        |        |        | 11 1111                       | 11 1111                   |

## TABLE 11-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by SSP in  $l^2C$  mode. Note 1: Bits ADIE and ADIF are reserved on the PIC16C923, always maintain these bits clear.

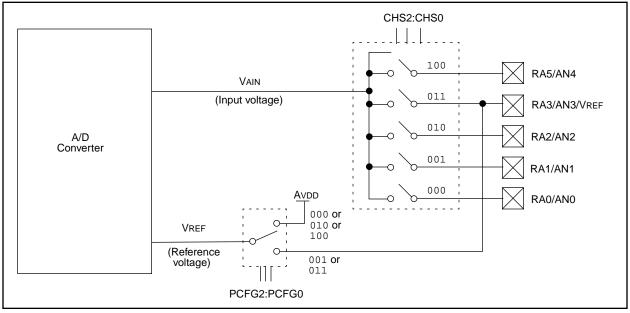

## FIGURE 12-3: A/D BLOCK DIAGRAM

## 12.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5 TAD per 8-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 12-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## 12.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog inputs will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

## TABLE 12-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock             | Source (TAD) | Device Frequency          |                           |                           |                             |  |  |  |  |

|-----------------------|--------------|---------------------------|---------------------------|---------------------------|-----------------------------|--|--|--|--|

| Operation ADCS1:ADCS0 |              | 8 MHz                     | 5 MHz                     | 1.25 MHz                  | 333.33 kHz                  |  |  |  |  |

| 2Tosc                 | 00           | 250 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 µs                        |  |  |  |  |

| 8Tosc                 | 01           | 1 μs                      | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>        |  |  |  |  |

| 32Tosc                | 10           | 4 μs                      | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <b><sup>(3)</sup></b> |  |  |  |  |

| RC                    | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup>     |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When derived frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep mode only

5: For extended voltage devices (LC), please refer to the electrical specifications section.

#### 13.4.1 SEGMENT ENABLES

The LCDSE register is used to select the pin function for groups of pins. The selection allows each group of pins to operate as either LCD drivers or digital only pins. To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared.

If the pin is a digital I/O the corresponding TRIS bit controls the data direction. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

- **Note 1:** On a Power-on Reset these pins are configured as LCD drivers.

- Note 2: The LMUX1:LMUX0 takes precedence over the LCDSE bit settings for pins RD7, RD6 and RD5.

### EXAMPLE 13-1: STATIC MUX WITH 32 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2          |

|-------|--------------|-------------------------|

| BSF   | STATUS, RP1  | ;                       |

| BCF   | LCDCON,LMUX1 | ;Select Static MUX      |

| BCF   | LCDCON,LMUX0 | ;                       |

| MOVLW | OxFF         | ;Make PortD,E,F,G       |

| MOVWF | LCDSE        | ;LCD pins               |

|       |              | ; configure rest of LCD |

## EXAMPLE 13-2: 1/3 MUX WITH 13 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2                             |

|-------|--------------|--------------------------------------------|

| BSF   | STATUS, RP1  | ;                                          |

| BSF   | LCDCON,LMUX1 | ;Select 1/3 MUX                            |

| BCF   | LCDCON,LMUX0 | ;                                          |

| MOVLW | 0x87         | ;Make PORTD<7:0> &                         |

| MOVWF | LCDSE        | ;PORTE<6:0> LCD pins                       |

|       |              | ; configure rest of LCD                    |

| MOVLW | 0x87         | ;Make PORTD<7:0> &<br>;PORTE<6:0> LCD pins |

## FIGURE 13-12:LCDSE REGISTER (ADDRESS 10Dh)

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |             |       |          |       | D 44/ 4     |                                                                                                      |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------|----------|-------|-------------|------------------------------------------------------------------------------------------------------|--|--|--|

| R/W-1        | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-1      | R/W-1       | R/W-1 | R/W-1    | R/W-1 | R/W-1       |                                                                                                      |  |  |  |

| SE29<br>bit7 | SE27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SE20       | SE16        | SE12  | SE9      | SE5   | SE0<br>bit0 | R =Readable bit<br>W =Writable bit<br>U =Unimplemented bit,<br>Read as '0'<br>-n =Value at POR reset |  |  |  |

| bit 7:       | bit 7: SE29: Pin function select RD7/COM1/SEG31 - RD5/COM3/SEG29<br>1 = pins have LCD drive function<br>0 = pins have digital Input function<br>The LMUX1:LMUX0 setting takes precedence over the LCDSE register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |       |          |       |             |                                                                                                      |  |  |  |

| bit 6:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |             |       |          |       |             |                                                                                                      |  |  |  |

| bit 5:       | <b>SE20</b> : Pin fr<br>1 = pins hav<br>0 = pins hav                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ve LCD dri | ve function | 1     | - RG0/SE | G20   |             |                                                                                                      |  |  |  |

| bit 4:       | <b>SE16</b> : Pin fr<br>1 = pins hav<br>0 = pins hav                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ve LCD dri | ve functior | ו     | RF4/SEC  | 616   |             |                                                                                                      |  |  |  |

| bit 3:       | <b>SE12</b> : Pin for $1 = pins have 0 = pins have 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ve LCD dri | ve function | 1     | RF0/SEC  | 912   |             |                                                                                                      |  |  |  |

| bit 2:       | <b>SE9</b> : Pin function select RE6/SEG11 - RE4/SEG09<br>1 = pins have LCD drive function<br>0 = pins have digital Input function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |             |       |          |       |             |                                                                                                      |  |  |  |

| bit 1:       | <b>SE5</b> : Pin function select RE3/SEG08 - RE0/SEG05<br>1 = pins have LCD drive function<br>0 = pins have digital Input function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |             |       |          |       |             |                                                                                                      |  |  |  |

| bit 0:       | <b>SE0</b> : Pin for $1 = pins have 0 = pins have$ | ve LCD dri | ve function | 1     | RD0/SE   | G00   |             |                                                                                                      |  |  |  |

## 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16CXXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

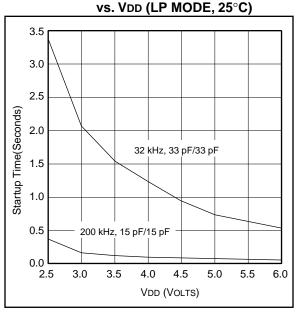

The PIC16CXXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

## FIGURE 14-1: CONFIGURATION WORD

| CP1 C    | CP0 CP1                                                                                | CP0                                            | CP1                                         | CP0                         | —                  | —   | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|----------|----------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|-----------------------------|--------------------|-----|-----|-----|-------|------|-------|-------|-----------|--------|

| oit13    |                                                                                        |                                                |                                             |                             |                    |     |     |     |       |      |       | bit0  | Address   | 2007h  |

|          | <b>CP1:CP0</b><br>11 = Code<br>10 = Uppe<br>01 = Uppe<br>00 = All m<br><b>Unimpler</b> | e protec<br>er half o<br>er 3/4 of<br>nemory i | tion off<br>f progra<br>f progra<br>is code | am men<br>Im men<br>protect | nory co<br>10ry co | •   |     |     |       |      |       |       |           |        |

| oit 3:   | <b>PWRTE</b> : F<br>1 = PWRT<br>0 = PWRT                                               | r disable                                      | ed                                          | r Enable                    | e bit              |     |     |     |       |      |       |       |           |        |

| oit 2:   | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                                                  | enabled                                        |                                             | Enable                      | bit                |     |     |     |       |      |       |       |           |        |

| bit 1-0: | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (                            | oscillato<br>oscillato<br>oscillator           | r<br>r<br>r                                 | or Sele                     | ction bi           | its |     |     |       |      |       |       |           |        |

# PIC16C9XX

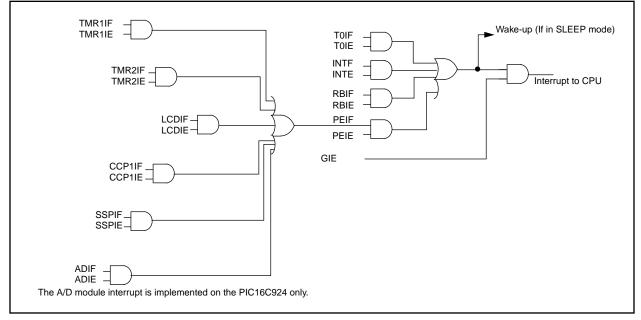

## FIGURE 14-14:INTERRUPT LOGIC

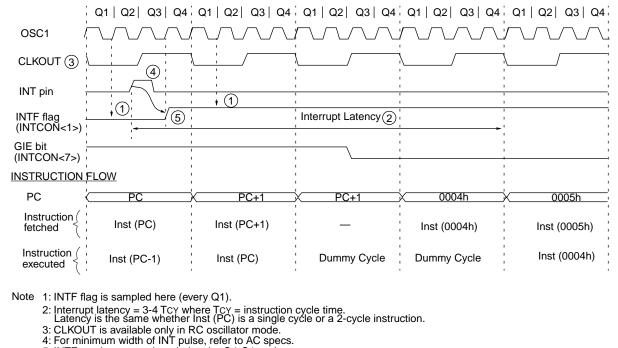

## FIGURE 14-15:INT PIN INTERRUPT TIMING

- 5: INTF can be set anytime during the Q4-Q1 cycles.

| CLRF              | Clear f                                                               |                               |                 |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] C                                                    | [ <i>label</i> ] CLRF f       |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 127$                                                     |                               |                 |                       |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                               |                 |                       |  |  |  |

| Status Affected:  | Z                                                                     |                               |                 |                       |  |  |  |

| Encoding:         | 00                                                                    | 0001                          | lfff            | ffff                  |  |  |  |

| Description:      | The conter<br>and the Z                                               | -                             | ster 'f' are    | cleared               |  |  |  |

| Words:            | 1                                                                     |                               |                 |                       |  |  |  |

| Cycles:           | 1                                                                     |                               |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                            | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f'       | Process<br>data | Write<br>register 'f' |  |  |  |

|                   |                                                                       |                               |                 |                       |  |  |  |

| Example           | CLRF                                                                  | FLAG                          | S_REG           |                       |  |  |  |

|                   | After Inst                                                            | FLAG_RE<br>ruction<br>FLAG_RE | EG =<br>EG =    | 0x5A<br>0x00          |  |  |  |

|                   |                                                                       | Z                             | =               | 1                     |  |  |  |

| CLRW              | Clear W                              |                  |                 |               |

|-------------------|--------------------------------------|------------------|-----------------|---------------|

| Syntax:           | [ label ]                            | CLRW             |                 |               |

| Operands:         | None                                 |                  |                 |               |

| Operation:        | $00h \rightarrow (V 1 \rightarrow Z$ | V)               |                 |               |

| Status Affected:  | Z                                    |                  |                 |               |

| Encoding:         | 00                                   | 0001             | 0xxx            | xxxx          |

| Description:      | W register<br>set.                   | is cleared       | . Zero bit (    | Z) is         |

| Words:            | 1                                    |                  |                 |               |

| Cycles:           | 1                                    |                  |                 |               |

| Q Cycle Activity: | Q1                                   | Q2               | Q3              | Q4            |

|                   | Decode                               | No-<br>Operation | Process<br>data | Write to<br>W |

| Example           | CLRW                                 |                  |                 |               |

|                   | Before In                            | struction        |                 |               |

|                   |                                      |                  | 0x5A            |               |

|                   | After Inst                           |                  | 0x00            |               |

|                   |                                      | VV =             | UXUU            |               |

| DECFSZ                    | Decreme                                                                                                                                                                                                                                     | nt f, Skip                                           | o if O                                                                                                                                                   |                                                                | GOTO                                    | Uncondi                                                                                                                                                                                       | tional Br           | anch            |                |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|