Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | ·                                                                          |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c924-08i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-1: PIC16C9XX PINOUT DESCRIPTION

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                       |

|-------------------|-------------|--------------|--------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 22          | 24           | 14           | I           | ST/CMOS        | Oscillator crystal input or external clock source input. This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.                                                 |

| OSC2/CLKOUT       | 23          | 25           | 15           | 0           | _              | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/VPP          | 1           | 2            | 57           | I/P         | ST             | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                                        |

|                   |             |              |              |             |                | PORTA is a bi-directional I/O port. The AN and VREF multi-<br>plexed functions are used by the PIC16C924 only.                                                                                                    |

| RA0/AN0           | 4           | 5            | 60           | I/O         | TTL            | RA0 can also be Analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 5           | 6            | 61           | I/O         | TTL            | RA1 can also be Analog input1.                                                                                                                                                                                    |

| RA2/AN2           | 7           | 8            | 63           | I/O         | TTL            | RA2 can also be Analog input2.                                                                                                                                                                                    |

| RA3/AN3/Vref      | 8           | 9            | 64           | I/O         | TTL            | RA3 can also be Analog input3 or A/D Voltage Reference.                                                                                                                                                           |

| RA4/T0CKI         | 9           | 10           | 1            | I/O         | ST             | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                           |

| RA5/AN4/SS        | 10          | 11           | 2            | I/O         | TTL            | RA5 can be the slave select for the synchronous serial port or Analog input4.                                                                                                                                     |

|                   |             |              |              |             |                | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                                                                                    |

| RB0/INT           | 12          | 13           | 4            | I/O         | TTL/ST         | RB0 can also be the external interrupt pin. This buffer<br>is a Schmitt Trigger input when configured as an exter-<br>nal interrupt.                                                                              |

| RB1               | 11          | 12           | 3            | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB2               | 3           | 4            | 59           | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB3               | 2           | 3            | 58           | I/O         | TTL            |                                                                                                                                                                                                                   |

| RB4               | 64          | 68           | 56           | I/O         | TTL            | Interrupt on change pin.                                                                                                                                                                                          |

| RB5               | 63          | 67           | 55           | I/O         | TTL            | Interrupt on change pin.                                                                                                                                                                                          |

| RB6               | 61          | 65           | 53           | I/O         | TTL/ST         | Interrupt on change pin. Serial programming clock.<br>This buffer is a Schmitt Trigger input when used in<br>serial programming mode.                                                                             |

| RB7               | 62          | 66           | 54           | I/O         | TTL/ST         | Interrupt on change pin. Serial programming data<br>This buffer is a Schmitt Trigger input when used in<br>serial programming mode.                                                                               |

|                   |             |              |              |             |                | PORTC is a bi-directional I/O port.                                                                                                                                                                               |

| RC0/T1OSO/T1CKI   | 24          | 26           | 16           | I/O         | ST             | RC0 can also be the Timer1 oscillator output or<br>Timer1 clock input.                                                                                                                                            |

| RC1/T1OSI         | 25          | 27           | 17           | I/O         | ST             | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                      |

| RC2/CCP1          | 26          | 28           | 18           | I/O         | ST             | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                              |

| RC3/SCK/SCL       | 13          | 14           | 5            | I/O         | ST             | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                                |

| RC4/SDI/SDA       | 14          | 15           | 6            | I/O         | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).                                                                                                                                          |

| RC5/SDO           | 15          | 16           | 7            | I/O         | ST             | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                      |

| C1                | 16          | 17           | 8            | Р           |                | LCD Voltage Generation.                                                                                                                                                                                           |

| C2                | 17          | 18           | 9            | Р           |                | LCD Voltage Generation.                                                                                                                                                                                           |

| Legend: I = input | O = ou      | tput         |              | P = pow     | er<br>TL input | L = LCD Driver<br>ST = Schmitt Trigger input                                                                                                                                                                      |

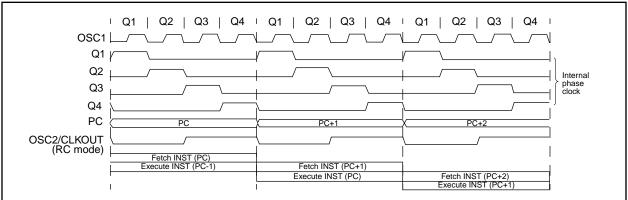

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3.

### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

|                                                                                                                                                                                                                    | Tcy0    | Tcy1      | Tcy2      | Tcy3      | Tcy4        | Tcy5          |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|-----------|-----------|-------------|---------------|--|--|--|--|--|

| 1. MOVLW 55h                                                                                                                                                                                                       | Fetch 1 | Execute 1 |           |           |             |               |  |  |  |  |  |

| 2. MOVWF PORTB                                                                                                                                                                                                     |         | Fetch 2   | Execute 2 |           |             |               |  |  |  |  |  |

| 3. CALL SUB_1                                                                                                                                                                                                      |         |           | Fetch 3   | Execute 3 |             |               |  |  |  |  |  |

| 4. BSF PORTA, BIT3 (Forced NOP) Fetch 4 Flush                                                                                                                                                                      |         |           |           |           |             |               |  |  |  |  |  |

| 5. Instruction @ addres                                                                                                                                                                                            | s SUB_1 |           |           |           | Fetch SUB_1 | Execute SUB_1 |  |  |  |  |  |

|                                                                                                                                                                                                                    |         |           |           |           |             |               |  |  |  |  |  |

|                                                                                                                                                                                                                    |         |           |           |           |             |               |  |  |  |  |  |

| All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed. |         |           |           |           |             |               |  |  |  |  |  |

# TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address            | Name    | Bit 7         | Bit 6                                        | Bit 5                   | Bit 4          | Bit 3        | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|---------------|----------------------------------------------|-------------------------|----------------|--------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 1             | ·       | •             |                                              |                         |                |              | ·                |                |          | •                             |                           |

| 80h                | INDF    | Addressing    | this location                                | uses conten             | ts of FSR to   | address data | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 81h                | OPTION  | RBPU          | INTEDG                                       | TOCS                    | T0SE           | PSA          | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 82h                | PCL     | Program Co    | rogram Counter's (PC) Least Significant Byte |                         |                |              |                  |                |          |                               | 0000 0000                 |

| 83h                | STATUS  | IRP           | RP1                                          | RP0                     | TO             | PD           | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 84h                | FSR     | Indirect data | a memory ad                                  | dress pointe            | r              |              |                  |                |          | XXXX XXXX                     | uuuu uuuu                 |

| 85h                | TRISA   | —             | _                                            | PORTA Dat               | a Direction R  | egister      |                  |                |          | 11 1111                       | 11 1111                   |

| 86h                | TRISB   | PORTB Dat     | a Direction R                                | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 87h                | TRISC   | —             | _                                            | PORTC Da                | ta Direction F | Register     |                  |                |          | 11 1111                       | 11 1111                   |

| 88h                | TRISD   | PORTD Dat     | a Direction F                                | Register                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 89h                | TRISE   | PORTE Dat     | a Direction R                                | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 8Ah                | PCLATH  | —             | _                                            | —                       | Write Buffer   | for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 8Bh                | INTCON  | GIE           | PEIE                                         | T0IE                    | INTE           | RBIE         | T0IF             | INTF           | RBIF     | 0000 000x                     | 0000 000u                 |

| 8Ch                | PIE1    | LCDIE         | ADIE <sup>(2)</sup>                          | —                       | _              | SSPIE        | CCP1IE           | TMR2IE         | TMR1IE   | 00 0000                       | 00 0000                   |

| 8Dh                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | _                         |

| 8Eh                | PCON    | —             | _                                            | —                       | _              | _            | _                | POR            | —        | 0-                            | u-                        |

| 8Fh                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | _                         |

| 90h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | —                             | —                         |

| 91h                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | _                         |

| 92h                | PR2     | Timer2 Peri   | od Register                                  |                         |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 93h                | SSPADD  | Synchronou    | is Serial Port                               | (I <sup>2</sup> C mode) | Address Reg    | ister        |                  |                |          | 0000 0000                     | 0000 0000                 |

| 94h                | SSPSTAT | SMP           | CKE                                          | D/Ā                     | Р              | S            | R/W              | UA             | BF       | 0000 0000                     | 0000 0000                 |

| 95h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 96h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 97h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 98h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 99h                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 9Ah                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | _                         |

| 9Bh                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | -                             | —                         |

| 9Ch                | —       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | —                         |

| 9Dh                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | —                             | —                         |

| 9Eh                | _       | Unimpleme     | nted                                         |                         |                |              |                  |                |          | _                             | _                         |

| 9Fh <sup>(1)</sup> | ADCON1  |               | —                                            | _                       |                | _            | PCFG2            | PCFG1          | PCFG0    | 000                           | 000                       |

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0',

Note

shaded locations are unimplemented, read as '0'. 1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

These bits are reserved on the PIC16C923, always maintain these bits clear.

These pixels do not display, but can be used as general purpose RAM.

PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

# TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address | Name   | Bit 7         | Bit 6          | Bit 5       | Bit 4        | Bit 3          | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|--------|---------------|----------------|-------------|--------------|----------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 3  |        |               |                |             |              |                |                  |                |          |                               |                           |

| 180h    | INDF   | Addressing    | this location  | uses conten | ts of FSR to | address data   | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 181h    | OPTION | RBPU          | INTEDG         | TOCS        | T0SE         | PSA            | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 182h    | PCL    | Program Co    | ounter's (PC)  |             | 0000 0000    | 0000 0000      |                  |                |          |                               |                           |

| 183h    | STATUS | IRP           | RP1            | RP0         | TO           | PD             | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 184h    | FSR    | Indirect data | a memory ad    |             | XXXX XXXX    | uuuu uuuu      |                  |                |          |                               |                           |

| 185h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 186h    | TRISB  | PORTB Dat     | ta Direction R | egister     |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 187h    | TRISF  | PORTF Dat     | a Direction R  | egister     |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 188h    | TRISG  | PORTG Da      | ta Direction F | Register    |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 189h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 18Ah    | PCLATH | _             | _              | _           | Write Buffe  | r for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 18Bh    | INTCON | GIE           | PEIE           | TOIE        | INTE         | RBIE           | TOIF             | INTF           | RBIF     | 0000 000x                     | 0000 000u                 |

| 18Ch    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 18Dh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 18Eh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 18Fh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 190h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 191h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 192h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 193h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 194h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 195h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 196h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 197h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 198h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 199h    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 19Ah    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | -                             | _                         |

| 19Bh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | —                         |

| 19Ch    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | —                         |

| 19Dh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 19Eh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

| 19Fh    | _      | Unimpleme     | nted           |             |              |                |                  |                |          | _                             | _                         |

Legend:

d: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0', shaded locations are unimplemented, read as '0'.

1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

2: These bits are reserved on the PIC16C923, always maintain these bits clear.

3: These pixels do not display, but can be used as general purpose RAM.

4: PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

5: Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear. Note

#### 4.2.2.1 STATUS REGISTER

The STATUS register, shown in Figure 4-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

Note 1: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# FIGURE 4-3: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

| R/W-0       | R/W-0                                                                | R/W-0                                    | R-1                                 | R-1                                       | R/W-x                                                                                                            | R/W-x                       | R/W-x                        |                                                                                                           |

|-------------|----------------------------------------------------------------------|------------------------------------------|-------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|

| IRP<br>bit7 | RP1                                                                  | RP0                                      | TO                                  | PD                                        | Z                                                                                                                | DC                          | C<br>bit0                    | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:      | <b>IRP</b> : Regis<br>1 = Bank 2<br>0 = Bank (                       | 2, 3 (100h                               | - 1FFh)                             | used for ir                               | ndirect addr                                                                                                     | essing)                     |                              |                                                                                                           |

| bit 6-5:    | <b>RP1:RP0</b> :<br>11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | 3 (180h -<br>2 (100h -<br>1 (80h - F     | 1FFh)<br>17Fh)<br><sup>-</sup> Fh)  | ct bits (use                              | ed for direct                                                                                                    | addressin                   | g)                           |                                                                                                           |

| bit 4:      | $\overline{\mathbf{TO}}$ : Time-o<br>1 = After p<br>0 = A WD         | ower-up,                                 |                                     | struction, c                              | or SLEEP ins                                                                                                     | struction                   |                              |                                                                                                           |

| bit 3:      | <b>PD</b> : Power<br>1 = After p<br>0 = By exe                       | ower-up c                                |                                     |                                           |                                                                                                                  |                             |                              |                                                                                                           |

| bit 2:      |                                                                      | sult of an                               |                                     |                                           | peration is z                                                                                                    |                             |                              |                                                                                                           |

| bit 1:      | 1 = A carry                                                          | y-out from                               | the 4th lo                          | w order bit                               | , SUBLW , SU<br>t of the resu<br>bit of the res                                                                  | It occurred                 | , ,                          | porrow the polarity is reversed)                                                                          |

| bit 0:      | 1 = A carry<br>0 = No car<br>Note: A su                              | y-out from<br>rry-out from<br>ubtraction | the most<br>n the mos<br>is execute | significant<br>t significar<br>d by addir | bit of the rent bit of the two's | esult occuri<br>result occu | red<br>irred<br>ent of the s | the polarity is reversed)<br>econd operand. For rotate (RRE<br>ne source register.                        |

# PIC16C9XX

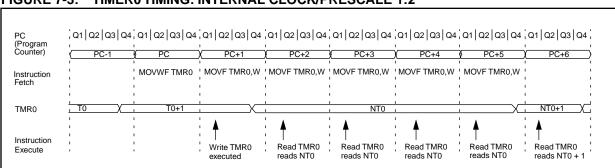

# FIGURE 7-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

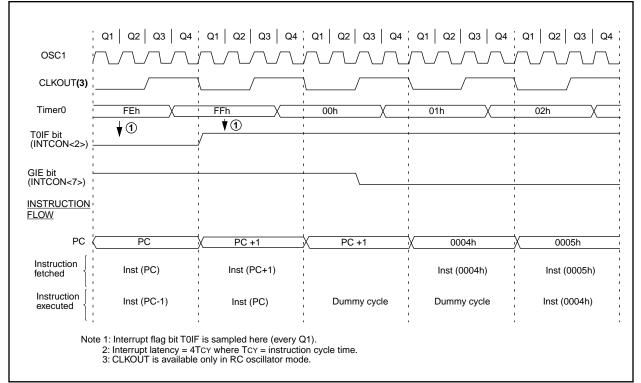

#### FIGURE 7-4: **TIMER0 INTERRUPT TIMING**

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

| Note: | To avoid an unintended device RESET, the |  |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | following instruction sequence (shown in |  |  |  |  |  |  |  |  |  |  |

|       | Example 7-1) must be executed when       |  |  |  |  |  |  |  |  |  |  |

|       | changing the prescaler assignment from   |  |  |  |  |  |  |  |  |  |  |

|       | Timer0 to the WDT. This precaution must  |  |  |  |  |  |  |  |  |  |  |

|       | be followed even if the WDT is disabled. |  |  |  |  |  |  |  |  |  |  |

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 → WDT)

|                                                                          | 1)  | BSF    | STATUS, RPO | ;Select Bank1                              |

|--------------------------------------------------------------------------|-----|--------|-------------|--------------------------------------------|

| Lines 2 and 3 do NOT have to                                             | 2)  | MOVLW  | b'xx0x0xxx' | ;Select clock source and prescale value of |

| be included if the final desired                                         | 3)  | MOVWF  | OPTION_REG  | ;other than 1:1                            |

| prescale value is other than 1:1.<br>If 1:1 is final desired value, then | 4)  | BCF    | STATUS, RPO | ;Select Bank0                              |

| a temporary prescale value is                                            | 5)  | CLRF   | TMR0        | ;Clear TMR0 and prescaler                  |

| set in lines 2 and 3 and the fina                                        | 6)  | BSF    | STATUS, RP1 | ;Select Bankl                              |

| prescale value will be set in lines                                      | 7)  | MOVLW  | b'xxxx1xxx' | ;Select WDT, do not change prescale value  |

| 10 and 11.                                                               | 8)  | MOVWF  | OPTION_REG  | ;                                          |

|                                                                          | 9)  | CLRWDT |             | ;Clears WDT and prescaler                  |

|                                                                          | 10) | MOVLW  | b'xxxx1xxx' | ;Select new prescale value and WDT         |

|                                                                          | 11) | MOVWF  | OPTION_REG  | ;                                          |

|                                                                          | 12) | BCF    | STATUS, RPO | ;Select Bank0                              |

|                                                                          |     |        |             |                                            |

To change prescaler from the WDT to the Timer0 module use the precaution shown in Example 7-2.

### EXAMPLE 7-2: CHANGING PRESCALER (WDT → TIMER0)

| CLRWDT |             | ;Clear WDT and prescaler             |

|--------|-------------|--------------------------------------|

| BSF    | STATUS, RPO | ;Select Bank1                        |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new prescale value and |

| MOVWF  | OPTION_REG  | ;clock source                        |

| BCF    | STATUS, RPO | ;Select Bank0                        |

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address                 | Name   | Bit 7  | Bit 6                            | Bit 5    | Bit 4       | Bit 3      | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|--------|--------|----------------------------------|----------|-------------|------------|-------|---------|---------|-------------------------------|---------------------------|

| 01h, 101h               | TMR0   | Timer0 | imer0 module's register xxxx xxx |          |             |            |       |         |         |                               |                           |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE                             | TOIE     | INTE        | RBIE       | TOIF  | INTF    | RBIF    | 0000 000x                     | 0000 000u                 |

| 81h, 181h               | OPTION | RBPU   | INTEDG                           | TOCS     | TOSE        | PSA        | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                 |

| 85h                     | TRISA  | _      | _                                | PORTA Da | ta Directio | on Control |       | 11 1111 | 11 1111 |                               |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

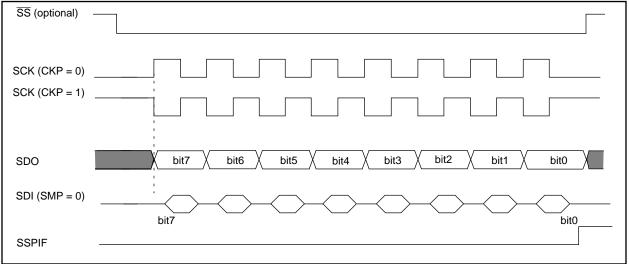

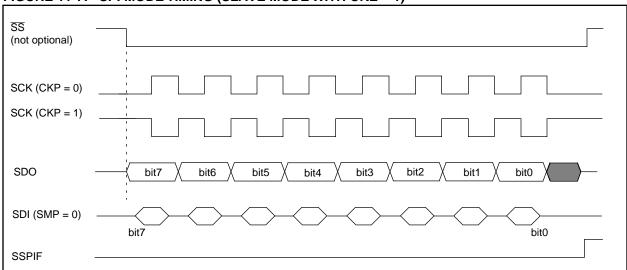

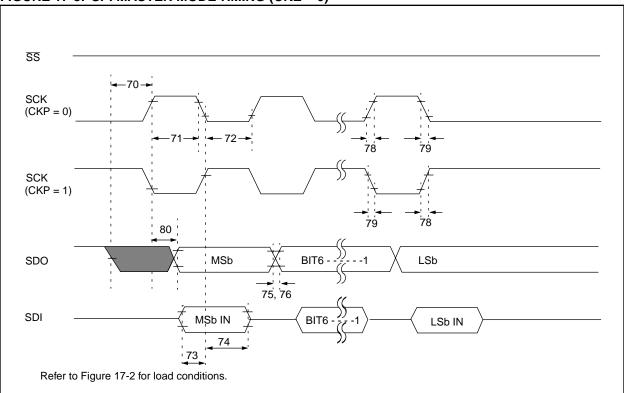

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

- Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- **Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

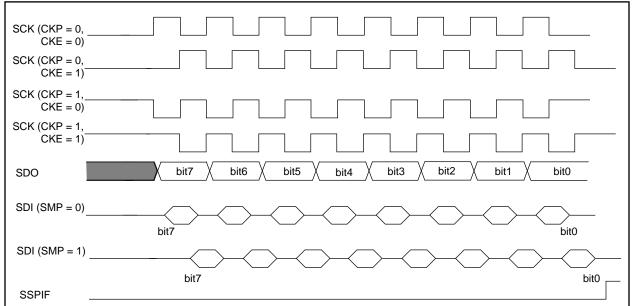

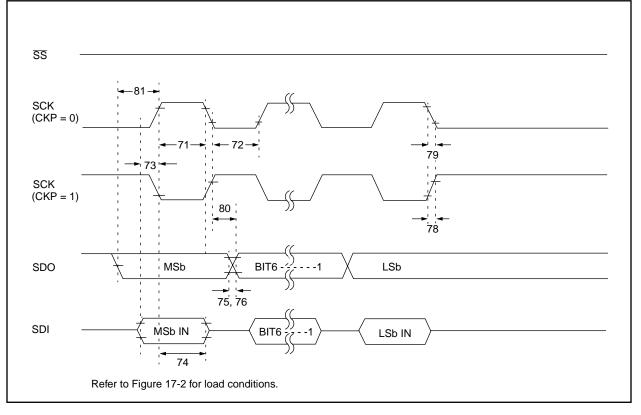

# FIGURE 11-5: SPI MODE TIMING, MASTER MODE

# FIGURE 11-6: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

# FIGURE 11-7: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

| Address                 | Name    | Bit 7   | Bit 6               | Bit 5       | Bit 4         | Bit 3        | Bit 2   | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|---------|---------|---------------------|-------------|---------------|--------------|---------|--------|--------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                | TOIE        | INTE          | RBIE         | TOIF    | INTF   | RBIF   | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1    | LCDIF   | ADIF <sup>(1)</sup> | _           | _             | SSPIF        | CCP1IF  | TMR2IF | TMR1IF | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1    | LCDIE   | ADIE <sup>(1)</sup> | —           | _             | SSPIE        | CCP1IE  | TMR2IE | TMR1IE | 00 0000                       | 00 0000                   |

| 13h                     | SSPBUF  | Synchro | nous Serial         | Port Receiv | ve Buffer/Tra | ansmit Reg   | ster    | -      |        | XXXX XXXX                     | uuuu uuuu                 |

| 14h                     | SSPCON  | WCOL    | SSPOV               | SSPEN       | СКР           | SSPM3        | SSPM2   | SSPM1  | SSPM0  | 0000 0000                     | 0000 0000                 |

| 85h                     | TRISA   | _       | _                   | PORTA Da    | ata Direction | n Control Re | egister |        |        | 11 1111                       | 11 1111                   |

| 87h                     | TRISC   | _       | _                   | PORTC D     | ata Directio  | 11 1111      | 11 1111 |        |        |                               |                           |

| 94h                     | SSPSTAT | SMP     | CKE                 | D/Ā         | Р             | S            | R/W     | UA     | BF     | 0000 0000                     | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: Bits ADIE and ADIF are reserved on the PIC16C923, always maintain these bits clear.

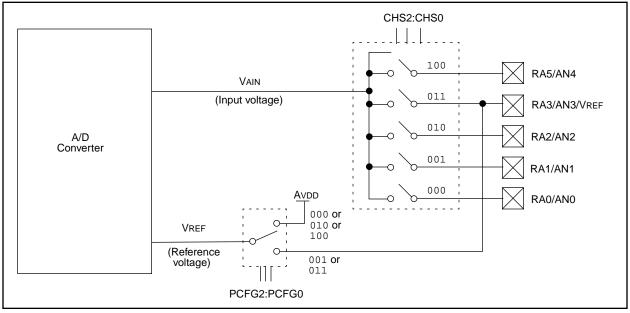

# FIGURE 12-3: A/D BLOCK DIAGRAM

# 12.8 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

# 12.9 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

# 12.10 Transfer Function

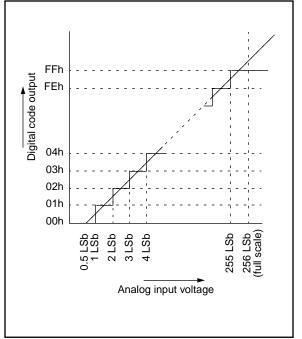

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is Analog VREF / 256 (Figure 12-5).

#### 13.6 **Configuring the LCD Module**

The following is the sequence of steps to follow to configure the LCD module.

- 1. Select the frame clock prescale using bits LP3:LP0 (LCDPS<3:0>).

- 2. Configure the appropriate pins to function as segment drivers using the LCDSE register.

- 3. Configure the LCD module for the following using the LCDCON register.

- Multiplex mode and Bias, bits -LMUX1:LMUX0

- Timing source, bits CS1:CS0

- Voltage generation, bit VGEN

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCDD00 through LCDD15.

- 5. Clear LCD interrupt flag, LCDIF (PIR1<7>), and if desired, enable the interrupt by setting bit LCDIE (PIE1<7>).

- 6. Enable the LCD module, by setting bit LCDEN (LCDCON<7>).

# TABLE 13-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE LCD MODULE

| Address                 | Name   | Bit 7                        | Bit 6                        | Bit 5                        | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|-------------------------|--------|------------------------------|------------------------------|------------------------------|---------------|---------------|---------------|---------------|---------------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                          | PEIE                         | TOIE                         | INTE          | RBIE          | TOIF          | INTF          | RBIF          | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1   | LCDIF                        | ADIF <sup>(1)</sup>          | _                            | _             | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF        | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1   | LCDIE                        | ADIE <sup>(1)</sup>          | _                            | _             | SSPIE         | CCP1IE        | TMR2IE        | TMR1IE        | 00 0000                       | 00 0000                         |

| 10h                     | T1CON  | _                            | _                            | T1CKPS1                      | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS        | TMR10N        | 00 0000                       | uu uuuu                         |

| 10Dh                    | LCDSE  | SE29                         | SE27                         | SE20                         | SE16          | SE12          | SE9           | SE5           | SE0           | 1111 1111                     | 1111 1111                       |

| 10Eh                    | LCDPS  | _                            | _                            | _                            | _             | LP3           | LP2           | LP1           | LP0           | 0000                          | 0000                            |

| 10Fh                    | LCDCON | LCDEN                        | SLPEN                        | _                            | VGEN          | CS1           | CS0           | LMUX1         | LMUX0         | 00-0 0000                     | 00-0 0000                       |

| 110h                    | LCDD00 | SEG07<br>COM0                | SEG06<br>COM0                | SEG05<br>COM0                | SEG04<br>COM0 | SEG03<br>COM0 | SEG02<br>COM0 | SEG01<br>COM0 | SEG00<br>COM0 | xxxx xxxx                     | uuuu uuuu                       |

| 111h                    | LCDD01 | SEG15<br>COM0                | SEG14<br>COM0                | SEG13<br>COM0                | SEG12<br>COM0 | SEG11<br>COM0 | SEG10<br>COM0 | SEG09<br>COM0 | SEG08<br>COM0 | xxxx xxxx                     | սսսս սսսս                       |

| 112h                    | LCDD02 | SEG23<br>COM0                | SEG22<br>COM0                | SEG21<br>COM0                | SEG20<br>COM0 | SEG19<br>COM0 | SEG18<br>COM0 | SEG17<br>COM0 | SEG16<br>COM0 | xxxx xxxx                     | uuuu uuuu                       |

| 113h                    | LCDD03 | SEG31<br>COM0                | SEG30<br>COM0                | SEG29<br>COM0                | SEG28<br>COM0 | SEG27<br>COM0 | SEG26<br>COM0 | SEG25<br>COM0 | SEG24<br>COM0 | xxxx xxxx                     | uuuu uuuu                       |

| 114h                    | LCDD04 | SEG07<br>COM1                | SEG06<br>COM1                | SEG05<br>COM1                | SEG04<br>COM1 | SEG03<br>COM1 | SEG02<br>COM1 | SEG01<br>COM1 | SEG00<br>COM1 | xxxx xxxx                     | uuuu uuuu                       |

| 115h                    | LCDD05 | SEG15<br>COM1                | SEG14<br>COM1                | SEG13<br>COM1                | SEG12<br>COM1 | SEG11<br>COM1 | SEG10<br>COM1 | SEG09<br>COM1 | SEG08<br>COM1 | xxxx xxxx                     | uuuu uuuu                       |

| 116h                    | LCDD06 | SEG23<br>COM1                | SEG22<br>COM1                | SEG21<br>COM1                | SEG20<br>COM1 | SEG19<br>COM1 | SEG18<br>COM1 | SEG17<br>COM1 | SEG16<br>COM1 | xxxx xxxx                     | uuuu uuuu                       |

| 117h                    | LCDD07 | SEG31<br>COM1 <sup>(2)</sup> | SEG30<br>COM1                | SEG29<br>COM1                | SEG28<br>COM1 | SEG27<br>COM1 | SEG26<br>COM1 | SEG25<br>COM1 | SEG24<br>COM1 | xxxx xxxx                     | սսսս սսսս                       |

| 118h                    | LCDD08 | SEG07<br>COM2                | SEG06<br>COM2                | SEG05<br>COM2                | SEG04<br>COM2 | SEG03<br>COM2 | SEG02<br>COM2 | SEG01<br>COM2 | SEG00<br>COM2 | xxxx xxxx                     | uuuu uuuu                       |

| 119h                    | LCDD09 | SEG15<br>COM2                | SEG14<br>COM2                | SEG13<br>COM2                | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG09<br>COM2 | SEG08<br>COM2 | xxxx xxxx                     | uuuu uuuu                       |

| 11Ah                    | LCDD10 | SEG23<br>COM2                | SEG22<br>COM2                | SEG21<br>COM2                | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | xxxx xxxx                     | uuuu uuuu                       |

| 11Bh                    | LCDD11 | SEG31<br>COM2 <sup>(2)</sup> | SEG30<br>COM2 <sup>(2)</sup> | SEG29<br>COM2                | SEG28<br>COM2 | SEG27<br>COM2 | SEG26<br>COM2 | SEG25<br>COM2 | SEG24<br>COM2 | xxxx xxxx                     | uuuu uuuu                       |

| 11Ch                    | LCDD12 | SEG07<br>COM3                | SEG06<br>COM3                | SEG05<br>COM3                | SEG04<br>COM3 | SEG03<br>COM3 | SEG02<br>COM3 | SEG01<br>COM3 | SEG00<br>COM3 | xxxx xxxx                     | uuuu uuuu                       |

| 11Dh                    | LCDD13 | SEG15<br>COM3                | SEG14<br>COM3                | SEG13<br>COM3                | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG09<br>COM3 | SEG08<br>COM3 | xxxx xxxx                     | uuuu uuuu                       |

| 11Eh                    | LCDD14 | SEG23<br>COM3                | SEG22<br>COM3                | SEG21<br>COM3                | SEG20<br>COM3 | SEG19<br>COM3 | SEG18<br>COM3 | SEG17<br>COM3 | SEG16<br>COM3 | xxxx xxxx                     | uuuu uuuu                       |

| 11Fh                    | LCDD15 | SEG31<br>COM3 <sup>(2)</sup> | SEG30<br>COM3 <sup>(2)</sup> | SEG29<br>COM3 <sup>(2)</sup> | SEG28<br>COM3 | SEG27<br>COM3 | SEG26<br>COM3 | SEG25<br>COM3 | SEG24<br>COM3 | xxxx xxxx                     | uuuu uuuu                       |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the LCD Module.

These bits are reserved on the PIC16C923, always maintain these bits clear. Legend:

Note 2: These pixels do not display, but can be used as general purpose RAM.

| Register Applica    |     | le Devices | Power-on Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |  |

|---------------------|-----|------------|----------------|--------------------------|------------------------------------|--|

| PORTD               | 923 | 924        | 0000 0000      | 0000 0000                | սսսս սսսս                          |  |

| PORTE               | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| PCLATH              | 923 | 924        | 0 0000         | 0 0000                   | u uuuu                             |  |

| INTCON              | 923 | 924        | x000 0000x     | 0000 000u                | սսսս սսսս(1)                       |  |

| PIR1 <sup>(4)</sup> | 923 | 924        | 00 0000        | 00 0000                  | uu uuuu <b>(1)</b>                 |  |

| TMR1L               | 923 | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |  |

| TMR1H               | 923 | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |  |

| T1CON               | 923 | 924        | 00 0000        | uu uuuu                  | uu uuuu                            |  |

| TMR2                | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| T2CON               | 923 | 924        | -000 0000      | -000 0000                | -uuu uuuu                          |  |

| SSPBUF              | 923 | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |  |

| SSPCON              | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| CCPR1L              | 923 | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |  |

| CCPR1H              | 923 | 924        | XXXX XXXX      | uuuu uuuu                | uuuu uuuu                          |  |

| CCP1CON             | 923 | 924        | 00 0000        | 00 0000                  | uu uuuu                            |  |

| ADRES               | 923 | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |  |

| ADCON0              | 923 | 924        | 0000 00-0      | 0000 00-0                | uuuu uu-u                          |  |

| OPTION              | 923 | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |  |

| TRISA               | 923 | 924        | 11 1111        | 11 1111                  | uu uuuu                            |  |

| TRISB               | 923 | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |  |

| TRISC               | 923 | 924        | 11 1111        | 11 1111                  | uu uuuu                            |  |

| TRISD               | 923 | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |  |

| TRISE               | 923 | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |  |

| PIE1 <sup>(4)</sup> | 923 | 924        | 00 0000        | 00 0000                  | uu uuuu                            |  |

| PCON                | 923 | 924        | 0-             | u-                       | u-                                 |  |

| PR2                 | 923 | 924        | 1111 1111      | 1111 1111                | 1111 1111                          |  |

| SSPADD              | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| SSPSTAT             | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| ADCON1              | 923 | 924        | 000            | 000                      | uuu                                |  |

| PORTF               | 923 | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |  |

| PORTG               | 923 | 924        | 0000 0000      | 0000 0000                | นนนน นนนน                          |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on conditionNote 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-5 for reset value for specific condition.

4: Bits PIE1<6> and PIR1<6> are reserved on the PIC16C923, always maintain these bits clear.

5: PORTA values when read.

# 14.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or some peripheral interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. A/D conversion (when A/D clock source is RC).

- 6. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 7. LCD module.

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# FIGURE 17-8: SPI MASTER MODE TIMING (CKE = 0)

# FIGURE 17-9: SPI MASTER MODE TIMING (CKE = 1)

# PIC16C9XX

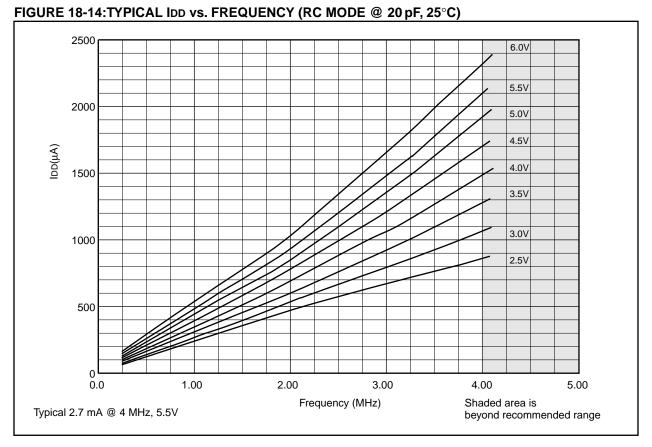

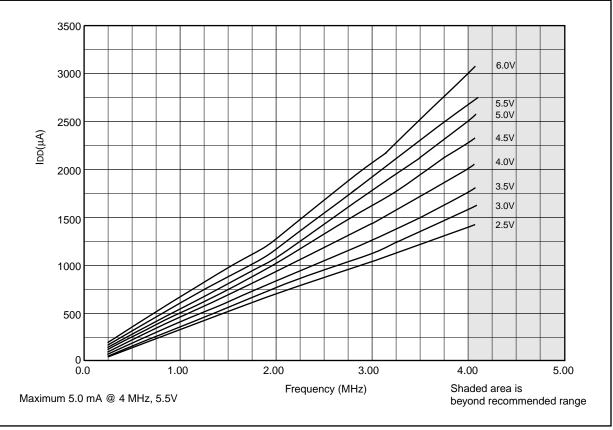

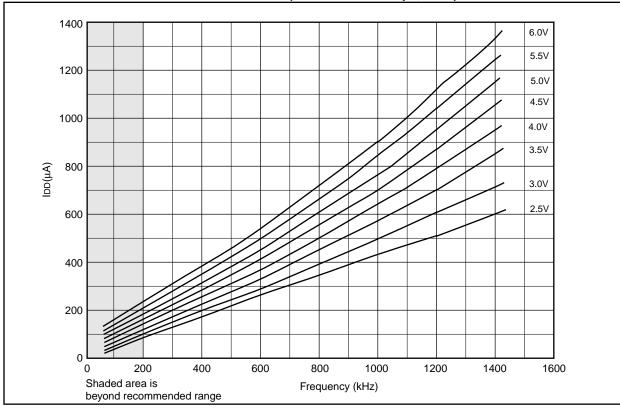

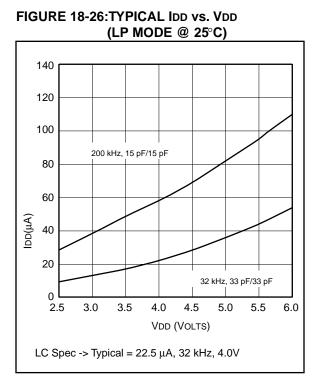

FIGURE 18-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 20 pF, -40°C TO +85°C)

FIGURE 18-16:TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

Data based on process characterization samples. See first page of this section for details.

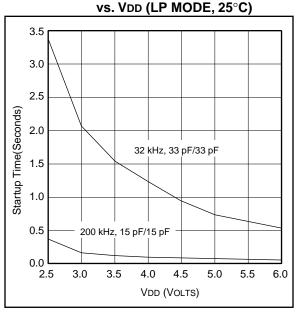

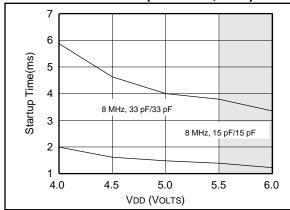

FIGURE 18-23: TYPICAL XTAL STARTUP TIME

FIGURE 18-24:TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

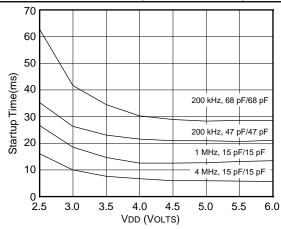

FIGURE 18-25:TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

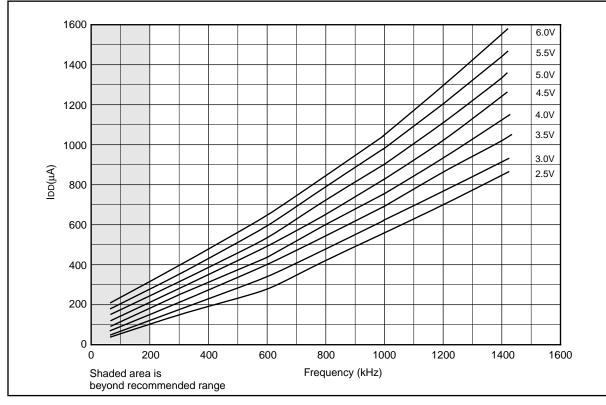

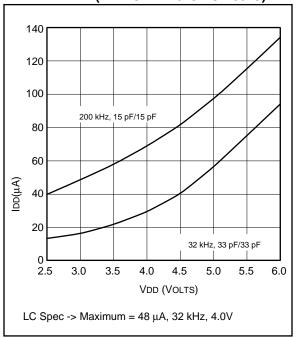

FIGURE 18-27:MAXIMUM IDD vs. VDD (LP MODE -40°C TO +85°C)

# PIC16C9XX

NOTES:

| Table 9 2:        | Pagisters Associated with Timer1 as a                                            |

|-------------------|----------------------------------------------------------------------------------|

| Table 8-2:        | Registers Associated with Timer1 as a<br>Timer/counter54                         |

| Table 9-1:        | Registers Associated with Timer2 as a                                            |

|                   | Timer/Counter56                                                                  |

| Table 10-1:       | CCP Mode - Timer Resource57                                                      |

| Table 10-2:       | Example PWM Frequencies and                                                      |

|                   | Resolutions at 8 MHz60                                                           |

| Table 10-3:       | Registers Associated with Timer1,                                                |

|                   | Capture and Compare                                                              |

| Table 10-4:       | Registers Associated with PWM and<br>Timer261                                    |

| Table 11-1:       | Registers Associated with SPI Operation 68                                       |

| Table 11-2:       | I <sup>2</sup> C Bus Terminology                                                 |

| Table 11-3:       | Data Transfer Received Byte Actions                                              |

| Table 11-4:       | Registers Associated with I <sup>2</sup> C Operation77                           |

| Table 12-1:       | TAD vs. Device Operating Frequencies 83                                          |

| Table 12-2:       | Summary of A/D Registers                                                         |

| Table 13-1:       | Frame Frequency Formulas96                                                       |

| Table 13-2:       | Approx. Frame Freq in Hz using Timer1 @                                          |

| <b>T</b>     10.0 | 32.768 kHz or Fosc @ 8 MHz                                                       |

| Table 13-3:       | Approx. Frame Freq in Hz using internal<br>RC osc @ 14 kHz96                     |

| Table 13-4:       | Summary of Registers Associated with                                             |

| Table 13-4.       | the LCD Module                                                                   |

| Table 14-1:       | Ceramic Resonators                                                               |

| Table 14-2:       | Capacitor Selection for Crystal Oscillator . 104                                 |

| Table 14-3:       | Time-out in Various Situations                                                   |

| Table 14-4:       | Status Bits and Their Significance                                               |

| Table 14-5:       | Reset Condition for Special Registers 108                                        |

| Table 14-6:       | Initialization Conditions for all Registers 108                                  |

| Table 15-1:       | Opcode Field Descriptions119                                                     |

| Table 15-2:       | PIC16CXXX Instruction Set120                                                     |

| Table 16-1:       | development tools from microchip                                                 |

| Table 17-1:       | Cross Reference of Device Specs for<br>Oscillator Configurations and Frequencies |

|                   | of Operation (Commercial Devices)                                                |

| Table 17-2:       | LCD Module Electrical Specifications 145                                         |

| Table 17-3:       | VLCD Charge Pump Electrical                                                      |

|                   | Specifications145                                                                |

| Table 17-4:       | External Clock Timing Requirements 148                                           |

| Table 17-5:       | CLKOUT and I/O Timing Requirements 149                                           |

| Table 17-6:       | Reset, Watchdog Timer, Oscillator                                                |

|                   | Start-up Timer and Power-up Timer                                                |

|                   | Requirements                                                                     |

| Table 17-7:       | Timer0 and Timer1 External Clock                                                 |

| Table 17-8:       | Requirements151<br>Capture/Compare/PWM Requirements152                           |

| Table 17-9:       | SPI Mode Requirements                                                            |

| Table 17-3.       | I <sup>2</sup> C Bus Start/Stop Bits Requirements 156                            |

| Table 17-11:      | I <sup>2</sup> C Bus Data Requirements                                           |

| Table 17-12:      | A/D Converter Characteristics:                                                   |

|                   | PIC16C924-04 (Commercial, Industrial)                                            |

|                   | PIC16LC924-04 (Commercial, Industrial). 158                                      |

| Table 17-13:      | A/D Conversion Requirements 159                                                  |

| Table 18-1:       | RC Oscillator Frequencies167                                                     |