Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923-04-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-1: PIC16C9XX PINOUT DESCRIPTION (Cont.'d)

| Pin Name                        | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin#   | Pin<br>Type                                  | Buffer<br>Type | Description                                                                     |

|---------------------------------|-------------|--------------|----------------|----------------------------------------------|----------------|---------------------------------------------------------------------------------|

| VLCD3                           | 19          | 20           | 11             | Р                                            | _              | LCD Voltage.                                                                    |

| Vdd                             | 20, 60      | 22, 64       | 12, 52         | Р                                            | —              | Digital power.                                                                  |

| Vss                             | 6, 21       | 7, 23        | 13, 62         | Р                                            | _              | Ground reference.                                                               |

| NC                              | -           | 1            | _              | _                                            | —              | These pins are not internally connected. These pins should be left unconnected. |

| Legend: I = input<br>— = Not us |             | P = pow      | er<br>TL input | L = LCD Driver<br>ST = Schmitt Trigger input |                |                                                                                 |

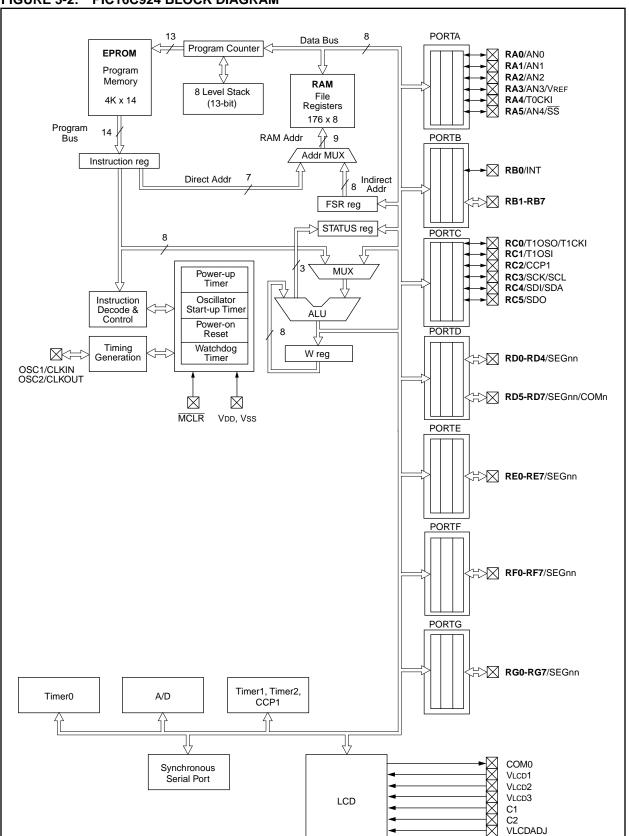

## 4.0 MEMORY ORGANIZATION

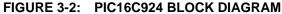

## 4.1 Program Memory Organization

The PIC16C9XX family has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

Only the first 4K x 14 (0000h-0FFFh) is physically implemented. Accessing a location above the physically implemented addresses will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

## 4.2 Data Memory Organization

The data memory is partitioned into four Banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

11 = Bank 3 (180h-1FFh)

10 = Bank 2 (100h-17Fh)

01 = Bank 1 (80h-FFh)

00 = Bank 0 (00h-7Fh)

The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. All four banks contain special function registers. Some "high use" special function registers are mirrored in other banks for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

The following General Purpose Registers are not physically implemented:

- F0h-FFh of Bank 1

- 170h-17Fh of Bank 2

- 1F0h-1FFh of Bank 3

These locations are used for common access across banks.

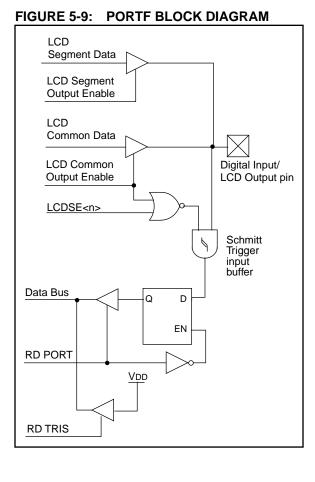

#### 5.6 PORTF and TRISF Register

PORTF is an digital input only port. Each pin is multiplexed with an LCD segment driver. These pins have Schmitt Trigger input buffers.

- **Note 1:** On a Power-on Reset these pins are configured as LCD segment drivers.

- Note 2: To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

## EXAMPLE 5-6: INITIALIZING PORTF

| BCF STATUS, RP0 | ;Select Bank2   |

|-----------------|-----------------|

| BSF STATUS, RP1 | ;               |

| BCF LCDSE,SE16  | ;Make all PORTF |

| BCF LCDSE, SE12 | digital inputs; |

## **TABLE 5-11: PORTF FUNCTIONS**

| Name      | Bit# | Buffer Type | Function                          |  |  |  |  |

|-----------|------|-------------|-----------------------------------|--|--|--|--|

| RF0/SEG12 | bit0 | ST          | Digital input or Segment Driver12 |  |  |  |  |

| RF1/SEG13 | bit1 | ST          | Digital input or Segment Driver13 |  |  |  |  |

| RF2/SEG14 | bit2 | ST          | Digital input or Segment Driver14 |  |  |  |  |

| RF3/SEG15 | bit3 | ST          | Digital input or Segment Driver15 |  |  |  |  |

| RF4/SEG16 | bit4 | ST          | Digital input or Segment Driver16 |  |  |  |  |

| RF5/SEG17 | bit5 | ST          | Digital input or Segment Driver17 |  |  |  |  |

| RF6/SEG18 | bit6 | ST          | Digital input or Segment Driver18 |  |  |  |  |

| RF7/SEG19 | bit7 | ST          | Digital input or Segment Driver19 |  |  |  |  |

Legend: ST = Schmitt Trigger input

#### TABLE 5-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Address | Name  | Bit 7                                 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|---------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------|

| 107h    | PORTF | RF7                                   | RF6   | RF5   | RF4   | RF3   | RF2   | RF1   | RF0   | 0000 0000                     | 0000 0000                 |

| 187h    | TRISF | PORTF Data Direction Control Register |       |       |       |       |       |       |       | 1111 1111                     | 1111 1111                 |

| 10Dh    | LCDSE | SE29                                  | SE27  | SE20  | SE16  | SE12  | SE9   | SE5   | SE0   | 1111 1111                     | 1111 1111                 |

Legend: Shaded cells are not used by PORTF.

## TABLE 10-3: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Address                 | Name    | Bit 7   | Bit 6                      | Bit 5                                 | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |                 |              |        |        | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|-------------------------|---------|---------|----------------------------|---------------------------------------|-------------------------------------|-----------------|--------------|--------|--------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                       | TOIE                                  | INTE                                | RBIE            | TOIF         | INTF   | RBIF   | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1    | LCDIF   | ADIF <sup>(1)</sup>        | —                                     | _                                   | SSPIF           | CCP1IF       | TMR2IF | TMR1IF | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1    | LCDIE   | ADIE <sup>(1)</sup>        | _                                     | _                                   | SSPIE           | CCP1IE       | TMR2IE | TMR1IE | 00 0000                       | 00 0000                         |

| 87h                     | TRISC   | _       | _                          | PORTC Data Direction Control Register |                                     |                 |              |        |        |                               | 11 1111                         |

| 0Eh                     | TMR1L   | Holding | register fo                | or the Least S                        | Significant By                      | rte of the 16-b | oit TMR1 reg | ister  |        | xxxx xxxx                     | uuuu uuuu                       |

| 0Fh                     | TMR1H   | Holding | register fo                | or the Most S                         | ignificant By                       | te of the 16-bi | it TMR1 regi | ster   |        | xxxx xxxx                     | uuuu uuuu                       |

| 10h                     | T1CON   | _       |                            | T1CKPS1                               | T1CKPS0                             | T1OSCEN         | T1SYNC       | TMR1CS | TMR10N | 00 0000                       | uu uuuu                         |

| 15h                     | CCPR1L  | Capture | Capture/Compare/PWM1 (LSB) |                                       |                                     |                 |              |        |        | xxxx xxxx                     | uuuu uuuu                       |

| 16h                     | CCPR1H  | Capture | Capture/Compare/PWM1 (MSB) |                                       |                                     |                 |              |        |        | xxxx xxxx                     | uuuu uuuu                       |

| 17h                     | CCP1CON | _       | _                          | CCP1X                                 | CCP1Y                               | CCP1M3          | CCP1M2       | CCP1M1 | CCP1M0 | 00 0000                       | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes. Note 1: Bits ADIE and ADIF reserved on the PIC16C923, always maintain these bits clear.

#### TABLE 10-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                 | Name    | Bit 7                                   | Bit 6                      | 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0    |         |         |        |         |         | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|-------------------------|---------|-----------------------------------------|----------------------------|------------------------------------------|---------|---------|--------|---------|---------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                                     | PEIE                       | TOIE                                     | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1    | LCDIF                                   | ADIF <sup>(1)</sup>        | _                                        | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1    | LCDIE                                   | ADIE <sup>(1)</sup>        | _                                        | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 00 0000                       | 00 0000                         |

| 87h                     | TRISC   | — PORTC Data Direction Control Register |                            |                                          |         |         |        |         | 11 1111 | 11 1111                       |                                 |

| 11h                     | TMR2    | Timer2                                  | module's reg               | gister                                   |         |         |        |         |         | 0000 0000                     | 0000 0000                       |

| 92h                     | PR2     | Timer2                                  | module's Pe                | riod register                            |         |         |        |         |         | 1111 1111                     | 1111 1111                       |

| 12h                     | T2CON   | _                                       | TOUTPS3                    | TOUTPS2                                  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                     | -000 0000                       |

| 15h                     | CCPR1L  | Capture                                 | Capture/Compare/PWM1 (LSB) |                                          |         |         |        |         |         | xxxx xxxx                     | uuuu uuuu                       |

| 16h                     | CCPR1H  | Capture                                 | Capture/Compare/PWM1 (MSB) |                                          |         |         |        |         |         | xxxx xxxx                     | uuuu uuuu                       |

| 17h                     | CCP1CON | _                                       | _                          | - CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M |         |         |        |         |         |                               | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode. Note 1: Bits ADIE and ADIF reserved on the PIC16C923, always maintain these bits clear.

Г

## FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                           | R/W-0                                                                                                                                               | R/W-0                                                                                                                         | R/W-0                                                                                  | R/W-0                                                                | R/W-0                |                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                                        | SSPEN                                                                                                                                                           | CKP                                                                                                                                                 | SSPM3                                                                                                                         | SSPM2                                                                                  | SSPM1                                                                | SSPM0                | R = Readable bit                                                                                                  |

| bit7     |                                                                                                                                              |                                                                                                                                                                 |                                                                                                                                                     |                                                                                                                               |                                                                                        |                                                                      | bit0                 | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                              |

| bit 7:   | WCOL: We<br>1 = The SS<br>(must be c<br>0 = No col                                                                                           | SPBUF reg                                                                                                                                                       | jister is w                                                                                                                                         |                                                                                                                               | e it is still ti                                                                       | ransmitting                                                          | the previo           | us word                                                                                                           |

| bit 6:   | SSPOV: R                                                                                                                                     | eceive Ov                                                                                                                                                       | erflow Ind                                                                                                                                          | icator bit                                                                                                                    |                                                                                        |                                                                      |                      |                                                                                                                   |

|          | the data in<br>if only tran                                                                                                                  | byte is rece<br>SSPSR is<br>smitting da<br>tion (and t                                                                                                          | lost. Ove<br>ata, to avo                                                                                                                            | rflow can c<br>oid setting                                                                                                    | only occur<br>overflow.                                                                | in slave mo<br>In master i                                           | ode. The us          | revious data. In case of overflov<br>er must read the SSPBUF, eve<br>werflow bit is not set since eac<br>egister. |

|          | $\frac{\ln I^2 C \mod}{1 = A \text{ byte}}$<br>in transmit<br>0 = No over                                                                    | is received<br>mode. SS                                                                                                                                         |                                                                                                                                                     |                                                                                                                               |                                                                                        |                                                                      |                      | ous byte. SSPOV is a "don't care                                                                                  |

| bit 5:   | SSPEN: S                                                                                                                                     | ynchronou                                                                                                                                                       | s Serial F                                                                                                                                          | ort Enable                                                                                                                    | e bit                                                                                  |                                                                      |                      |                                                                                                                   |

|          | $0 = \text{Disable}$ $\frac{\ln l^2 C \mod l}{l + l^2}$                                                                                      | es serial po<br>es serial p<br><u>de</u><br>es the seria                                                                                                        | ort and co<br>al port and                                                                                                                           | nfigures th<br>configure                                                                                                      | nese pins                                                                              | as I/O port                                                          | pins as sei          | rt pins<br>rial port pins                                                                                         |

| bit 4:   | <b>CKP</b> : Cloc<br>In SPI mod<br>1 = Idle sta<br>0 = Idle sta<br>In $I^2$ C mod<br>SCK relea                                               | k Polarity S<br>de<br>ate for cloc<br>ate for cloc<br>de<br>se control                                                                                          | Select bit<br>k is a higł                                                                                                                           | n level                                                                                                                       | s must be                                                                              | properly c                                                           | onfigured a          | is input or output.                                                                                               |

|          | 1 = Enable<br>0 = Holds                                                                                                                      |                                                                                                                                                                 | clock stra                                                                                                                                          | tch) (Llead                                                                                                                   | to onsure                                                                              | , data sotu                                                          | n time)              |                                                                                                                   |

| bit 3-0: | SSPM3:S3<br>0000 = SP<br>0001 = SP<br>0010 = SP<br>0100 = SP<br>0100 = SP<br>0101 = SP<br>0110 = I <sup>2</sup> C<br>0111 = I <sup>2</sup> C | SPM0: Syr<br>Pl master m<br>Pl master m<br>Pl master m<br>Pl master m<br>Pl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo<br>Cl slave mo | achronous<br>node, cloc<br>node, cloc<br>node, cloc<br>de, clock<br>de, clock<br>de, clock<br>de, 7-bit a<br>de, 10-bit<br>controlle<br>de, 7-bit a | Serial Pol<br>k = Fosc/4<br>k = Fosc/6<br>k = TMR2<br>= SCK pin<br>= SCK pin<br>ddress<br>address<br>d master n<br>ddress wit | rt Mode Si<br>4<br>16<br>54<br>. SS pin ci<br>. SS pin ci<br>node (slav<br>th start an | elect bits<br>ontrol enal<br>ontrol disa<br>re idle)<br>d stop bit i | bled.<br>bled. SS ca |                                                                                                                   |

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and  $\overline{SS}$  could be used as general purpose outputs by clearing their corresponding TRIS register bits.

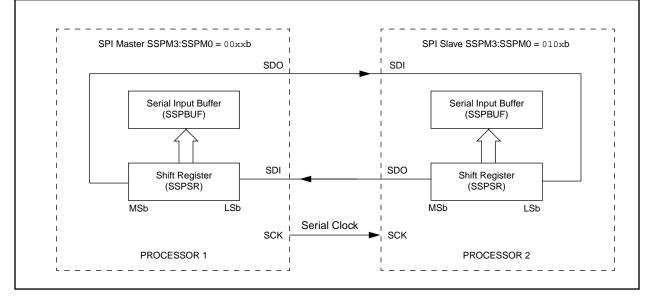

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

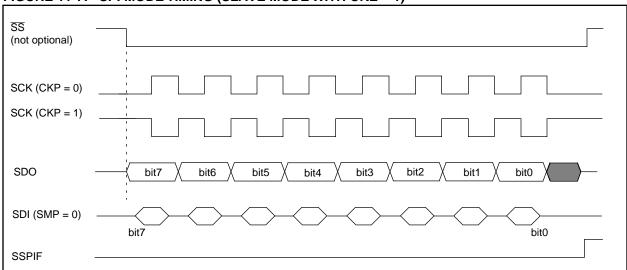

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5, Figure 11-6, and Figure 11-7 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 8 MHz) of 2 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

## FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

### FIGURE 11-7: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

| Address                 | Name    | Bit 7   | Bit 6               | Bit 5       | Bit 4                                 | Bit 3      | Bit 2   | Bit 1   | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|-------------------------|---------|---------|---------------------|-------------|---------------------------------------|------------|---------|---------|--------|-------------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                | TOIE        | INTE                                  | RBIE       | TOIF    | INTF    | RBIF   | 0000 000x                     | 0000 000u                 |

| 0Ch                     | PIR1    | LCDIF   | ADIF <sup>(1)</sup> | _           | _                                     | SSPIF      | CCP1IF  | TMR2IF  | TMR1IF | 00 0000                       | 00 0000                   |

| 8Ch                     | PIE1    | LCDIE   | ADIE <sup>(1)</sup> | —           | _                                     | SSPIE      | CCP1IE  | TMR2IE  | TMR1IE | 00 0000                       | 00 0000                   |

| 13h                     | SSPBUF  | Synchro | nous Serial         | Port Receiv | ve Buffer/Tra                         | ansmit Reg | ster    | -       |        | XXXX XXXX                     | uuuu uuuu                 |

| 14h                     | SSPCON  | WCOL    | SSPOV               | SSPEN       | СКР                                   | SSPM3      | SSPM2   | SSPM1   | SSPM0  | 0000 0000                     | 0000 0000                 |

| 85h                     | TRISA   | _       | _                   | PORTA Da    | ata Direction                         |            | 11 1111 | 11 1111 |        |                               |                           |

| 87h                     | TRISC   | _       | _                   | PORTC D     | PORTC Data Direction Control Register |            |         |         |        |                               | 11 1111                   |

| 94h                     | SSPSTAT | SMP     | CKE                 | D/Ā         | Р                                     | S          | R/W     | UA      | BF     | 0000 0000                     | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: Bits ADIE and ADIF are reserved on the PIC16C923, always maintain these bits clear.

# PIC16C9XX

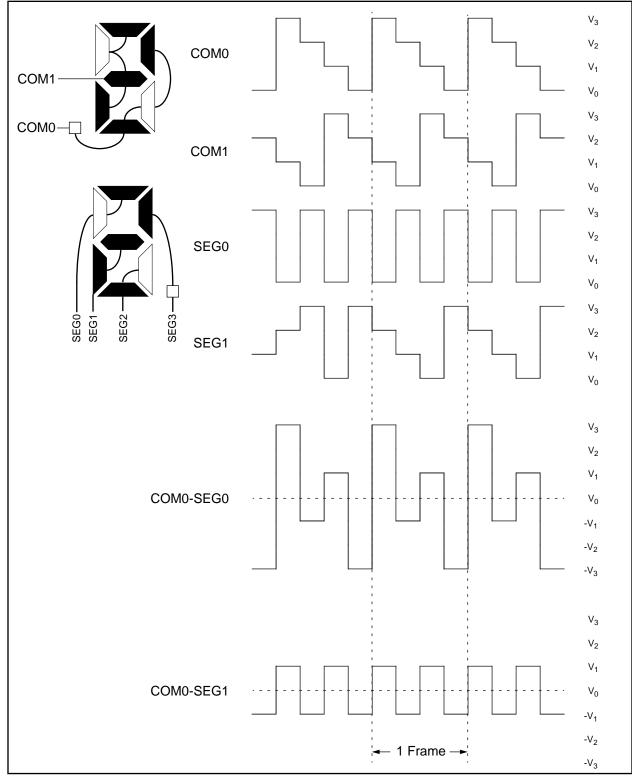

## FIGURE 13-5: WAVEFORMS IN 1/2 MUX, 1/3 BIAS DRIVE

### 14.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or some peripheral interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. A/D conversion (when A/D clock source is RC).

- 6. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 7. LCD module.

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| BSF               | Bit Set f                        |                 |                 |              | BTFSC           |

|-------------------|----------------------------------|-----------------|-----------------|--------------|-----------------|

| Syntax:           | [ <i>label</i> ] BS              | SF f,b          |                 |              | Syntax:         |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$ |                 |                 |              | Operands:       |

| Operation:        | $1 \rightarrow (f < b$           | >)              |                 |              | Operation:      |

| Status Affected:  | None                             |                 |                 |              | Status Affected |

| Encoding:         | 01                               | 01bb            | bfff            | ffff         | Encoding:       |

| Description:      | Bit 'b' in re                    | gister 'f' i    | s set.          |              | Description:    |

| Words:            | 1                                |                 |                 |              |                 |

| Cycles:           | 1                                |                 |                 |              |                 |

| Q Cycle Activity: | Q1                               | Q2              | Q3              | Q4           |                 |

|                   | Decode                           | Read            | Process         | Write        | Words:          |

|                   |                                  | register<br>'f' | data            | register 'f' | Cycles:         |

| Example           | BSF                              | FLAG_F          | Q Cycle Activit |              |                 |

|                   | Before In<br>After Inst          | FLAG_R          | lf Skip         |              |                 |

|                   |                                  |                 |                 |              | Example         |

|                   |                                  |                 |                 |              |                 |

|           | Bit Test,                                                                                                                                                                                                                          | Skip if Cle          | ear              |                  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--|--|--|--|

|           | [ <i>label</i> ] BT                                                                                                                                                                                                                | FSC f,b              |                  |                  |  |  |  |  |

| ds:       | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                |                      |                  |                  |  |  |  |  |

| on:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                            |                      |                  |                  |  |  |  |  |

| ffected:  | None                                                                                                                                                                                                                               |                      |                  |                  |  |  |  |  |

| g:        | 01 10bb bfff ffff                                                                                                                                                                                                                  |                      |                  |                  |  |  |  |  |

| tion:     | If bit 'b' in register 'f' is '1' then the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2Tcy<br>instruction. |                      |                  |                  |  |  |  |  |

|           | 1                                                                                                                                                                                                                                  |                      |                  |                  |  |  |  |  |

|           | 1(2)                                                                                                                                                                                                                               |                      |                  |                  |  |  |  |  |

| Activity: | Q1                                                                                                                                                                                                                                 | Q2                   | Q3               | Q4               |  |  |  |  |

|           | Decode                                                                                                                                                                                                                             | Read<br>register 'f' | Process<br>data  | No-<br>Operation |  |  |  |  |

| If Skip:  | (2nd Cyc                                                                                                                                                                                                                           | le)                  |                  |                  |  |  |  |  |

|           | Q1                                                                                                                                                                                                                                 | Q2                   | Q3               | Q4               |  |  |  |  |

|           | No-<br>Operation                                                                                                                                                                                                                   | No-<br>Operation     | No-<br>Operation | No-<br>Operation |  |  |  |  |

| Э         | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •                                                                                                                                                                             |                      |                  |                  |  |  |  |  |

|           |                                                                                                                                                                                                                                    |                      |                  |                  |  |  |  |  |

|           | Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                        |                      |                  |                  |  |  |  |  |

# PIC16C9XX

| INCF                                                                | Increment f                                                                                                                                                                                | INCFSZ                                                  | Increment f, Skip if 0                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                             | [ <i>label</i> ] INCF f,d                                                                                                                                                                  | Syntax:                                                 | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                              |

| Operands:                                                           | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                 | Operands:                                               | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                               |

| Operation:<br>Status Affected:                                      | (f) + 1 $\rightarrow$ (destination)<br>Z                                                                                                                                                   | Operation:                                              | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                               |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 001010dfffffffThe contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.1112Q1Q2Q3Q4Write to | Status Affected:<br>Encoding:<br>Description:<br>Words: | 001111dfffffffThe contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead making it a 2Tcy instruction.1 |

| Example                                                             | Decode     Read<br>register<br>'f'     Process<br>data     Write to<br>destination       INCF     CNT , 1                                                                                  | Cycles:<br>Q Cycle Activity:                            | 1(2)<br>Q1 Q2 Q3 Q4<br>Decode Read register 'f' Process Write to destination                                                                                                                                                                                                                             |

|                                                                     | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                                                      | If Skip:                                                | (2nd Cycle)Q1Q2Q3Q4No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                                                                                      |

|                                                                     |                                                                                                                                                                                            | Example                                                 | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction                                                                                                                                                                             |

CNT = CNT + 1 if CNT= 0, PC = address CONTINUE

if  $CNT \neq 0$ , PC = address HERE +1

| IORLW             | Inclusive OR Literal with W                                                                                           |                     |                 |               |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                             | IORLW               | k               |               |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                                                     |                     |                 |               |  |  |  |  |  |  |

| Operation:        | (W) .OR.                                                                                                              | $k \rightarrow (W)$ | I               |               |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                     |                     |                 |               |  |  |  |  |  |  |

| Encoding:         | 11                                                                                                                    | 1000                | kkkk            | kkkk          |  |  |  |  |  |  |

| Description:      | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                     |                 |               |  |  |  |  |  |  |

| Words:            | 1                                                                                                                     |                     |                 |               |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                     |                     |                 |               |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                    | Q2                  | Q3              | Q4            |  |  |  |  |  |  |

|                   | Decode                                                                                                                | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |  |  |  |

| Example           | IORLW                                                                                                                 | 0x35                |                 |               |  |  |  |  |  |  |

|                   | Before Instruction                                                                                                    |                     |                 |               |  |  |  |  |  |  |

|                   | W = 0x9A<br>After Instruction                                                                                         |                     |                 |               |  |  |  |  |  |  |

|                   |                                                                                                                       | W =                 | 0xBF            |               |  |  |  |  |  |  |

|                   |                                                                                                                       | Z =                 | 1               |               |  |  |  |  |  |  |

|                   |                                                                                                                       |                     |                 |               |  |  |  |  |  |  |

| IORWF             | Inclusive C                                                           | OR W v                 | vith f           |                      |  |  |  |  |

|-------------------|-----------------------------------------------------------------------|------------------------|------------------|----------------------|--|--|--|--|

| Syntax:           | [label] IC                                                            | ORWF                   | f,d              |                      |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$     |                        |                  |                      |  |  |  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ (destination)                              |                        |                  |                      |  |  |  |  |

| Status Affected:  | Z                                                                     |                        |                  |                      |  |  |  |  |

| Encoding:         | 00 0                                                                  | 0100                   | dfff             | ffff                 |  |  |  |  |

| Description:      | Inclusive OR<br>ter 'f'. If 'd' is<br>W register. If<br>back in regis | 0 the re<br>'d' is 1   | sult is place    | ced in the           |  |  |  |  |

| Words:            | 1                                                                     |                        |                  |                      |  |  |  |  |

| Cycles:           | 1                                                                     |                        |                  |                      |  |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                     | Q3               | Q4                   |  |  |  |  |

|                   |                                                                       | Read<br>egister<br>'f' | Process<br>data  | Write to destination |  |  |  |  |

| Example           | IORWF                                                                 |                        | RESULT,          | 0                    |  |  |  |  |

|                   | Before Insti<br>RE<br>W                                               | ruction<br>ESULT       |                  |                      |  |  |  |  |

|                   | After Instru                                                          | ction                  | 0,101            |                      |  |  |  |  |

|                   | RE<br>W                                                               | ESULT                  | = 0x13<br>= 0x93 |                      |  |  |  |  |

| vv | = | UX |

|----|---|----|

| Z  | = | 1  |

| SUBWF             | Subilaci                                                          | W from f                     |                                   |                      |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|--|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                         | SUBWF                        | f,d                               |                      |  |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ | 7                            |                                   |                      |  |  |  |  |  |  |  |

| Operation:        | (f) - (W) –                                                       | → (destina                   | ation)                            |                      |  |  |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                          | C, DC, Z                     |                                   |                      |  |  |  |  |  |  |  |

| Encoding:         | 00                                                                | 0010                         | dfff                              | ffff                 |  |  |  |  |  |  |  |

| Description:      | Subtract (2<br>ister from r<br>stored in th<br>result is sto      | egister 'f'. I<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | e result is<br>the   |  |  |  |  |  |  |  |

| Words:            | 1                                                                 |                              |                                   |                      |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                 |                              |                                   |                      |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                | Q2                           | Q3                                | Q4                   |  |  |  |  |  |  |  |

|                   | Decode                                                            | Read<br>register 'f'         | Process<br>data                   | Write to destinatior |  |  |  |  |  |  |  |

| Example 1:        | SUBWF                                                             | REG1,1                       | 1                                 |                      |  |  |  |  |  |  |  |

|                   | Before Instruction                                                |                              |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 3<br>2<br>?<br>?                  |                      |  |  |  |  |  |  |  |

|                   | After Instruction                                                 |                              |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 1<br>2<br>1; result is<br>0       | positive             |  |  |  |  |  |  |  |

| Example 2:        | Before Instruction                                                |                              |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 2<br>2<br>?<br>?                  |                      |  |  |  |  |  |  |  |

|                   | After Instruction                                                 |                              |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 0<br>2<br>1; result is<br>1       | zero                 |  |  |  |  |  |  |  |

| Example 3:        | Before Ins                                                        | struction                    |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 1<br>2<br>?<br>?                  |                      |  |  |  |  |  |  |  |

|                   | After Instr                                                       | uction                       |                                   |                      |  |  |  |  |  |  |  |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 0xFF<br>2<br>0; result is<br>0    | negative             |  |  |  |  |  |  |  |

| SWAPF                                                                                         | Swap Nibbles in f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                                       | [ <i>label</i> ] SWAPF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Operands:                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Operation:                                                                                    | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                                     | 00 1110 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Description:                                                                                  | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Q Cycle Activity:                                                                             | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                               | Decode Read register 'f' Process Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Example                                                                                       | SWAPF REG, 0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                                                                                               | REG1 = 0xA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|                                                                                               | After Instruction<br>REG1 = 0xA5<br>W = 0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| TRIS                                                                                          | REG1 = 0xA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| TRIS<br>Syntax:                                                                               | REG1 = 0xA5<br>W = 0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| -                                                                                             | REG1 = 0xA5<br>W = 0x5A<br>Load TRIS Register                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                                       | REG1       =       0xA5         W       =       0x5A             Load TRIS Register         [/abel]       TRIS       f                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                          | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                            | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \textbf{Load TRIS Register} \\ \hline \\ \textbf{[label]} & TRIS & f\\ 5 \leq f \leq 7\\ \hline \\ (W) \rightarrow TRIS register f;\\ \hline \\ \textbf{None} \end{array}$                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \textbf{Load TRIS Register} \\ \hline \\ $                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |