Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923-04i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address            | Name    | Bit 7         | Bit 6               | Bit 5                   | Bit 4          | Bit 3        | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|---------------|---------------------|-------------------------|----------------|--------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 1             | ·       | •             |                     |                         |                |              | ·                |                |          | •                             |                           |

| 80h                | INDF    | Addressing    | this location       | uses conten             | ts of FSR to   | address data | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 81h                | OPTION  | RBPU          | INTEDG              | TOCS                    | T0SE           | PSA          | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 82h                | PCL     | Program Co    | ounter's (PC)       | Least Signif            | icant Byte     |              |                  |                |          | 0000 0000                     | 0000 0000                 |

| 83h                | STATUS  | IRP           | RP1                 | RP0                     | TO             | PD           | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 84h                | FSR     | Indirect data | a memory ad         | dress pointe            | r              |              |                  |                |          | XXXX XXXX                     | uuuu uuuu                 |

| 85h                | TRISA   | —             | _                   | PORTA Dat               | a Direction R  | egister      |                  |                |          | 11 1111                       | 11 1111                   |

| 86h                | TRISB   | PORTB Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 87h                | TRISC   | —             | _                   | PORTC Da                | ta Direction F | Register     |                  |                |          | 11 1111                       | 11 1111                   |

| 88h                | TRISD   | PORTD Dat     | a Direction F       | Register                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 89h                | TRISE   | PORTE Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 8Ah                | PCLATH  | —             | _                   | —                       | Write Buffer   | for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 8Bh                | INTCON  | GIE           | PEIE                | T0IE                    | INTE           | RBIE         | T0IF             | INTF           | RBIF     | 0000 000x 0000 00             |                           |

| 8Ch                | PIE1    | LCDIE         | ADIE <sup>(2)</sup> | —                       | _              | SSPIE        | CCP1IE           | TMR2IE         | TMR1IE   | 00 0000                       | 00 0000                   |

| 8Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 8Eh                | PCON    | —             | — — — — — — POR —   |                         |                |              |                  | 0-             | u-       |                               |                           |

| 8Fh                | _       | Unimpleme     | Unimplemented       |                         |                |              |                  |                |          | _                             | _                         |

| 90h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | —                             | —                         |

| 91h                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 92h                | PR2     | Timer2 Peri   | od Register         |                         |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 93h                | SSPADD  | Synchronou    | is Serial Port      | (I <sup>2</sup> C mode) | Address Reg    | ister        |                  |                |          | 0000 0000                     | 0000 0000                 |

| 94h                | SSPSTAT | SMP           | CKE                 | D/Ā                     | Р              | S            | R/W              | UA             | BF       | 0000 0000                     | 0000 0000                 |

| 95h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 96h                | —       | Unimpleme     | Jnimplemented —     |                         |                |              |                  |                | _        | —                             |                           |

| 97h                | —       | Unimpleme     | Jnimplemented –     |                         |                |              |                  |                | _        | —                             |                           |

| 98h                | —       | Unimpleme     | Jnimplemented —     |                         |                |              |                  |                | _        | —                             |                           |

| 99h                | —       | Unimpleme     | Jnimplemented –     |                         |                |              |                  |                | _        | —                             |                           |

| 9Ah                | _       | Unimpleme     | Unimplemented —     |                         |                |              |                  |                | _        | _                             |                           |

| 9Bh                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | -                             | —                         |

| 9Ch                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | -                             | —                         |

| 9Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | —                             | —                         |

| 9Eh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 9Fh <sup>(1)</sup> | ADCON1  |               | —                   | _                       |                | _            | PCFG2            | PCFG1          | PCFG0    | 000                           | 000                       |

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0',

Note

shaded locations are unimplemented, read as '0'. 1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

These bits are reserved on the PIC16C923, always maintain these bits clear.

These pixels do not display, but can be used as general purpose RAM.

PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT pin interrupt, TMR0, and the weak pull-ups on PORTB. **Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### FIGURE 4-4: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1        | R/W-1                                                                                                                                                             | R/W-1                                             | R/W-1              | R/W-1      | R/W-1 | R/W-1 | R/W-1       |                                                                                                                                                |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------|------------|-------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RBPU<br>bit7 | INTEDG                                                                                                                                                            | TOCS                                              | TOSE               | PSA        | PS2   | PS1   | PS0<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |

| bit 7:       | <b>RBPU</b> : PORTB Pull-up Enable bit         1 = PORTB pull-ups are disabled         0 = PORTB pull-ups are enabled by individual port latch values             |                                                   |                    |            |       |       |             |                                                                                                                                                |  |  |

| bit 6:       | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin<br>0 = Interrupt on falling edge of RB0/INT pin                                  |                                                   |                    |            |       |       |             |                                                                                                                                                |  |  |

| bit 5:       | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                    |                                                   |                    |            |       |       |             |                                                                                                                                                |  |  |

| bit 4:       | <b>TOSE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |                                                   |                    |            |       |       |             |                                                                                                                                                |  |  |

| bit 3:       | <ul> <li><b>PSA</b>: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>    |                                                   |                    |            |       |       |             |                                                                                                                                                |  |  |

| bit 2-0:     | PS2:PS0:                                                                                                                                                          | Prescale                                          | r Rate Se          | ect bits   |       |       |             |                                                                                                                                                |  |  |

|              | Bit Value                                                                                                                                                         | TMR0 R                                            | ate WD             | T Rate     |       |       |             |                                                                                                                                                |  |  |

|              | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                              | 1:2<br>1:4<br>1:8<br>1:10<br>1:32<br>1:64<br>1:12 | 2 1<br>4 1<br>28 1 | : 2<br>: 4 |       |       |             |                                                                                                                                                |  |  |

#### 5.8 <u>I/O Programming Considerations</u>

#### 5.8.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the contents of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-8 shows the effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 5-8: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

.

| i                                         |                 |           |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------|-----------|--|--|--|--|--|--|--|

| ;                                         | PORT latch      | PORT pins |  |  |  |  |  |  |  |

| ;                                         |                 |           |  |  |  |  |  |  |  |

| BCF PORTB, 7                              | ; 01pp pppp     | 11pp pppp |  |  |  |  |  |  |  |

| BCF PORTB, 6                              | ; 10pp pppp     | 11pp pppp |  |  |  |  |  |  |  |

| BCF STATUS, RP1                           | ;               |           |  |  |  |  |  |  |  |

| BSF STATUS, RPO                           | ;               |           |  |  |  |  |  |  |  |

| BCF TRISB, 7                              | ; 10pp pppp     | 11pp pppp |  |  |  |  |  |  |  |

| BCF TRISB, 6                              | ; 10pp pppp     | 10pp pppp |  |  |  |  |  |  |  |

| ;                                         |                 |           |  |  |  |  |  |  |  |

| ;Note that the user may have expected the |                 |           |  |  |  |  |  |  |  |

| ;pin values to be                         | 00pp ppp. The 2 | 2nd BCF   |  |  |  |  |  |  |  |

| · · · · · · · · · · · · · · · · · · ·     |                 |           |  |  |  |  |  |  |  |

;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### 5.8.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-11). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

| PC<br>Instruction       | X PC                             | X PC + 1                         | X  | PC + 2                | PC + 3                                       | This example shows a write to PORT                                                         |

|-------------------------|----------------------------------|----------------------------------|----|-----------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|

| fetched                 | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W                     |    | NOP                   | followed by a read from PORTB.<br>Note that: |                                                                                            |

| RB7:RB0                 |                                  | <u>.</u>                         | X  |                       |                                              | data setup time = (0.25TCY - TPD)                                                          |

| 1                       |                                  | 1<br>1<br>1<br>1                 |    | Port pin sampled here | 1                                            | where Tcy = instruction cycle<br>TPD = propagation delay                                   |

| Instruction<br>executed |                                  | MOVWF PORTB<br>write to<br>PORTB | MO | VF PORTB,W            | NOP                                          | Therefore, at higher clock frequencie<br>a write followed by a read may be pro<br>lematic. |

| 1                       |                                  | 1                                | 1  | 1                     | 1<br>1                                       |                                                                                            |

#### FIGURE 5-11: SUCCESSIVE I/O OPERATION

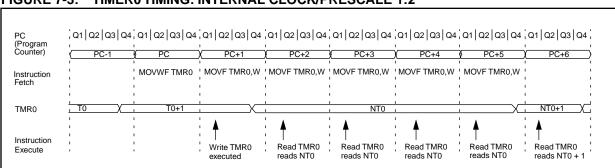

## FIGURE 7-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

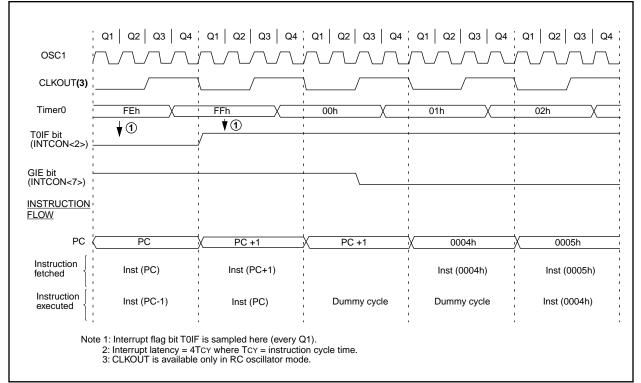

#### FIGURE 7-4: **TIMER0 INTERRUPT TIMING**

#### 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u>

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read-from or write-to the Timer1 register pair (TMR1H:TMR1L) (Section 8.3.2).

In asynchronous counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements, as specified in timing parameters 45, 46, and 47.

#### 8.3.2 READING AND WRITING TMR1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ;Read high byte

MOVWF TMPH

;

MOVF

TMR1L, W ;Read low byte

MOVWE TMPL

;

MOVF

TMR1H, W ;Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

CONTINUE ;Good 16-bit read

GOTO

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

;

and low bytes now will read a good value.

;

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

TMR1L, W ;Read low byte

MOVE

MOVWF TMPL

;

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

### 8.4 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

#### TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                               | Freq                                                                                                       | C1            | C2       |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|----------|--|--|--|

| LP                                     | 32 kHz                                                                                                     | 33 pF         |          |  |  |  |

|                                        | 100 kHz                                                                                                    | 15 pF         | 15 pF    |  |  |  |

|                                        | 200 kHz                                                                                                    | 15 pF         | 15 pF    |  |  |  |

| These v                                | alues are for o                                                                                            | design guidan | ce only. |  |  |  |

| Crystals Tested:                       |                                                                                                            |               |          |  |  |  |

| 32.768 kHz                             | Epson C-001R32.768K-A ± 20 PPM                                                                             |               |          |  |  |  |

| 100 kHz                                | Epson C-2 100.00 KC-P ± 20 PPM                                                                             |               |          |  |  |  |

| 200 kHz                                | STD XTL 200.000 kHz ± 20 PPM                                                                               |               |          |  |  |  |

| of o<br>time<br>2: Sind<br>cha<br>reso | te 1: Higher capacitance increases the stability<br>of oscillator but also increases the start-up<br>time. |               |          |  |  |  |

NOTES:

### 11.2 $\underline{I^2}C^{\mathbb{T}}$ Overview

This section provides an overview of the Inter-Integrated Circuit ( $I^2C$ ) bus, with Section 11.3 discussing the operation of the SSP module in  $I^2C$  mode.

The  $l^2C$  bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. An enhanced specification, or fast mode is not supported. This device will communicate with fast mode devices if attached to the same bus.

The  $l^2C$  interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXXX software. Table 11-2 defines some of the  $l^2C$  bus terminology. For additional information on the  $l^2C$  interface specification, refer to the Philips document "*The*  $l^2C$  bus and how to use it."#939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the  $I^2C$  bus is limited only by the maximum bus loading specification of 400 pF.

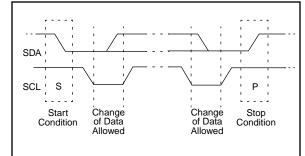

#### 11.2.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions. The master generates these conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### FIGURE 11-8: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

### TABLE 11-2: I<sup>2</sup>C BUS TERMINOLOGY

#### 11.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 11-3 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

#### 11.3.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The

address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 11-10). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | its as Data<br>is Received |                    |                       | Set bit SSPIF                        |

|----|----------------------------|--------------------|-----------------------|--------------------------------------|

| BF | SSPOV                      | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |

| 0  | 0                          | Yes                | Yes                   | Yes                                  |

| 1  | 0                          | No                 | No                    | Yes                                  |

| 1  | 1                          | No                 | No                    | Yes                                  |

| 0  | 1                          | No                 | No                    | Yes                                  |

#### TABLE 11-3: DATA TRANSFER RECEIVED BYTE ACTIONS

# FIGURE 11-21: OPERATION OF THE I<sup>2</sup>C MODULE IN IDLE\_MODE, RCV\_MODE OR XMIT\_MODE

| IDLE_MODE (7-bit):<br>if (Addr_match)                   | { Set interrupt;<br>if $(R/\overline{W} = 1)$ { Send $\overline{ACK} = 0$ ; |

|---------------------------------------------------------|-----------------------------------------------------------------------------|

|                                                         | set XMIT_MODE;                                                              |

|                                                         | }<br>else if (R/W = 0) set RCV_MODE;<br>}                                   |

| RCV_MODE:                                               |                                                                             |

| if ((SSPBUF=Full) OR (SSPOV = 1<br>{ Set SSPOV;         |                                                                             |

| <pre>{ Set SSPOV;<br/>Do not acknowle</pre>             | edge;                                                                       |

| }                                                       |                                                                             |

| else { transfer SSPSF<br>send ACK = 0;                  | $R \rightarrow SSPBUF;$                                                     |

| }<br>Receive 8-bits in SSPSR;                           |                                                                             |

| Set interrupt;                                          |                                                                             |

| XMIT_MODE:                                              |                                                                             |

| While ((SSPBUF = Empty) AND (C                          | :KP=0)) Hold SCL Low;                                                       |

| Send byte;                                              |                                                                             |

| Set interrupt;<br>if ( <del>ACK</del> Received = 1)     | End of transmission;                                                        |

|                                                         | Go back to IDLE_MODE;                                                       |

|                                                         | }                                                                           |

| else if ( ACK Received = 0) Go ba                       | ack to XMIT_MODE;                                                           |

| IDLE_MODE (10-Bit):<br>If (High_byte_addr_match AND (R/ | $\overline{M}$ = 0))                                                        |

|                                                         | _MATCH = FALSE;                                                             |

| Set interrupt;                                          |                                                                             |

|                                                         | Full) OR ((SSPOV = 1))                                                      |

| {                                                       | Set SSPOV;                                                                  |

| ,                                                       | Do not acknowledge;                                                         |

| }<br>else {                                             | Set UA = 1;                                                                 |

|                                                         | Send $\overline{ACK} = 0;$                                                  |

|                                                         | While (SSPADD not updated) Hold SCL low;                                    |

|                                                         | Clear UA = 0;                                                               |

|                                                         | Receive Low_addr_byte;                                                      |

|                                                         | Set interrupt;<br>Set UA = 1;                                               |

|                                                         | If (Low_byte_addr_match)                                                    |

|                                                         | { PRIOR_ADDR_MATCH = TRUE;                                                  |

|                                                         | Send $\overline{ACK} = 0;$                                                  |

|                                                         | while (SSPADD not updated) Hold SCL low;                                    |

|                                                         | Clear UA = 0;<br>Set RCV_MODE;                                              |

|                                                         |                                                                             |

| ١                                                       | }                                                                           |

| }                                                       |                                                                             |

| ر<br>else if (High_byte_addr_match ANI                  | $D(R\overline{W}=1)$                                                        |

| eise ii (high_byte_addi_match Ani                       |                                                                             |

|                                                         | send ACK = 0;                                                               |

|                                                         | set XMIT_MODE;                                                              |

| }                                                       |                                                                             |

| ہ<br>else PRIOR_ADDR_MA                                 | TCH = FALSE                                                                 |

| }                                                       |                                                                             |

| ,                                                       |                                                                             |

#### 12.4 **A/D Conversions**

Example 12-2 show how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel0).

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### EXAMPLE 12-2: DOING AN A/D CONVERSION

BCF STATUS, RP1 ; Select Bank1 STATUS, RPO BSF ; ADCON1 CLRF ; Configure A/D inputs BSF PIE1, ADIE ; Enable A/D interrupts ; Select Bank0 BCF STATUS, RPO MOVLW 0xC1 ; RC Clock, A/D is on, Channel 0 is selected MOVWF ADCON0 ; PIR1, ADIF ; Clear A/D interrupt flag bit BCF INTCON, PEIE BSF ; Enable peripheral interrupts BSF INTCON, GIE ; Enable all interrupts Ensure that the required acquisition time for the selected input channel has elapsed.

; ; Then the conversion may be started.

;

;

| BSF | ADCON0, | GO ; | St | art A/ | D Co | nvers | ion  |      |      |       |        |             |    |

|-----|---------|------|----|--------|------|-------|------|------|------|-------|--------|-------------|----|

| :   |         | ;    | Tł | e ADIF | 'bit | will  | be   | set  | and  | the   | GO/D   | ONE bit     |    |

| :   |         | ;    | i  | s clea | ired | upon  | comp | leti | on c | of th | ne A/I | O Conversio | n. |

Clearing the GO/DONE bit during a conversion will

abort the current conversion. The ADRES register will

NOT be updated with the partially completed A/D con-

version sample. That is, the ADRES register will con-

tinue to contain the value of the last completed

conversion (or the last value written to the ADRES reg-

ister). After the A/D conversion is aborted, a 2TAD wait

is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on

the selected channel.

#### 12.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 12-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 8 MHz (The A/D clock is programmed for 32Tosc), and assumes that immediately after 6TAD, the A/D clock is programmed for 2Tosc.

The 2TOSC violates the minimum TAD time, therefore the last 4-bits will not be converted to correct values.

### EXAMPLE 12-3: 4-BIT vs. 8-BIT CONVERSION TIMES

|                                 | - (111)     | Resolution |        |  |  |

|---------------------------------|-------------|------------|--------|--|--|

|                                 | Freq. (MHz) | 4-bit      | 8-bit  |  |  |

| TAD                             | 8           | 1.6 μs     | 1.6 μs |  |  |

| Tosc                            | 8           | 12.5 ns    | 125 ns |  |  |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 8           | 10.6 μs    | 16 μs  |  |  |

#### 13.4.1 SEGMENT ENABLES

The LCDSE register is used to select the pin function for groups of pins. The selection allows each group of pins to operate as either LCD drivers or digital only pins. To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared.

If the pin is a digital I/O the corresponding TRIS bit controls the data direction. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

- **Note 1:** On a Power-on Reset these pins are configured as LCD drivers.

- Note 2: The LMUX1:LMUX0 takes precedence over the LCDSE bit settings for pins RD7, RD6 and RD5.

#### EXAMPLE 13-1: STATIC MUX WITH 32 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2          |

|-------|--------------|-------------------------|

| BSF   | STATUS, RP1  | ;                       |

| BCF   | LCDCON,LMUX1 | ;Select Static MUX      |

| BCF   | LCDCON,LMUX0 | ;                       |

| MOVLW | OxFF         | ;Make PortD,E,F,G       |

| MOVWF | LCDSE        | ;LCD pins               |

|       |              | ; configure rest of LCD |

#### EXAMPLE 13-2: 1/3 MUX WITH 13 SEGMENTS

| BCF   | STATUS, RPO  | ;Select Bank 2                             |

|-------|--------------|--------------------------------------------|

| BSF   | STATUS, RP1  | ;                                          |

| BSF   | LCDCON,LMUX1 | ;Select 1/3 MUX                            |

| BCF   | LCDCON,LMUX0 | ;                                          |

| MOVLW | 0x87         | ;Make PORTD<7:0> &                         |

| MOVWF | LCDSE        | ;PORTE<6:0> LCD pins                       |

|       |              | ; configure rest of LCD                    |

| MOVLW | 0x87         | ;Make PORTD<7:0> &<br>;PORTE<6:0> LCD pins |

#### FIGURE 13-12:LCDSE REGISTER (ADDRESS 10Dh)

| R/W-1        | R/W-1                                                             | R/W-1                       | R/W-1       | R/W-1   | R/W-1     | R/W-1 | R/W-1       | []                                                                                                   |

|--------------|-------------------------------------------------------------------|-----------------------------|-------------|---------|-----------|-------|-------------|------------------------------------------------------------------------------------------------------|

| SE29<br>bit7 | SE27                                                              | SE20                        | SE16        | SE12    | SE9       | SE5   | SE0<br>bit0 | R =Readable bit<br>W =Writable bit<br>U =Unimplemented bit,<br>Read as '0'<br>-n =Value at POR reset |

|              | <b>SE29</b> : Pin fi<br>1 = pins hav<br>0 = pins hav<br>The LMUX1 | ve LCD dri<br>ve digital Ir | ve functior | า<br>วท |           |       |             |                                                                                                      |

|              | <b>SE27</b> : Pin for<br>1 = pins hav<br>0 = pins hav             | ve LCD dri                  | ve function | 1       | and RE7/S | SEG27 |             |                                                                                                      |

|              | <b>SE20</b> : Pin for<br>1 = pins hav<br>0 = pins hav             | ve LCD dri                  | ve function | 1       | RG0/SE    | G20   |             |                                                                                                      |

|              | <b>SE16</b> : Pin for<br>1 = pins hav<br>0 = pins hav             | ve LCD dri                  | ve function | 1       | RF4/SEC   | G16   |             |                                                                                                      |

|              | <b>SE12</b> : Pin for<br>1 = pins hav<br>0 = pins hav             | ve LCD dri                  | ve functior | ı       | RF0/SEC   | G12   |             |                                                                                                      |

|              | <b>SE9</b> : Pin for<br>1 = pins hav<br>0 = pins hav              | ve LCD dri                  | ve function | 1       | RE4/SE    | G09   |             |                                                                                                      |

|              | <b>SE5</b> : Pin fi<br>1 = pins hav<br>0 = pins hav               | ve LCD dri                  | ve function | 1       | RE0/SE0   | G05   |             |                                                                                                      |

|              | <b>SE0</b> : Pin for<br>1 = pins have $0 = pins have$             | ve LCD dri                  | ve functior | 1       | RD0/SE    | G00   |             |                                                                                                      |

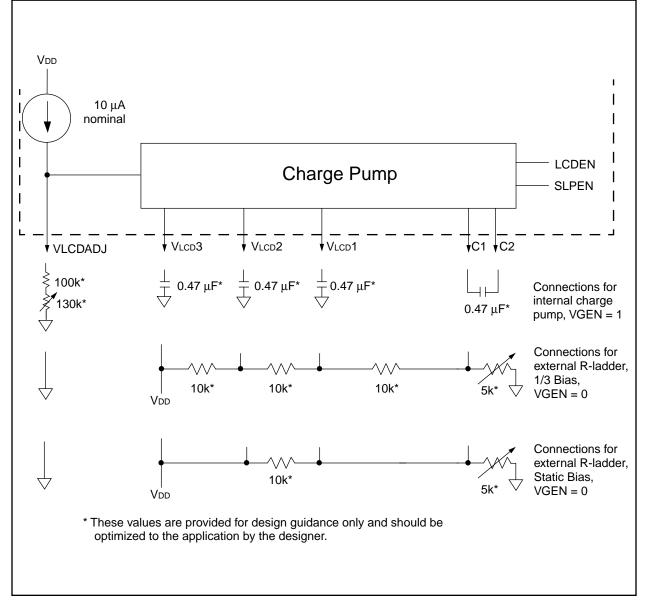

#### 13.5 Voltage Generation

There are two methods for LCD voltage generation, internal charge pump, or external resistor ladder.

#### 13.5.1 CHARGE PUMP

The LCD charge pump is shown in Figure 13-13. The 1.0V - 2.3V regulator will establish a stable base voltage from the varying battery voltage. This regulator is adjustable through the range by connecting a variable external resistor from VLCDADJ to ground. The potentiometer provides contrast adjustment for the LCD. This base voltage is connected to VLCD1 on the charge pump. The charge pump boosts VLCD1 into VLCD2 =

$2*V_{LCD1}$  and  $V_{LCD3} = 3*V_{LCD1}$ . When the charge pump is not operating, Vlcd3 will be internally tied to VDD. See the Electrical Specifications section for charge pump capacitor and potentiometer values.

#### 13.5.2 EXTERNAL R-LADDER

The LCD module can also use an external resistor ladder (R-Ladder) to generate the LCD voltages. Figure 13-13 shows external connections for static and 1/3 bias. The VGEN (LCDCON<4>) bit must be cleared to use an external R-Ladder.

#### FIGURE 13-13:CHARGE PUMP AND RESISTOR LADDER

### TABLE 15-2: PIC16CXXX INSTRUCTION SET

| Mnemonic,  |         | Description                                     | Cycles |     | 14-Bit       | Status       | Notes |                 |       |

|------------|---------|-------------------------------------------------|--------|-----|--------------|--------------|-------|-----------------|-------|

| Operands   |         |                                                 |        | MSb |              |              | LSb   | Affected        |       |

| BYTE-ORIE  | NTED    | FILE REGISTER OPERATIONS                        |        |     |              |              |       | -               |       |

| ADDWF      | f, d    | Add W and f                                     | 1      | 00  | 0111         |              | ffff  | C,DC,Z          | 1,2   |

| ANDWF      | f, d    | AND W with f                                    | 1      | 00  | 0101         |              | ffff  | Z               | 1,2   |

| CLRF       | f       | Clear f                                         | 1      | 00  | 0001         |              | ffff  | Z               | 2     |

| CLRW       | -       | Clear W                                         | 1      | 00  | 0001         |              | xxxx  | Z               |       |

| COMF       | f, d    | Complement f                                    | 1      | 00  |              | dfff         |       | Z               | 1,2   |

| DECF       | f, d    | Decrement f                                     | 1      | 00  |              | dfff         |       | Z               | 1,2   |

| DECFSZ     | f, d    | Decrement f, Skip if 0                          | 1(2)   | 00  | 1011         |              | ffff  |                 | 1,2,3 |

| INCF       | f, d    | Increment f                                     | 1      | 00  | 1010         | dfff         | ffff  | Z               | 1,2   |

| INCFSZ     | f, d    | Increment f, Skip if 0                          | 1(2)   | 00  | 1111         | dfff         | ffff  |                 | 1,2,3 |

| IORWF      | f, d    | Inclusive OR W with f                           | 1      | 00  | 0100         |              | ffff  | Z               | 1,2   |

| MOVF       | f, d    | Move f                                          | 1      | 00  | 1000         | dfff         | ffff  | Z               | 1,2   |

| MOVWF      | f       | Move W to f                                     | 1      | 00  | 0000         | lfff         | ffff  |                 |       |

| NOP        | -       | No Operation                                    | 1      | 00  | 0000         | 0xx0         | 0000  |                 |       |

| RLF        | f, d    | Rotate Left f through Carry                     | 1      | 00  | 1101         | dfff         | ffff  | С               | 1,2   |

| RRF        | f, d    | Rotate Right f through Carry                    | 1      | 00  | 1100         | dfff         | ffff  | С               | 1,2   |

| SUBWF      | f, d    | Subtract W from f                               | 1      | 00  | 0010         | dfff         | ffff  | C,DC,Z          | 1,2   |

| SWAPF      | f, d    | Swap nibbles in f                               | 1      | 00  | 1110         | dfff         | ffff  | - , - ,         | 1,2   |

| XORWF      | f, d    | Exclusive OR W with f                           | 1      | 00  | 0110         | dfff         | ffff  | z               | 1,2   |

| BIT-ORIENT | red fil | E REGISTER OPERATIONS                           |        |     |              |              |       |                 |       |

| BCF        | f, b    | Bit Clear f                                     | 1      | 01  | 00bb         | bfff         | ffff  |                 | 1,2   |

| BSF        | f, b    | Bit Set f                                       | 1      | 01  | 01bb         | bfff         | ffff  |                 | 1,2   |

| BTFSC      | f, b    | Bit Test f, Skip if Clear                       | 1 (2)  | 01  | 10bb         | bfff         | ffff  |                 | 3     |

| BTFSS      | f, b    | Bit Test f, Skip if Set                         | 1 (2)  | 01  | 11bb         | bfff         | ffff  |                 | 3     |

| LITERAL A  | ND CO   | NTROL OPERATIONS                                | 1      |     |              |              |       |                 |       |

| ADDLW      | k       | Add literal and W                               | 1      | 11  | 111x         | kkkk         | kkkk  | C,DC,Z          |       |

| ANDLW      | k       | AND literal with W                              | 1      | 11  | 1001         | kkkk         | kkkk  | Z               |       |

| CALL       | k       | Call subroutine                                 | 2      | 10  | 0kkk         | kkkk         | kkkk  |                 |       |

| CLRWDT     | -       | Clear Watchdog Timer                            | 1      | 00  | 0000         | 0110         | 0100  | TO,PD           |       |

| GOTO       | k       | Go to address                                   | 2      | 10  | 1kkk         | kkkk         | kkkk  |                 |       |

| IORLW      | k       | Inclusive OR literal with W                     | 1      | 11  | 1000         | kkkk         | kkkk  | Z               |       |

| MOVLW      | k       | Move literal to W                               | 1      | 11  | 00xx         | kkkk         | kkkk  |                 |       |

| RETFIE     | -       | Return from interrupt                           | 2      | 00  | 0000         | 0000         | 1001  |                 |       |

| RETLW      | k       | Return with literal in W                        | 2      | 11  | 01xx         | kkkk         | kkkk  |                 |       |

| RETURN     | -       | Return from Subroutine                          | 2      | 00  | 0000         | 0000         | 1000  |                 |       |

|            |         |                                                 |        |     |              |              |       |                 |       |

| SLEEP      | -       | Go into standby mode                            | 1      | 00  | 0000         | 0110         | 0011  | I 10,PD         |       |

| -          | -<br>k  | Go into standby mode<br>Subtract W from literal | 1      | 11  | 0000<br>110x | 0110<br>kkkk |       | TO,PD<br>C,DC,Z |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRWDT            | Clear Watchdog Timer                                                                                                                               |                       |                 |                         |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------------|--|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                          | [label] CLRWDT        |                 |                         |  |  |  |  |  |  |  |

| Operands:         | None                                                                                                                                               |                       |                 |                         |  |  |  |  |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |                       |                 |                         |  |  |  |  |  |  |  |

| Status Affected:  | TO, PD                                                                                                                                             |                       |                 |                         |  |  |  |  |  |  |  |

| Encoding:         | 00 0000 0110 0100                                                                                                                                  |                       |                 |                         |  |  |  |  |  |  |  |

| Description:      | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD are<br>set.                   |                       |                 |                         |  |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                  |                       |                 |                         |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                  |                       |                 |                         |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                 | Q2                    | Q3              | Q4                      |  |  |  |  |  |  |  |

|                   | Decode                                                                                                                                             | No-<br>Operation      | Process<br>data | Clear<br>WDT<br>Counter |  |  |  |  |  |  |  |

| Example           | CLRWDT                                                                                                                                             |                       |                 |                         |  |  |  |  |  |  |  |

|                   | Before In                                                                                                                                          | struction<br>WDT cour | nter =          | ?                       |  |  |  |  |  |  |  |

|                   | After Instruction<br>WDT counter = $0x00$<br>WDT prescaler= $0$<br>TO = $1$<br>PD = $1$                                                            |                       |                 |                         |  |  |  |  |  |  |  |

| COMF                                                                                                                          | Compler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nent f                                                                                                   |                                                                                                |                                                                         |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                                       | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | COMF                                                                                                     | f,d                                                                                            |                                                                         |  |  |  |  |  |  |

| Operands:                                                                                                                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |                                                                                                |                                                                         |  |  |  |  |  |  |

| Operation:                                                                                                                    | $(\bar{f}) \rightarrow (de)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | stination                                                                                                | )                                                                                              |                                                                         |  |  |  |  |  |  |