Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923t-04-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 4-2: REGISTER FILE MAP

|                                   | File<br>Address |                                | File<br>Address |                                                   | File<br>Address | ŀ                              | File<br>Address |

|-----------------------------------|-----------------|--------------------------------|-----------------|---------------------------------------------------|-----------------|--------------------------------|-----------------|

| Indirect addr.(1)                 | 00h             | Indirect addr.(1)              | 80h             | Indirect addr.(1)                                 | 100h            | Indirect addr.(1)              | 180h            |

| TMR0                              | 01h             | OPTION                         | 81h             | TMR0                                              | 101h            | OPTION                         | 181h            |

| PCL                               | 02h             | PCL                            | 82h             | PCL                                               | 102h            | PCL                            | 182h            |

| STATUS                            | 03h             | STATUS                         | 83h             | STATUS                                            | 103h            | STATUS                         | 183h            |

| FSR                               | 04h             | FSR                            | 84h             | FSR                                               | 104h            | FSR                            | 184h            |

| PORTA                             | 05h             | TRISA                          | 85h             |                                                   | 105h            |                                | 185h            |

| PORTB                             | 06h             | TRISB                          | 86h             | PORTB                                             | 106h            | TRISB                          | 186h            |

| PORTC                             | 07h             | TRISC                          | 87h             | PORTF                                             | 107h            | TRISF                          | 187h            |

| PORTD                             | 08h             | TRISD                          | 88h             | PORTG                                             | 108h            | TRISG                          | 188h            |

| PORTE                             | 09h             | TRISE                          | 89h             |                                                   | 109h            |                                | 189h            |

| PCLATH                            | 0Ah             | PCLATH                         | 8Ah             | PCLATH                                            | 10Ah            | PCLATH                         | 18Ah            |

| INTCON                            | 0Bh             | INTCON                         | 8Bh             | INTCON                                            | 10Bh            | INTCON                         | 18Bh            |

| PIR1                              | 0Ch             | PIE1                           | 8Ch             |                                                   | 10Ch            |                                | 18Ch            |

|                                   | 0Dh             |                                | 8Dh             | LCDSE                                             | 10Dh            |                                | 18Dh            |

| TMR1L                             | 0Eh             | PCON                           | 8Eh             | LCDPS                                             | 10Eh            |                                | 18Eh            |

| TMR1H                             | 0Fh             | 1001                           | 8Fh             | LCDCON                                            | 10Fh            |                                | 18Fh            |

| T1CON                             | 10h             |                                | 90h             | LCDD00                                            | 110h            |                                | 190h            |

| TMR2                              | 11h             |                                | 91h             | LCDD00                                            | 111h            |                                | 191h            |

| T2CON                             | 12h             | PR2                            | 92h             | LCDD01                                            | 112h            |                                | 192h            |

| SSPBUF                            | 13h             | SSPADD                         | 93h             | LCDD02                                            | 113h            |                                | 193h            |

| SSPCON                            | 14h             | SSPADD                         | 9311<br>94h     | LCDD03                                            | 114h            |                                | 193h            |

| CCPR1L                            | 15h             | 33F3TAI                        | 9411<br>95h     |                                                   | 115h            |                                | 195h            |

| CCPR1H                            | 16h             |                                | 96h             | LCDD05                                            | 116h            |                                | 196h            |

| CCP1CON                           | 17h             |                                | 901<br>97h      | LCDD06                                            | 117h            |                                | 1901            |

| COFICON                           | 1711<br>18h     |                                |                 | LCDD07                                            | 118h            |                                | 1971<br>198h    |

|                                   | 19h             |                                | 98h             | LCDD08                                            | 119h            |                                | 199h            |

|                                   | 1Ah             |                                | 99h             | LCDD09                                            | 11Ah            |                                | 1990<br>19Ah    |

|                                   | 1Bh             |                                | 9Ah             | LCDD10                                            | 11Bh            |                                | 19An<br>19Bh    |

|                                   | 1Ch             |                                | 9Bh             | LCDD11                                            | 11Ch            |                                |                 |

|                                   | 1Dh             |                                | 9Ch             | LCDD12                                            | 11Dh            |                                | 19Ch            |

| ADRES <sup>(2)</sup>              | 1Eh             |                                | 9Dh             | LCDD13                                            | 11Eh            |                                | 19Dh            |

| ADRES(=)<br>ADCON0 <sup>(2)</sup> | 1En<br>1Fh      | ADCON1 <sup>(2)</sup>          | 9Eh             | LCDD14                                            | 11Fh            |                                | 19Eh            |

| ADCONU /                          |                 | ADCON1-                        | 9Fh             | LCDD15                                            | 120h            |                                | 19Fh            |

|                                   | 20h             |                                | A0h             |                                                   | 12011           |                                | 1A0h            |

| General<br>Purpose                |                 | General<br>Purpose<br>Register |                 |                                                   |                 |                                |                 |

| Register                          |                 |                                | EFh             |                                                   | 16F             |                                | 1EFh            |

| -                                 |                 | Mapped in<br>Bank 0<br>70h-7Fh | F0h             | Mapped in<br>Bank 0<br>70h-7Fh                    | 170             | Mapped in<br>Bank 0<br>70h-7Fh | 1F0h            |

|                                   | 7Fh             |                                | FFh             |                                                   | 17F             |                                | 1FFh            |

| Bank 0                            |                 | Bank 1                         |                 | Bank 2                                            |                 | Bank 3                         |                 |

|                                   |                 | Note 1: Not a p                | hysical reg     | a memory locations<br>ister.<br>e not implemented |                 |                                |                 |

#### TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address | Name   | Bit 7         | Bit 6           | Bit 5        | Bit 4        | Bit 3          | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|--------|---------------|-----------------|--------------|--------------|----------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 3  |        |               |                 |              |              |                |                  |                |          |                               |                           |

| 180h    | INDF   | Addressing    | this location   | uses conten  | ts of FSR to | address data   | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 181h    | OPTION | RBPU          | INTEDG          | TOCS         | T0SE         | PSA            | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 182h    | PCL    | Program Co    | ounter's (PC)   | Least Signif | icant Byte   |                |                  |                |          | 0000 0000                     | 0000 0000                 |

| 183h    | STATUS | IRP           | RP1             | RP0          | TO           | PD             | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 184h    | FSR    | Indirect data | a memory ad     | dress pointe | r            |                |                  |                |          | XXXX XXXX                     | uuuu uuuu                 |

| 185h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 186h    | TRISB  | PORTB Dat     | ta Direction R  | egister      |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 187h    | TRISF  | PORTF Dat     | a Direction R   | egister      |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 188h    | TRISG  | PORTG Da      | ta Direction F  | Register     |              |                |                  |                |          | 1111 1111                     | 1111 1111                 |

| 189h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 18Ah    | PCLATH | _             | _               | _            | Write Buffe  | r for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 18Bh    | INTCON | GIE           | PEIE            | TOIE         | INTE         | RBIE           | TOIF             | INTF           | RBIF     | 0000 000x                     | 0000 000u                 |

| 18Ch    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 18Dh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 18Eh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 18Fh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 190h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 191h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 192h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 193h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 194h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 195h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 196h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 197h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 198h    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | -                             | _                         |

| 199h    | _      | Unimpleme     | Unimplemented   |              |              |                |                  |                | -        | _                             |                           |

| 19Ah    | _      | Unimpleme     | Unimplemented   |              |              |                |                  |                | -        | _                             |                           |

| 19Bh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | —                         |

| 19Ch    | _      | Unimpleme     | Unimplemented   |              |              |                |                  |                | _        | —                             |                           |

| 19Dh    | _      | Unimpleme     | Unimplemented — |              |              |                |                  |                | _        | _                             |                           |

| 19Eh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

| 19Fh    | _      | Unimpleme     | nted            |              |              |                |                  |                |          | _                             | _                         |

Legend:

d: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0', shaded locations are unimplemented, read as '0'.

1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

2: These bits are reserved on the PIC16C923, always maintain these bits clear.

3: These pixels do not display, but can be used as general purpose RAM.

4: PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

5: Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear. Note

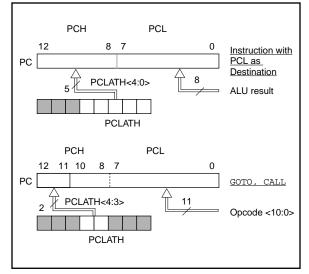

#### 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-9 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-9: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Program Memory Paging

PIC16C9XX devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: The PIC16C9XX ignores paging bit PCLATH<4>, which is used to access program memory pages 2 and 3. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### TABLE 5-1:PORTA FUNCTIONS

| Name                        | Bit# | Buffer | Function                                                                       |

|-----------------------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0 <sup>(1)</sup>      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1 <sup>(1)</sup>      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2 <sup>(1)</sup>      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF <sup>(1)</sup> | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI                   | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type   |

| RA5/AN4/SS (1)              | bit5 | TTL    | Input/output or analog input or slave select input for synchronous serial port |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The AN and VREF functions are for the A/D module and are only implemented on the PIC16C924.

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address            | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4                                 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>resets |

|--------------------|--------|-------|-------|---------|---------------------------------------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 05h                | PORTA  |       | —     | RA5     | RA4                                   | RA3   | RA2   | RA1   | RA0   | (2)                           | (2)                             |

| 85h                | TRISA  | —     | —     | PORTA D | PORTA Data Direction Control Register |       |       |       |       | 11 1111                       | 11 1111                         |

| 9Fh <sup>(1)</sup> | ADCON1 | —     | —     | _       | _                                     | _     | PCFG2 | PCFG1 | PCFG0 | 000                           | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: The ADCON1 register is implemented on the PIC16C924 only.

2: PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

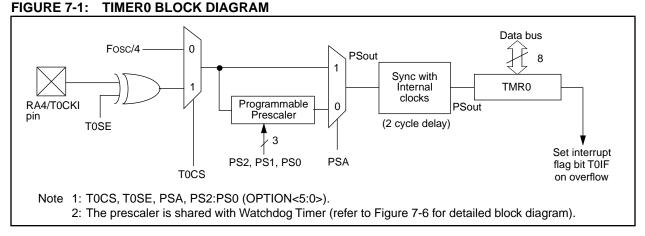

#### 7.0 TIMER0 MODULE

The Timer0 module has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

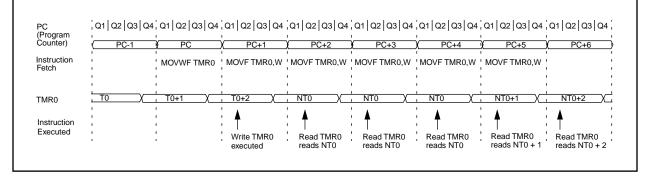

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION<5>). In counter mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION<4>). Clearing

bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

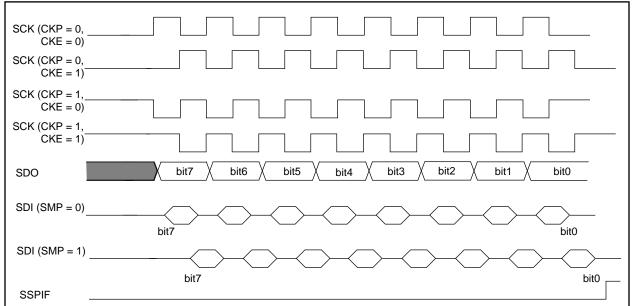

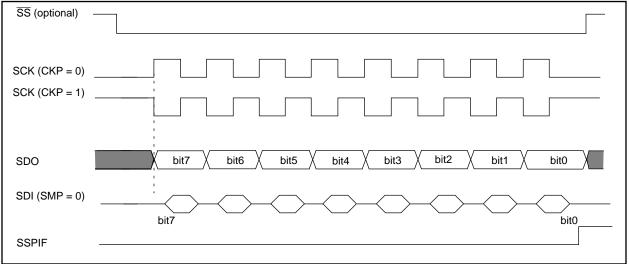

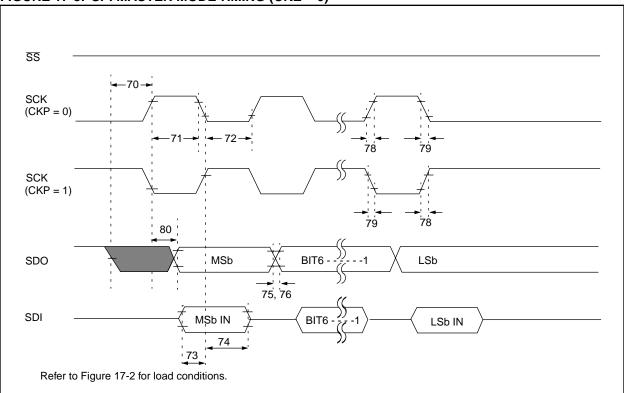

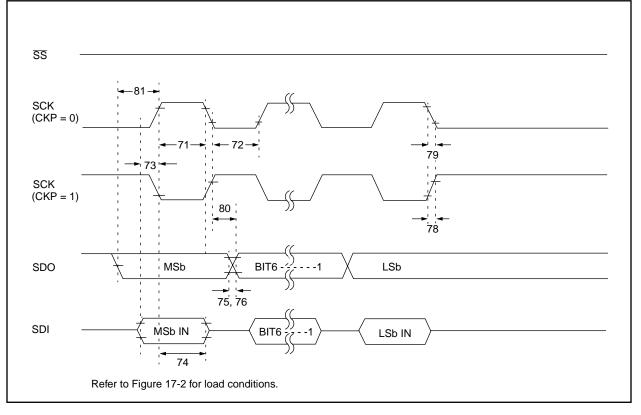

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

- Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- **Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#### FIGURE 11-5: SPI MODE TIMING, MASTER MODE

#### FIGURE 11-6: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

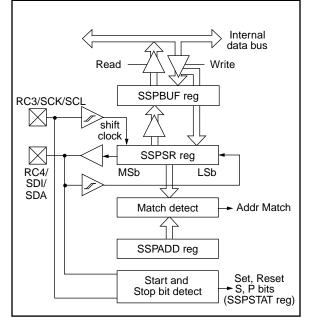

#### 11.3 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

#### FIGURE 11-18: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

٦

#### 11.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

## FIGURE 11-19: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W=0         Receiving Data         ACK         Receiving Data           SDA           AT_XA6_XA5_XA4_XA3_XA2_XA1        ACK_D7_XD6_XD5_XD4_XD3_XD2_XD1_XD0 |                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                            | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u><br>Bit SSPOV is set because the SSPBUF register is still full.<br>ACK is not sent                                                                      |                                      |

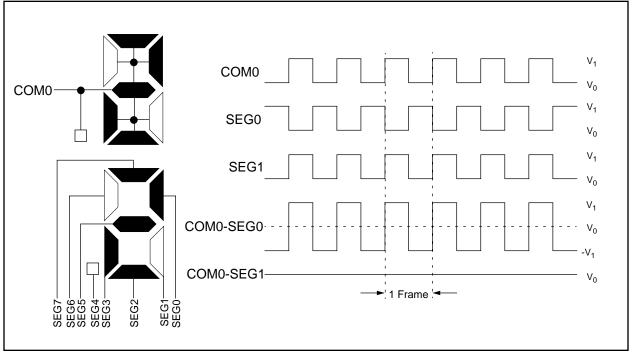

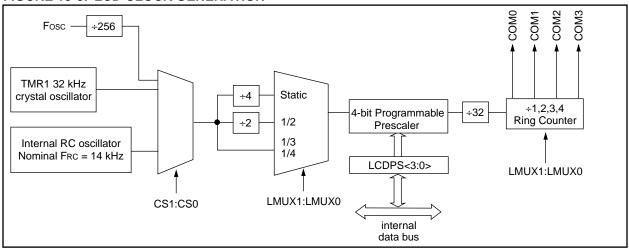

#### 13.1 LCD Timing

The LCD module has 3 possible clock source inputs and supports static, 1/2, 1/3, and 1/4 multiplexing.

#### 13.1.1 TIMING CLOCK SOURCE SELECTION

The clock sources for the LCD timing generation are:

- Internal RC oscillator

- Timer1 oscillator

- System clock divided by 256

The first timing source is an internal RC oscillator which runs at a nominal frequency of 14 kHz. This oscillator provides a lower speed clock which may be used to continue running the LCD while the processor is in sleep. The RC oscillator will power-down when it is not selected or when the LCD module is disabled. The second source is the Timer1 external oscillator. This oscillator provides a lower speed clock which may be used to continue running the LCD while the processor is in sleep. It is assumed that the frequency provided on this oscillator will be 32 kHz. To use the Timer1 oscillator as a LCD module clock source, it is only necessary to set the T1OSCEN (T1CON<3>) bit.

The third source is the system clock divided by 256. This divider ratio is chosen to provide about 32 kHz output when the external oscillator is 8 MHz. The divider is not programmable. Instead the LCDPS register is used to set the LCD frame clock rate.

All of the clock sources are selected with bits CS1:CS0 (LCDCON<3:2>). Refer to Figure 13-1 for details of the register programming.

#### FIGURE 13-8: LCD CLOCK GENERATION

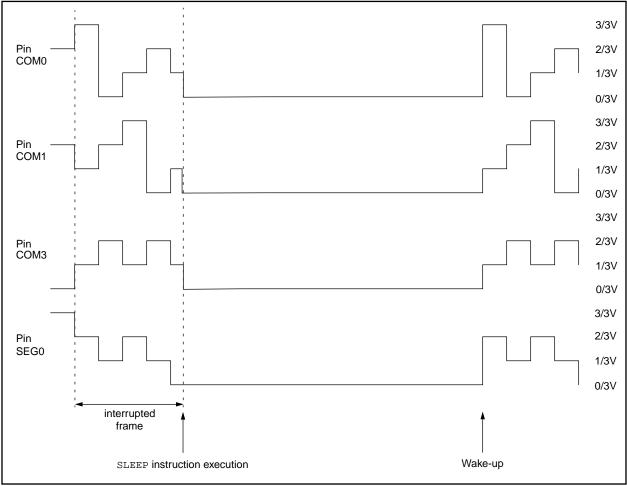

#### 13.4 Operation During Sleep

The LCD module can operate during sleep. The selection is controlled by bit SLPEN (LCDCON<6>). Setting the SLPEN bit allows the LCD module to go to sleep. Clearing the SLPEN bit allows the module to continue to operate during sleep.

If a SLEEP instruction is executed and SLPEN = '1', the LCD module will cease all functions and go into a very low current consumption mode. The module will stop operation immediately and drive the minimum LCD voltage on both segment and common lines. Figure 13-11 shows this operation. To ensure that the LCD completes the frame, the SLEEP instruction should be executed immediately after a LCD frame boundary.

The LCD interrupt can be used to determine the frame boundary. See Section 13.2 for the formulas to calculate the delay.

If a SLEEP instruction is executed and SLPEN = '0', the module will continue to display the current contents of the LCDD registers. To allow the module to continue operation while in sleep, the clock source must be either the internal RC oscillator or Timer1 external oscillator. While in sleep, the LCD data cannot be changed. The LCD module current consumption will not decrease in this mode, however the overall consumption of the device will be lower due to shutdown of the core and other peripheral functions.

Note: The internal RC oscillator or external Timer1 oscillator must be used to operate the LCD module during sleep.

#### FIGURE 13-11:SLEEP ENTRY/EXIT WHEN SLPEN = 1 OR CS1:CS0 = 00

| CLRF              | Clear f                                    |                                                                |                 |                       |  |  |  |

|-------------------|--------------------------------------------|----------------------------------------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] C                         | LRF f                                                          |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$                           | 27                                                             |                 |                       |  |  |  |

| Operation:        | $00h \rightarrow (f)$<br>1 $\rightarrow Z$ | 1                                                              |                 |                       |  |  |  |

| Status Affected:  | Z                                          |                                                                |                 |                       |  |  |  |

| Encoding:         | 00                                         | 0001                                                           | lfff            | ffff                  |  |  |  |

| Description:      |                                            | The contents of register 'f' are cleared and the Z bit is set. |                 |                       |  |  |  |

| Words:            | 1                                          |                                                                |                 |                       |  |  |  |

| Cycles:           | 1                                          |                                                                |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                         | Q2                                                             | Q3              | Q4                    |  |  |  |

|                   | Decode                                     | Read<br>register<br>'f'                                        | Process<br>data | Write<br>register 'f' |  |  |  |

|                   |                                            |                                                                |                 |                       |  |  |  |

| Example           | CLRF                                       | FLAG                                                           | S_REG           |                       |  |  |  |

| After Instruction |                                            |                                                                |                 | 0x5A<br>0x00          |  |  |  |

|                   |                                            | Z                                                              | =               | 1                     |  |  |  |

| CLRW               | Clear W                              |                  |                 |               |

|--------------------|--------------------------------------|------------------|-----------------|---------------|

| Syntax:            | [ label ]                            | CLRW             |                 |               |

| Operands:          | None                                 |                  |                 |               |

| Operation:         | $00h \rightarrow (V 1 \rightarrow Z$ | V)               |                 |               |

| Status Affected:   | Z                                    |                  |                 |               |

| Encoding:          | 00                                   | 0001             | 0xxx            | xxxx          |

| Description:       | W register<br>set.                   | is cleared       | . Zero bit (    | Z) is         |

| Words:             | 1                                    |                  |                 |               |

| Cycles:            | 1                                    |                  |                 |               |

| Q Cycle Activity:  | Q1                                   | Q2               | Q3              | Q4            |

|                    | Decode                               | No-<br>Operation | Process<br>data | Write to<br>W |

| Example            | CLRW                                 |                  |                 |               |

| Before Instruction |                                      |                  |                 |               |

|                    |                                      |                  | 0x5A            |               |

|                    | After Inst                           |                  | 0200            |               |

|                    |                                      | VV =             | 0x00            |               |

# PIC16C9XX

| INCF                                                                | Increment f                                                                                                                                                                        | INCFSZ                                                  | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                             | [ <i>label</i> ] INCF f,d                                                                                                                                                          | Syntax:                                                 | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                        |

| Operands:                                                           | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                         | Operands:                                               | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                         |

| Operation:<br>Status Affected:                                      | (f) + 1 $\rightarrow$ (destination)<br>Z                                                                                                                                           | Operation:                                              | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                         |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 001010dfffffffThe contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.1112Q1Q2Q3Q4 | Status Affected:<br>Encoding:<br>Description:<br>Words: | Oo     1111     dfff     ffff       The contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.     If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead making it a 2TcY instruction. |

| Example                                                             | Decode     Read<br>register<br>'f'     Process<br>data     Write to<br>destination       INCF     CNT , 1                                                                          | Cycles:<br>Q Cycle Activity:                            | 1(2)<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to                                                                                                                                                                                                                                                                                |

| Livanipie                                                           | Before Instruction<br>CNT = 0xFF $Z = 0$ After Instruction<br>CNT = 0x00 $Z = 1$                                                                                                   | lf Skip:                                                | register 'f'datadestination(2nd Cycle)Q1Q2Q3Q4No-<br>OperationNo-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                                                                     |

|                                                                     |                                                                                                                                                                                    | Example                                                 | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction                                                                                                                                                                                                            |

CNT = CNT + 1 if CNT= 0, PC = address CONTINUE

if  $CNT \neq 0$ , PC = address HERE +1

| NOP               | No Operation |                  |                  |                  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |

| Operation:        | No opera     | ation            |                  |                  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |

| Description:      | No operat    | ion.             |                  |                  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |

|                   | Decode       | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |

| Example           | NOP          |                  |                  |                  |  |  |

| Return from Interrupt                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [ label ]                                                                                                                                                                                                         | RETFIE                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| None                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| $\begin{array}{l} TOS \rightarrow F \\ 1 \rightarrow GIE \end{array}$                                                                                                                                             | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| None                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 00                                                                                                                                                                                                                | 0000                                                                                                                                                                                                                                                                                          | 0000                                                                                                                                                                                                                                          | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in the<br>PC. Interrupts are enabled by setting<br>Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Q1                                                                                                                                                                                                                | Q2                                                                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                            | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Decode                                                                                                                                                                                                            | No-<br>Operation                                                                                                                                                                                                                                                                              | Set the<br>GIE bit                                                                                                                                                                                                                            | Pop from the Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| No-<br>Operation                                                                                                                                                                                                  | No-<br>Operation                                                                                                                                                                                                                                                                              | No-<br>Operation                                                                                                                                                                                                                              | No-<br>Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                                                                                                                   | $\begin{bmatrix} label \\ None \\ TOS \rightarrow F \\ 1 \rightarrow GIE \\ None \\ \hline 00 \\ \hline 00 \\ Return fro and Top of PC. Interru Global Interru Global Interru Global Interru Global Interru Global Interruction 1 \\ 2 \\ Q1 \\ \hline Decode \\ \hline No- \\ \end{bmatrix}$ | $[label] RETFIE$ None $TOS \rightarrow PC,$ $1 \rightarrow GIE$ None $00 0000$ Return from Interrup and Top of Stack (TC PC. Interrupts are er Global Interrupt Ena (INTCON<7>). This is instruction. 1 2 Q1 Q2 $Decode No-Operation$ No- No- | $\begin{bmatrix} label \end{bmatrix} \text{ RETFIE} \\ \text{None} \\ \hline \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \\ \hline \text{None} \\ \hline 00 & 0000 & 0000 \\ \hline 0000 & 0000 \\ \hline \text{Return from Interrupt. Stack is and Top of Stack (TOS) is loade PC. Interrupts are enabled by s Global Interrupt Enable bit, GIE (INTCON<7>). This is a two cyrinstruction. \\ 1 \\ 2 \\ \hline Q1 & Q2 & Q3 \\ \hline \hline \text{Decode} & \frac{\text{No-}}{\text{Operation}} & \frac{\text{Set the}}{\text{GIE bit}} \\ \hline \text{No-} & \text{No-} & \text{No-} \\ \hline \end{array}$ |  |  |  |

Example

RETFIE

After Interrupt

| PC  | = | TOS |

|-----|---|-----|

| GIE | = | 1   |

| OPTION           | Load Op                                                                                                                                                                                                                                            | tion Reg | gister |      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                     |          |        |      |

| Operands:        | None                                                                                                                                                                                                                                               |          |        |      |

| Operation:       | $(W) \to OPTION$                                                                                                                                                                                                                                   |          |        |      |

| Status Affected: | None                                                                                                                                                                                                                                               |          |        |      |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000     | 0110   | 0010 |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |          |        |      |

| Words:           | 1                                                                                                                                                                                                                                                  |          |        |      |

| Cycles:          | 1                                                                                                                                                                                                                                                  |          |        |      |

| Example          |                                                                                                                                                                                                                                                    |          |        |      |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                 |          |        |      |

#### 16.0 DEVELOPMENT SUPPORT

#### 16.1 Development Tools

The PICmicro<sup>™</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

#### 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 16.3 ICEPIC: Low-Cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

### **17.0 ELECTRICAL CHARACTERISTICS**

| Absolute Maximum Ratings †                                                                                                                   |                      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Ambient temperature under bias                                                                                                               | 55°C to +125°C       |  |  |  |

| Storage temperature                                                                                                                          | 65°C to +150°C       |  |  |  |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                           | 0.3V to (VDD + 0.3V) |  |  |  |

| Voltage on VDD with respect to Vss                                                                                                           | 0.3V to +7.5V        |  |  |  |

| Voltage on MCLR with respect to Vss                                                                                                          | 0V to +14V           |  |  |  |

| Voltage on RA4 with respect to Vss                                                                                                           | 0V to +14V           |  |  |  |

| Total power dissipation (Note 1)                                                                                                             | 1.0W                 |  |  |  |

| Maximum current out of Vss pin                                                                                                               | 300 mA               |  |  |  |

| Maximum current into Vod pin                                                                                                                 | 250 mA               |  |  |  |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                 | ±20 mA               |  |  |  |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                                               | ±20 mA               |  |  |  |

| Maximum output current sunk by any I/O pin                                                                                                   | 10 mA                |  |  |  |

| Maximum output current sourced by any I/O pin                                                                                                | 10 mA                |  |  |  |

| Maximum current sunk by all Ports combined                                                                                                   | 200 mA               |  |  |  |