Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI                                                                    |

| Peripherals                | LCD, POR, PWM, WDT                                                          |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 176 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923t-04-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0 General Description                          | 5  |  |  |  |  |

|--------------------------------------------------|----|--|--|--|--|

| 2.0 PIC16C9XX Device Varieties                   | 7  |  |  |  |  |

| 3.0 Architectural Overview                       | 9  |  |  |  |  |

| 4.0 Memory Organization                          | 17 |  |  |  |  |

| 5.0 Ports                                        | 31 |  |  |  |  |

| 6.0 Overview of Timer Modules                    | 43 |  |  |  |  |

| 7.0 Timer0 Module                                | 45 |  |  |  |  |

| 8.0 Timer1 Module                                | 51 |  |  |  |  |

| 9.0 Timer2 Module                                | 55 |  |  |  |  |

| 10.0 Capture/Compare/PWM (CCP) Module            | 57 |  |  |  |  |

| 11.0 Synchronous Serial Port (SSP) Module        | 63 |  |  |  |  |

| 12.0 Analog-to-Digital Converter (A/D) Module    | 79 |  |  |  |  |

| 13.0 LCD Module                                  | 89 |  |  |  |  |

| 14.0 Special Features of the CPU1                | 03 |  |  |  |  |

| 15.0 Instruction Set Summary                     | 19 |  |  |  |  |

| 16.0 Development Support                         | 37 |  |  |  |  |

| 17.0 Electrical Characteristics                  | 41 |  |  |  |  |

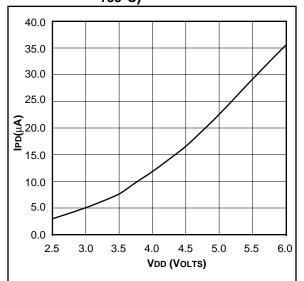

| 18.0 DC and AC Characteristics Graphs and Tables | 61 |  |  |  |  |

| 19.0 Packaging Information                       | 71 |  |  |  |  |

| Appendix A:                                      | 75 |  |  |  |  |

| Appendix B: Compatibility                        | 75 |  |  |  |  |

| Appendix C: What's New1                          | 76 |  |  |  |  |

| Appendix D: What's Changed1                      | 76 |  |  |  |  |

| Index 1                                          | 77 |  |  |  |  |

| ist of Equations And Examples                    |    |  |  |  |  |

| ist of Figures                                   |    |  |  |  |  |

| ist of Tables                                    |    |  |  |  |  |

| Reader Response                                  |    |  |  |  |  |

| PIC16C9XX Product Identification System          |    |  |  |  |  |

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

# TABLE 3-1: PIC16C9XX PINOUT DESCRIPTION (Cont.'d)

| Pin Name                        | DIP<br>Pin#                                                      | PLCC<br>Pin# | TQFP<br>Pin# | Pin<br>Type | Buffer<br>Type | Description                                                                     |

|---------------------------------|------------------------------------------------------------------|--------------|--------------|-------------|----------------|---------------------------------------------------------------------------------|

| VLCD3                           | 19                                                               | 20           | 11           | Р           | _              | LCD Voltage.                                                                    |

| Vdd                             | 20, 60                                                           | 22, 64       | 12, 52       | Р           | —              | Digital power.                                                                  |

| Vss                             | 6, 21                                                            | 7, 23        | 13, 62       | Р           | _              | Ground reference.                                                               |

| NC                              | -                                                                | 1            | _            | _           | —              | These pins are not internally connected. These pins should be left unconnected. |

| Legend: I = input<br>— = Not us | d: I = input O = output P = power<br>— = Not used TTL = TTL inpu |              |              | •           |                | L = LCD Driver<br>ST = Schmitt Trigger input                                    |

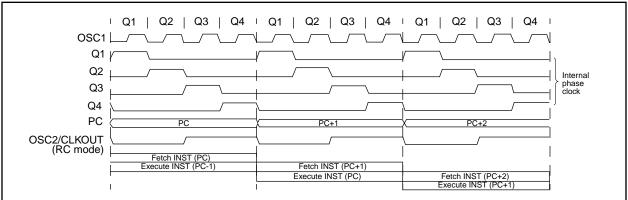

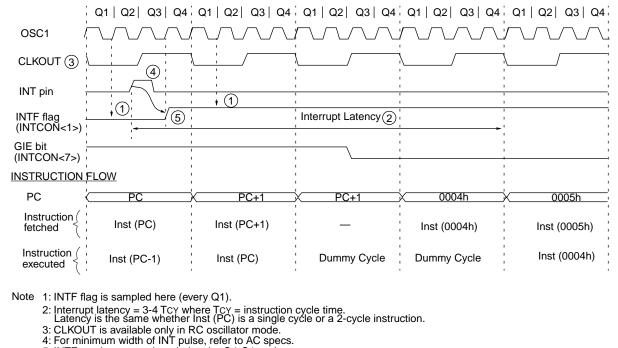

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

|                                                                                                                                                                                                                    | Tcy0       | Tcy1      | Tcy2      | Tcy3      | Tcy4        | Tcy5          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----------|-----------|-------------|---------------|--|

| 1. MOVLW 55h                                                                                                                                                                                                       | Fetch 1    | Execute 1 |           |           |             |               |  |

| 2. MOVWF PORTB                                                                                                                                                                                                     |            | Fetch 2   | Execute 2 |           |             |               |  |

| 3. CALL SUB_1                                                                                                                                                                                                      |            |           | Fetch 3   | Execute 3 |             |               |  |

| 4. BSF PORTA, BIT3 (F                                                                                                                                                                                              | orced NOP) |           |           | Fetch 4   | Flush       |               |  |

| 5. Instruction @ addres                                                                                                                                                                                            | s SUB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |  |

|                                                                                                                                                                                                                    |            |           |           |           |             |               |  |

|                                                                                                                                                                                                                    |            |           |           |           |             |               |  |

| All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed. |            |           |           |           |             |               |  |

# FIGURE 4-2: REGISTER FILE MAP

|                                   | File<br>Address |                                | File<br>Address |                                                   | File<br>Address | ŀ                              | File<br>Address |

|-----------------------------------|-----------------|--------------------------------|-----------------|---------------------------------------------------|-----------------|--------------------------------|-----------------|

| Indirect addr.(1)                 | 00h             | Indirect addr.(1)              | 80h             | Indirect addr.(1)                                 | 100h            | Indirect addr.(1)              | 180h            |

| TMR0                              | 01h             | OPTION                         | 81h             | TMR0                                              | 101h            | OPTION                         | 181h            |

| PCL                               | 02h             | PCL                            | 82h             | PCL                                               | 102h            | PCL                            | 182h            |

| STATUS                            | 03h             | STATUS                         | 83h             | STATUS                                            | 103h            | STATUS                         | 183h            |

| FSR                               | 04h             | FSR                            | 84h             | FSR                                               | 104h            | FSR                            | 184h            |

| PORTA                             | 05h             | TRISA                          | 85h             |                                                   | 105h            |                                | 185h            |

| PORTB                             | 06h             | TRISB                          | 86h             | PORTB                                             | 106h            | TRISB                          | 186h            |

| PORTC                             | 07h             | TRISC                          | 87h             | PORTF                                             | 107h            | TRISF                          | 187h            |

| PORTD                             | 08h             | TRISD                          | 88h             | PORTG                                             | 108h            | TRISG                          | 188h            |

| PORTE                             | 09h             | TRISE                          | 89h             |                                                   | 109h            |                                | 189h            |

| PCLATH                            | 0Ah             | PCLATH                         | 8Ah             | PCLATH                                            | 10Ah            | PCLATH                         | 18Ah            |

| INTCON                            | 0Bh             | INTCON                         | 8Bh             | INTCON                                            | 10Bh            | INTCON                         | 18Bh            |

| PIR1                              | 0Ch             | PIE1                           | 8Ch             |                                                   | 10Ch            |                                | 18Ch            |

|                                   | 0Dh             |                                | 8Dh             | LCDSE                                             | 10Dh            |                                | 18Dh            |

| TMR1L                             | 0Eh             | PCON                           | 8Eh             | LCDPS                                             | 10Eh            |                                | 18Eh            |

| TMR1H                             | 0Fh             | 1001                           | 8Fh             | LCDCON                                            | 10Fh            |                                | 18Fh            |

| T1CON                             | 10h             |                                | 90h             | LCDD00                                            | 110h            |                                | 190h            |

| TMR2                              | 11h             |                                | 91h             | LCDD00                                            | 111h            |                                | 191h            |

| T2CON                             | 12h             | PR2                            | 92h             | LCDD01                                            | 112h            |                                | 192h            |

| SSPBUF                            | 13h             | SSPADD                         | 93h             | LCDD02                                            | 113h            |                                | 193h            |

| SSPCON                            | 14h             | SSPADD                         | 9311<br>94h     | LCDD03                                            | 114h            |                                | 193h            |

| CCPR1L                            | 15h             | 33F3TAI                        | 9411<br>95h     |                                                   | 115h            |                                | 195h            |

| CCPR1H                            | 16h             |                                | 96h             | LCDD05                                            | 116h            |                                | 196h            |

| CCP1CON                           | 17h             |                                | 901<br>97h      | LCDD06                                            | 117h            |                                | 1901            |

| CUPTOON                           | 1711<br>18h     |                                |                 | LCDD07                                            | 118h            |                                | 1971<br>198h    |

|                                   | 19h             |                                | 98h             | LCDD08                                            | 119h            |                                | 199h            |

|                                   | 1Ah             |                                | 99h             | LCDD09                                            | 11Ah            |                                | 1990<br>19Ah    |

|                                   | 1Bh             |                                | 9Ah             | LCDD10                                            | 11Bh            |                                | 19An<br>19Bh    |

|                                   | 1Ch             |                                | 9Bh             | LCDD11                                            | 11Ch            |                                |                 |

|                                   | 1Dh             |                                | 9Ch             | LCDD12                                            | 11Dh            |                                | 19Ch            |

| ADRES <sup>(2)</sup>              | 1Eh             |                                | 9Dh             | LCDD13                                            | 11Eh            |                                | 19Dh            |

| ADRES(=)<br>ADCON0 <sup>(2)</sup> | 1En<br>1Fh      | ADCON1 <sup>(2)</sup>          | 9Eh             | LCDD14                                            | 11Fh            |                                | 19Eh            |

| ADCONU /                          |                 | ADCON1-                        | 9Fh             | LCDD15                                            | 120h            |                                | 19Fh            |

|                                   | 20h             |                                | A0h             |                                                   | 12011           |                                | 1A0h            |

| General<br>Purpose                |                 | General<br>Purpose<br>Register |                 |                                                   |                 |                                |                 |

| Register                          |                 |                                | EFh             |                                                   | 16F             |                                | 1EFh            |

| -                                 |                 | Mapped in<br>Bank 0<br>70h-7Fh | F0h             | Mapped in<br>Bank 0<br>70h-7Fh                    | 170             | Mapped in<br>Bank 0<br>70h-7Fh | 1F0h            |

|                                   | 7Fh             |                                | FFh             |                                                   | 17F             |                                | 1FFh            |

| Bank 0                            |                 | Bank 1                         |                 | Bank 2                                            |                 | Bank 3                         |                 |

|                                   |                 | Note 1: Not a p                | hysical reg     | a memory locations<br>ister.<br>e not implemented |                 |                                |                 |

# TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address            | Name    | Bit 7         | Bit 6               | Bit 5                   | Bit 4          | Bit 3        | Bit 2            | Bit 1          | Bit 0    | Value on<br>Power-on<br>Reset | Value on all other resets |

|--------------------|---------|---------------|---------------------|-------------------------|----------------|--------------|------------------|----------------|----------|-------------------------------|---------------------------|

| Bank 1             | ·       | •             |                     |                         |                |              | ·                |                |          | •                             |                           |

| 80h                | INDF    | Addressing    | this location       | uses conten             | ts of FSR to   | address data | memory (no       | t a physical r | egister) | 0000 0000                     | 0000 0000                 |

| 81h                | OPTION  | RBPU          | INTEDG              | TOCS                    | T0SE           | PSA          | PS2              | PS1            | PS0      | 1111 1111                     | 1111 1111                 |

| 82h                | PCL     | Program Co    | ounter's (PC)       | Least Signif            | icant Byte     |              |                  |                |          | 0000 0000                     | 0000 0000                 |

| 83h                | STATUS  | IRP           | RP1                 | RP0                     | TO             | PD           | Z                | DC             | С        | 0001 1xxx                     | 000q quuu                 |

| 84h                | FSR     | Indirect data | a memory ad         | dress pointe            | r              |              |                  |                |          | XXXX XXXX                     | uuuu uuuu                 |

| 85h                | TRISA   | —             | _                   | PORTA Dat               | a Direction R  | egister      |                  |                |          | 11 1111                       | 11 1111                   |

| 86h                | TRISB   | PORTB Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 87h                | TRISC   | —             | _                   | PORTC Da                | ta Direction F | Register     |                  |                |          | 11 1111                       | 11 1111                   |

| 88h                | TRISD   | PORTD Dat     | a Direction F       | Register                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 89h                | TRISE   | PORTE Dat     | a Direction R       | legister                |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 8Ah                | PCLATH  | —             | _                   | —                       | Write Buffer   | for the uppe | er 5 bits of the | e PC           |          | 0 0000                        | 0 0000                    |

| 8Bh                | INTCON  | GIE           | PEIE                | T0IE                    | INTE           | RBIE         | T0IF             | INTF           | RBIF     | 0000 000x                     | 0000 000u                 |

| 8Ch                | PIE1    | LCDIE         | ADIE <sup>(2)</sup> | —                       | _              | SSPIE        | CCP1IE           | TMR2IE         | TMR1IE   | 00 0000                       | 00 0000                   |

| 8Dh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 8Eh                | PCON    | —             | _                   | —                       | _              | _            | _                | POR            | —        | 0-                            | u-                        |

| 8Fh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 90h                | —       | Unimpleme     | Inimplemented       |                         |                |              |                  |                |          | —                             | —                         |

| 91h                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 92h                | PR2     | Timer2 Peri   | od Register         |                         |                |              |                  |                |          | 1111 1111                     | 1111 1111                 |

| 93h                | SSPADD  | Synchronou    | is Serial Port      | (I <sup>2</sup> C mode) | Address Reg    | ister        |                  |                |          | 0000 0000                     | 0000 0000                 |

| 94h                | SSPSTAT | SMP           | CKE                 | D/Ā                     | Р              | S            | R/W              | UA             | BF       | 0000 0000                     | 0000 0000                 |

| 95h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 96h                | —       | Unimpleme     | Inimplemented —     |                         |                |              |                  |                | —        |                               |                           |

| 97h                | —       | Unimpleme     | Inimplemented       |                         |                |              |                  |                |          | _                             | —                         |

| 98h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 99h                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | —                         |

| 9Ah                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 9Bh                | —       | Unimpleme     | nted                |                         |                |              |                  |                |          | -                             | —                         |

| 9Ch                | —       | Unimpleme     | Inimplemented       |                         |                |              |                  |                | _        | —                             |                           |

| 9Dh                | _       | Unimpleme     | Unimplemented       |                         |                |              |                  |                |          | —                             | —                         |

| 9Eh                | _       | Unimpleme     | nted                |                         |                |              |                  |                |          | _                             | _                         |

| 9Fh <sup>(1)</sup> | ADCON1  |               | —                   | _                       |                | _            | PCFG2            | PCFG1          | PCFG0    | 000                           | 000                       |

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged,  ${\rm q}$  = value depends on condition, - = unimplemented read as '0',

Note

shaded locations are unimplemented, read as '0'. 1: Registers ADRES, ADCON0, and ADCON1 are not implemented in the PIC16C923, read as '0'.

These bits are reserved on the PIC16C923, always maintain these bits clear.

These pixels do not display, but can be used as general purpose RAM.

PIC16C923 reset values for PORTA: --xx xxxx for a POR, and --uu uuuu for all other resets, PIC16C924 reset values for PORTA: --0x 0000 when read.

Bit1 of ADCON0 is reserved on the PIC16C924, always maintain this bit clear.

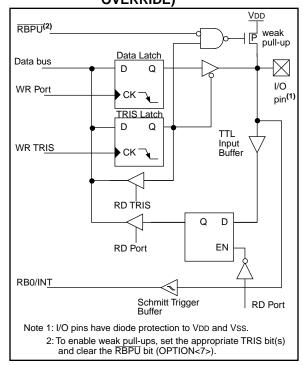

#### 5.3 PORTC and TRISC Register

PORTC is an 6-bit bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### **EXAMPLE 5-3: INITIALIZING PORTC**

| BCF<br>BCF | STATUS, RPO<br>STATUS, RP1 | ; | Select Bank0          |

|------------|----------------------------|---|-----------------------|

| CLRF       | PORTC                      | ; | Initialize PORTC      |

| BSF        | STATUS, RPO                | ; |                       |

| MOVLW      | 0xCF                       | ; | Value used to         |

|            |                            | ; | initialize data       |

|            |                            | ; | direction             |

| MOVWF      | TRISC                      | ; | Set RC<3:0> as inputs |

|            |                            | ; | RC<5:4> as outputs    |

|            |                            | ; | RC<7:6> always read 0 |

#### FIGURE 5-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

| Name            | Bit# | Buffer Type | Function                                                                                 |

|-----------------|------|-------------|------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input                  |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                         |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture input/Compare output/PWM output                         |

| RC3/SCK/SCL     | bit3 | ST          | Input/output port pin or the synchronous serial clock for both SPI and $\rm I^2C$ modes. |

| RC4/SDI/SDA     | bit4 | ST          | Input/output port pin or the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode). |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data out                                |

#### TABLE 5-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

#### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6 | Bit 5                                 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|-------|---------------------------------------|-------|-------|-------|---------|---------|-------------------------------|---------------------------|

| 07h     | PORTC | —     |       | RC5                                   | RC4   | RC3   | RC2   | RC1     | RC0     | xx xxxx                       | uu uuuu                   |

| 87h     | TRISC | —     | —     | PORTC Data Direction Control Register |       |       |       | 11 1111 | 11 1111 |                               |                           |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTC.

# PIC16C9XX

NOTES:

# 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u>

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read-from or write-to the Timer1 register pair (TMR1H:TMR1L) (Section 8.3.2).

In asynchronous counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements, as specified in timing parameters 45, 46, and 47.

#### 8.3.2 READING AND WRITING TMR1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

# EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ;Read high byte

MOVWF TMPH

;

MOVF

TMR1L, W ;Read low byte

MOVWE TMPL

;

MOVF

TMR1H, W ;Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

CONTINUE ;Good 16-bit read

GOTO

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

;

and low bytes now will read a good value.

;

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

TMR1L, W ;Read low byte

MOVE

MOVWF TMPL

;

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

# 8.4 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                               | Freq                                                | C1            | C2       |  |  |

|----------------------------------------|-----------------------------------------------------|---------------|----------|--|--|

| LP                                     | 32 kHz                                              | 33 pF         | 33 pF    |  |  |

|                                        | 100 kHz                                             | 15 pF         | 15 pF    |  |  |

|                                        | 200 kHz                                             | 15 pF         | 15 pF    |  |  |

| These va                               | alues are for o                                     | design guidan | ce only. |  |  |

| Crystals Tes                           | ted:                                                |               |          |  |  |

| 32.768 kHz                             | Epson C-00 <sup>-</sup>                             | 1R32.768K-A   | ± 20 PPM |  |  |

| 100 kHz                                | Epson C-2 100.00 KC-P ± 20 PF                       |               |          |  |  |

| 200 kHz                                | STD XTL 200.000 kHz ± 20 PPM                        |               |          |  |  |

| of o<br>time<br>2: Sind<br>cha<br>reso | of oscillator but also increases the start-up time. |               |          |  |  |

**Note:** The Timer2 postscaler (Section 9.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

#### EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 31.25 kHz, Fosc = 8 MHz TMR2 prescale = 1

| 1/31.25 kHz | = [ (PR2) + 1 ] • 4 • 1/8 MHz • 1 |

|-------------|-----------------------------------|

| 32 µs       | = [ (PR2) + 1 ] • 4 • 125 ns • 1  |

| PR2         | = 63                              |

Find the maximum resolution of the duty cycle that can be used with a 31.25 kHz frequency and 8 MHz oscillator:

| 1/31.25 kHz | $= 2^{\text{PWM RESOLUTION}} \bullet 1/8 \text{ MHz} \bullet 1$ |

|-------------|-----------------------------------------------------------------|

| 32 µs       | $=2^{\text{PWM RESOLUTION}} \bullet 125 \text{ ns} \bullet 1$   |

| 256         | $= 2^{\text{PWM RESOLUTION}}$                                   |

| log(256)    | = (PWM Resolution) • $log(2)$                                   |

| 8.0         | = PWM Resolution                                                |

At most, an 8-bit resolution duty cycle can be obtained from a 31.25 kHz frequency and a 8 MHz oscillator, i.e.,  $0 \le CCPR1L:CCP1CON<5:4> \le 255$ . Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-2 lists example PWM frequencies and resolutions for Fosc = 8 MHz. TMR2 prescaler and PR2 values are also shown.

#### 10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP module for PWM operation.

#### TABLE 10-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 8 MHz

| PWM Frequency              | 488 Hz | 1.95 kHz | 7.81 kHz | 31.25 kHz | 62.5 kHz | 250 kHz |

|----------------------------|--------|----------|----------|-----------|----------|---------|

| Timer Prescaler (1, 4, 16) | 16     | 4        | 1        | 1         | 1        | 1       |

| PR2 Value                  | 0xFF   | 0xFF     | 0xFF     | 0x3F      | 0x1F     | 0x07    |

| Maximum Resolution (bits)  | 10     | 10       | 10       | 8         | 7        | 5       |

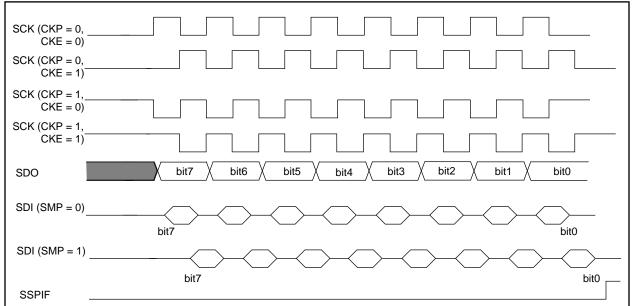

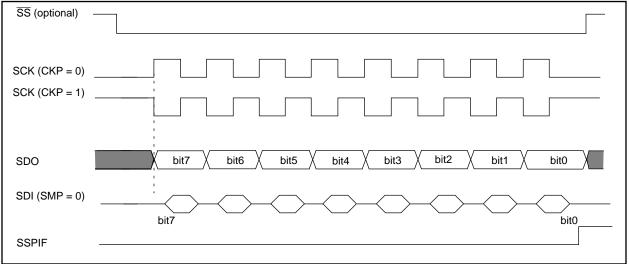

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

- Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- **Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

# FIGURE 11-5: SPI MODE TIMING, MASTER MODE

# FIGURE 11-6: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

# 11.2 $\underline{I^2}C^{\mathbb{T}}$ Overview

This section provides an overview of the Inter-Integrated Circuit ( $I^2C$ ) bus, with Section 11.3 discussing the operation of the SSP module in  $I^2C$  mode.

The  $l^2C$  bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. An enhanced specification, or fast mode is not supported. This device will communicate with fast mode devices if attached to the same bus.

The  $l^2C$  interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXXX software. Table 11-2 defines some of the  $l^2C$  bus terminology. For additional information on the  $l^2C$  interface specification, refer to the Philips document "*The*  $l^2C$  bus and how to use it."#939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the  $I^2C$  bus is limited only by the maximum bus loading specification of 400 pF.

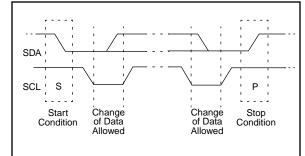

#### 11.2.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions. The master generates these conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

# FIGURE 11-8: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

# TABLE 11-2: I<sup>2</sup>C BUS TERMINOLOGY

# 12.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5 TAD per 8-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 12-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# 12.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog inputs will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

# TABLE 12-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock             | Source (TAD) | Device Frequency          |                           |                               |                             |  |  |  |

|-----------------------|--------------|---------------------------|---------------------------|-------------------------------|-----------------------------|--|--|--|

| Operation ADCS1:ADCS0 |              | 8 MHz                     | 5 MHz                     | 1.25 MHz                      | 333.33 kHz                  |  |  |  |

| 2Tosc                 | 00           | 250 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                        | 6 µs                        |  |  |  |

| 8Tosc                 | 01           | 1 μs                      | 1.6 μs                    | 6.4 μs                        | 24 μs <sup>(3)</sup>        |  |  |  |

| 32Tosc                | 10           | 4 μs                      | 6.4 μs                    | 25.6 μs <b><sup>(3)</sup></b> | 96 μs <b><sup>(3)</sup></b> |  |  |  |

| RC                    | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup>     | 2 - 6 μs <sup>(1)</sup>     |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When derived frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep mode only

5: For extended voltage devices (LC), please refer to the electrical specifications section.

# 13.3 Pixel Control

#### 13.3.1 LCDD (PIXEL DATA) REGISTERS

The pixel registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Table 13-4 shows the correlation of each bit in the LCDD registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

# FIGURE 13-10:GENERIC LCDD REGISTER LAYOUT

| R/W-x        | R/W-x                                 | R/W-x        | R/W-x        | R/W-x        | R/W-x        | R/W-x        | R/W-x        |                                                                |

|--------------|---------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------------------------------------------------|

| SEGs<br>COMc | SEGs<br>COMc                          | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | SEGs<br>COMc | R =Readable bit<br>W =Writable bit                             |

| bit7         |                                       |              |              |              |              |              | bit0         | U =Unimplemented bit,<br>Read as '0'<br>-n =Value at POR reset |

|              | SEGsCON<br>1 = Pixel o<br>0 = Pixel o | n (dark)     | ata Bit for  | segment s    | s and com    | mon c        |              |                                                                |

# 14.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 14.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

#### 14.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

# 14.4.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-8, Figure 14-9, and Figure 14-10 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 14-5 shows the reset conditions for some special function registers, while Table 14-6 shows the reset conditions for all the registers.

#### 14.4.5 POWER CONTROL/STATUS REGISTER (PCON)

Bit1 is Power-on Reset Status bit POR. It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configuration | Powe      | r-up             | Wake-up from SLEEP |

|--------------------------|-----------|------------------|--------------------|

|                          | PWRTE = 1 | PWRTE = 0        |                    |

| XT, HS, LP               | 1024Tosc  | 72 ms + 1024Tosc | 1024 Tosc          |

| RC                       |           | 72 ms            |                    |

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

# PIC16C9XX

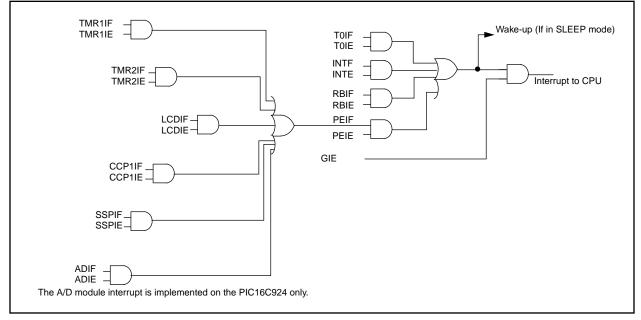

# FIGURE 14-14:INTERRUPT LOGIC

# FIGURE 14-15:INT PIN INTERRUPT TIMING

- 5: INTF can be set anytime during the Q4-Q1 cycles.

| SUBWF             | Subilaci                                                          | W from f                     |                                   |                      |

|-------------------|-------------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|

| Syntax:           | [ label ]                                                         | SUBWF                        | f,d                               |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ | 7                            |                                   |                      |

| Operation:        | (f) - (W) –                                                       | → (destina                   | ation)                            |                      |

| Status Affected:  | C, DC, Z                                                          |                              |                                   |                      |

| Encoding:         | 00                                                                | 0010                         | dfff                              | ffff                 |

| Description:      | Subtract (2<br>ister from r<br>stored in th<br>result is sto      | egister 'f'. I<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | e result is<br>the   |

| Words:            | 1                                                                 |                              |                                   |                      |

| Cycles:           | 1                                                                 |                              |                                   |                      |

| Q Cycle Activity: | Q1                                                                | Q2                           | Q3                                | Q4                   |

|                   | Decode                                                            | Read<br>register 'f'         | Process<br>data                   | Write to destinatior |

| Example 1:        | SUBWF                                                             | REG1,1                       | 1                                 |                      |

|                   | Before Ins                                                        | struction                    |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 3<br>2<br>?<br>?                  |                      |

|                   | After Instr                                                       | uction                       |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 1<br>2<br>1; result is<br>0       | positive             |

| Example 2:        | Before Ins                                                        | struction                    |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 2<br>2<br>?<br>?                  |                      |

|                   | After Instr                                                       | uction                       |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 0<br>2<br>1; result is<br>1       | zero                 |

| Example 3:        | Before Ins                                                        | struction                    |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 1<br>2<br>?<br>?                  |                      |

|                   | After Instr                                                       | uction                       |                                   |                      |

|                   | REG1<br>W<br>C<br>Z                                               | =<br>=<br>=                  | 0xFF<br>2<br>0; result is<br>0    | negative             |

| SWAPF                                                                                         | Swap Nibbles in f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                       | [label] SWAPF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:                                                                                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Operation:                                                                                    | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Status Affected:                                                                              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:                                                                                     | 00 1110 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:                                                                                  | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Q Cycle Activity:                                                                             | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                                                                               | Decode Read register 'f' Process Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Example                                                                                       | SWAPF REG, 0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                                               | REG1 = 0xA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| After Instruction                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                                                                                               | After Instruction<br>REG1 = 0xA5<br>W = 0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| TRIS                                                                                          | REG1 = 0xA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| TRIS<br>Syntax:                                                                               | REG1 = 0xA5<br>W = 0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| -                                                                                             | REG1 = 0xA5<br>W = 0x5A<br>Load TRIS Register                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Syntax:                                                                                       | REG1       =       0xA5         W       =       0x5A             Load TRIS Register         [/abel]       TRIS       f                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                          | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                            | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \textbf{Load TRIS Register} \\ \hline \\ \textbf{[label]} & TRIS & f\\ 5 \leq f \leq 7\\ \hline \\ (W) \rightarrow TRIS register f;\\ \hline \\ \textbf{None} \end{array}$                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \textbf{Load TRIS Register} \\ \hline \\ $                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \hline \\ \hline $                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$ $\begin{array}{rcl} \textbf{Load TRIS Register} \\ \hline \\ \textbf{[label]} & TRIS & f\\ 5 \leq f \leq 7\\ (W) \rightarrow TRIS register f;\\ \hline \\ \textbf{None} \\ \hline \hline \\ 00 & 0000 & 0110 & 0fff\\ \hline \\ \hline \\ \textbf{The instruction is supported for code compatibility with the PIC16C5X products. Since TRIS registers are readable and writable, the user can directly address them. \\ \hline 1 \end{array}$ |  |  |  |  |  |  |

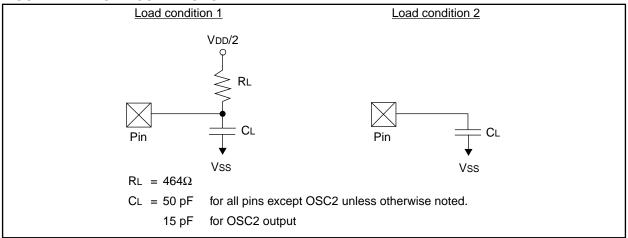

# FIGURE 17-2: LOAD CONDITIONS

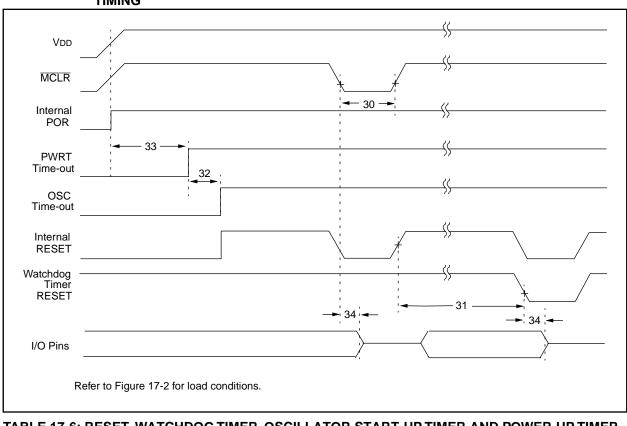

# FIGURE 17-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Мах | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | —        | —   | μs    |                          |