Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | LCD, POR, PWM, WDT                                                          |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 176 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-LCC (J-Lead)                                                             |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923t-04i-l |

**NOTES:**

# 6.0 OVERVIEW OF TIMER MODULES

Each module can generate an interrupt to indicate that an event has occurred (e.g. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

#### 6.1 Timer0 Overview

The Timer0 module is a simple 8-bit timer/counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 when prescaler assigned to Watchdog timer, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

#### 6.2 Timer1 Overview

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit capture or the 16-bit compare and must be synchronized to the device. Timer1 oscillator is also one of the clock sources for the LCD module.

#### 6.3 Timer2 Overview

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the clock source for the Syn-

chronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

#### 6.4 CCP Overview

The CCP module can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPR1H:CCPR1L register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCP1 pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPR1H:CCPR1L register pair. When a match occurs an interrupt can be generated, and the output pin CCP1 can be forced to given state (High or Low), TMR1 can be reset and start A/D conversion. This depends on the control bits CCP1M3:CCP1M0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPR1H:CCPR1L<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCP1 pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCP1 pin (if an output) will be forced high.

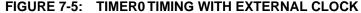

## 7.2 <u>Using Timer0 with an External Clock</u>

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### 8.3 <u>Timer1 Operation in Asynchronous</u> Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read-from or write-to the Timer1 register pair (TMR1H:TMR1L) (Section 8.3.2).

In asynchronous counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

## 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements, as specified in timing parameters 45, 46, and 47.

## 8.3.2 READING AND WRITING TMR1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

## EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ; Read high byte

MOVWF TMPH

TMR1L, W ; Read low byte

MOVE

MOVWE TMPL

MOVF

TMR1H, W ; Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS, Z ; Is result = 0

CONTINUE ; Good 16-bit read

GOTO

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

and low bytes now will read a good value.

MOVF

TMR1H, W ; Read high byte

MOVWF

TMPH

TMR1L, W ; Read low byte

MOVF

MOVWF TMPL

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

#### 8.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                   | Freq    | C1    | C2    |  |

|--------------------------------------------|---------|-------|-------|--|

| LP                                         | 32 kHz  | 33 pF | 33 pF |  |

|                                            | 100 kHz | 15 pF | 15 pF |  |

|                                            | 200 kHz | 15 pF | 15 pF |  |

| These values are for design guidance only. |         |       |       |  |

#### **Crystals Tested:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM |

|------------|-----------------------|----------|

| 100 kHz    | Epson C-2 100.00 KC-P | ± 20 PPM |

| 200 kHz    | STD XTL 200.000 kHz   | ± 20 PPM |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

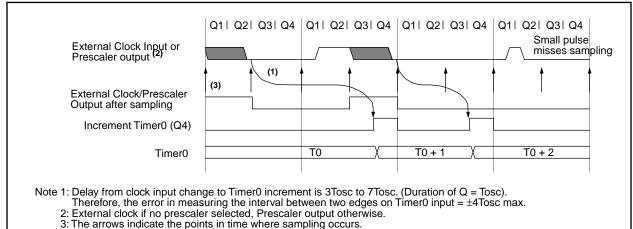

#### 11.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge  $(\overline{ACK})$  pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

### FIGURE 11-19: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

TABLE 14-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

| Register            | Applicab | le Devices | Power-on Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|----------|------------|----------------|--------------------------|------------------------------------|

| PORTD               | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| PORTE               | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| PCLATH              | 923      | 924        | 0 0000         | 0 0000                   | u uuuu                             |

| INTCON              | 923      | 924        | 0000 000x      | 0000 000u                | uuuu uuuu(1)                       |

| PIR1 <sup>(4)</sup> | 923      | 924        | 00 0000        | 00 0000                  | uu uuuu <b>(1)</b>                 |

| TMR1L               | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| TMR1H               | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| T1CON               | 923      | 924        | 00 0000        | uu uuuu                  | uu uuuu                            |

| TMR2                | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| T2CON               | 923      | 924        | -000 0000      | -000 0000                | -uuu uuuu                          |

| SSPBUF              | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| SSPCON              | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| CCPR1L              | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| CCPR1H              | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| CCP1CON             | 923      | 924        | 00 0000        | 00 0000                  | uu uuuu                            |

| ADRES               | 923      | 924        | xxxx xxxx      | uuuu uuuu                | uuuu uuuu                          |

| ADCON0              | 923      | 924        | 0000 00-0      | 0000 00-0                | uuuu uu-u                          |

| OPTION              | 923      | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| TRISA               | 923      | 924        | 11 1111        | 11 1111                  | uu uuuu                            |

| TRISB               | 923      | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| TRISC               | 923      | 924        | 11 1111        | 11 1111                  | uu uuuu                            |

| TRISD               | 923      | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| TRISE               | 923      | 924        | 1111 1111      | 1111 1111                | uuuu uuuu                          |

| PIE1 <sup>(4)</sup> | 923      | 924        | 00 0000        | 00 0000                  | uu uuuu                            |

| PCON                | 923      | 924        | 0-             | u-                       | u-                                 |

| PR2                 | 923      | 924        | 1111 1111      | 1111 1111                | 1111 1111                          |

| SSPADD              | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| SSPSTAT             | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| ADCON1              | 923      | 924        | 000            | 000                      | uuu                                |

| PORTF               | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

| PORTG               | 923      | 924        | 0000 0000      | 0000 0000                | uuuu uuuu                          |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector

<sup>3:</sup> See Table 14-5 for reset value for specific condition.

<sup>4:</sup> Bits PIE1<6> and PIR1<6> are reserved on the PIC16C923, always maintain these bits clear.

<sup>5:</sup> PORTA values when read.

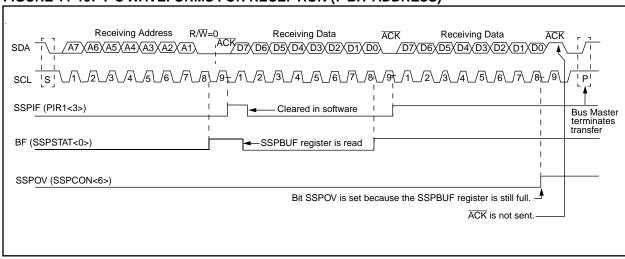

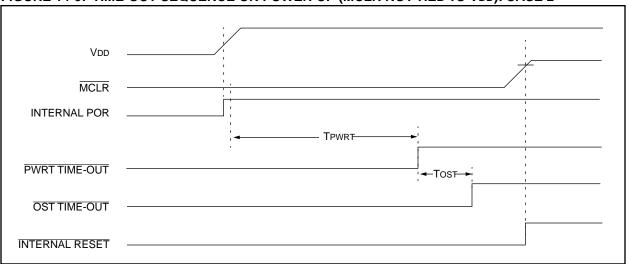

FIGURE 14-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

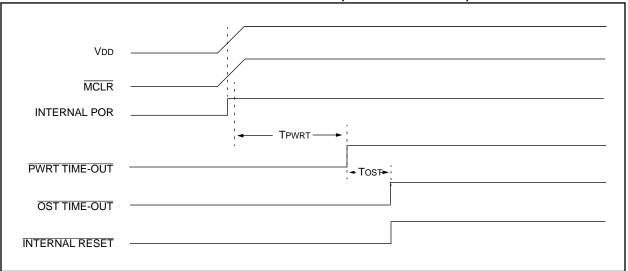

FIGURE 14-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 14-10:TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

## 15.1 <u>Instruction Descriptions</u>

| ADDLW             | Add Lite           | ral and \           | N               |               | ADDWF             | Add W a                               | nd f                    |                      |                      |

|-------------------|--------------------|---------------------|-----------------|---------------|-------------------|---------------------------------------|-------------------------|----------------------|----------------------|

| Syntax:           | [ <i>label</i> ] A | DDLW                | k               |               | Syntax:           | [label] A                             | DDWF                    | f,d                  |                      |

| Operands:         | $0 \le k \le 2$    | 55                  |                 |               | Operands:         | $0 \le f \le 12$                      | 27                      |                      |                      |

| Operation:        | $(W) + k \to (W)$  |                     |                 |               |                   | d ∈ [0,1]                             |                         |                      |                      |

| Status Affected:  | C, DC, Z           |                     |                 |               | Operation:        | $(W) + (f) \rightarrow (destination)$ |                         |                      |                      |

| Encoding:         | 11                 | 111x                | kkkk            | kkkk          | Status Affected:  | C, DC, Z                              |                         |                      |                      |

| Description:      | The conte          | nts of the          | W registe       | r are         | Encoding:         | 00                                    | 0111                    | dfff                 | ffff                 |

| Decomption.       | added to t         | he eight b          | it literal 'k'  | and the       | Description:      | Add the coregister 'f'.               | . If 'd' is 0           | the result           | is stored            |

| Words:            | 1                  |                     |                 |               |                   | in the W re<br>stored bac             | Ū                       |                      | result is            |

| Cycles:           | 1                  |                     |                 |               | Words:            | 1                                     |                         |                      |                      |

| Q Cycle Activity: | Q1                 | Q2                  | Q3              | Q4            | Cycles:           | 1                                     |                         |                      |                      |

|                   | Decode             | Read<br>literal 'k' | Process<br>data | Write to<br>W | Q Cycle Activity: | Q1                                    | Q2                      | Q3                   | Q4                   |

| Example:          | ADDLW              | 0x15                |                 |               |                   | Decode                                | Read<br>register<br>'f' | Process<br>data      | Write to destination |

|                   | Before In          | W =                 | 0x10            |               | Example           | ADDWF                                 | FSR,                    | 0                    |                      |

|                   | After Inst         | W =                 | 0x25            |               |                   | After Inst                            | W =<br>FSR =            | 0x17<br>0xC2<br>0xD9 |                      |

|                   |                    |                     |                 |               |                   |                                       | FSR =                   | 0xC2                 |                      |

| BTFSS                       | Bit Test f, Skip if Set                                                                                                                                                                            |                                       |                   |                  |  | CALL              | Call Sub                              | routine                        |                                                 |                                |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|------------------|--|-------------------|---------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|

| Syntax:                     | [ <i>label</i> ] BT                                                                                                                                                                                | FSS f,b                               |                   |                  |  | Syntax:           | [ label ]                             | CALL F                         | (                                               |                                |

| Operands:                   | 0 ≤ f ≤ 12                                                                                                                                                                                         | 7                                     |                   |                  |  | Operands:         | $0 \le k \le 2047$                    |                                |                                                 |                                |

| Operation: Status Affected: |                                                                                                                                                                                                    | $0 \le b < 7$ skip if $(f < b >) = 1$ |                   |                  |  | Operation:        | $(PC)+ 1-k \rightarrow PC<$ $(PCLATE$ | <10:0>,                        | → PC<12                                         | :11>                           |

|                             | 01                                                                                                                                                                                                 | 11bb                                  | bfff              | ffff             |  | Status Affected:  | None                                  |                                |                                                 |                                |

| Encoding:                   |                                                                                                                                                                                                    |                                       |                   |                  |  | Encoding:         | 10                                    | 0kkk                           | kkkk                                            | kkkk                           |

| Description:                | If bit 'b' in register 'f' is '0' then the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2Tcy instruction. |                                       |                   |                  |  | Description:      | (PC+1) is<br>eleven bit<br>into PC bi | pushed or immediate ts <10:0>. | t, return action the stace address in the upper | ck. The<br>s loaded<br>bits of |

| Words:                      | 1                                                                                                                                                                                                  |                                       |                   |                  |  |                   |                                       | e loaded fi<br>ycle instru     | rom PČLAT<br>ction.                             | TH. CALL                       |

| Cycles:                     | 1(2)                                                                                                                                                                                               |                                       |                   |                  |  | Words:            | 1                                     |                                |                                                 |                                |

| Q Cycle Activity:           | Q1                                                                                                                                                                                                 | Q2                                    | Q3                | Q4               |  | Cycles:           | 2                                     |                                |                                                 |                                |

|                             | Decode                                                                                                                                                                                             | Read<br>register 'f'                  | Process<br>data   | No-<br>Operation |  | Q Cycle Activity: | Q1                                    | Q2                             | Q3                                              | Q4                             |

| If Skip:                    | (2nd Cyc                                                                                                                                                                                           | le)                                   |                   |                  |  | 1st Cycle         | Decode                                | Read<br>literal 'k',           | Process<br>data                                 | Write to<br>PC                 |

|                             | Q1                                                                                                                                                                                                 | Q2                                    | Q3                | Q4               |  |                   |                                       | Push PC<br>to Stack            |                                                 |                                |

|                             | No-<br>Operation                                                                                                                                                                                   | No-<br>Operation                      | No-<br>Operation  | No-<br>Operation |  | 2nd Cycle         | No-<br>Operation                      | No-<br>Operation               | No-<br>Operation                                | No-<br>Operation               |

| Example                     | HERE<br>FALSE<br>TRUE                                                                                                                                                                              | BTFSC<br>GOTO<br>•                    | FLAG,1<br>PROCESS | _CODE            |  | Example           | HERE Before In                        | truction                       | Nddress HE                                      |                                |

|                             | After Instr<br>i<br>I                                                                                                                                                                              | PC = a<br>ruction<br>if FLAG<1>       | address F.        |                  |  |                   |                                       | _                              | Address TH<br>Address HE                        |                                |

PC =

address TRUE

Write to

Operation

| DECFSZ                 | Decrement f, Skip if 0                                                                                                                                                           | GOTO              | Unconditional Branch                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                | [ label ] DECFSZ f,d                                                                                                                                                             | Syntax:           | [label] GOTO k                                                                                                                                                                    |

| Operands:              | $0 \le f \le 127$                                                                                                                                                                | Operands:         | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:             | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (destination);                                                                                                                            | Operation:        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |

|                        | skip if result = 0                                                                                                                                                               | Status Affected:  | None                                                                                                                                                                              |

| Status Affected:       | None                                                                                                                                                                             | Encoding:         | 10 1kkk kkkk kkkk                                                                                                                                                                 |

| Encoding: Description: | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.                         | Description:      | GOTO is an unconditional branch. The eleven bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two cycle instruction. |

|                        | If the result is 1, the next instruction, is executed. If the result is 0, then a NOP is                                                                                         | Words:            | 1                                                                                                                                                                                 |

|                        | executed instead making it a 2Tcy instruction.                                                                                                                                   | Cycles:           | 2                                                                                                                                                                                 |

| Words:                 | 1                                                                                                                                                                                | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                       |

| Cycles:                | 1(2)                                                                                                                                                                             | 1st Cycle         | Decode Read Process Write to literal 'k' data PC                                                                                                                                  |

| Q Cycle Activity:      | Q1 Q2 Q3 Q4                                                                                                                                                                      | 2nd Cycle         | No-<br>Operation Operation Operation Operation                                                                                                                                    |

|                        | Decode Read Process Write to register 'f' data destination                                                                                                                       |                   | Operation Operation Operation                                                                                                                                                     |

| If Skip:               | (2nd Cycle)                                                                                                                                                                      | Example           | GOTO THERE                                                                                                                                                                        |

|                        | Q1 Q2 Q3 Q4                                                                                                                                                                      |                   | After Instruction                                                                                                                                                                 |

|                        | No-<br>Operation                                                                                                                                                                 |                   | PC = Address THERE                                                                                                                                                                |

| Example                | HERE DECFSZ CNT, 1 GOTO LOOP  CONTINUE   Before Instruction PC = address HERE  After Instruction CNT = CNT - 1 if CNT = 0, PC = address CONTINUE if CNT ≠ 0, PC = address HERE+1 |                   |                                                                                                                                                                                   |

| RLF               | Rotate Left f th                                                                                             | rough Ca                                    | rry                  | RRF               | Rotate F                                              | Right f th                                   | rough C                                                                  | arry                               |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|-------------------|-------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------|------------------------------------|

| Syntax:           | [ label ] RLF                                                                                                | f,d                                         |                      | Syntax:           | [ label ]                                             | RRF f                                        | ,d                                                                       |                                    |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in  [0,1] \end{array}$                                             |                                             |                      | Operands:         | $0 \le f \le 12$ $d \in [0,1]$                        |                                              |                                                                          |                                    |

| Operation:        | See description                                                                                              | below                                       |                      | Operation:        | See description below                                 |                                              |                                                                          |                                    |

| Status Affected:  | С                                                                                                            |                                             |                      | Status Affected:  | С                                                     |                                              |                                                                          |                                    |

| Encoding:         | 00 1101                                                                                                      | dfff                                        | ffff                 | Encoding:         | 00                                                    | 1100                                         | dfff                                                                     | ffff                               |

| Description:      | The contents of re one bit to the left the Flag. If 'd' is 0 the W register. If 'd' is back in register 'f'. | hrough the<br>result is pla<br>1 the result | Carry<br>ced in the  | Description:      | one bit to<br>Flag. If 'd'<br>W registe<br>back in re | the right t<br>is 0 the re<br>r. If 'd' is 1 | ister 'f' are<br>hrough the<br>esult is plad<br>the result<br>Register f | e Carry<br>ced in the<br>is placed |

| Words:            | 1                                                                                                            |                                             |                      | Words:            | 1                                                     |                                              |                                                                          |                                    |

| Cycles:           | 1                                                                                                            |                                             |                      | Cycles:           | 1                                                     |                                              |                                                                          |                                    |

| Q Cycle Activity: | Q1 Q2                                                                                                        | Q3                                          | Q4                   | Q Cycle Activity: | Q1                                                    | Q2                                           | Q3                                                                       | Q4                                 |

|                   | Decode Read registe                                                                                          | Process<br>data                             | Write to destination |                   | Decode                                                | Read<br>register<br>'f'                      | Process<br>data                                                          | Write to destination               |

| Example           | RLF R                                                                                                        | EG1,0                                       |                      | Example           | RRF                                                   |                                              | REG1,0                                                                   |                                    |

|                   | Before Instruction<br>REG1<br>C<br>After Instruction                                                         | = 111<br>= 0                                | 0 0110               |                   | Before Ir                                             | REG1<br>C                                    |                                                                          | 0 0110                             |

|                   | REG1<br>W<br>C                                                                                               |                                             | 0 0110<br>0 1100     |                   |                                                       | REG1<br>W<br>C                               |                                                                          | 0 0110<br>1 0011                   |

| XORLW                       | Exclusive OR Literal with W                                                     | XORWF                         | Exclusive OR W with f                                                                                                                                                     |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                     | [ <i>label</i> ] XORLW k                                                        | Syntax:                       | [ <i>label</i> ] XORWF f,d                                                                                                                                                |  |  |  |

| Operands:                   | 0 ≤ k ≤ 255                                                                     | Operands:                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        |  |  |  |

| Operation: Status Affected: | (W) .XOR. $k \rightarrow (W)$                                                   | Operation:                    | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |  |

| Encoding: Description:      | 11 1010 kkkk kkkk  The contents of the W register are                           | Status Affected:<br>Encoding: | Z 00 0110 dfff ffff                                                                                                                                                       |  |  |  |

| ·                           | XOR'ed with the eight bit literal 'k'.  The result is placed in the W register. | Description:                  | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |  |  |  |

| Words:                      | 1                                                                               | Words:                        | 1                                                                                                                                                                         |  |  |  |

| Cycles:                     | 1                                                                               | Cycles:                       | 1                                                                                                                                                                         |  |  |  |

| Q Cycle Activity:           | Q1 Q2 Q3 Q4                                                                     | •                             |                                                                                                                                                                           |  |  |  |

|                             | Decode Read Process Write to data W                                             | Q Cycle Activity:             | Q1 Q2 Q3 Q4    Decode   Read   Process   Write to   destination                                                                                                           |  |  |  |

| Example:                    | XORLW 0xAF                                                                      |                               |                                                                                                                                                                           |  |  |  |

|                             | Before Instruction                                                              | Example                       | XORWF REG 1                                                                                                                                                               |  |  |  |

|                             | W = 0xB5                                                                        |                               | Before Instruction                                                                                                                                                        |  |  |  |

|                             | After Instruction $W = 0x1A$                                                    |                               | $ \begin{array}{rcl} REG & = & 0xAF \\ W & = & 0xB5 \end{array} $                                                                                                         |  |  |  |

|                             | W - WIA                                                                         |                               | After Instruction                                                                                                                                                         |  |  |  |

|                             |                                                                                 |                               | $ REG = 0x1A \\ W = 0xB5 $                                                                                                                                                |  |  |  |

## 16.0 DEVELOPMENT SUPPORT

#### 16.1 Development Tools

The PICmicro<sup>™</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE® II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB™ SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy Logic Development System (fuzzyTECH<sup>®</sup>–MP)

### 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> MPLAB IDE

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB™ Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

### 16.3 <u>ICEPIC: Low-Cost PIC16CXXX</u> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT $^{\oplus}$  through Pentium $^{\top M}$  based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

### 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

### 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

TABLE 18-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average    |        |

|--------|------|------------|--------|

| Cext   | Kext | Fosc @ 5V, | 25°C   |

| 22 pF  | 5k   | 4.12 MHz   | ± 1.4% |

|        | 10k  | 2.35 MHz   | ± 1.4% |

|        | 100k | 268 kHz    | ± 1.1% |

| 100 pF | 3.3k | 1.80 MHz   | ± 1.0% |

|        | 5k   | 1.27 MHz   | ± 1.0% |

|        | 10k  | 688 kHz    | ± 1.2% |

|        | 100k | 77.2 kHz   | ± 1.0% |

| 300 pF | 3.3k | 707 kHz    | ± 1.4% |

|        | 5k   | 501 kHz    | ± 1.2% |

|        | 10k  | 269 kHz    | ± 1.6% |

|        | 100k | 28.3 kHz   | ± 1.1% |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

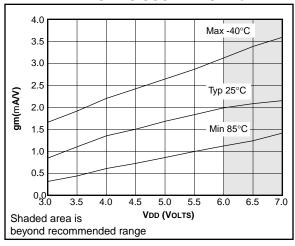

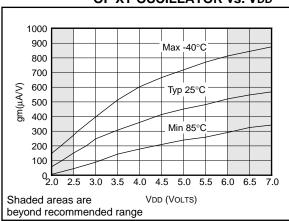

FIGURE 18-20:TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

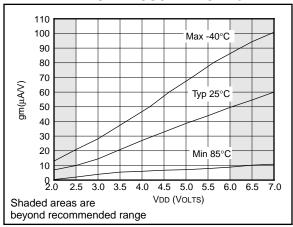

FIGURE 18-21:TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

FIGURE 18-22:TRANSCONDUCTANCE(gm)

OF XT OSCILLATOR vs. VDD

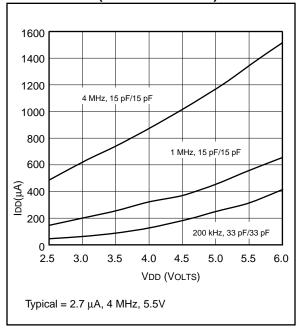

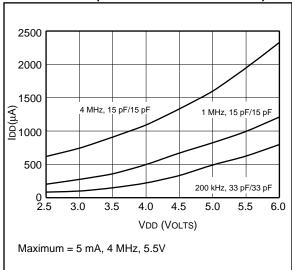

FIGURE 18-28:TYPICAL IDD vs. VDD (XT MODE @ 25°C)

FIGURE 18-29:MAXIMUM IDD vs. VDD (XT MODE -40°C TO +85°C)

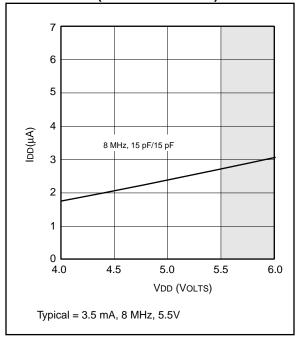

FIGURE 18-30:TYPICAL IDD vs. VDD (HS MODE @ 25°C)

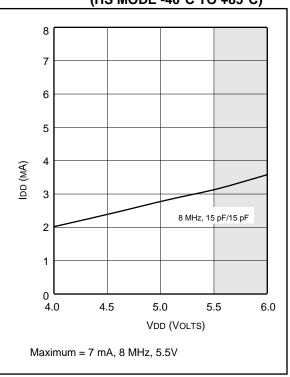

FIGURE 18-31:MAXIMUM IDD vs. VDD (HS MODE -40°C TO +85°C)

### 19.4 Package Marking Information

#### 68-Lead CERQUAD Windowed

### 64-Lead TQFP

#### 68-Lead PLCC

## 64-Lead SDIP (Shrink DIP)

## Example

#### Example

#### Example

### Example

| Legend: | MMM<br>XXX<br>AA<br>BB<br>C                                                                                                                                                                            | Microchip part number information Customer specific information* Year code (last 2 digits of calender year) Week code (week of January 1 is week '01') Facility code of the plant at which wafer is manufactured. |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | Ü                                                                                                                                                                                                      | C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.                                                                                                                                                       |  |

|         | $D_1$                                                                                                                                                                                                  | Mask revision number for microcontroller                                                                                                                                                                          |  |

|         | E                                                                                                                                                                                                      | Assembly code of the plant or country of origin in which part was assembled.                                                                                                                                      |  |

| Note:   | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information. |                                                                                                                                                                                                                   |  |

<sup>\*</sup> Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

#### INDEX PORTG......40 PWM......59 Α RA3:RA0 and RA5 Port Pins ......31 A/D RA4/T0CKI Pin ......31 Accuracy/Error ......86 RB3:RB0 Port Pins .......33 ADCON0......79, 80 RB7:RB4 Port Pins......33 ADCON1......79, 80 RC Oscillator ...... 105 ADIF......80 SSP (I<sup>2</sup>C Mode)......73 Analog-to-Digital Converter......79 SSP (SPI Mode) ......65 Configuring Analog Port......83 Timer0 ......45 Connection Considerations......87 Timer0/WDT Prescaler ......48 Conversion time .......85 Timer1 ......52 Conversions .......84 Timer2 ......55 Watchdog Timer ...... 116 Faster Conversion - Lower Resolution Tradeoff ........ 85 Internal Sampling Switch (Rss) Impedance......82 Operation During Sleep ......86 C bit ......23 Sampling Requirements......82 Capture/Compare/PWM (CCP) Sampling Time ......82 Capture Mode......58 Source Impedance......82 CCP1 ......57 Transfer Function......87 CCP1CON ...... 109 A/D Conversion Clock......83 CCPR1H......109 Registers CCPR1L ...... 109 Compare Mode......58 Absolute Maximum Ratings ......141 Compare Mode Block Diagram ......58 ACK......70, 74, 75, 76, 77 Prescaler ......58 PWM Block Diagram .....59 ADCON1 Register......20 PWM Mode......59 ADIE bit......26 PWM, Example Frequencies/Resolutions ......60 ADIF bit ......27 Section......57 Carry bit ......9 ALU ......9 CCP1CON Register.....19 Application Notes CCP1IE bit .......26 CCP1IF bit ......27 AN552......33 CCPR1H Register ......19 CCPR1L Register ......19 AN578......63 Clocking Scheme......15 AN594......57 Code Examples AN607......107 Call of a Subroutine in Page 1 from Page 0 ......30 Architecture Changing Between Capture Prescalers ......58 Harvard ......9 Changing Prescaler (Timer0 to WDT) ......49 Overview .......9 Changing Prescaler (WDT to Timer0) ......49 von Neumann......9 Doing an A/D Conversion .....84 Assembler I/O Programming ......41 MPASM Assembler......138 I<sup>2</sup>C Module Operation......78 Indirect Addressing......30 В Initializing PORTA ......31 BF ......74 Initializing PORTB ......33 Block Diagrams Initializing PORTC ......35 A/D......81 Initializing PORTD ......36 Capture Mode ...... 58 Initializing PORTE ......38 Compare Mode ...... 58 Initializing PORTF......39 External Brown-out1 ......112 Initializing PORTG ......40 External Brown-out2 ......112 Loading the SSPBUF register ......65 External Parallel Cystal Oscillator......105 Reading a 16-bit Free-running Timer ......53 External Power-on Reset ......112 Computed GOTO ......29 Interrupt Logic ......114 Configuration Bits ...... 103 LCD Module ...... 90 PIC16C923 ...... 10 DC bit 23 PIC16C924 ......11 PORTC ......35 PORTE......38 Digit Carry bit.....9

| Direct Addressing30                               | NOP13 <sup>2</sup>                                    |

|---------------------------------------------------|-------------------------------------------------------|

| E                                                 | OPTION13 <sup>4</sup>                                 |

| Electrical Characteristics                        | RETFIE13 <sup>r</sup>                                 |

| External Power-on Reset Circuit                   | RETLW 132                                             |

| F                                                 | RETURN 132                                            |

|                                                   | RLF                                                   |

| Family of Devices                                 | RRF                                                   |

| PIC16C9XX6                                        | SLEEP                                                 |

| FSR                                               | SUBLW                                                 |

| FSR Register                                      | SUBWF                                                 |

| Fuzzy Logic Dev. System (fuzzyTECH®-MP)139        | SWAPF                                                 |

| G                                                 | TRIS                                                  |

| GIE113                                            | XORLW                                                 |

| 1                                                 | Section                                               |

| I/O Ports                                         | INT Interrupt                                         |

| Section31                                         | INTCON                                                |

| I/O Programming Considerations41                  | INTCON Register                                       |

| l <sup>2</sup> C                                  | INTEDG                                                |

| Addressing I <sup>2</sup> C Devices70             | INTEDG bit                                            |

| Arbitration                                       | Inter-Integrated Circuit (I <sup>2</sup> C)           |

| BF74, 75                                          | Internal Sampling Switch (Rss) Impedance              |

| CKP                                               | Interrupt Flag                                        |

| Clock Synchronization72                           | Interrupts                                            |

| Combined Format71                                 | RB7:RB4 Port Change                                   |

| I <sup>2</sup> C Overview69                       | IRP bit                                               |

| Initiating and Terminating Data Transfer69        | K                                                     |

| Master-Receiver Sequence71                        |                                                       |

| Master-Transmitter Sequence71                     | KeeLoq® Evaluation and Programming Tools              |

| Multi-master72                                    | L                                                     |

| START69                                           | Loading of PC                                         |

| STOP69, 70                                        | M                                                     |

| Transfer Acknowledge70                            | MCLR106, 108                                          |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator 137 | Memory                                                |

| IDLE_MODE78                                       | Data Memory                                           |

| In-Circuit Serial Programming                     | Maps, PIC16C9XX 17                                    |

| INDF                                              | Program Memory17                                      |

| INDF Register                                     | MP-DriveWay™ - Application Code Generator 139         |

| Indirect Addressing                               | MPLAB C                                               |

| Instruction Cycle                                 | MPLAB Integrated Development Environment Software 138 |

| Instruction Format                                | 0                                                     |

| Instruction Set                                   | One-Time-Programmable Devices                         |

| ADDLW 121                                         | OPCODE119                                             |

| ADDWF 121                                         | OPTION                                                |

| ANDLW122                                          | OPTION Register                                       |

| ANDWF122                                          | Orthogonal                                            |

| BCF122                                            | OSC selection                                         |

| BSF123                                            | Oscillator                                            |

| BTFSC123                                          | HS104, 107                                            |

| BTFSS124                                          | LP 104, 107                                           |

| CALL124                                           | Oscillator Configurations104                          |

| CLRF125                                           | Output of TMR2 55                                     |

| CLRW 125                                          | P                                                     |

| CLRWDT126                                         | Paging, Program Memory29                              |

| COMF126                                           | PC                                                    |

| DECF                                              | PCL Register                                          |

| DECFSZ                                            | PCLATH                                                |

| GOTO                                              | PCLATH Register 19, 20, 21, 22, 29                    |

| INCF                                              | PCON109                                               |

| INCFSZ                                            | PCON Register                                         |

| IORLW129<br>IORWF129                              | PD106, 108                                            |

| MOVF                                              | PD bit                                                |

| MOVLW                                             | PICDEM-1 Low-Cost PICmicro Demo Board 138             |

| MOVWF                                             | PICDEM-2 Low-Cost PIC16CXX Demo Board 138             |

|                                                   | PICDEM-3 Low-Cost PIC16CXXX Demo Board 138            |

| List of Ed                 | uations And Examples                          | Figure 8-1:                  | T1CON: Timer1 Control Register (Address                |

|----------------------------|-----------------------------------------------|------------------------------|--------------------------------------------------------|

| Evample 3-1:               | Instruction Pipeline Flow15                   | Figure 8-2:                  | 10h)51 Timer1 Block Diagram52                          |

| •                          | Call of a Subroutine in Page 1 from Page 030  | Figure 9-1:                  | Timer2 Block Diagram55                                 |

|                            | Indirect Addressing30                         | Figure 9-2:                  | T2CON: Timer2 Control Register (Address                |

|                            | Initializing PORTA31                          | g                            | 12h)55                                                 |

| Example 5-2:               | Initializing PORTB33                          | Figure 10-1:                 | CCP1CON Register (Address 17h)57                       |

|                            | Initializing PORTC35                          | Figure 10-2:                 | Capture Mode Operation Block Diagram58                 |

|                            | Initializing PORTD36                          | Figure 10-3:                 | Compare Mode Operation Block Diagram58                 |

|                            | Initializing PORTE38                          | Figure 10-4:                 | Simplified PWM Block Diagram59                         |

|                            | Initializing PORTF39                          | Figure 10-5:                 | PWM Output59                                           |

|                            | Initializing PORTG40                          | Figure 11-1:                 | SSPSTAT: Sync Serial Port Status Register              |

| Example 5-8:               | Read-Modify-Write Instructions on an          |                              | (Address 94h)63                                        |

|                            | I/O Port41                                    | Figure 11-2:                 | SSPCON: Sync Serial Port Control Register              |

| •                          | Changing Prescaler (Timer0→WDT)49             |                              | (Address 14h)64                                        |

|                            | Changing Prescaler (WDT→Timer0)49             | Figure 11-3:                 | SSP Block Diagram (SPI Mode)65                         |

|                            | Reading a 16-bit Free-Running Timer 53        | Figure 11-4:                 | SPI Master/Slave Connection                            |

| •                          | Changing Between Capture Prescalers 58        | Figure 11-5:                 | SPI Mode Timing, Master Mode67                         |

|                            | PWM Period and Duty Cycle Calculation 60      | Figure 11-6:                 | SPI Mode Timing                                        |

|                            | Loading the SSPBUF (SSPSR) Register 65        | Figure 11-7:                 | (Slave Mode With CKE = 0)67<br>SPI Mode Timing         |

| •                          | A/D Minimum Charging Time                     | rigule 11-7.                 | (Slave Mode With CKE = 1)68                            |

| Example 12-1:              | Calculating the Minimum Required              | Figure 11-8:                 | Start and Stop Conditions69                            |

| Evample 12.2:              | Sample Time                                   | Figure 11-9:                 | 7-bit Address Format70                                 |

|                            | 4-bit vs. 8-bit Conversion Times85            |                              | I <sup>2</sup> C 10-bit Address Format70               |

|                            | Static MUX with 32 Segments                   |                              | Slave-receiver Acknowledge70                           |

|                            | 1/3 MUX with 13 Segments                      |                              | Data Transfer Wait State70                             |

|                            | Saving STATUS, W, and PCLATH                  |                              | Master-transmitter Sequence71                          |

| Example 11 1.              | Registers in RAM115                           |                              | Master-receiver Sequence71                             |

|                            |                                               |                              | Combined Format71                                      |

| List of Fig                | gures                                         | -                            | Multi-master Arbitration                               |

|                            | <b>9</b> ··· · · ·                            |                              | (Two Masters)72                                        |

| Figure 3-1:                | PIC16C923 Block Diagram10                     | Figure 11-17:                | Clock Synchronization72                                |

| Figure 3-2:                | PIC16C924 Block Diagram11                     | Figure 11-18:                | SSP Block Diagram                                      |

| Figure 3-3:                | Clock/Instruction Cycle15                     |                              | (I <sup>2</sup> C Mode)73                              |

| Figure 4-1:                | Program Memory Map and Stack17                | Figure 11-19:                | I <sup>2</sup> C Waveforms for Reception               |

| Figure 4-2:                | Register File Map18                           |                              | (7-bit Address)75                                      |

| Figure 4-3:                | Status Register (Address 03h, 83h, 103h,      | Figure 11-20:                | I <sup>2</sup> C Waveforms for Transmission            |

| E'                         | 183h)                                         | E' 44 04                     | (7-bit Address)                                        |

| Figure 4-4:                | OPTION Register (Address 81h, 181h) 24        | Figure 11-21:                | Operation of the I <sup>2</sup> C Module in IDLE_MODE, |

| Figure 4-5:                | INTCON Register (Address 0Bh, 8Bh,            | Figure 40.4.                 | RCV_MODE or XMIT_MODE78                                |

| Ciaura 4 Ci                | 10Bh, 18Bh)                                   | Figure 12-1:                 | ADCON1 Register (Address 1Fh)                          |

| Figure 4-6:<br>Figure 4-7: | PIR1 Register (Address 0Ch)                   | Figure 12-2:<br>Figure 12-3: | ADCON1 Register (Address 9Fh)80 A/D Block Diagram81    |

| Figure 4-7:                | PCON Register (Address 8Eh)                   | Figure 12-3:                 | Analog Input Model82                                   |

| Figure 4-9:                | Loading of PC In Different Situations29       | Figure 12-5:                 | A/D Transfer Function87                                |

| Figure 4-10:               | Direct/Indirect Addressing30                  | Figure 12-6:                 | Flowchart of A/D Operation88                           |

| Figure 5-1:                | Block Diagram of pins RA3:RA0 and RA5 31      | Figure 13-1:                 | LCDCON Register (Address 10Fh)89                       |

| Figure 5-2:                | Block Diagram of RA4/T0CKI Pin31              | Figure 13-2:                 | LCD Module Block Diagram90                             |

| Figure 5-3:                | Block Diagram of RB3:RB0 Pins33               | Figure 13-3:                 | LCDPS Register (Address 10Eh)90                        |

| Figure 5-4:                | Block Diagram of RB7:RB4 Pins33               | Figure 13-4:                 | Waveforms in Static Drive91                            |

| Figure 5-5:                | PORTC Block Diagram (Peripheral Output        | Figure 13-5:                 | Waveforms in 1/2 MUX, 1/3 Bias Drive92                 |

| J                          | Override)35                                   | Figure 13-6:                 | Waveforms in 1/3 MUX, 1/3 Bias93                       |

| Figure 5-6:                | PORTD<4:0> Block Diagram36                    | Figure 13-7:                 | Waveforms in 1/4 MUX, 1/3 Bias94                       |

| Figure 5-7:                | PORTD<7:5> Block Diagram37                    | Figure 13-8:                 | LCD Clock Generation95                                 |

| Figure 5-8:                | PORTE Block Diagram                           | Figure 13-9:                 | Example Waveforms in 1/4 MUX Drive97                   |

| Figure 5-9:                | PORTF Block Diagram39                         | Figure 13-10:                | Generic LCDD Register Layout98                         |

| Figure 5-10:               | PORTG Block Diagram40                         | Figure 13-11:                | Sleep Entry/exit When SLPEN = 1 or                     |

| Figure 5-11:               | Successive I/O Operation41                    |                              | CS1:CS0 = 0099                                         |

| Figure 7-1:                | Timer0 Block Diagram45                        | Figure 13-12:                | LCDSE Register (Address 10Dh) 100                      |

| Figure 7-2:                | Timer0 Timing: Internal Clock/No Prescale 45  | Figure 13-13:                | Charge Pump and Resistor Ladder 101                    |

| Figure 7-3:                | Timer0 Timing: Internal Clock/Prescale 1:2 46 | Figure 14-1:                 | Configuration Word 103                                 |

| Figure 7-4:                | Timer0 Interrupt Timing                       | Figure 14-2:                 | Crystal/Ceramic Resonator Operation                    |