Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | LCD, POR, PWM, WDT                                                           |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 176 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc923t-04i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

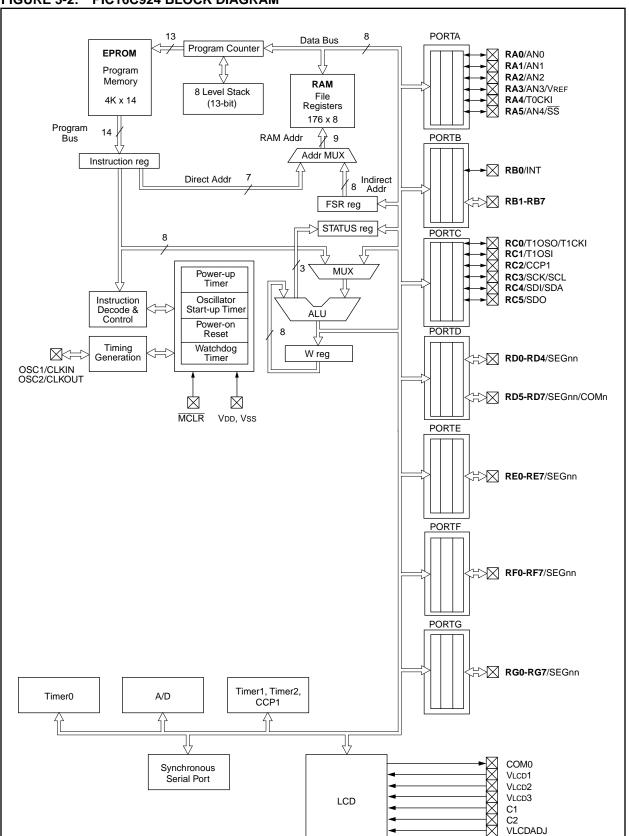

# 1.0 GENERAL DESCRIPTION

The PIC16C9XX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with an integrated LCD Driver module, in the PIC16CXXX mid-range family.

All PICmicro<sup>™</sup> microcontrollers employ an advanced RISC architecture. The PIC16CXXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C923** devices have 176 bytes of RAM and 25 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/PWM module, one serial port and one LCD module. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The LCD module features programmable multiplex mode (static, 1/2, 1/3 and 1/4) and drive bias (static and 1/3). It is capable of driving up to 32 segments and up to 4 commons. It can also drive the LCD panel while in SLEEP mode.

The PIC16C924 devices have 176 bytes of RAM and 25 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/PWM module, one serial port and one LCD module. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The LCD module features programmable multiplex mode (static, 1/2, 1/3 and 1/4) and drive bias (static and 1/3). It is capable of driving up to 32 segments and up to 4 commons. It can also drive the LCD panel while in SLEEP mode. The PIC16C924 also has an 5-channel high-speed 8-bit A/D. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, and meters.

The PIC16C9XX family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and reset(s).

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides recovery in the event of a software lock-up.

A UV erasable CERQUAD (compatible with PLCC) packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C9XX family fits perfectly in applications ranging from handheld meters, thermostats, to home security products. The EPROM technology makes customization of application programs (LCD panels, calibration constants, sensor interfaces, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C9XX very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, capture and compare, PWM functions and coprocessor applications).

# 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXXX family of devices (Appendix B).

# 1.2 Development Support

PIC16C9XX devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (500 ns @ 8 MHz) except for program branches.

The PIC16C923 and PIC16C924 both address 4K x 14 of program memory and 176 x 8 of data memory.

The PIC16CXXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXXX simple yet efficient, thus significantly reducing the learning curve.

PIC16CXXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# PIC16C9XX

NOTES:

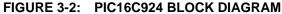

# 4.0 MEMORY ORGANIZATION

# 4.1 Program Memory Organization

The PIC16C9XX family has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

Only the first 4K x 14 (0000h-0FFFh) is physically implemented. Accessing a location above the physically implemented addresses will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

# 4.2 Data Memory Organization

The data memory is partitioned into four Banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

11 = Bank 3 (180h-1FFh)

10 = Bank 2 (100h-17Fh)

01 = Bank 1 (80h-FFh)

00 = Bank 0 (00h-7Fh)

The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. All four banks contain special function registers. Some "high use" special function registers are mirrored in other banks for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

The following General Purpose Registers are not physically implemented:

- F0h-FFh of Bank 1

- 170h-17Fh of Bank 2

- 1F0h-1FFh of Bank 3

These locations are used for common access across banks.

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT pin interrupt, TMR0, and the weak pull-ups on PORTB. **Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

# FIGURE 4-4: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1        | R/W-1                                                | R/W-1                                             | R/W-1              | R/W-1      | R/W-1                  | R/W-1      | R/W-1       |                                                                                                                                                |

|--------------|------------------------------------------------------|---------------------------------------------------|--------------------|------------|------------------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| RBPU<br>bit7 | INTEDG                                               | TOCS                                              | TOSE               | PSA        | PS2                    | PS1        | PS0<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:       | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE           | 3 pull-ups                                        | s are disa         | bled       | lividual port          | latch valu | es          |                                                                                                                                                |

| bit 6:       | INTEDG: In<br>1 = Interru<br>0 = Interru             | pt on risi                                        | ng edge o          | f RB0/INT  |                        |            |             |                                                                                                                                                |

| bit 5:       | <b>TOCS</b> : TMI<br>1 = Transiti<br>0 = Interna     | ion on RA                                         | A4/T0CKI           | pin        | (OUT)                  |            |             |                                                                                                                                                |

| bit 4:       |                                                      | ent on hi                                         | gh-to-low          | transition | on RA4/T0<br>on RA4/T0 |            |             |                                                                                                                                                |

| bit 3:       | <b>PSA</b> : Pres<br>1 = Presca<br>0 = Presca        | ler is ass                                        | signed to t        | he WDT     | module                 |            |             |                                                                                                                                                |

| bit 2-0:     | PS2:PS0:                                             | Prescale                                          | r Rate Se          | ect bits   |                        |            |             |                                                                                                                                                |

|              | Bit Value                                            | TMR0 R                                            | ate WD             | T Rate     |                        |            |             |                                                                                                                                                |

|              | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1:2<br>1:4<br>1:8<br>1:10<br>1:32<br>1:64<br>1:12 | 2 1<br>4 1<br>28 1 | : 2<br>: 4 |                        |            |             |                                                                                                                                                |

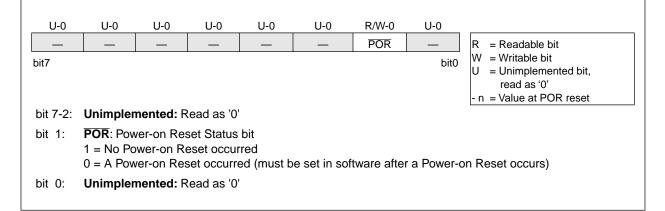

#### 4.2.2.6 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset.

# FIGURE 4-8: PCON REGISTER (ADDRESS 8Eh)

For various reset conditions see Table 14-4 and Table 14-5.

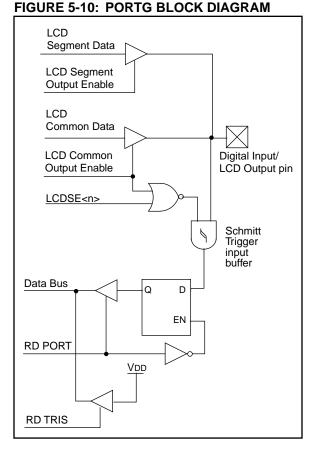

#### 5.7 PORTG and TRISG Register

PORTG is an digital input only port. Each pin is multiplexed with an LCD segment driver. These pins have Schmitt Trigger input buffers.

- Note 1: On a Power-on Reset these pins are configured as LCD segment drivers.

- Note 2: To configure the pins as a digital port, the corresponding bits in the LCDSE register must be cleared. Any bit set in the LCDSE register overrides any bit settings in the corresponding TRIS register.

# EXAMPLE 5-7: INITIALIZING PORTG

BCF STATUS,RP0 ;Select Bank2 BSF STATUS,RP1 ; BCF LCDSE,SE27 ;Make all PORTG BCF LCDSE,SE20 ;and PORTE<7> ;digital inputs

# TABLE 5-13: PORTG FUNCTIONS

| Bit# | Buffer Type                                          | Function                                                            |  |  |  |

|------|------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| bit0 | ST                                                   | Digital input or Segment Driver20                                   |  |  |  |

| bit1 | ST                                                   | Digital input or Segment Driver21                                   |  |  |  |

| bit2 | ST                                                   | Digital input or Segment Driver22                                   |  |  |  |

| bit3 | ST                                                   | Digital input or Segment Driver23                                   |  |  |  |

| bit4 | ST                                                   | Digital input or Segment Driver24                                   |  |  |  |

| bit5 | ST                                                   | Digital input or Segment Driver25                                   |  |  |  |

| bit6 | ST                                                   | Digital input or Segment Driver26                                   |  |  |  |

| bit7 | ST                                                   | Digital input or Segment Driver28 (not available on 64-pin devices) |  |  |  |

|      | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6 | bit0STbit1STbit2STbit3STbit4STbit5STbit6ST                          |  |  |  |

Legend: ST = Schmitt Trigger input

#### TABLE 5-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

| Address | Name  | Bit 7 | Bit 6      | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|------------|-------|-----------|-----------|-------|-------|-------|-------------------------------|---------------------------|

| 108h    | PORTG | RG7   | RG6        | RG5   | RG4       | RG3       | RG2   | RG1   | RG0   | 0000 0000                     | 0000 0000                 |

| 188h    | TRISG | PORTG | Data Direc | -     | 1111 1111 | 1111 1111 |       |       |       |                               |                           |

| 10Dh    | LCDSE | SE29  | SE27       | SE20  | SE16      | SE12      | SE9   | SE5   | SE0   | 1111 1111                     | 1111 1111                 |

Legend: Shaded cells are not used by PORTG.

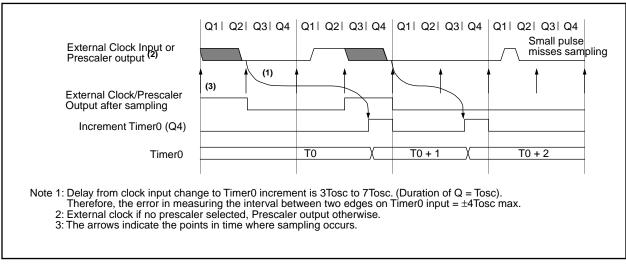

# 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

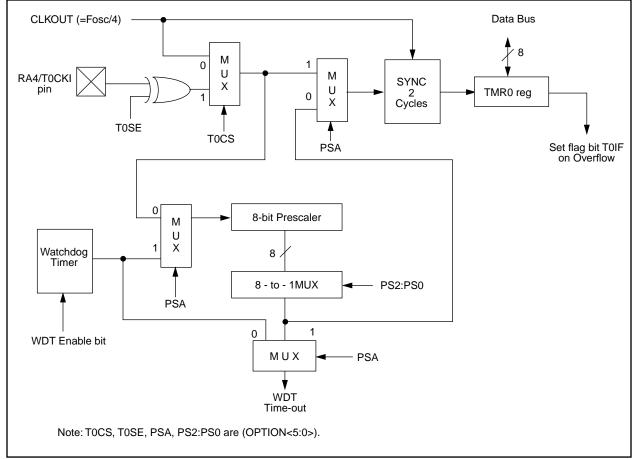

# 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler count. When assigned to WDT, a CLRWDT instruction will clear the prescaler count along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

# FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# TABLE 10-3: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Address                 | Name    | Bit 7   | Bit 6                      | Bit 5          | Bit 4          | Bit 3           | Bit 2        | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|-------------------------|---------|---------|----------------------------|----------------|----------------|-----------------|--------------|--------|--------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                       | TOIE           | INTE           | RBIE            | TOIF         | INTF   | RBIF   | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1    | LCDIF   | ADIF <sup>(1)</sup>        | —              | _              | SSPIF           | CCP1IF       | TMR2IF | TMR1IF | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1    | LCDIE   | ADIE <sup>(1)</sup>        | _              | _              | SSPIE           | CCP1IE       | TMR2IE | TMR1IE | 00 0000                       | 00 0000                         |

| 87h                     | TRISC   | _       | _                          | PORTC Da       | ta Direction ( | Control Regist  | ter          |        |        | 11 1111                       | 11 1111                         |

| 0Eh                     | TMR1L   | Holding | register fo                | or the Least S | Significant By | rte of the 16-b | oit TMR1 reg | ister  |        | xxxx xxxx                     | uuuu uuuu                       |

| 0Fh                     | TMR1H   | Holding | register fo                | or the Most S  | ignificant By  | te of the 16-bi | it TMR1 regi | ster   |        | xxxx xxxx                     | uuuu uuuu                       |

| 10h                     | T1CON   | _       |                            | T1CKPS1        | T1CKPS0        | T1OSCEN         | T1SYNC       | TMR1CS | TMR10N | 00 0000                       | uu uuuu                         |

| 15h                     | CCPR1L  | Capture | Capture/Compare/PWM1 (LSB) |                |                |                 |              |        |        |                               | uuuu uuuu                       |

| 16h                     | CCPR1H  | Capture | /Compare                   | /PWM1 (MS      | B)             |                 |              |        |        | xxxx xxxx                     | uuuu uuuu                       |

| 17h                     | CCP1CON | _       | _                          | CCP1X          | CCP1Y          | CCP1M3          | CCP1M2       | CCP1M1 | CCP1M0 | 00 0000                       | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes. Note 1: Bits ADIE and ADIF reserved on the PIC16C923, always maintain these bits clear.

#### TABLE 10-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                 | Name                              | Bit 7   | Bit 6                      | Bit 5         | Bit 4        | Bit 3        | Bit 2  | Bit 1   | Bit 0   | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|---------|----------------------------|---------------|--------------|--------------|--------|---------|---------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE     | PEIE                       | TOIE          | INTE         | RBIE         | TOIF   | INTF    | RBIF    | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1                              | LCDIF   | ADIF <sup>(1)</sup>        | _             | _            | SSPIF        | CCP1IF | TMR2IF  | TMR1IF  | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1                              | LCDIE   | ADIE <sup>(1)</sup>        | _             | _            | SSPIE        | CCP1IE | TMR2IE  | TMR1IE  | 00 0000                       | 00 0000                         |

| 87h                     | TRISC                             | _       | -                          | PORTC Da      | ta Direction | Control Regi | ster   |         |         | 11 1111                       | 11 1111                         |

| 11h                     | TMR2                              | Timer2  | module's reg               | gister        |              |              |        |         |         | 0000 0000                     | 0000 0000                       |

| 92h                     | PR2                               | Timer2  | module's Pe                | riod register |              |              |        |         |         | 1111 1111                     | 1111 1111                       |

| 12h                     | T2CON                             | _       | TOUTPS3                    | TOUTPS2       | TOUTPS1      | TOUTPS0      | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                     | -000 0000                       |

| 15h                     | CCPR1L Capture/Compare/PWM1 (LSB) |         |                            |               |              |              |        |         |         |                               | uuuu uuuu                       |

| 16h                     | CCPR1H                            | Capture | Capture/Compare/PWM1 (MSB) |               |              |              |        |         |         |                               | uuuu uuuu                       |

| 17h                     | CCP1CON                           | _       | _                          | CCP1X         | CCP1Y        | CCP1M3       | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                       | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode. Note 1: Bits ADIE and ADIF reserved on the PIC16C923, always maintain these bits clear.

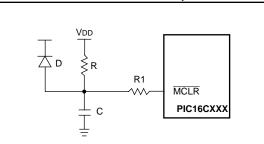

#### FIGURE 14-11:EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3: R1 =  $100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{\text{MCLR}}$  from external capacitor C in the event of  $\overline{\text{MCLR}}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

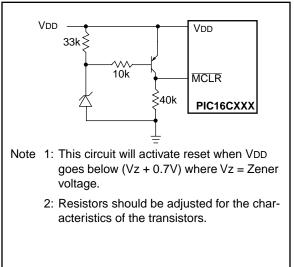

#### FIGURE 14-12:EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

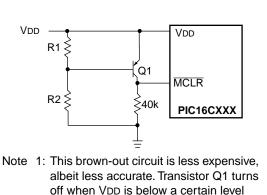

# FIGURE 14-13:EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

2: Resistors should be adjusted for the characteristics of the transistors.

#### 14.5 Interrupts

The PIC16C9XX family has up to 9 sources of interrupt:

| Interrupt Sources                         |     | cable<br>ices |

|-------------------------------------------|-----|---------------|

| External interrupt RB0/INT                | 923 | 924           |

| TMR0 overflow interrupt                   | 923 | 924           |

| PORTB change interrupts<br>(pins RB7:RB4) | 923 | 924           |

| A/D Interrupt                             | 923 | 924           |

| TMR1 overflow interrupt                   | 923 | 924           |

| TMR2 matches period interrupt             | 923 | 924           |

| CCP1 interrupt                            | 923 | 924           |

| Synchronous serial port interrupt         | 923 | 924           |

| LCD Module interrupt                      | 923 | 924           |

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function register PIR1. The corresponding interrupt enable bits are contained in special function register PIE1, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the RB0/INT pin or RB Port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

# 15.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

#### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file   | regis                                                                                 | ster op | perat | ions        |   |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------|---------|-------|-------------|---|--|--|--|--|--|

| 13                   | 8                                                                                     | 7       | 6     |             | 0 |  |  |  |  |  |

| OPCODE               |                                                                                       | d       |       | f (FILE #)  |   |  |  |  |  |  |

| d = 1 for des        | d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |         |       |             |   |  |  |  |  |  |

| Bit-oriented file re | giste                                                                                 | er ope  | ratio | ns          |   |  |  |  |  |  |

| 13                   | 10                                                                                    | 9       | 7     | 6           | 0 |  |  |  |  |  |

| OPCODE               |                                                                                       | b (Bl   | T #)  | f (FILE #)  |   |  |  |  |  |  |

| Literal and contro   | ol op                                                                                 | eratio  | ns    |             |   |  |  |  |  |  |

| 13                   |                                                                                       | 8       | 7     |             | 0 |  |  |  |  |  |

| OPCODE               |                                                                                       |         |       | k (literal) |   |  |  |  |  |  |

|                      | k = 8-bit immediate value                                                             |         |       |             |   |  |  |  |  |  |

| 13 11                | 10                                                                                    |         |       |             | 0 |  |  |  |  |  |

| OPCODE               |                                                                                       |         | k (   | (literal)   |   |  |  |  |  |  |

| k = 11-bit im        | med                                                                                   | iate va | alue  |             |   |  |  |  |  |  |

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16CXXX products, do not use |

|       | the OPTION and TRIS instructions.     |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PICmicro. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PICmicro series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 16.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PICmicro family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

#### 16.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PICmicro device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

# 16.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 16.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

#### 17.2 DC Characteristics:

#### PIC16LC923/924-04 (Commercial, Industrial)

| DC CHA       | ARACTERISTICS                                                    |         | Standa<br>Operat | •    | itions (unless otherwise stated) $.0^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial |       |                                                                         |

|--------------|------------------------------------------------------------------|---------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                                   | Sym     | Min              | Тур† | Max                                                                                                                                          | Units | Conditions                                                              |

| D001         | Supply Voltage                                                   | Vdd     | 2.5              | -    | 6.0                                                                                                                                          | V     | LP, XT, RC osc configuration                                            |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                           | Vdr     | -                | 1.5  | -                                                                                                                                            | V     |                                                                         |

| D003         | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | VPOR    | -                | Vss  | -                                                                                                                                            | V     | See Power-on Reset section for details                                  |

| D004*        | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | SVDD    | 0.05             | -    | -                                                                                                                                            | V/ms  | (Note 6) See Power-on Reset section for details                         |

| D010         | Supply Current (Note 2)                                          | Idd     | -                | 2.0  | 3.8                                                                                                                                          | mA    | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = $3.0V$ (Note 4)      |

| D011         |                                                                  |         | -                | 13.5 | 30                                                                                                                                           | μA    | LP osc configuration,<br>Fosc = $32 \text{ kHz}$ , VDD = $4.0 \text{V}$ |

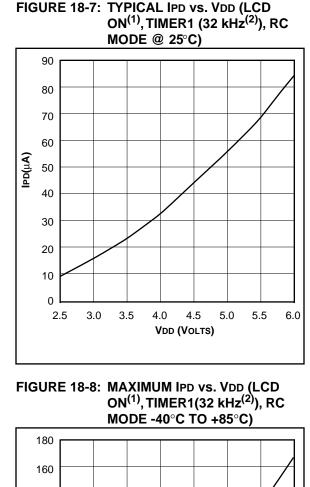

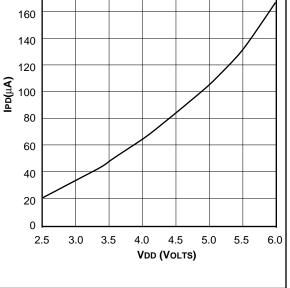

| D020         | Power-down Current<br>(Note 3)                                   | IPD     | -                | 0.9  | 5                                                                                                                                            | μA    | VDD = 3.0V                                                              |

|              | Module Differential Cur-<br>rent (Note 5)                        |         |                  |      |                                                                                                                                              |       |                                                                         |

| D021         | Watchdog Timer                                                   | ∆lwdt   | -                | 6.0  | 20                                                                                                                                           | μA    | VDD = 3.0V                                                              |

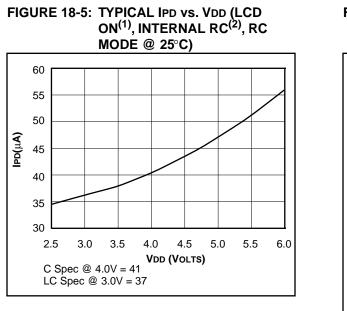

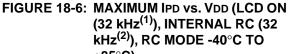

| D022*        | LCD Voltage Generation<br>w/internal RC osc<br>enabled           | ∆ILCDRC | -                | 36   | 50                                                                                                                                           | μA    | VDD = 3.0V (Note 7)                                                     |

| D024*        | LCD Voltage Generation<br>w/Timer1 @ 32.768 kHz                  | ∆ILCDT1 | -                | 15   | 29                                                                                                                                           | μA    | VDD = 3.0V (Note 7)                                                     |

| D025*        | Timer1 oscillator                                                | ∆l⊤1osc | -                | 3.1  | 6.5                                                                                                                                          | μA    | VDD = 3.0V                                                              |

| D026*        | A/D Converter                                                    | ΔIAD    | -                | 1.0  | -                                                                                                                                            | μA    | A/D on, not converting                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 6: PWRT must be enabled for slow ramps.

- 7:  $\Delta$ ILCDT1 and  $\Delta$ ILCDRC includes the current consumed by the LCD Module and the voltage generation circuitry. This does not include current dissipated by the LCD panel.

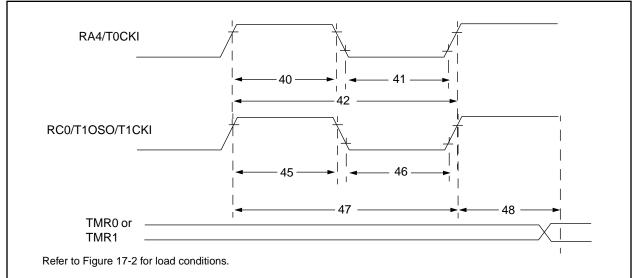

#### FIGURE 17-6: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 17-7: TIMER0 AND TIMER1 EXTERNAL CL | OCK REQUIREMENTS |

|-------------------------------------------|------------------|

|-------------------------------------------|------------------|

| Param<br>No. | Sym               | Characteristic                                                                         |                            |                         | Min                                              | Тур† | Max | Units | Conditions                         |  |

|--------------|-------------------|----------------------------------------------------------------------------------------|----------------------------|-------------------------|--------------------------------------------------|------|-----|-------|------------------------------------|--|

| 40*          | Tt0H              | ··· · · · · · · · · · · · · · · · · ·                                                  |                            | No Prescaler            | 0.5Tcy + 20                                      | -    | —   | ns    | Must also meet<br>parameter 42     |  |

|              |                   |                                                                                        |                            | With Prescaler          | 10                                               | _    | _   | ns    |                                    |  |

| 41*          | Tt0L              |                                                                                        |                            | No Prescaler            | 0.5TCY + 20                                      | —    | —   | ns    | Must also meet parameter 42        |  |

|              |                   |                                                                                        |                            | With Prescaler          | 10                                               | —    | —   | ns    |                                    |  |

| 42*          | Tt0P T0CKI Period |                                                                                        |                            | No Prescaler            | Tcy + 40                                         | —    | —   | ns    |                                    |  |

|              |                   |                                                                                        |                            | With Prescaler          | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | _   | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H              | T1CKI High Time                                                                        | Synchronous, P             | rescaler = 1            | 0.5TCY + 20                                      | _    | —   | ns    | Must also meet                     |  |

|              |                   |                                                                                        | Synchronous,               | PIC16 <b>C</b> 923/924  | 15                                               | -    | -   | ns    | parameter 47                       |  |

|              |                   |                                                                                        | Prescaler = 2,4,8          | PIC16 <b>LC</b> 923/924 | 25                                               | -    | -   | ns    |                                    |  |

|              |                   |                                                                                        | Asynchronous               | PIC16 <b>C</b> 923/924  | 30                                               | —    | —   | ns    |                                    |  |

|              |                   |                                                                                        |                            |                         | PIC16LC923/924                                   | 50   | —   | —     | ns                                 |  |

| 46*          | Tt1L              | Tt1L T1CKI Low Time                                                                    | Synchronous, Prescaler = 1 |                         | 0.5TCY + 20                                      | —    | —   | ns    | Must also meet                     |  |

|              |                   |                                                                                        | Synchronous,               | PIC16 <b>C</b> 923/924  | 15                                               | —    | —   | ns    | parameter 47                       |  |

|              |                   |                                                                                        | Prescaler =<br>2,4,8       | PIC16 <b>LC</b> 923/924 | 25                                               | -    | -   | ns    |                                    |  |

|              |                   |                                                                                        | Asynchronous               | PIC16 <b>C</b> 923/924  | 30                                               | —    | —   | ns    | _                                  |  |

|              |                   |                                                                                        |                            | PIC16LC923/924          | 50                                               | —    | —   | ns    |                                    |  |

| 47*          | Tt1P              | T1CKI input period                                                                     | Synchronous                | PIC16 <b>C</b> 923/924  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | _   | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                   |                                                                                        |                            | PIC16 <b>LC</b> 923/924 | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |     |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                   |                                                                                        | Asynchronous               | PIC16 <b>C</b> 923/924  | 60                                               | —    | -   | ns    |                                    |  |

|              |                   |                                                                                        |                            | PIC16LC923/924          |                                                  | _    | _   | ns    |                                    |  |

|              | Ft1               | Timer1 oscillator input frequency range<br>(oscillator enabled by setting bit T1OSCEN) |                            |                         | DC                                               | -    | 200 | kHz   |                                    |  |

| 48           | TCKEZtmr          | 1 Delay from external                                                                  | 2Tosc                      | —                       | 7Tosc                                            | —    |     |       |                                    |  |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The LCD module is turned on, internal charge pump enabled, 1/4 MUX, 32 Hz frame frequency and no load on LCD segments/commons. IPD will increase depending on the LCD panel connected to the PIC16C9XX.

Note 2: Indicates the clock source to the LCD module.