Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 x 8                                                                    |

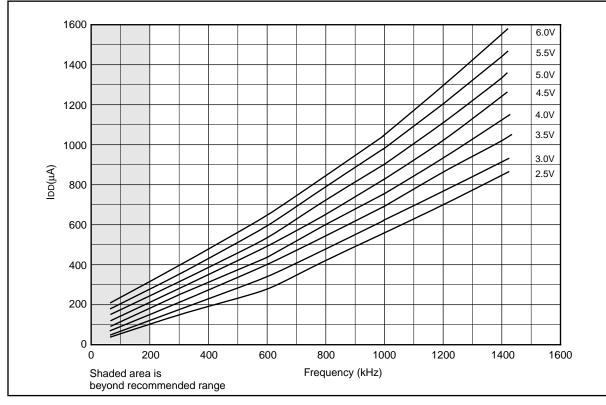

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc924-04i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC16C9XX FAMILY OF DEVICES

|            |                                                              | PIC16C923                                    | PIC16C924                                    |

|------------|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Clock      | Maximum Frequency of Operation (MHz)                         | 8                                            | 8                                            |

| Mamani     | EPROM Program Memory                                         | 4K                                           | 4K                                           |

| Memory     | Data Memory (bytes)                                          | 176                                          | 176                                          |

|            | Timer Module(s)                                              | TMR0,<br>TMR1,<br>TMR2                       | TMR0,<br>TMR1,<br>TMR2                       |

|            | Capture/Compare/PWM Module(s)                                | 1                                            | 1                                            |

| Peripheral | Serial Port(s)<br><sup>S</sup> (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C                         | SPI/I <sup>2</sup> C                         |

|            | Parallel Slave Port                                          | —                                            | —                                            |

|            | A/D Converter (8-bit) Channels                               |                                              | 5                                            |

|            | LCD Module                                                   | 4 Com,<br>32 Seg                             | 4 Com,<br>32 Seg                             |

|            | Interrupt Sources                                            | 8                                            | 9                                            |

|            | I/O Pins                                                     | 25                                           | 25                                           |

|            | Input Pins                                                   | 27                                           | 27                                           |

|            | Voltage Range (Volts)                                        | 2.5-6.0                                      | 2.5-6.0                                      |

| Features   | In-Circuit Serial Programming                                | Yes                                          | Yes                                          |

|            | Brown-out Reset                                              | —                                            | —                                            |

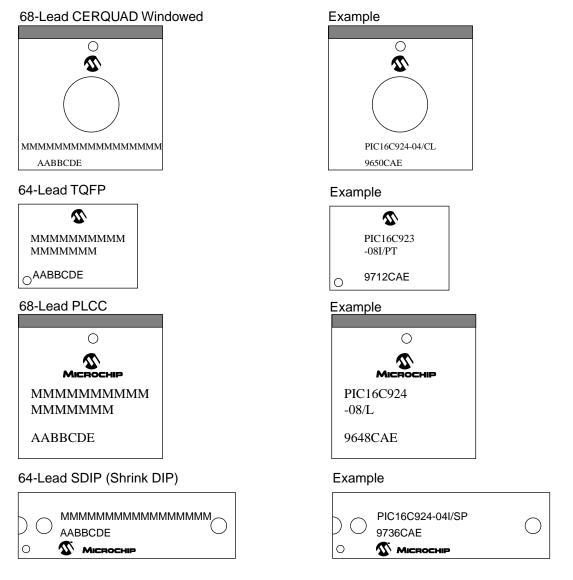

|            | Packages                                                     | 64-pin SDIP,<br>TQFP;<br>68-pin PLCC,<br>Die | 64-pin SDIP,<br>TQFP;<br>68-pin PLCC,<br>Die |

All PICmicro Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C9XX Family devices use serial programming with clock pin RB6 and data pin RB7.

#### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and external RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### FIGURE 4-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0       | R/W-0                                                                                                                                                                                                                                                                                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-x        |                                                                               |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------------|-------------------------------------------------------------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                                                                                                                                                 | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |  |

| bit 7:      | - n = Value at POR reset<br>GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                                                                                                                                                  |       |       |       |       |       |              |                                                                               |  |

| bit 6:      |                                                                                                                                                                                                                                                                                                                                      |       |       |       |       |       |              |                                                                               |  |

| bit 5:      |                                                                                                                                                                                                                                                                                                                                      |       |       |       |       |       |              |                                                                               |  |

| bit 4:      | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                                                                                                                                                             |       |       |       |       |       |              |                                                                               |  |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                                                           |       |       |       |       |       |              |                                                                               |  |

| bit 2:      | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                                                                               |       |       |       |       |       |              |                                                                               |  |

| bit 1:      |                                                                                                                                                                                                                                                                                                                                      |       |       |       |       |       |              |                                                                               |  |

| bit 0:      |                                                                                                                                                                                                                                                                                                                                      |       |       |       |       |       |              |                                                                               |  |

| globa       | U = None of the RB7:RB4 pins have changed state<br>Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the<br>global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to<br>enabling an interrupt. |       |       |       |       |       |              |                                                                               |  |

### 11.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, dis-

play drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

#### FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                           | R-0                                                                      | R-0                                       | R-0                                                                  | R-0                                              | R-0          | R-0                      | ]                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|--------------|--------------------------|------------------------------------------------------------------|

| SMP    | CKE                                                                                                                                                                                                                                                                                             | D/Ā                                                                      | Р                                         | S                                                                    | R/W                                              | UA           | BF                       | R = Readable bit<br>W = Writable bit                             |

| bit7   |                                                                                                                                                                                                                                                                                                 |                                                                          |                                           |                                                                      |                                                  |              | bitO                     | U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |

| bit 7: | <u>SPI Ma</u><br>1 = Inpu<br>0 = Inpu<br><u>SPI Sla</u>                                                                                                                                                                                                                                         | <u>ster Mod</u> ut data sa<br>ut data sa<br>ut data sa<br><u>ve Mode</u> | Impled at o<br>Impled at i                | end of data<br>niddle of d                                           | i output time<br>ata output tir<br>ed in slave n |              |                          |                                                                  |

| oit 6: | $\frac{CKP = 0}{1 = Dat}$ $0 = Dat$ $\frac{CKP = 0}{1 = Dat}$                                                                                                                                                                                                                                   | <u>0</u><br>a transmi<br>a transmi<br><u>1</u><br>a transmi              | tted on ris<br>tted on fal<br>tted on fal | ct (Figure<br>ing edge o<br>ling edge c<br>ling edge c<br>ing edge o | of SCK<br>of SCK                                 | 11-6, and F  | <sup>-</sup> igure 11-7) |                                                                  |

| bit 5: | <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                                         |                                                                          |                                           |                                                                      |                                                  |              |                          |                                                                  |

| bit 4: | <ul> <li>P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Start bit was detected last)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul>   |                                                                          |                                           |                                                                      |                                                  |              |                          |                                                                  |

| bit 3: | <ul> <li>S: Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Stop bit was detected last)</li> <li>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Start bit was not detected last</li> </ul> |                                                                          |                                           |                                                                      |                                                  |              |                          |                                                                  |

| bit 2: | <b>R/W</b> : Read/Write bit information ( $I^2C$ mode only)<br>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or $\overline{ACK}$ bit.<br>1 = Read<br>0 = Write                        |                                                                          |                                           |                                                                      |                                                  |              |                          |                                                                  |

| bit 1: | 1 = Indi                                                                                                                                                                                                                                                                                        | cates tha                                                                | t the user                                | t I <sup>2</sup> C mode<br>needs to u<br>I to be upd                 | pdate the ad                                     | dress in the | e SSPADD                 | register                                                         |

| bit 0: | BF: Buf                                                                                                                                                                                                                                                                                         | fer Full S                                                               | tatus bit                                 |                                                                      |                                                  |              |                          |                                                                  |

|        | 1 = Rec                                                                                                                                                                                                                                                                                         | eive com                                                                 |                                           | es)<br>PBUF is ful<br>SSPBUF is                                      |                                                  |              |                          |                                                                  |

|        | 1 = Trar                                                                                                                                                                                                                                                                                        |                                                                          | rogress, S                                | SPBUF is<br>PBUF is er                                               |                                                  |              |                          |                                                                  |

## 12.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

#### This section applies to the PIC16C924 only.

The analog-to-digital (A/D) converter module has five inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's AVDD pin or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 12-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 12-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0    | R/W-0                                                                                                                                                                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |                  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------|-------|-------|------------------|--|--|

| ADCS1    | ADCS0                                                                                                                                                                                                                   | CHS2  | CHS1  | CHS0  | GO/DONE | —     | ADON  | R = Readable bit |  |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                                                                                                           |       |       |       |         |       |       |                  |  |  |

| bit 7-6: |                                                                                                                                                                                                                         |       |       |       |         |       |       |                  |  |  |

| bit 5-3: | : CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)                           |       |       |       |         |       |       |                  |  |  |

| bit 2:   | GO/DONE: A/D Conversion Status bit                                                                                                                                                                                      |       |       |       |         |       |       |                  |  |  |

|          | If ADON = 1<br>1 = A/D conversion in progress (setting this bit starts the A/D conversion)<br>0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion<br>is complete) |       |       |       |         |       |       |                  |  |  |

| bit 1:   | Reserved: Always maintain this bit clear                                                                                                                                                                                |       |       |       |         |       |       |                  |  |  |

| bit 0:   | <ul> <li>ADON: A/D On bit</li> <li>1 = A/D converter module is operating</li> <li>0 = A/D converter module is shutoff and consumes no operating current</li> </ul>                                                      |       |       |       |         |       |       |                  |  |  |

### FIGURE 12-1: ADCON0 REGISTER (ADDRESS 1Fh)

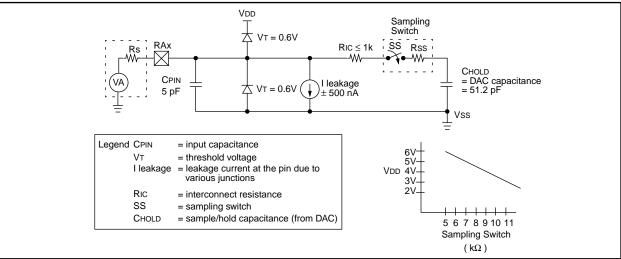

#### 12.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 12-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), (Figure 12-4). The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 12-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

# EQUATION 12-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-Tc/CHOLD(Ric + Rss + Rs))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$Tc = -(51.2 \text{ pF})(1 \text{ k}\Omega - \text{Rss} + \text{Rs}) \ln(1/511)$

Example 12-1 shows the calculation of the minimum required acquisition time (TACQ). This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (system max.) = 50°C

VHOLD = 0 @ t = 0

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 12-1: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

TACQ = Amplifier Settling Time +

- Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \,\mu s + Tc + [(Temp 25^{\circ}C)(0.05 \,\mu s/^{\circ}C)]$

- TC = -CHOLD (RIC + RSS + RS) ln(1/511) -51.2 pF (1 k $\Omega$  + 7 k $\Omega$  + 10 k $\Omega$ ) ln(0.0020) -51.2 pF (18 k $\Omega$ ) ln(0.0020) -0.921  $\mu$ s (-6.2364) 5.747  $\mu$ s TACO = 5  $\mu$ s + 5 747  $\mu$ s + 1/50°C - 25°C)(0.05  $\mu$ s/°C

- TACQ = 5 μs + 5.747 μs + [(50°C 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

#### 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

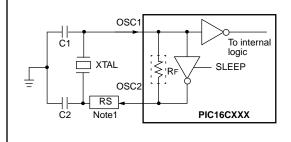

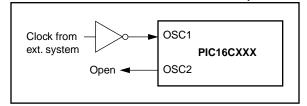

# 14.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 14-3).

#### FIGURE 14-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 14-1 and Table 14-2 for recommended values of C1 and C2.

Note 1: A series resistor may be required for AT strip cut crystals.

#### FIGURE 14-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 14-1: CERAMIC RESONATORS

| lz 15<br>lz 15                                                          | <b>OSC1</b><br>- 100 pF<br>- 68 pF<br>- 68 pF             | <b>OSC2</b><br>68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF                              |  |  |  |

|-------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| lz 15<br>lz 15                                                          | - 68 pF                                                   | 15 - 68 pF                                                                          |  |  |  |

| z 15                                                                    | •                                                         |                                                                                     |  |  |  |

|                                                                         | - 68 pF                                                   | 15 - 68 pF                                                                          |  |  |  |

| - 40                                                                    |                                                           |                                                                                     |  |  |  |

| lz  10                                                                  | - 68 pF                                                   | 10 - 68 pF                                                                          |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                                           |                                                                                     |  |  |  |

| :                                                                       |                                                           |                                                                                     |  |  |  |

| nic EFO-/                                                               | A455K04B                                                  | ± 0.3%                                                                              |  |  |  |

| Murata Erie CSA2.00MG ± 0.5%                                            |                                                           |                                                                                     |  |  |  |

| Murata Erie CSA4.00MG ± 0.5%                                            |                                                           |                                                                                     |  |  |  |

| Erie CSA                                                                | 8.00MT                                                    | ± 0.5%                                                                              |  |  |  |

|                                                                         | es are for d<br>om of page<br>:<br>Dnic EFO-/<br>Erie CSA | es are for design guidar<br>om of page.<br>:<br>pnic EFO-A455K04B<br>Erie CSA2.00MG |  |  |  |

All resonators used did not have built-in capacitors.

#### TABLE 14-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Оѕс Туре | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| ХТ       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                       |          |  |  |  |

|---------------|-----------------------|----------|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A | ± 20 PPM |  |  |  |

| 200 kHz       | STD XTL 200.000KHz    | ± 20 PPM |  |  |  |

| 1 MHz         | ECS ECS-10-13-1       | ± 50 PPM |  |  |  |

| 4 MHz         | ECS ECS-40-20-1       | ± 50 PPM |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C | ± 30 PPM |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 14-1).

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 14.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 14.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

#### 14.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 14.4.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-8, Figure 14-9, and Figure 14-10 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 14-5 shows the reset conditions for some special function registers, while Table 14-6 shows the reset conditions for all the registers.

#### 14.4.5 POWER CONTROL/STATUS REGISTER (PCON)

Bit1 is Power-on Reset Status bit POR. It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configuration | Powe      | Wake-up from SLEEP |           |

|--------------------------|-----------|--------------------|-----------|

|                          | PWRTE = 1 | <b>PWRTE = 0</b>   |           |

| XT, HS, LP               | 1024Tosc  | 72 ms + 1024Tosc   | 1024 Tosc |

| RC                       |           | 72 ms              |           |

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS

| CLRF              | Clear f                                                               |                                                                        |                 |                       |  |

|-------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----------------|-----------------------|--|

| Syntax:           | [ <i>label</i> ] C                                                    | [label] CLRF f                                                         |                 |                       |  |

| Operands:         | $0 \le f \le 12$                                                      | $0 \le f \le 127$                                                      |                 |                       |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                                                                        |                 |                       |  |

| Status Affected:  | Z                                                                     |                                                                        |                 |                       |  |

| Encoding:         | 00                                                                    | 0001                                                                   | lfff            | ffff                  |  |

| Description:      | The conter<br>and the Z                                               | -                                                                      | ster 'f' are    | cleared               |  |

| Words:            | 1                                                                     |                                                                        |                 |                       |  |

| Cycles:           | 1                                                                     |                                                                        |                 |                       |  |

| Q Cycle Activity: | Q1                                                                    | Q2                                                                     | Q3              | Q4                    |  |

|                   | Decode                                                                | Read<br>register<br>'f'                                                | Process<br>data | Write<br>register 'f' |  |

|                   |                                                                       |                                                                        |                 |                       |  |

| Example           | CLRF                                                                  | FLAG                                                                   | S_REG           |                       |  |

|                   | After Inst                                                            | ore Instruction<br>FLAG_REG = 0x5A<br>r Instruction<br>FLAG_REG = 0x00 |                 |                       |  |

|                   |                                                                       | Z                                                                      | =               | 1                     |  |

| CLRW              | Clear W                              |                  |                 |               |

|-------------------|--------------------------------------|------------------|-----------------|---------------|

| Syntax:           | [ label ]                            | CLRW             |                 |               |

| Operands:         | None                                 |                  |                 |               |

| Operation:        | $00h \rightarrow (V 1 \rightarrow Z$ | V)               |                 |               |

| Status Affected:  | Z                                    |                  |                 |               |

| Encoding:         | 00                                   | 0001             | 0xxx            | xxxx          |

| Description:      | W register<br>set.                   | is cleared       | . Zero bit (    | Z) is         |

| Words:            | 1                                    |                  |                 |               |

| Cycles:           | 1                                    |                  |                 |               |

| Q Cycle Activity: | Q1                                   | Q2               | Q3              | Q4            |

|                   | Decode                               | No-<br>Operation | Process<br>data | Write to<br>W |

| Example           | CLRW                                 |                  |                 |               |

|                   | Before In                            | struction        |                 |               |

|                   |                                      |                  | 0x5A            |               |

|                   | After Inst                           |                  | 0200            |               |

|                   |                                      | VV =             | 0x00            |               |

# PIC16C9XX

| INCF                           | Increment f                                                                                                              | INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                             |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                        | [ <i>label</i> ] INCF f,d                                                                                                | Syntax:           | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                        |  |  |  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                               | Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                           |  |  |  |

| Operation:<br>Status Affected: | (f) + 1 $\rightarrow$ (destination)<br>Z                                                                                 | Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                         |  |  |  |

| Encoding:                      | -<br>00 1010 dfff ffff                                                                                                   | Status Affected:  | None                                                                                                                                                                                                               |  |  |  |

| Description:                   | The contents of register 'f' are incre-                                                                                  | Encoding:         | 00 1111 dfff ffff                                                                                                                                                                                                  |  |  |  |

| Words:                         | mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. | Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is |  |  |  |

| Cycles:                        | 1                                                                                                                        |                   | executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction.                                                                                                                        |  |  |  |

| Q Cycle Activity:              | Q1 Q2 Q3 Q4                                                                                                              | Words:            | 1                                                                                                                                                                                                                  |  |  |  |

|                                | Decode Read Process Write to destination                                                                                 | Cycles:           | 1(2)                                                                                                                                                                                                               |  |  |  |

|                                | 'f'                                                                                                                      | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                        |  |  |  |

| Example                        | incf CNT, 1                                                                                                              |                   | Decode Read register 'f' Process Write to destination                                                                                                                                                              |  |  |  |

|                                | Before Instruction                                                                                                       | If Skip:          | (2nd Cycle)                                                                                                                                                                                                        |  |  |  |

|                                | CNT = 0xFF<br>Z = 0                                                                                                      |                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                        |  |  |  |

|                                | After Instruction<br>CNT = 0x00<br>Z = 1                                                                                 |                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                   |  |  |  |

|                                |                                                                                                                          | Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                 |  |  |  |

|                                |                                                                                                                          |                   | Before Instruction<br>PC = address HERE<br>After Instruction                                                                                                                                                       |  |  |  |

CNT = CNT + 1 if CNT= 0, PC = address CONTINUE

if  $CNT \neq 0$ , PC = address HERE +1

| NOP               | No Oper       | ation            |                  |                  |  |  |

|-------------------|---------------|------------------|------------------|------------------|--|--|

| Syntax:           | [ label ]     | NOP              |                  |                  |  |  |

| Operands:         | None          |                  |                  |                  |  |  |

| Operation:        | No opera      | No operation     |                  |                  |  |  |

| Status Affected:  | None          |                  |                  |                  |  |  |

| Encoding:         | 00            | 0000             | 0xx0             | 0000             |  |  |

| Description:      | No operation. |                  |                  |                  |  |  |

| Words:            | 1             |                  |                  |                  |  |  |

| Cycles:           | 1             |                  |                  |                  |  |  |

| Q Cycle Activity: | Q1            | Q2               | Q3               | Q4               |  |  |

|                   | Decode        | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |

| Example           | NOP           |                  |                  |                  |  |  |

| Return from Interrupt                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [ label ]                                                                                                                                                                                                         | RETFIE                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| None                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| $\begin{array}{l} TOS \rightarrow F \\ 1 \rightarrow GIE \end{array}$                                                                                                                                             | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| None                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 00                                                                                                                                                                                                                | 0000                                                                                                                                                                                                                                                                                          | 0000                                                                                                                                                                                                                                          | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in the<br>PC. Interrupts are enabled by setting<br>Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Q1                                                                                                                                                                                                                | Q2                                                                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                            | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Decode                                                                                                                                                                                                            | No-<br>Operation                                                                                                                                                                                                                                                                              | Set the<br>GIE bit                                                                                                                                                                                                                            | Pop from the Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| No-<br>Operation                                                                                                                                                                                                  | No-<br>Operation                                                                                                                                                                                                                                                                              | No-<br>Operation                                                                                                                                                                                                                              | No-<br>Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                   | $\begin{bmatrix} label \\ None \\ TOS \rightarrow F \\ 1 \rightarrow GIE \\ None \\ \hline 00 \\ \hline 00 \\ Return fro and Top of PC. Interru Global Interru Global Interru Global Interru Global Interru Global Interruction 1 \\ 2 \\ Q1 \\ \hline Decode \\ \hline No- \\ \end{bmatrix}$ | $[label] RETFIE$ None $TOS \rightarrow PC,$ $1 \rightarrow GIE$ None $00 0000$ Return from Interrup and Top of Stack (TC PC. Interrupts are er Global Interrupt Ena (INTCON<7>). This is instruction. 1 2 Q1 Q2 $Decode No-Operation$ No- No- | $\begin{bmatrix} label \end{bmatrix} \text{ RETFIE} \\ \text{None} \\ \hline \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \\ \hline \text{None} \\ \hline 00 & 0000 & 0000 \\ \hline 0000 & 0000 \\ \hline \text{Return from Interrupt. Stack is and Top of Stack (TOS) is loade PC. Interrupts are enabled by s Global Interrupt Enable bit, GIE (INTCON<7>). This is a two cyrinstruction. \\ 1 \\ 2 \\ \hline Q1 & Q2 & Q3 \\ \hline \hline \text{Decode} & \frac{\text{No-}}{\text{Operation}} & \frac{\text{Set the}}{\text{GIE bit}} \\ \hline \text{No-} & \text{No-} & \text{No-} \\ \hline \end{array}$ |  |  |

Example

RETFIE

After Interrupt

| PC  | = | TOS |

|-----|---|-----|

| GIE | = | 1   |

| OPTION           | Load Op                                                                                      | tion Reg                                       | gister                                               |                                         |

|------------------|----------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|

| Syntax:          | [ label ]                                                                                    | OPTION                                         | ٧                                                    |                                         |

| Operands:        | None                                                                                         |                                                |                                                      |                                         |

| Operation:       | $(W) \rightarrow O$                                                                          | PTION                                          |                                                      |                                         |

| Status Affected: | None                                                                                         |                                                |                                                      |                                         |

| Encoding:        | 00                                                                                           | 0000                                           | 0110                                                 | 0010                                    |

| Description:     | The conter<br>loaded in t<br>instruction<br>patibility w<br>Since OPT<br>register, th<br>it. | he OPTIC<br>is suppo<br>ith PIC16<br>TION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |

| Words:           | 1                                                                                            |                                                |                                                      |                                         |

| Cycles:          | 1                                                                                            |                                                |                                                      |                                         |

| Example          |                                                                                              |                                                |                                                      |                                         |

|                  |                                                                                              | re PIC16                                       | rd compa<br>CXX production.                          |                                         |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                  | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                           |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                        |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                            |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |