Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | S08                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 40MHz                                                         |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                            |

| Number of I/O              | 39                                                            |

| Program Memory Size        | 32KB (32K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 48-VFQFN Exposed Pad                                          |

| Supplier Device Package    | 48-QFN-EP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08gt32acfder |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

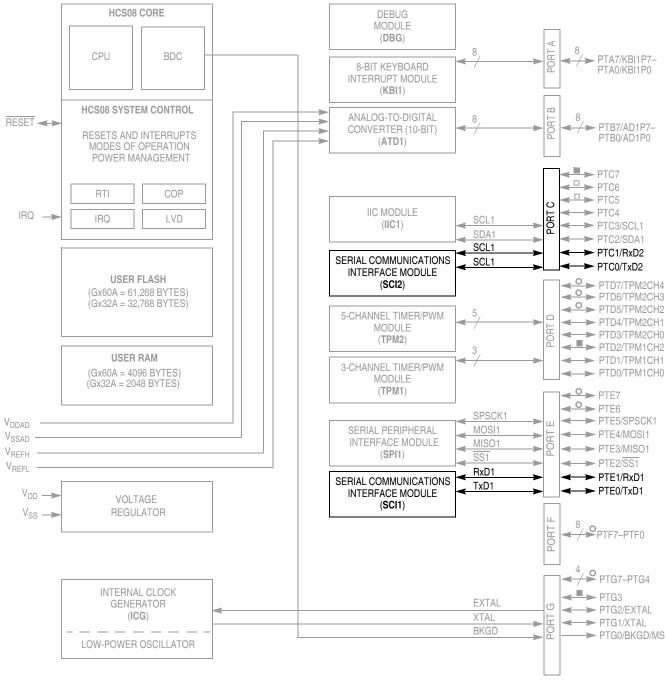

# MC9S08GB60A Data Sheet

Covers: MC9S08GB60A MC9S08GB32A MC9S08GT60A MC9S08GT32A

> MC9S08GB60A Rev. 2 07/2008

**Chapter 2 Pins and Connections**

debug connector so a development system can directly reset the MCU system. If desired, a manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

Whenever any reset is initiated (whether from an external signal or from an internal system), the reset pin is driven low for approximately 34 cycles of  $f_{Self\_reset}$ , released, and sampled again approximately 38 cycles of  $f_{Self\_reset}$  later. If reset was caused by an internal source such as low-voltage reset or watchdog timeout, the circuitry expects the reset pin sample to return a logic 1. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system control reset status register (SRS).

In EMC-sensitive applications, an external RC filter is recommended on the reset pin. See Figure 2-4 for an example.

### 2.3.4 Background / Mode Select (PTG0/BKGD/MS)

The background/mode select (BKGD/MS) shares its function with an I/O port pin. While in reset, the pin functions as a mode select pin. Immediately after reset rises the pin functions as the background pin and can be used for background debug communication. While functioning as a background/mode select pin, the pin includes an internal pullup device, input hysteresis, a standard output driver, and no output slew rate control. When used as an I/O port (PTG0) the pin is limited to output only.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during the rising edge of reset which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

### 2.3.5 General-Purpose I/O and Peripheral Ports

The remaining 55 pins are shared among general-purpose I/O and on-chip peripheral functions such as timers and serial I/O systems. (17 of these pins are not bonded out on the 48-pin package, 20 of these pins are not bonded out on the 44-pin package and 22 of hese pins are not bonded out on the 42-pin package.) Immediately after reset, all 55 of these pins are configured as high-impedance general-purpose inputs with internal pullup devices disabled.

#### NOTE

To prevent extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

Chapter 5 Resets, Interrupts, and System Configuration

- Illegal opcode detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self}$  reset selected. The reset pin is driven low for 34 internal bus cycles where the internal bus frequency is half the ICG frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.8.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>13</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user should still write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is set to 1 to enable the interrupt. The I bit

**Chapter 6 Parallel Input/Output**

Port A can be configured to be keyboard interrupt input pins. Refer to Chapter 9, "Keyboard Interrupt (S08KBIV1)," for more information about using port A pins as keyboard interrupts pins.

### 6.3.2 Port B and Analog to Digital Converter Inputs

| Port B                       |          | Bit 7          | 6              | 5              | 4              | 3              | 2              | 1              | Bit 0          |

|------------------------------|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                              | MCU Pin: | PTB7/<br>AD1P7 | PTB6/<br>AD1P6 | PTB5/<br>AD1P5 | PTB4/<br>AD1P4 | PTB3/<br>AD1P3 | PTB2/<br>AD1P2 | PTB1/<br>AD1P1 | PTB0/<br>AD1P0 |

| Figure 6-3. Port B Pin Names |          |                |                |                |                |                |                |                |                |

Port B is an 8-bit port shared among the ATD inputs and general-purpose I/O. Any pin enabled as an ATD input will be forced to act as an input.

Port B pins are available as general-purpose I/O pins controlled by the port B data (PTBD), data direction (PTBDD), pullup enable (PTBPE), and slew rate control (PTBSE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

When the ATD module is enabled, analog pin enables are used to specify which pins on port B will be used as ATD inputs. Refer to Chapter 14, "Analog-to-Digital Converter (S08ATDV3)," for more information about using port B pins as ATD pins.

### 6.3.3 Port C and SCI2, IIC, and High-Current Drivers

| Port C |          | Bit 7 | 6    | 5    | 3    | 3             | 2             | 1             | Bit 0         |

|--------|----------|-------|------|------|------|---------------|---------------|---------------|---------------|

|        | MCU Pin: | PTC7  | PTC6 | PTC5 | PTC4 | PTC3/<br>SCL1 | PTC2/<br>SDA1 | PTC1/<br>RxD2 | PTC0/<br>TxD2 |

#### Figure 6-4. Port C Pin Names

Port C is an 8-bit port which is shared among the SCI2 and IIC1 modules, and general-purpose I/O. When SCI2 or IIC1 modules are enabled, the pin direction will be controlled by the module or function. Port C has high current output drivers.

Port C pins are available as general-purpose I/O pins controlled by the port C data (PTCD), data direction (PTCDD), pullup enable (PTCPE), and slew rate control (PTCSE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

When the SCI2 module is enabled, PTC0 serves as the SCI2 module's transmit pin (TxD2) and PTC1 serves as the receive pin (RxD2). Refer to Chapter 11, "Serial Communications Interface (S08SCIV1)," for more information about using PTC0 and PTC1 as SCI pins

When the IIC module is enabled, PTC2 serves as the IIC modules's serial data input/output pin (SDA1) and PTC3 serves as the clock pin (SCL1). Refer to Chapter 13, "Inter-Integrated Circuit (S08IICV1)," for more information about using PTC2 and PTC3 as IIC pins.

Chapter 6 Parallel Input/Output

# 6.5 Stop Modes

Depending on the stop mode, I/O functions differently as the result of executing a STOP instruction. An explanation of I/O behavior for the various stop modes follows:

- When the MCU enters stop1 mode, all internal registers including general-purpose I/O control and data registers are powered down. All of the general-purpose I/O pins assume their reset state: output buffers and pullups turned off. Upon exit from stop1, all I/O must be initialized as if the MCU had been reset.

- When the MCU enters stop2 mode, the internal registers are powered down as in stop1 but the I/O pin states are latched and held. For example, a port pin that is an output driving low continues to function as an output driving low even though its associated data direction and output data registers are powered down internally. Upon exit from stop2, the pins continue to hold their states until a 1 is written to the PPDACK bit. To avoid discontinuity in the pin state following exit from stop2, the user must restore the port control and data registers to the values they held before entering stop2. These values can be stored in RAM before entering stop2 because the RAM is maintained during stop2.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.6 Parallel I/O Registers and Control Bits

This section provides information about all registers and control bits associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory" for the absolute address assignments for all parallel I/O registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

### 6.6.1 Port A Registers (PTAD, PTAPE, PTASE, and PTADD)

Port A includes eight pins shared between general-purpose I/O and the KBI module. Port A pins used as general-purpose I/O pins are controlled by the port A data (PTAD), data direction (PTADD), pullup enable (PTAPE), and slew rate control (PTASE) registers.

If the KBI takes control of a port A pin, the corresponding PTASE bit is ignored since the pin functions as an input. As long as PTADD is 0, the PTAPE controls the pullup enable for the KBI function. Reads of PTAD will return the logic value of the corresponding pin, provided PTADD is 0.

# Chapter 7 Internal Clock Generator (S08ICGV2)

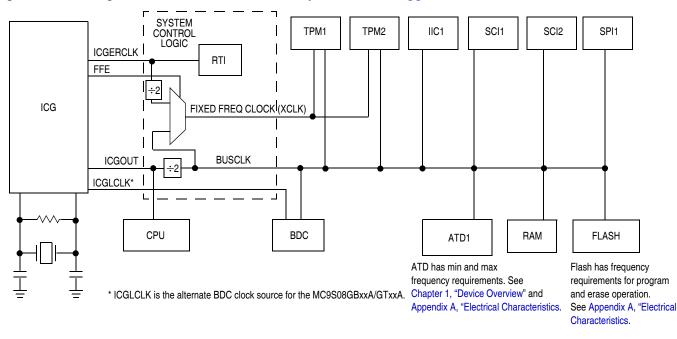

The MC9S08GBxxA/GTxxA microcontroller provides one internal clock generation (ICG) module to create the system bus frequency. All functions described in this section are available on the MC9S08GBxxA/GTxxA microcontroller. The EXTAL and XTAL pins share port G bits 2 and 1, respectively. Analog supply lines V<sub>DDA</sub> and V<sub>SSA</sub> are internally derived from the MCU's V<sub>DD</sub> and V<sub>SS</sub> pins. Electrical parametric data for the ICG may be found in Appendix A, "Electrical Characteristics."

Figure 7-1. System Clock Distribution Diagram

#### NOTE

Freescale Semiconductor recommends that flash location \$FFBE be reserved to store a nonvolatile version of ICGTRM. This will allow debugger and programmer vendors to perform a manual trim operation and store the resultant ICGTRM value for users to access at a later time.

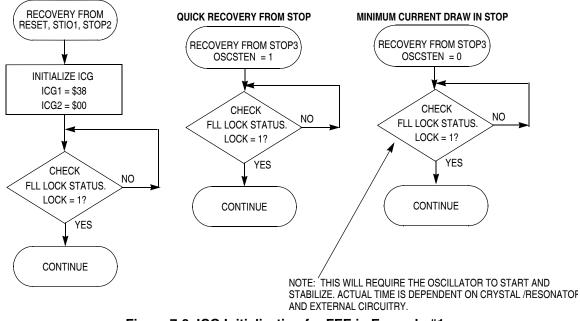

Figure 7-8 shows flow charts for three conditions requiring ICG initialization.

### 7.4.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz

In this example, the FLL will be used (in FEE mode) to multiply the external 4 MHz oscillator up to 40-MHz to achieve 20 MHz bus frequency.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

During reset initialization software, the clock scheme will be set to FLL engaged, external (FEE). So

Solving for N / R gives:

The values needed in each register to set up the desired operation are:

#### ICGC1 = \$78 (%01111000)

| Bit 7    | HGO     | 0  | Configures oscillator for low-power operation                            |

|----------|---------|----|--------------------------------------------------------------------------|

| Bit 6    | RANGE   | 1  | Configures oscillator for high-frequency range; FLL prescale factor is 1 |

| Bit 5    | REFS    | 1  | Requests an oscillator                                                   |

| Bits 4:3 | CLKS    | 11 | FLL engaged, external reference clock mode                               |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator in stop modes                                    |

| Bit 1    | LOCD    | 0  | Loss-of-clock detection enabled                                          |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                             |

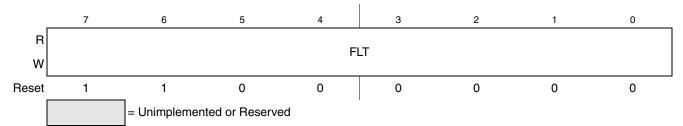

#### Figure 7-17. ICG Upper Filter Register (ICGFLTL)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

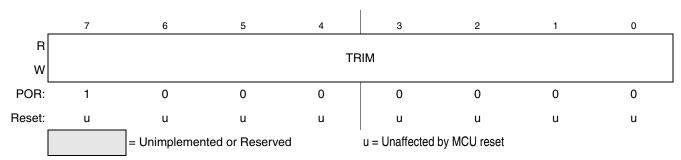

### 7.5.6 ICG Trim Register (ICGTRM)

Figure 7-18. ICG Trim Register (ICGTRM)

#### Table 7-12. ICGTRM Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>TRIM | <b>ICG Trim Setting</b> — The TRIM bits control the internal reference generator frequency. They allow a $\pm$ 25% adjustment of the nominal (POR) period. The bit's effect on period is binary weighted (i.e., bit 1 will adjust twice as much as changing bit 0). Increasing the binary value in TRIM will increase the period and decreasing the value will decrease the period. |

| Source                                                                                                          |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                    | Effect<br>on CCR |    |   |    |    |                 | ess<br>de                                           | ode                                | and                                 | Cycles <sup>1</sup>             |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----|---|----|----|-----------------|-----------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                            | Operation                                                              | Description<br>V                                                                                                                                                                                                                                                                                                                                                                                   |                  |    |   | z  | С  | Address<br>Mode | Opcode                                              | Operand                            | Bus Cy                              |                                 |

| ROR opr8a<br>RORA<br>RORX<br>ROR oprx8,X<br>ROR ,X<br>ROR oprx8,SP                                              | Rotate Right through<br>Carry                                          | b7 b0                                                                                                                                                                                                                                                                                                                                                                                              | ¢                | _  | _ | \$ | \$ | \$              | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66 | ff                                  | 5<br>1<br>5<br>4<br>6           |

| RSP                                                                                                             | Reset Stack Pointer                                                    | SP ← 0xFF<br>(High Byte Not Affected)                                                                                                                                                                                                                                                                                                                                                              | -                | -  | - | -  | -  | -               | INH                                                 | 9C                                 |                                     | 1                               |

| RTI                                                                                                             | Return from Interrupt                                                  | $\begin{array}{l} SP \leftarrow (SP) + 0x0001; \ Pull \ (CCR) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (A) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (X) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (PCH) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (PCL) \end{array}$                                                                                                                                 | \$               | \$ | ¢ | \$ | \$ | \$              | INH                                                 | 80                                 |                                     | 9                               |

| RTS                                                                                                             | Return from Subroutine                                                 | $SP \leftarrow SP + 0x0001$ ; Pull (PCH)<br>$SP \leftarrow SP + 0x0001$ ; Pull (PCL)                                                                                                                                                                                                                                                                                                               | -                | -  | - | -  | -  | -               | INH                                                 | 81                                 |                                     | 6                               |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry                                                    | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                                                                                                                                                                                     | \$               | _  | _ | \$ | \$ | \$              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| SEC                                                                                                             | Set Carry Bit                                                          | C ← 1                                                                                                                                                                                                                                                                                                                                                                                              | -                | -  | - | -  | -  | 1               | INH                                                 | 99                                 |                                     | 1                               |

| SEI                                                                                                             | Set Interrupt Mask Bit                                                 | l ← 1                                                                                                                                                                                                                                                                                                                                                                                              | -                | -  | 1 | -  | -  | -               | INH                                                 | 9B                                 |                                     | 1                               |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in<br>Memory                                         | M ← (A)                                                                                                                                                                                                                                                                                                                                                                                            | 0                | _  | _ | \$ | \$ | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        |                                    | hh II<br>ee ff<br>ff<br>ee ff       | 3<br>4<br>3<br>2<br>5<br>4      |

| STHX opr8a<br>STHX opr16a<br>STHX oprx8,SP                                                                      | Store H:X (Index Reg.)                                                 | (M:M + 0x0001) ← (H:X)                                                                                                                                                                                                                                                                                                                                                                             | 0                | -  | _ | \$ | \$ | _               | DIR<br>EXT<br>SP1                                   | 35<br>96<br>9EFF                   | hh ll                               | 4<br>5<br>5                     |

| STOP                                                                                                            | Enable Interrupts:<br>Stop Processing<br>Refer to MCU<br>Documentation | I bit $\leftarrow$ 0; Stop Processing                                                                                                                                                                                                                                                                                                                                                              | _                | -  | 0 | _  | -  | _               | INH                                                 | 8E                                 |                                     | 2+                              |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of<br>Index Register)<br>in Memory                 | M ← (X)                                                                                                                                                                                                                                                                                                                                                                                            | 0                | _  | _ | \$ | \$ | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        |                                    | hh II<br>ee ff<br>ff<br>ee ff       | 3443254                         |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx8,SP                  | Subtract                                                               | A ← (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                      | ¢                | _  | _ | \$ | \$ | ¢               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| swi                                                                                                             | Software Interrupt                                                     | $\begin{array}{l} PC \leftarrow (PC) + 0x0001\\ Push\ (PCL);\ SP \leftarrow (SP) - 0x0001\\ Push\ (PCH);\ SP \leftarrow (SP) - 0x0001\\ Push\ (X);\ SP \leftarrow (SP) - 0x0001\\ Push\ (A);\ SP \leftarrow (SP) - 0x0001\\ Push\ (CR);\ SP \leftarrow (SP) - 0x0001\\ I \leftarrow 1;\\ PCH \leftarrow Interrupt\ Vector\ High\ Byte\\ PCL \leftarrow Interrupt\ Vector\ Low\ Byte\\ \end{array}$ | _                | _  | 1 | _  | _  | _               | INH                                                 | 83                                 |                                     | 11                              |

| Table 8-2. HCS08 In | struction Set Summar | v (Sheet 6 of 7) |

|---------------------|----------------------|------------------|

|                     |                      |                  |

# Chapter 9 Keyboard Interrupt (S08KBIV1)

### 9.1 Introduction

The MC9S08GBxxA/GTxxA has one KBI module with eight keyboard interrupt inputs that share port A pins. See Chapter 2, "Pins and Connections" for more information about the logic and hardware aspects of these pins.

### 9.1.1 Port A and Keyboard Interrupt Pins

|          | PTA7/  | PTA6/  | PTA5/  | PTA4/  | PTA3/  | PTA2/  | PTA1/  | PTA0/  |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| MCU Pin: | KBI1P7 | KBI1P6 | KBI1P5 | KBI1P4 | KBI1P3 | KBI1P2 | KBI1P1 | KBI1P0 |

Figure 9-1. Port A Pin Names

The following paragraphs discuss controlling the keyboard interrupt pins.

Port A is an 8-bit port which is shared among the KBI keyboard interrupt inputs and general-purpose I/O. The eight KBIPEn control bits in the KBIPE register allow selection of any combination of port A pins to be assigned as KBI inputs. Any pins which are enabled as KBI inputs will be forced to act as inputs and the remaining port A pins are available as general-purpose I/O pins controlled by the port A data (PTAD), data direction (PTADD), and pullup enable (PTAPE) registers.

KBI inputs can be configured for edge-only sensitivity or edge-and-level sensitivity. Bits 3 through 0 of port A are falling-edge/low-level sensitive while bits 7 through 4 can be configured for rising-edge/high-level or for falling-edge/low-level sensitivity.

The eight PTAPEn control bits in the PTAPE register allow you to select whether an internal pullup device is enabled on each port A pin that is configured as an input. When any of bits 7 through 4 of port A are enabled as KBI inputs and are configured to detect rising edges/high levels, the pullup enable bits enable pulldown rather than pullup devices.

An enabled keyboard interrupt can be used to wake the MCU from wait or standby (stop3).

### 9.2 Features

The keyboard interrupt (KBI) module features include:

- Keyboard interrupts selectable on eight port pins:

- Four falling-edge/low-level sensitive

- Four falling-edge/low-level or rising-edge/high-level sensitive

- Choice of edge-only or edge-and-level sensitivity

- Common interrupt flag and interrupt enable control

- Capable of waking up the MCU from stop3 or wait mode

associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

### 10.5.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for each of the TPM can be independently selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input through the TPMxCH0 pin. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 10.7.1, "Timer x Status and Control Register (TPMxSC)," and Table 10-2 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from \$0000 through its terminal count and then continues with \$0000. The terminal count is FFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts upward from \$0000 through its terminal count and then counts downward to \$0000 where it returns to up-counting. Both \$0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from \$0000 through \$FFFF and overflows to \$0000 on the next counting clock. TOF becomes set at the transition from \$FFFF to \$0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to \$0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The \$0000 count value corresponds to the center of a period.)

Timer/PWM (TPM)

| Table 10-2 | ТРМ | Clock | Source | Selection |

|------------|-----|-------|--------|-----------|

|------------|-----|-------|--------|-----------|

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input           |

|-------------|-----------------------------------------------|

| 0:0         | No clock selected (TPM disabled)              |

| 0:1         | Bus rate clock (BUSCLK)                       |

| 1:0         | Fixed system clock (XCLK)                     |

| 1:1         | External source (TPMx Ext Clk) <sup>1,2</sup> |

1. The maximum frequency that is allowed as an external clock is one-fourth of the bus frequency.

2. When the TPMxCH0 pin is selected as the TPM clock source, the corresponding ELS0B:ELS0A control bits should be set to 0:0 so channel 0 does not try to use the same pin for a conflicting function.

| PS2:PS1:PS0 | TPM Clock Source Divided-By |

|-------------|-----------------------------|

| 0:0:0       | 1                           |

| 0:0:1       | 2                           |

| 0:1:0       | 4                           |

| 0:1:1       | 8                           |

| 1:0:0       | 16                          |

| 1:0:1       | 32                          |

| 1:1:0       | 64                          |

| 1:1:1       | 128                         |

#### Table 10-3. Prescale Divisor Selection

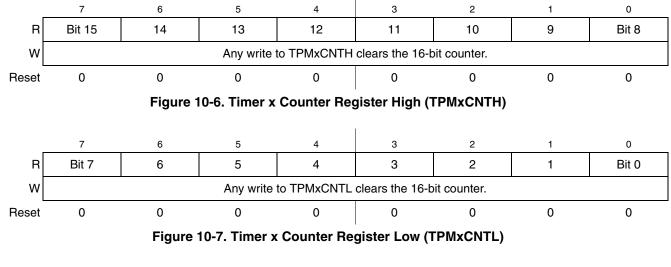

#### 10.7.2 Timer x Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This allows coherent 16-bit reads in either order. The coherency mechanism is automatically restarted by an MCU reset, a write of any value to TPMxCNTH or TPMxCNTL, or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers.

Timer/PWM (TPM)

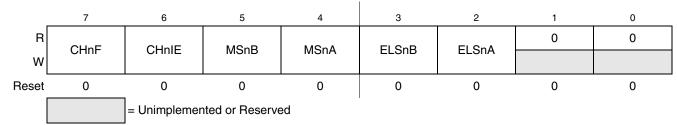

### **10.7.4** Timer x Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

#### Figure 10-10. Timer x Channel n Status and Control Register (TPMxCnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | <ul> <li>Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.</li> <li>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMxCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.</li> <li>No input capture or output compare event occurred on channel n</li> </ul> |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>0 Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 10-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 10-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 10-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin. This is also the setting required for channel 0 when the TPMxCH0 pin is used as an external clock input.                                                                                                                                                                                                                                                                                      |

#### Table 10-4. TPMxCnSC Register Field Descriptions

Chapter 11 Serial Communications Interface (S08SCIV1)

Note: Not all pins are bonded out in all packages. See Table 2-2 for complete details.

Figure 11-1. Block Diagram Highlighting the SCI Modules

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSTR  | Master/Slave Mode Select         0       SPI module configured as a slave SPI device         1       SPI module configured as a master SPI device                                                                                                                                                                                                                                                             |

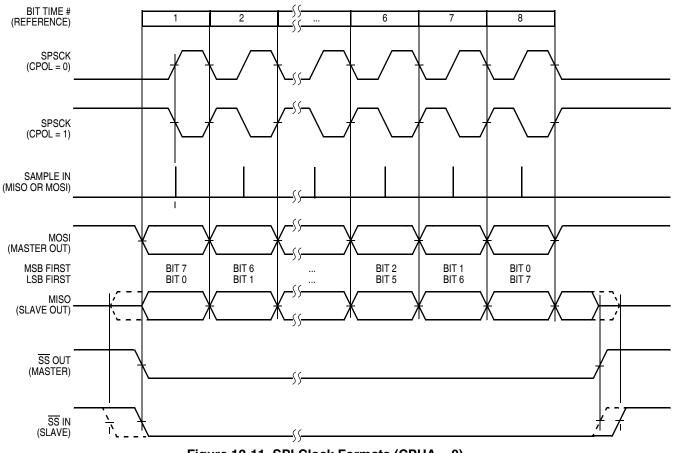

| 3<br>CPOL  | <ul> <li>Clock Polarity — This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 12.5.1, "SPI Clock Formats" for more details.</li> <li>0 Active-high SPI clock (idles low)</li> <li>1 Active-low SPI clock (idles high)</li> </ul>                                                                                             |

| 2<br>CPHA  | <ul> <li>Clock Phase — This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 12.5.1, "SPI Clock Formats" for more details.</li> <li>0 First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer</li> <li>1 First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer</li> </ul> |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the SS pin as shown in Table 12-2.                                                                                                                                                                                  |

| 0<br>LSBFE | <ul> <li>LSB First (Shifter Direction)</li> <li>0 SPI serial data transfers start with most significant bit</li> <li>1 SPI serial data transfers start with least significant bit</li> </ul>                                                                                                                                                                                                                  |

Table 12-2. SS Pin Function

| MODFEN | SSOE | Master Mode                   | Slave Mode         |

|--------|------|-------------------------------|--------------------|

| 0      | 0    | General-purpose I/O (not SPI) | Slave select input |

| 0      | 1    | General-purpose I/O (not SPI) | Slave select input |

| 1      | 0    | SS input for mode fault       | Slave select input |

| 1      | 1    | Automatic SS output           | Slave select input |

#### NOTE

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

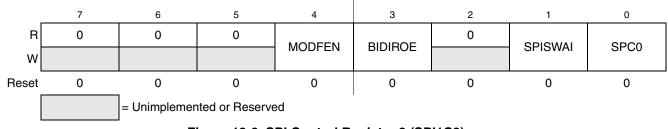

### 12.4.2 SPI Control Register 2 (SPI1C2)

This read/write register is used to control optional features of the SPI system. Bits 7, 6, 5, and 2 are not implemented and always read 0.

#### Serial Peripheral Interface (S08SPIV3)

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

Inter-Integrated Circuit (S08IICV1)

#### 13.4.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 13-8, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

#### 13.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 13-8).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

#### 13.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 13-8. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

Inter-Integrated Circuit (S08IICV1)

# 13.7 Initialization/Application Information

| -  | Module Initialization (Slave)                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Write: IICA                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2. | <ul> <li>to set the slave address</li> <li>Write: IICC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |

| ۷. | <ul> <li>to enable IIC and interrupts</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    |

| 3. | Initialize RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                                                                                                                                                                                                                                                                                                                                                |

| 4. | Initialize RAM variables used to achieve the routine shown in Figure 13-11                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | Module Initialization (Master)                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1. | Write: IICF                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ~  | <ul> <li>to set the IIC baud rate (example provided in this chapter)</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

| 2. | Write: IICC  — to enable IIC and interrupts                                                                                                                                                                                                                                                                                                                                                                                         |

| 3. | Initialize RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                                                                                                                                                                                                                                                                                                                                                |

| 4. | Initialize RAM variables used to achieve the routine shown in Figure 13-11                                                                                                                                                                                                                                                                                                                                                          |

| 5. | Write: IICC                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _  | — to enable TX                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6. | Write: IICC                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7. | <ul> <li>to enable MST (master mode)</li> <li>Write: IICD</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

| 1. | <ul> <li>with the address of the target slave. (The LSB of this byte will determine whether the communication is</li> </ul>                                                                                                                                                                                                                                                                                                         |

|    | master receive or transmit.)                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | Module Use                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | The routine shown in Figure 13-11 can handle both master and slave IIC operations. For slave operation, an                                                                                                                                                                                                                                                                                                                          |

|    | incoming IIC message that contains the proper address will begin IIC communication. For master operation, communication must be initiated by writing to the IICD register.                                                                                                                                                                                                                                                          |

|    | communication must be initiated by writing to the nob register.                                                                                                                                                                                                                                                                                                                                                                     |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | Register Model                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | IICA ADDR 0                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | IICA ADDR 0<br>Address to which the module will respond when addressed as a slave (in slave mode)                                                                                                                                                                                                                                                                                                                                   |

|    | IICA     ADDR     0       Address to which the module will respond when addressed as a slave (in slave mode)     IICF     MULT                                                                                                                                                                                                                                                                                                      |

|    | IICA ADDR 0<br>Address to which the module will respond when addressed as a slave (in slave mode)                                                                                                                                                                                                                                                                                                                                   |

|    | IICA     ADDR     0       Address to which the module will respond when addressed as a slave (in slave mode)     IICF     MULT                                                                                                                                                                                                                                                                                                      |

|    | IICA       ADDR       0         Address to which the module will respond when addressed as a slave (in slave mode)       IICF       MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))       IICC       IICEN       IICIE       MST       TX       TXAK       RSTA       0       0                                                                                                                              |

|    | IICA       ADDR       0         Address to which the module will respond when addressed as a slave (in slave mode)       IICF       MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))       IICC       IICEN       IICIE       MST       TX       TXAK       RSTA       0       0         Module configuration       IICE       MST       TX       TXAK       RSTA       0       0                            |

|    | IICA       ADDR       0         Address to which the module will respond when addressed as a slave (in slave mode)       IICF       MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))       IICC       IICEN       IICIE       MST       TX       TXAK       RSTA       0       0         Module configuration       IICS       TCF       IAAS       BUSY       ARBL       0       SRW       IICIF       RXAK |

|    | IICA       ADDR       0         Address to which the module will respond when addressed as a slave (in slave mode)       IICF         IICF       MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))       IICC         IICE       IICIE       MST         Module configuration       IICS         TCF       IAAS       BUSY         ARBL       0       SRW         Module status flags       IICIF             |

|    | IICA       ADDR       0         Address to which the module will respond when addressed as a slave (in slave mode)       IICF       MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))       IICC       IICEN       IICIE       MST       TX       TXAK       RSTA       0       0         Module configuration       IICS       TCF       IAAS       BUSY       ARBL       0       SRW       IICIF       RXAK |

#### Figure 13-10. IIC Module Quick Start

#### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

### 15.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

#### **Development Support**

the host must perform ((8 - CNT) - 1) dummy reads of the FIFO to advance it to the first significant entry in the FIFO.

In most trigger modes, the information stored in the FIFO consists of 16-bit change-of-flow addresses. In these cases, read DBGFH then DBGFL to get one coherent word of information out of the FIFO. Reading DBGFL (the low-order byte of the FIFO data port) causes the FIFO to shift so the next word of information is available at the FIFO data port. In the event-only trigger modes (see Section 15.3.5, "Trigger Modes"), 8-bit data information is stored into the FIFO. In these cases, the high-order half of the FIFO (DBGFH) is not used and data is read out of the FIFO by simply reading DBGFL. Each time DBGFL is read, the FIFO is shifted so the next data value is available through the FIFO data port at DBGFL.

In trigger modes where the FIFO is storing change-of-flow addresses, there is a delay between CPU addresses and the input side of the FIFO. Because of this delay, if the trigger event itself is a change-of-flow address or a change-of-flow address appears during the next two bus cycles after a trigger event starts the FIFO, it will not be saved into the FIFO. In the case of an end-trace, if the trigger event is a change-of-flow, it will be saved as the last change-of-flow entry for that debug run.

The FIFO can also be used to generate a profile of executed instruction addresses when the debugger is not armed. When ARM = 0, reading DBGFL causes the address of the most-recently fetched opcode to be saved in the FIFO. To use the profiling feature, a host debugger would read addresses out of the FIFO by reading DBGFH then DBGFL at regular periodic intervals. The first eight values would be discarded because they correspond to the eight DBGFL reads needed to initially fill the FIFO. Additional periodic reads of DBGFH and DBGFL return delayed information about executed instructions so the host debugger can develop a profile of executed instruction addresses.

#### 15.3.3 Change-of-Flow Information