# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500mc                                                       |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                                       |

| Speed                           | 667MHz                                                               |

| Co-Processors/DSP               | -                                                                    |

| RAM Controllers                 | DDR3, DDR3L                                                          |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (5)                                                  |

| SATA                            | SATA 3Gbps (2)                                                       |

| USB                             | USB 2.0 + PHY (2)                                                    |

| Voltage - I/O                   | 1.0V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                    |

| Package / Case                  | -                                                                    |

| Supplier Device Package         | 780-FCPBGA (23x23)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/p2040nsn1flb |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 7           |              |             |                         |              |                          |              |                          |                                    |                          |                                     |                          |                                     |                          |

|----|-------------|--------------|-------------|-------------------------|--------------|--------------------------|--------------|--------------------------|------------------------------------|--------------------------|-------------------------------------|--------------------------|-------------------------------------|--------------------------|

| R  | LCS<br>[3]  | GND<br>[097] | LA<br>[21]  | BV <sub>DD</sub><br>[1] | LCS<br>[0]   | LA<br>[24]               | LAD<br>[11]  | GND<br>[096]             | V <sub>DD</sub> _<br>CA_PL<br>[30] | GND<br>[095]             | V <sub>DD</sub> _<br>CA_PL<br>[29]  | GND<br>[094]             | V <sub>DD</sub><br>CA_PL<br>[28]    | GND<br>[093]             |

| Т  | LA<br>[22]  | LA<br>[27]   | LA<br>[26]  | LAD<br>[12]             | LA<br>[25]   | LAD<br>[14]              | LAD<br>[15]  | GND<br>[087]             | V <sub>DD</sub><br>CA_PL<br>[24]   | GND<br>[086]             | V <sub>DD</sub><br>CA_PL<br>[23]    | GND<br>[085]             | V <sub>DD</sub><br>CA_PL<br>[22]    | GND<br>[084]             |

| U  | LA<br>[23]  | LAD<br>[13]  | LA<br>[29]  | LCS2                    | LA<br>[28]   | TEMP_<br>CATHODE         | GND<br>[080] | GND<br>[079]             | V <sub>DD</sub><br>CA_PL<br>[18]   | GND<br>[078]             | V <sub>DD</sub><br>CA_PL<br>[17]    | GND<br>[077]             | V <sub>DD</sub><br>CA_PL<br>[16]    | GND<br>[076]             |

| V  | LA<br>[30]  | GND<br>[071] | LA<br>[31]  | GND<br>[070]            |              | GND<br>[069]             | AVDD_<br>CC1 | GND<br>[068]             | V <sub>DD</sub><br>CA_PL<br>[13],  | GND<br>[067]             | V <sub>DD</sub> _<br>CA_PL<br>[12], | GND<br>[066]             | V <sub>DD</sub> _<br>CA_PL<br>[11], | GND<br>[065]             |

| W  | NC<br>[05]  | GND<br>[058] | NC<br>[04]  | NC<br>[03]              | GND<br>[057] | AVDD_<br>DDR             | MVREF        | GND<br>[056]             | V <sub>DD</sub><br>CA_PL<br>[09],  | GND<br>[055]             | V <sub>DD</sub> _<br>CA_PL<br>[08], | GND<br>[054]             | V <sub>DD</sub><br>CA_PL<br>[07],   | GND<br>[053]             |

| Y  | MDQ<br>[04] | MDM<br>[0]   | MDQ<br>[05] | MDQ<br>[00]             | MDQ<br>[01]  | GND<br>[048]             | GND<br>[047] | GND<br>[046]             | V <sub>DD</sub> _<br>CA_PL<br>[05] | GND<br>[045]             | V <sub>DD</sub> _<br>CA_PL<br>[04]  | GND<br>[044]             | V <sub>DD</sub><br>CA_PL<br>[03]    | GND<br>[043]             |

| AA | MDQS<br>[0] | MDQS<br>[0]  | MDQ<br>[06] | MDQ<br>[07]             | GND<br>[038] | MDQ<br>[12]              | GND<br>[037] | GV <sub>DD</sub><br>[17] | GV <sub>DD</sub><br>[16]           | GV <sub>DD</sub><br>[15] | GV <sub>DD</sub><br>[14]            | GV <sub>DD</sub><br>[13] | GV <sub>DD</sub><br>[12]            | GV <sub>DD</sub><br>[11] |

| AB | MDQ<br>[02] | GND<br>[032] | MDQ<br>[03] | MDQ<br>[13]             | MDQ<br>[08   | MDQ<br>[09]              | MCKE<br>[1]  | MCKE<br>[0]              | GND<br>[031]                       | GND<br>[030]             | GND<br>[029]                        | GND<br>[028]             | GV <sub>DD</sub><br>[09]            | GV <sub>DD</sub><br>[08] |

| AC | MDQ<br>[24] | MDQ<br>[25]  | MDQ<br>[28] | MDQ<br>[29]             | GND<br>[025] | MDQ<br>[14]              | MDM<br>[1]   | MBA<br>[2]               | MA<br>[12]                         | MA<br>[07]               | MA<br>[06]                          | MA<br>[02]               | GV <sub>DD</sub><br>[07]            | GV <sub>DD</sub><br>[06] |

| AD | MDQS<br>[3] | MDQS<br>[3]  | MDQS<br>[1] | MDQS<br>[1]             | MDM<br>[3]   | MDQ<br>[15]              | MDQ<br>[21]  | MDM<br>[2]               | MDQS<br>[2]                        | MDQ<br>[22]              | MDQ<br>[18]                         | GND<br>[021]             | MCK<br>[1]                          | MCK<br>[0]               |

| AE | MDQ<br>[30] | GND<br>[019] | MDQ<br>[31] | MDQ<br>[10]             | GND<br>[018] | MDQ<br>[11]              | MDQ<br>[20]  | GND<br>[017]             | MDQS<br>[2]                        | MDQ<br>[23]              | GND<br>[016]                        | MDIC<br>[1]              | MCK<br>[1]                          | <u>МСК</u><br>[0]        |

| AF | MDQ<br>[26] | MDQ<br>[27]  | MECC<br>[1] | MDM<br>[8]              | MECC<br>[7]  | GV <sub>DD</sub><br>[05] | MDQ<br>[16]  | MDQ<br>[17]              | GV <sub>DD</sub><br>[04]           | MA<br>[08]               | MDQ<br>[19]                         | MA<br>[01]               | GND<br>[010]                        | GND<br>[009]             |

| AG | MECC<br>[4] | MECC<br>[5]  | MDQS<br>[8] | GND<br>[008]            | MECC<br>[2]  | MCKE<br>[3]              | GND<br>[007] | MA<br>[14]               | MA<br>[11]                         | GND<br>[006]             | MA<br>[04]                          | MDIC<br>[0]              | MCK<br>[2]                          | MCK<br>[3]               |

| AH |             | MECC<br>[0]  | MDQS<br>[8] | MECC<br>[6]             | MECC<br>[5]  | MCKE<br>[2]              | MA<br>[15]   | MAPAR<br>_ERR            | MA<br>[09]                         | MA<br>[05]               | MA<br>[03]                          | GND<br>[002]             | MCK<br>[2]                          | MCK<br>[3]               |

|    | 1           | 2            | 3           | 4                       | 5            | 6                        | 7            | 8                        | 9                                  | 10                       | 11                                  | 12                       | 13                                  | 14                       |

|    |             |              |             | Figure                  | 5 780        |                          |              | Diagra                   | n (Dota                            |                          | $\sim$                              |                          |                                     |                          |

Figure 5. 780 BGA Ball Map Diagram (Detail View C)

|                                    |                 |                                    |                |                                   |                                    |                                    |               |                          |                |               |                         |               | 7                  | -  |

|------------------------------------|-----------------|------------------------------------|----------------|-----------------------------------|------------------------------------|------------------------------------|---------------|--------------------------|----------------|---------------|-------------------------|---------------|--------------------|----|

| V <sub>DD_</sub><br>CA_PL<br>[27]  | GND<br>[092]    | V <sub>DD</sub> _<br>CA_PL<br>[26] | GND<br>[091]   | V <sub>DD_</sub><br>CA_PL<br>[25] | OV <sub>DD</sub><br>[4]            | GND<br>[090]                       | ASLEEP        | UART1_<br>SOUT           | GND<br>[089]   | UART1_<br>CTS | UART1_<br>SIN           | GND<br>[088]  | SYSCLK             | R  |

| V <sub>DD</sub><br>CA_PL<br>[21]   | GND<br>[083]    | V <sub>DD</sub> _<br>CA_PL<br>[20] | GND<br>[082]   | V <sub>DD</sub><br>CA_PL<br>[19]  | OV <sub>DD</sub><br>[3]            | GND<br>[081]                       | PORESE        | THRESET                  | TMP_<br>DETECT | CKSTP<br>OUT  | OV <sub>DD</sub><br>[2] | CLK_<br>OUT   | TEST_<br>SEL       | Т  |

| V <sub>DD_</sub><br>CA_PL<br>[15]  | VDD_CB<br>[11]  | GND<br>[075]                       | VDD_CB<br>[10] | GND<br>[074]                      | V <sub>DD</sub> _<br>CA_PL<br>[14] | POVDD                              | GND<br>[073]  | IO_<br>VSEL1             | EVT<br>[4]     | GND<br>[072]  | <b>EVT</b><br>[2]       | EVT<br>[1]    | RESET_<br>REQ      | U  |

| V <sub>DD_</sub><br>CA_PL<br>[10]  | GND<br>[064]    | GND<br>[063]                       | VDD_CB<br>[09] | GND<br>[062]                      | VDD_CB<br>[08]                     | GND<br>[061]                       | AVDD_<br>PLAT | GND<br>[060]             | IIC4_<br>SDA   | IRQ<br>[04]   | EVT<br>[0]              | GND<br>[059]  | SCAN_<br>MODE      | V  |

| V <sub>DD</sub> _<br>CA_PL<br>[06] | VDD_CB<br>[07]  | GND<br>[052]                       | VDD_CB<br>[06] | GND<br>[051]                      | VDD_CB<br>[05]                     | GND<br>[050]                       | AVDD_<br>CC2  | GND<br>[049]             | EVT<br>[3]     | IIC2_<br>SCL  | OV <sub>DD</sub><br>[1] | TMS           | TDI                | W  |

| V <sub>DD_</sub><br>CA_PL<br>[02]  | GND<br>[042]    | GND<br>[041]                       | VDD_CB<br>[04] | GND<br>[040]                      | VDD_CB<br>[03]                     | IO_<br>VSEL_<br>[4]                | GND<br>[039]  | IO_<br>VSEL_<br>[3]      |                | IIRQ_<br>[00] | IIRQ_<br>[06]           | TRST          | тск                | Y  |

| GV <sub>DD</sub><br>[10]           | SENSE<br>GND_CB | GND<br>[036]                       | VDD_CB<br>[02] | GND<br>[035]                      | VDD_CB<br>[01]                     | V <sub>DD</sub> _<br>CA_PL<br>[01] | IIRQ_<br>[05] | IIRQ_<br>[07]            | GND<br>[034]   | IIC2_<br>SDA  | IIRQ_<br>[03]           | GND<br>[033]  | TDO                | AA |

| GND<br>[027]                       | SENSE<br>VDD_CB | RSRV                               | RSRV           | RSRV                              | RSRV                               | IO_<br>VSEL<br>[2]                 | GND<br>[026]  | IIC3_<br>SCL             | IIRQ_<br>[10]  | IIRQ_<br>[02] | IIC3_<br>SDA            | IIRQ_<br>[0]  | IO_<br>VSEL<br>[0] | AB |

| MBA<br>[1]                         | MBA<br>[0]      | GND<br>[024]                       | MCS<br>[0]     | MODT<br>[0]                       | GND<br>[023]                       | MCS1                               | IIRQ_<br>[08] | IIC4_<br>SCL             | IIRQ_<br>[11]  | IIC1_<br>SCL  | GND<br>[022]            | IIRQ_<br>[09] | IIC1_<br>SDA       | AC |

| GND<br>[020]                       | MDQ<br>[33]     | MDQS<br>[4]                        | MDQS<br>[4]    | MDQ<br>[35]                       | MDQ<br>[53]                        | MDQ<br>[49]                        | MODT<br>[1]   | MDQ<br>[54]              | MDQ<br>[51]    | MDQ<br>[58]   | MDQ<br>[59]             | MDQ<br>[62]   | MDQ<br>[63]        | AD |

| GND<br>[015]                       | MDQ<br>[32]     | MDM<br>[4]                         | GND<br>[014]   | MDQ<br>[34]                       | MDQ<br>[52]                        | GND<br>[013]                       | MDQS<br>[6]   | MDQS<br>[6]              | GND<br>[012]   | MDQ<br>[55]   | MDM<br>[7]              | GND<br>[011]  | MDQS<br>[7]        | AE |

| MDQ<br>[36]                        | MDQ<br>[37]     | GV <sub>DD</sub><br>[03]           | MDQ<br>[38]    | MDQ<br>[39]                       | GV <sub>DD</sub><br>[02]           | MDQ<br>[48]                        | MDM<br>[6]    | GV <sub>DD</sub><br>[01] | MDQ<br>[50]    | MDQ<br>[61]   | MDQ<br>[56]             | MDQ<br>[57]   | MDQS<br>[7]        | AF |

| MAPAR<br>_OUT                      | MA<br>[00]      | MCS<br>[2]                         | MODT<br>[2]    | GND<br>[005]                      | MCS<br>[3]                         | MDQ<br>[44]                        | GND<br>[004]  | MDQ<br>[41]              | MDQS<br>[5]    | GND<br>[003]  | MDQ<br>[47]             | MDQ<br>[43]   | MDQ<br>[60]        | AG |

| GND<br>[001]                       | MA<br>[10]      | MRAS                               | MWE            | MCAS                              | MA<br>[13]                         | MODT<br>[3]                        | MDQ<br>[45]   | MDQ<br>[40]              | MDQS<br>[5]    | MDM<br>[5]    | MDQ<br>[46]             | MDQ<br>[42]   |                    | AH |

| 15                                 | 16              | 17                                 | 18             | 19                                | 20                                 | 21                                 | 22            | 23                       | 24             | 25            | 26                      | 27            | 28                 |    |

|                                    |                 |                                    | Fig            | ure 6.                            | 780 BG/                            | A Ball I                           | Map Dia       | gram (E                  | Detail V       | iew D)        |                         |               |                    |    |

# Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply         | Note |

|--------|--------------------|-----------------------|-------------|-------------------------|------|

| MDQ29  | Data               | AC4                   | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ30  | Data               | AE1                   | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ31  | Data               | AE3                   | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ32  | Data               | AE16                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ33  | Data               | AD16                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ34  | Data               | AE19                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ35  | Data               | AD19                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ36  | Data               | AF15                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ37  | Data               | AF16                  | I/O         | $GV_{DD}$               | _    |

| MDQ38  | Data               | AF18                  | I/O         | $\text{GV}_{\text{DD}}$ | —    |

| MDQ39  | Data               | AF19                  | I/O         | $GV_{DD}$               | _    |

| MDQ40  | Data               | AH23                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ41  | Data               | AG23                  | I/O         | $GV_{DD}$               | _    |

| MDQ42  | Data               | AH27                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ43  | Data               | AG27                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ44  | Data               | AG21                  | I/O         | $GV_{DD}$               | _    |

| MDQ45  | Data               | AH22                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ46  | Data               | AH26                  | I/O         | $GV_{DD}$               | _    |

| MDQ47  | Data               | AG26                  | I/O         | $GV_{DD}$               | _    |

| MDQ48  | Data               | AF21                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ49  | Data               | AD21                  | I/O         | $GV_{DD}$               | _    |

| MDQ50  | Data               | AF24                  | I/O         | $\text{GV}_{\text{DD}}$ | —    |

| MDQ51  | Data               | AD24                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ52  | Data               | AE20                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ53  | Data               | AD20                  | I/O         | $GV_{DD}$               | _    |

| MDQ54  | Data               | AD23                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ55  | Data               | AE25                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ56  | Data               | AF26                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ57  | Data               | AF27                  | I/O         | $\text{GV}_{\text{DD}}$ | _    |

| MDQ58  | Data               | AD25                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ59  | Data               | AD26                  | I/O         | GV <sub>DD</sub>        | —    |

| MDQ60  | Data               | AG28                  | I/O         | GV <sub>DD</sub>        | _    |

| MDQ61  | Data               | AF25                  | I/O         | GV <sub>DD</sub>        | —    |

| MDQ62  | Data               | AD27                  | I/O         | GV <sub>DD</sub>        | _    |

| Table 1. Pin Lis | t by Bus | (continued) |

|------------------|----------|-------------|

|------------------|----------|-------------|

| Signal                   | Signal Description                                 | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note  |

|--------------------------|----------------------------------------------------|-----------------------|-------------|------------------|-------|

| LA19                     | Address                                            | P3                    | I/O         | BV <sub>DD</sub> | 31    |

| LA20                     | Address                                            | P2                    | I/O         | $BV_DD$          | 31    |

| LA21                     | Address                                            | R3                    | I/O         | BV <sub>DD</sub> | 31    |

| LA22                     | Address                                            | T1                    | I/O         | BV <sub>DD</sub> | 31    |

| LA23                     | Address                                            | U1                    | I/O         | BV <sub>DD</sub> | 3     |

| LA24                     | Address                                            | R6                    | I/O         | BV <sub>DD</sub> | 3     |

| LA25                     | Address                                            | T5                    | I/O         | $BV_DD$          | 31    |

| LA26                     | Address                                            | Т3                    | I/O         | $BV_DD$          | 3, 29 |

| LA27                     | Address                                            | T2                    | 0           | $BV_DD$          | —     |

| LA28                     | Address                                            | U5                    | I/O         | $BV_DD$          | —     |

| LA29                     | Address                                            | U3                    | I/O         | $BV_DD$          | —     |

| LA30                     | Address                                            | V1                    | I/O         | $BV_DD$          | —     |

| LA31                     | Address                                            | V3                    | I/O         | $BV_DD$          | —     |

| LDP0                     | Data Parity                                        | L3                    | I/O         | BV <sub>DD</sub> | —     |

| LDP1                     | Data Parity                                        | M1                    | I/O         | BV <sub>DD</sub> | _     |

| LCSO                     | Chip Selects                                       | R5                    | 0           | $BV_DD$          | 5     |

| LCS1                     | Chip Selects                                       | P7                    | 0           | $BV_DD$          | 5     |

| LCS2                     | Chip Selects                                       | U4                    | 0           | BV <sub>DD</sub> | 5     |

| LCS3                     | Chip Selects                                       | R1                    | 0           | BV <sub>DD</sub> | 5     |

| LWEO                     | Write Enable                                       | M6                    | 0           | BV <sub>DD</sub> | —     |

| LWE1                     | Write Enable                                       | M3                    | 0           | BV <sub>DD</sub> |       |

| LBCTL                    | Buffer Control                                     | P1                    | 0           | $BV_DD$          | —     |

| LALE                     | Address Latch Enable                               | N6                    | I/O         | BV <sub>DD</sub> | —     |

| LGPL0/LFCLE              | UPM General Purpose Line 0/<br>LFCLE—FCM           | L5                    | 0           | $BV_DD$          | 3, 4  |

| LGPL1/LFALE              | UPM General Purpose Line 1/<br>LFALE—FCM           | K1                    | 0           | $BV_DD$          | 3, 4  |

| LGPL2/LOE/LFRE           | UPM General Purpose Line 2/<br>LOE_B—Output Enable | L6                    | 0           | BV <sub>DD</sub> | 3, 4  |

| LGPL3/LFWP               | UPM General Purpose Line 3/<br>LFWP_B—FCM          | J3                    | 0           | $BV_DD$          | 3, 4  |

| LGPL4/LGTA/LUPWAIT/LPBSE | UPM General Purpose Line 4/<br>LGTA_B—FCM          | L2                    | I/O         | $BV_DD$          | 36    |

| LGPL5                    | UPM General Purpose Line 5 / Amux                  | J1                    | 0           | BV <sub>DD</sub> | 3, 4  |

| LCLK0                    | Local Bus Clock                                    | M4                    | 0           | BV <sub>DD</sub> | _     |

| LCLK1                    | Local Bus Clock                                    | N7                    | 0           | BV <sub>DD</sub> | _     |

# Table 1. Pin List by Bus (continued)

| Signal                                                           | Signal Description           | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note   |

|------------------------------------------------------------------|------------------------------|-----------------------|-------------|------------------|--------|

| EVT8/GPIO29/IRQ11                                                | Event 8                      | AC24                  | I/O         | $OV_{DD}$        | _      |

| EVT9/IRQ_OUT                                                     | Event 9                      | Y24                   | I/O         | $OV_{DD}$        | —      |

| M1DVAL/LB_DVAL/IIC3_SCL/GPIO16/<br>SDHC_CD/DMA1_DACK0            | Debug Data Valid             | AB23                  | 0           | $OV_{DD}$        | —      |

| MSRCID0/LB_SRCID0/IIC3_SDA/GPIO17/<br>DMA_DDONE0/SDHC_WP         | Debug Source ID 0            | AB26                  | 0           | $OV_{DD}$        | 4, 31  |

| MSRCID1/LB_MSRCID1/EVT5/IIC4_SCL/<br>LB_SRCID1/GPIO18/DMA1_DREQ0 | Debug Source ID 1            | AC23                  | 0           | $OV_{DD}$        | —      |

| MSRCID2/LB_SRCID2/EVT6/IIC4_SDA/<br>LB_SRCID2/GPIO19             | Debug Source ID 2            | V24                   | 0           | $OV_{DD}$        | _      |

| CLK_OUT                                                          | Clock Out                    | T27                   | 0           | $OV_{DD}$        | 6      |

|                                                                  | Clock                        |                       | I           |                  | 1      |

| RTC                                                              | Real Time Clock              | P28                   | I           | OV <sub>DD</sub> |        |

| SYSCLK                                                           | System Clock                 | R28                   | I           | OV <sub>DD</sub> | _      |

|                                                                  | JTAG                         | -                     | 11          |                  | 1      |

| ТСК                                                              | Test Clock                   | Y28                   | I           | OV <sub>DD</sub> | _      |

| TDI                                                              | Test Data In                 | W28                   | I           | OV <sub>DD</sub> | 7      |

| TDO                                                              | Test Data Out                | AA28                  | 0           | OV <sub>DD</sub> | 6      |

| TMS                                                              | Test Mode Select             | W27                   | I           | $OV_{DD}$        | 7      |

| TRST                                                             | Test Reset                   | Y27                   | I           | $OV_DD$          | 7      |

|                                                                  | DFT                          |                       |             |                  | 1      |

| SCAN_MODE                                                        | Scan Mode                    | V28                   | Ι           | OV <sub>DD</sub> | 35     |

| TEST_SEL                                                         | Test Mode Select             | T28                   | I           | OV <sub>DD</sub> | 12, 26 |

|                                                                  | Power Management             |                       | 11          |                  |        |

| ASLEEP                                                           | Asleep                       | R22                   | 0           | OV <sub>DD</sub> | 31     |

|                                                                  | Input /Output Voltage Select |                       |             |                  |        |

| IO_VSEL0                                                         | I/O Voltage Select           | AB28                  | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL1                                                         | I/O Voltage Select           | U23                   | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL2                                                         | I/O Voltage Select           | AB21                  | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL3                                                         | I/O Voltage Select           | Y23                   | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL4                                                         | I/O Voltage Select           | Y21                   | I           | OV <sub>DD</sub> | 27     |

|                                                                  | Power and Ground Signals     |                       | 1           |                  | 1      |

| GND168                                                           | Ground                       | A23                   |             | _                | _      |

| GND167                                                           | Ground                       | B23                   |             | _                |        |

# Table 1. Pin List by Bus (continued)

| Signal      | Signal Description       | Package<br>Pin Number | Pin<br>Type | Power<br>Supply         | Note |

|-------------|--------------------------|-----------------------|-------------|-------------------------|------|

| USB1_AGND01 | USB1 PHY Transceiver GND | M28                   | —           | _                       | -    |

| USB2_AGND06 | USB2 PHY Transceiver GND | J22                   | _           | _                       | _    |

| USB2_AGND05 | USB2 PHY Transceiver GND | J24                   | —           | _                       | -    |

| USB2_AGND04 | USB2 PHY Transceiver GND | J26                   | —           | —                       | -    |

| USB2_AGND03 | USB2 PHY Transceiver GND | K25                   | —           | —                       | -    |

| USB2_AGND02 | USB2 PHY Transceiver GND | L25                   | —           | —                       | -    |

| USB2_AGND01 | USB2 PHY Transceiver GND | M26                   | —           | —                       | -    |

| OVDD06      | General I/O Supply       | N20                   | —           | $OV_{DD}$               | _    |

| OVDD05      | General I/O Supply       | P20                   | —           | $OV_{DD}$               | -    |

| OVDD04      | General I/O Supply       | R20                   | —           | $OV_{DD}$               | -    |

| OVDD03      | General I/O Supply       | T20                   | —           | $OV_{DD}$               | -    |

| OVDD02      | General I/O Supply       | T26                   | —           | $OV_{DD}$               | -    |

| OVDD01      | General I/O Supply       | W26                   | —           | $OV_{DD}$               | -    |

| CVDD2       | eSPI and eSDHC Supply    | K20                   | —           | $CV_{DD}$               | _    |

| CVDD1       | eSPI and eSDHC Supply    | M20                   | —           | $CV_{DD}$               | -    |

| GVDD17      | DDR Supply               | AA8                   | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD16      | DDR Supply               | AA9                   | —           | ${\sf GV}_{\sf DD}$     | -    |

| GVDD15      | DDR Supply               | AA10                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD14      | DDR Supply               | AA11                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD13      | DDR Supply               | AA12                  | —           | $\text{GV}_{\text{DD}}$ | -    |

| GVDD12      | DDR Supply               | AA13                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD11      | DDR Supply               | AA14                  | —           | ${\sf GV}_{\sf DD}$     | —    |

| GVDD10      | DDR Supply               | AA15                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD09      | DDR Supply               | AB13                  | —           | ${\sf GV}_{\sf DD}$     | —    |

| GVDD08      | DDR Supply               | AB14                  | —           | ${\sf GV}_{\sf DD}$     | —    |

| GVDD07      | DDR Supply               | AC13                  | —           | ${\rm GV}_{\rm DD}$     | —    |

| GVDD06      | DDR Supply               | AC14                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD05      | DDR Supply               | AF6                   | —           | ${\rm GV}_{\rm DD}$     | —    |

| GVDD04      | DDR Supply               | AF9                   | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD03      | DDR Supply               | AF17                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD02      | DDR Supply               | AF20                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| GVDD01      | DDR Supply               | AF23                  | —           | ${\rm GV}_{\rm DD}$     | -    |

| BVDD07      | Local Bus Supply         | J7                    | —           | BV <sub>DD</sub>        | -    |

| BVDD06      | Local Bus Supply         | K7                    | —           | BV <sub>DD</sub>        | -    |

While VDD is ramping, current may be supplied from VDD through the chip to GVDD. Nevertheless, GVDD from an external supply should follow the sequencing described above.

# WARNING

Only 100,000 POR cycles are permitted per lifetime of a device.

All supplies must be at their stable values within 75 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

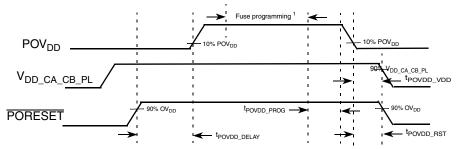

This figure provides the  $POV_{DD}$  timing diagram.

**NOTE:** POV<sub>DD</sub> must be stable at 1.5 V prior to initiating fuse programming.

# Figure 8. POV<sub>DD</sub> Timing Diagram

This table provides information on the power-down and power-up sequence parameters for POV<sub>DD</sub>.

Table 5. POV<sub>DD</sub> Timing <sup>5</sup>

| Driver Type              | Min | Мах | Unit    | Note |

|--------------------------|-----|-----|---------|------|

| <sup>t</sup> POVDD_DELAY | 100 | _   | SYSCLKs | 1    |

| tpovdd_prog              | 0   | —   | μs      | 2    |

| tpovdd_vdd               | 0   | —   | μs      | 3    |

| <sup>t</sup> povdd_rst   | 0   | —   | μs      | 4    |

Note:

1. Delay required from the negation of PORESET to driving POV<sub>DD</sub> ramp up. Delay measured from PORESET negation at 90% OV<sub>DD</sub> to 10% POV<sub>DD</sub> ramp up.

Delay required from fuse programming finished to POV<sub>DD</sub> ramp down start. Fuse programming must complete while POV<sub>DD</sub> is stable at 1.5 V. No activity other than that required for secure boot fuse programming is permitted while POV<sub>DD</sub> driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while POV<sub>DD</sub> = GND. After fuse programming is completed, it is required to return POV<sub>DD</sub> = GND.

Delay required from POV<sub>DD</sub> ramp down complete to V<sub>DD\_CA\_CB\_PL</sub> ramp down start. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before V<sub>DD\_CA\_CB\_PL</sub> is at 90% V<sub>DD</sub>.

Delay required from POV<sub>DD</sub> ramp down complete to PORESET assertion. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before PORESET assertion reaches 90% OV<sub>DD</sub>.

5. Only two secure boot fuse programming events are permitted per lifetime of a device.

To guarantee MCKE low during power up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, the sequencing for  $GV_{DD}$  is not required.

This table shows the estimated power dissipation on the AV<sub>DD</sub> and AV<sub>DD</sub> supplies for the device PLLs, at allowable voltage levels.

| AV <sub>DD</sub> s      | Typical | Maximum | Unit | Note |

|-------------------------|---------|---------|------|------|

| AV <sub>DD_DDR</sub>    | 5       | 15      | mW   | 1    |

| AV <sub>DD_CC1</sub>    | *       |         |      |      |

| AV <sub>DD_CC2</sub>    | *       |         |      |      |

| AV <sub>DD_PLAT</sub>   | *       |         |      |      |

| AV <sub>DD_SRDS1</sub>  | —       | 36      | mW   | 2    |

| AV <sub>DD_SRDS2</sub>  |         |         |      |      |

| USB_V <sub>DD_1P0</sub> | —       | 10      | mW   | 3    |

## Table 8. Device AV<sub>DD</sub> Power Dissipation

#### Note:

1.  $V_{DD\_CA\_CB\_PL}$ ,  $T_A = 80^{\circ}C$ ,  $T_J = 105^{\circ}C$ 2.  $SV_{DD} = 1.0$  V,  $T_A = 80^{\circ}C$ ,  $T_J = 105^{\circ}C$

3. USB\_V<sub>DD 1P0</sub> = 1.0V, T<sub>A</sub> = 80°C, T<sub>J</sub> = 105°C

This table shows the estimated power dissipation on the POV<sub>DD</sub> supply for the chip at allowable voltage levels.

### Table 9. POV<sub>DD</sub> Power Dissipation

| Supply            | Maximum | Unit | Notes |

|-------------------|---------|------|-------|

| POV <sub>DD</sub> | 450     | mW   | 1     |

#### Note:

1. To ensure device reliability, fuse programming must be performed within the recommended fuse programming temperature range per Table 3.

This table shows the estimated power dissipation on the  $V_{DD LP}$  supply for the device, at allowable voltage levels.

## Table 10. V<sub>DD LP</sub> Power Dissipation

| Supply                               | Maximum | Unit | Notes |

|--------------------------------------|---------|------|-------|

| V <sub>DD_LP</sub> (Device on, 105C) | 1.5     | mW   | 1     |

| V <sub>DD_LP</sub> (Device off, 70C) | 195     | uW   | 2     |

| V <sub>DD_LP</sub> (Device off, 40C) | 132     | uW   | 2     |

#### Note:

1.  $V_{DD_{LP}} = 1.0 \text{ V}, \text{ } \text{T}_{\text{J}} = 105^{\circ}\text{C}.$

2. When the device is off, V<sub>DD LP</sub> may be supplied by battery power to retain the Zeroizable Master Key and other Trust Architecture state. Board should implement a PMIC, which switches V<sub>DD IP</sub> to battery when the SoC is powered down. See the Trust Architecture chapter in the device reference manual for more information.

#### 2.5 Thermal

# Table 11. Package Thermal Characteristics <sup>6</sup>

| Rating                                  | Board                   | Symbol         | Value | Unit | Note |

|-----------------------------------------|-------------------------|----------------|-------|------|------|

| Junction to ambient, natural convection | Single-layer board (1s) | $R_{\ThetaJA}$ | 21    | °C/W | 1, 2 |

| Junction to ambient, natural convection | Four-layer board (2s2p) | $R_{\ThetaJA}$ | 15    | °C/W | 1, 3 |

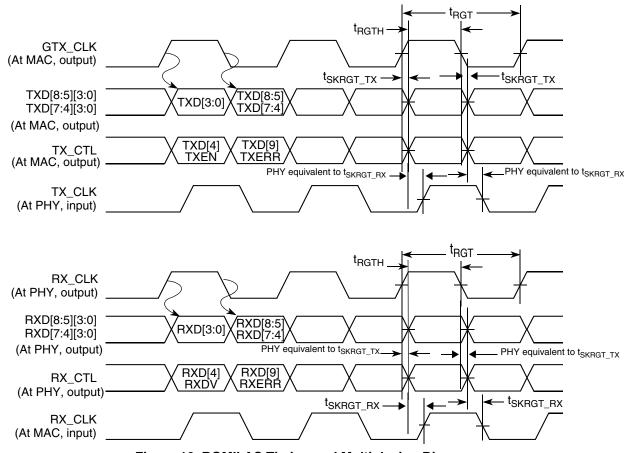

Figure 16. RGMII AC Timing and Multiplexing Diagrams

# 2.12.3 Ethernet Management Interface

This section discusses the electrical characteristics for the EMI1 interfaces. EMI1 is the PHY management interface controlled by the MDIO controller associated with Frame Manager 1 1GMAC–1.

# 2.12.3.1 Ethernet Management Interface DC Electrical Characteristics

The Ethernet management interface is defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for the Ethernet management interface is provided in this table.

# Table 38. Ethernet Management Interface DC Electrical Characteristics (LV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                             | Symbol          | Min  | Max | Unit | Note |

|-----------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                    | V <sub>IH</sub> | 2.0  | —   | V    | 2    |

| Input low voltage                                                     | V <sub>IL</sub> | _    | 0.9 | V    | 2    |

| Input high current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 2.1 V)  | I <sub>IH</sub> | _    | 40  | μΑ   | 1    |

| Input low current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V)   | IIL             | -600 | —   | μΑ   | 1    |

| Output high voltage ( $LV_{DD} = Min$ , $I_{OH} = -1.0 mA$ )          | V <sub>OH</sub> | 2.4  | _   | V    | _    |

| Output low voltage (LV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub> |      | 0.4 | V    |      |

# 2.13 USB

This section provides the AC and DC electrical specifications for the USB interface.

# 2.13.1 USB DC Electrical Characteristics

This table provides the DC electrical characteristics for the USB interface at  $USB_VDD_3P3 = 3.3 V$ .

## Table 44. USB DC Electrical Characteristics (USB\_V<sub>DD</sub>\_3P3 = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                                             | Symbol          | Min | Max | Unit | Note |

|-------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage <sup>1</sup>                                                                       | V <sub>IH</sub> | 2.0 | —   | V    | 1    |

| Input low voltage                                                                                     | V <sub>IL</sub> | —   | 0.8 | V    | 1    |

| Input current (USB_V <sub>IN</sub> _3P3 = 0 V or USB_V <sub>IN</sub> _3P3 = USB_V <sub>DD</sub> _3P3) | I <sub>IN</sub> | —   | ±40 | μA   | 2    |

| Output high voltage (USB_V <sub>DD</sub> _3P3 = min, $I_{OH} = -2 \text{ mA}$ )                       | V <sub>OH</sub> | 2.8 | —   | V    |      |

| Output low voltage (USB_V <sub>DD</sub> _3P3 = min, $I_{OL}$ = 2 mA)                                  | V <sub>OL</sub> | —   | 0.3 | V    | —    |

Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max USB\_ $V_{IN}$ \_3P3 values found in Table 3.

- The symbol USB\_V<sub>IN</sub>\_3P3, in this case, represents the USB\_V<sub>IN</sub>\_3P3 symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

# 2.13.2 USB AC Electrical Specifications

This table provides the USB clock input (USBn\_CLKIN) AC timing specifications.

## Table 45. USB\_CLK\_IN AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                                 | Condition                                                                     | Symbol                  | Min    | Тур | Max   | Unit | Note |

|-------------------------------------------|-------------------------------------------------------------------------------|-------------------------|--------|-----|-------|------|------|

| Frequency range                           | _                                                                             | f <sub>USB_CLK_IN</sub> | —      | 24  |       | MHz  | —    |

| Rise/Fall time                            | Measured between 10% and 90%                                                  | t <sub>USRF</sub>       | —      | —   | 6     | ns   | 1    |

| Clock frequency<br>tolerance              |                                                                               | t <sub>CLK_TOL</sub>    | -0.005 | 0   | 0.005 | %    | —    |

| Reference clock duty cycle                | Measured at 1.6 V                                                             | t <sub>CLK_DUTY</sub>   | 40     | 50  | 60    | %    | —    |

| Total input jitter/time<br>interval error | RMS value measured with a second-order, high-pass filter of 500-kHz bandwidth | t <sub>CLK_PJ</sub>     | —      |     | 5     | ps   | —    |

Note:

1. System/board must be designed to ensure the input requirement to the device is achieved. Proper device operation is guaranteed for inputs meeting this requirement by design, simulation, characterization, or functional testing.

# Table 56. I<sup>2</sup>C DC Electrical Characteristics ( $OV_{DD} = 3.3 V$ ) (continued)

For recommended operating conditions, see Table 3.

| Parameter                                                                                                | Symbol              | Min | Мах | Unit | Note |

|----------------------------------------------------------------------------------------------------------|---------------------|-----|-----|------|------|

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>i2KHKL</sub> | 0   | 50  | ns   | 3    |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -40 | 40  | μA   | 4    |

| Capacitance for each I/O pin                                                                             | CI                  | _   | 10  | pF   |      |

#### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $OV_{IN}$  values found in Table 3.

- 2. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 3. See the chip reference manual for information about the digital filter used.

- 4. I/O pins obstruct the SDA and SCL lines if OV<sub>DD</sub> is switched off.

# 2.18.2 I<sup>2</sup>C AC Electrical Specifications

This table provides the I<sup>2</sup>C AC timing specifications.

## Table 57. I<sup>2</sup>C AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400 | kHz  | 2    |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —   | μS   | —    |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | —   | μS   | —    |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | —   | μS   | —    |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | —   | μS   | —    |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 | _   | ns   | —    |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>i2DXKL</sub> | 0   |     | μS   | 3    |

| Data output delay time                                                                       | t <sub>I2OVKL</sub> | —   | 0.9 | μS   | 4    |

| Setup time for STOP condition                                                                | t <sub>I2PVKH</sub> | 0.6 | —   | μS   | —    |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3 | —   | μS   | —    |

# 2.19 GPIO

This section describes the DC and AC electrical characteristics for the GPIO interface.

# 2.19.1 GPIO DC Electrical Characteristics

This table provides the DC electrical characteristics for GPIO pins operating at  $CV_{DD}$ ,  $LV_{DD}$  or  $OV_{DD} = 3.3$  V.

## Table 58. GPIO DC Electrical Characteristics (CV<sub>DD</sub>, LV<sub>DD</sub> or OV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                      | Symbol          | Min | Max | Unit | Note |

|--------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                             | V <sub>IH</sub> | 2.0 | _   | V    | 1    |

| Input low voltage                                                              | V <sub>IL</sub> | —   | 0.8 | V    | 1    |

| Input current (OV <sub>IN</sub> = 0 V or OV <sub>IN</sub> = OV <sub>DD</sub> ) | I <sub>IN</sub> | —   | ±40 | μA   | 2    |

| Output high voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )                        | V <sub>OH</sub> | 2.4 | —   | V    | —    |

| Output low voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)            | V <sub>OL</sub> | —   | 0.4 | V    | —    |

Note:

1. The min V<sub>IL</sub> and max V<sub>IH</sub> values are based on the min and max L/OV<sub>IN</sub> respective values found in Table 3.

2. The symbol V<sub>IN</sub>, in this case, represents the L/OV<sub>IN</sub> symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

This table provides the DC electrical characteristics for GPIO pins operating at  $CV_{DD}$  or  $LV_{DD} = 2.5$  V.

## Table 59. GPIO DC Electrical Characteristics ( $CV_{DD}$ or $LV_{DD} = 2.5 V$ )

For recommended operating conditions, see Table 3.

| Parameter                                                                | Symbol          | Min | Мах | Unit | Note |

|--------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                       | V <sub>IH</sub> | 1.7 | _   | V    | 1    |

| Input low voltage                                                        | V <sub>IL</sub> | —   | 0.7 | V    | 1    |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = LV_{DD}$ )            | I <sub>IN</sub> | _   | ±40 | μA   | 2    |

| Output high voltage<br>(LV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub> | 2.0 | —   | V    | —    |

| Output low voltage<br>(LV <sub>DD</sub> = min, I <sub>OH</sub> = 2 mA)   | V <sub>OL</sub> | —   | 0.4 | V    | _    |

Note:

1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $LV_{IN}$  values found in Table 3.

2. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

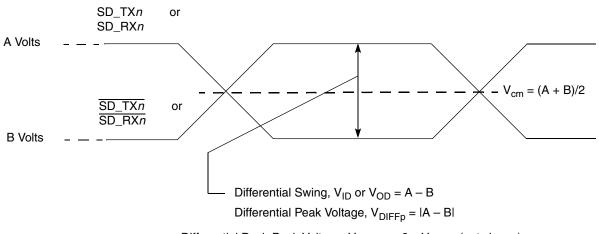

This figure shows how the signals are defined. For illustration purposes only, one SerDes lane is used in the description. This figure shows the waveform for either a transmitter output (SD\_TX*n* and  $\overline{SD_TXn}$ ) or a receiver input (SD\_RX*n* and  $\overline{SD_RXn}$ ). Each signal swings between A volts and B volts where A > B.

Differential Peak-Peak Voltage,  $V_{DIFFpp} = 2 \times V_{DIFFp}$  (not shown)

### Figure 32. Differential Voltage Definitions for Transmitter or Receiver

Using this waveform, the definitions are as shown in the following list. To simplify the illustration, the definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment:

**Single-Ended Swing** The transmitter output signals and the receiver input signals  $SD_TXn$ ,  $\overline{SD_TXn}$ ,  $SD_RXn$  and  $\overline{SD_RXn}$  each have a peak-to-peak swing of A - B volts. This is also referred as each signal wire's single-ended swing.

#### Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TXn} - V_{\overline{SD_TXn}}$ . The  $V_{OD}$  value can be either positive or negative.

#### Differential Input Voltage, VID (or Differential Input Swing):

The differential input voltage (or swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SD_RXn} - V_{\overline{SD_RXn}}$ . The  $V_{ID}$  value can be either positive or negative.

# Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as the differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

# Differential Peak-to-Peak, $V_{DIFFp-p}$

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice the differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

#### **Differential Waveform**

The differential waveform is constructed by subtracting the inverting signal ( $\overline{SD_TXn}$ , for example) from the non-inverting signal ( $\overline{SD_TXn}$ , for example) within a differential pair. There is

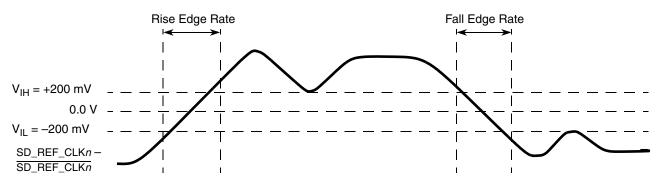

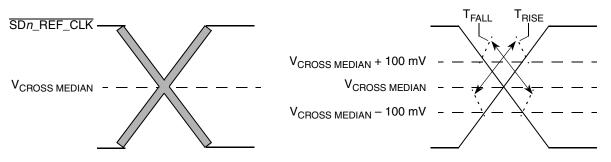

Figure 37. Differential Measurement Points for Rise and Fall Time

Figure 38. Single-Ended Measurement Points for Rise and Fall Time Matching

# 2.20.2.4 Spread Spectrum Clock

SD\_REF\_CLK1/SD\_REF\_CLK1 were designed to work with a spread spectrum clock (+0 to 0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation must be used.

SD\_REF\_CLK2/SD\_REF\_CLK2 were designed to work with a spread spectrum clock (+0 to 0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock and the industry protocol specifications supports it. For better results, a source without significant unintended modulation must be used.

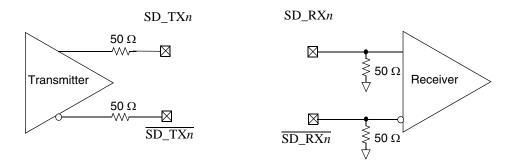

# 2.20.3 SerDes Transmitter and Receiver Reference Circuits

This figure shows the reference circuits for SerDes data lane's transmitter and receiver.

## Table 69. PCI Express 2.0 (5 GT/s) Differential Receiver (Rx) Input AC Specifications (continued)

For recommended operating conditions, see Table 3.

| Parameter                                  | Symbol                   | Min | Тур | Max  | Unit | Note                                                                              |

|--------------------------------------------|--------------------------|-----|-----|------|------|-----------------------------------------------------------------------------------|

| Max Rx inherent deterministic timing error | T <sub>RX-DJ-DD-CC</sub> |     | —   | 0.30 | UI   | The maximum inherent deterministic timing error for common RefClk Rx architecture |

| Max Rx inherent deterministic timing error | T <sub>RX-DJ-DD-DC</sub> |     | _   | 0.24 | UI   | The maximum inherent deterministic timing error for common RefClk Rx architecture |

#### Note:

1. No test load is necessarily associated with this value.

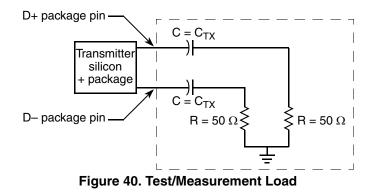

# 2.20.4.6 Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point. The package pins of the device must be connected to the test/measurement load within 0.2 inches of that load, as shown in this figure.

# NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary. If the vendor does not explicitly state where the measurement point is located, the measurement point is assumed to be the D+ and D- package pins.

# 2.20.5 Serial RapidIO (sRIO)

This section describes the DC and AC electrical specifications for the Serial RapidIO interface of the LP-Serial physical layer. The electrical specifications cover both single and multiple-lane links. Two transmitters (short run and long run) and a single receiver are specified for each of three baud rates: 2.50, 3.125, and 5 GBaud.

Two transmitter specifications allow for solutions ranging from simple board-to-board interconnect to driving two connectors across a backplane. A single receiver specification is given that accepts signals from both the short run and long run transmitter specifications.

The short run transmitter must be used mainly for chip-to-chip connections on either the same printed circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The minimum swings of the short run specification reduce the overall power used by the transceivers.

Figure 46. SGMII AC Test/Measurement Load

# 2.20.8.2.3 SGMII Receiver AC Timing Specification

This table provides the SGMII receiver AC timing specifications. The AC timing specifications do not include RefClk jitter. Source synchronous clocking is not supported. Clock is recovered from the data.

## Table 92. SGMII Receive AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                                          | Symbol | Min           | Тур | Мах               | Unit   | Note    |

|----------------------------------------------------|--------|---------------|-----|-------------------|--------|---------|

| Deterministic jitter tolerance                     | JD     | 0.37          | —   | _                 | UI p-p | 1, 2    |

| Combined deterministic and random jitter tolerance | JDR    | 0.55          | _   | —                 | UI p-p | 1, 2    |

| Total jitter tolerance                             | JT     | 0.65          | _   | —                 | UI p-p | 1, 2, 3 |

| Bit error ratio                                    | BER    |               | _   | 10 <sup>-12</sup> |        |         |

| Unit Interval: 1.25 GBaud                          | UI     | 800 – 100 ppm | 800 | 800 + 100 ppm     | ps     | 1       |

| Unit Interval: 3.125 GBaud                         | UI     | 320 – 100 ppm | 320 | 320 + 100 ppm     | ps     | 1       |

Note:

- 1. Measured at receiver

- 2. Refer to RapidIO<sup>™</sup> 1×/4× LP Serial Physical Layer Specification for interpretation of jitter specifications.

- 3. Total jitter is composed of three components: deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 42. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

The sinusoidal jitter in the total jitter tolerance may have any amplitude and frequency in the unshaded region of Figure 42.

# 3 Hardware Design Considerations

This section discusses the hardware design considerations.

# 3.1 System Clocking

This section describes the PLL configuration of the device.

This device includes six PLLs, as follows:

• There are two selectable core cluster PLLs that generate a core clock from the externally supplied SYSCLK input. Core complex 0–1 and platform can select from CC1 PLL; core complex 2–3 can select from CC2 PLL. The frequency ratio between the core cluster PLLs and SYSCLK is selected using the configuration bits as described in Section 3.1.3,

### Hardware Design Considerations

$ECn_GTX_CLK125$  is a 125-MHz input clock on the dTSEC ports. If the dTSEC ports are not used for RGMII, the  $ECn_GTX_CLK125$  input can be tied off to GND.

If RCW field I2C = 0b0100 or 0b0101 (RCW bits 354–357), the SDHC\_WP and  $\overline{SDHC_CD}$  input signals are enabled for external use. If SDHC\_WP and  $\overline{SDHC_CD}$  are selected and not used, they must be externally pulled low such that SDHC\_WP = 0 (write enabled) and  $\overline{SDHC_CD} = 0$  (card detected). If RCW field I2C  $\neq$  0b0100 or 0b0101, thereby selecting either I2C3 or GPIO functionality, SDHC\_WP and  $\overline{SDHC_CD}$  are internally driven such that SDHC\_WP = write enabled and  $\overline{SDHC_CD} = card detected$  and the selected I2C3 or GPIO external pin functionality may be used.

TMP\_DETECT pin and LP\_TMP DETECT pin are active low input to the Security Monitor (refer to the "Secure Boot and Trust Architecture" chapter of the chip reference manual). If a tamper sensor is used, it must maintain the signal at the specified voltage until a tamper is detected. A 1K pulldown resistor strongly recommended. If Trust is used without tamper sensors, tie high.VDD\_LP must be connected even if Low Power features aren't used. Otherwise, the LP\_Section will generate internal errors that will prevent the high power trust section from reaching Trusted/Secure state.

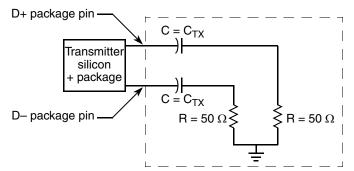

# 3.6.1 Legacy JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 55. Care must be taken to ensure that these pins are maintained at a valid negated state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires TRST to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to PORESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert PORESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 55 allows the COP port to independently assert **PORESET** or **TRST**, while ensuring that the target can drive **PORESET** as well.

The COP interface has a standard header, shown in Figure 54, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 54 is common to all known emulators.

# 3.6.1.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

TRST must be tied to PORESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (PORESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 55. If this is not possible, the

#### **Hardware Design Considerations**

#### Notes:

- 1. The Aurora port and target board must be able to independently assert PORESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 1 k $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. This switch is included as a precaution for BSDL testing. The switch must be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch must be closed to position B.

- 5. This is an open-drain gate. 4. Asserting HRESET causes a hard reset on the device.

## Figure 59. Aurora 70 Pin Connector Duplex Interface Connection

# 5 Security Fuse Processor

The device implements the QorIQ platform's Trust Architecture supporting capabilities such as secure boot. Use of the Trust Architecture features is dependent on programming fuses in the Security Fuse Processor (SFP). The details of the Trust Architecture and SFP can be found in the chip reference manual.

In order to program SFP fuses, the user is required to supply 1.5 V to the POV<sub>DD</sub> pin per Section 2.2, "Power Up Sequencing." POV<sub>DD</sub> should only be powered for the duration of the fuse programming cycle, with a per device limit of two fuse programming cycles. All other times POV<sub>DD</sub> must be connected to GND. The sequencing requirements for raising and lowering POV<sub>DD</sub> are shown in Figure 8. To ensure device reliability, fuse programming must be performed within the recommended fuse programming temperature range per Table 3.

Users not implementing the QorIQ platform's Trust Architecture features are not required to program fuses and should connect  $POV_{DD}$  to GND.

# 6 Ordering Information

Contact your local Freescale sales office or regional marketing team for ordering information.

# 6.1 Part Numbering Nomenclature

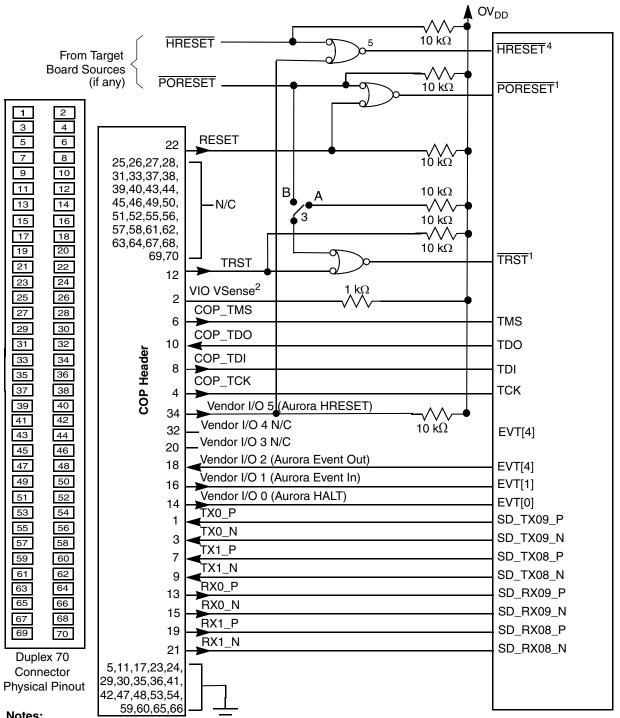

This table provides the Freescale QorIQ platform part numbering nomenclature. Not all possible combinations of part numbers implied by the part numbering scheme are supported. For a list of available part numbers, contact your Freescale Sales office. Each part number also contains a revision code which refers to the die mask revision number.

| p          | n        | nn                                          | n          | x                                                      | t                                                           | е                                            | n                                                                                     | с                                                                      | d                                    | r                                                  |

|------------|----------|---------------------------------------------|------------|--------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|

| Generation | Platform | Number<br>of Cores                          | Derivative | Qual<br>Status                                         | Temp.<br>Range                                              | Encryption                                   | Package<br>Type                                                                       | CPU<br>Freq                                                            | DDR<br>Data Rate                     | Die<br>Revision                                    |

| P = 45 nm  | 1–5      | 01 = 1 core<br>02 = 2 cores<br>04 = 4 cores | 0–9        | P =<br>Prototype<br>N =<br>Industrial<br>qualification | S =<br>Std temp<br>X =<br>Extended<br>temp (–40<br>to 105C) | E = SEC<br>present<br>N = SEC<br>not present | 1 =<br>FC-PBGA<br>Pb-free<br>spheres<br>7 =<br>FC-PBGA<br>C4 and<br>sphere<br>Pb-free | F =<br>667 MHz<br>H =<br>800 MHz<br>K =<br>1000 MHz<br>M =<br>1200 MHz | L =<br>1067 MT/s<br>M =<br>1200 MT/s | A = Rev<br>1.0<br>B = Rev<br>1.1<br>C =<br>Rev 2.0 |

Table 107. Part Numbering Nomenclature

# 6.2 Orderable Part Numbers Addressed by this Document

This table provides the Freescale orderable part numbers addressed by this document for the chip.

**Revision History**

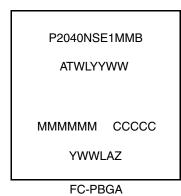

# 6.2.1 Part Marking

Parts are marked as in the example shown in this figure.

#### Notes:

P2040NSE1MMB is the orderable part number. See Table 107 for details.

ATWLYYWW is the test traceability code.

MMMMMM is the mask number.

CCCCC is the country code.

YWWLAZ is the assembly traceability code.

# Figure 64. Part Marking for FC-PBGA Device

# 7 Revision History

This table provides a revision history for this document.

## Table 108. Revision History

| Rev.<br>Number | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 02/2013 | <ul> <li>In Table 7, "P2040 I/O Power Supply Estimated Values," updated the USB power supply with USB_Vdd_3P3 and updated the typical value with "0.003" in the Others (Reset, System Clock, JTAG &amp; Misc.) row.</li> <li>In Table 8, "Device AVDD Power Dissipation," removed V<sub>DD_LP</sub> from table.</li> <li>Added Table 10, "VDD_LP Power Dissipation."</li> <li>In Table 53, "MPIC Input AC Timing Specifications," added Trust inputs AC timing and footnote 2.</li> <li>In Table 93, "Processor Clocking Specifications," updated footnote 8 with Rev 1.1 silicon.</li> <li>In Table 107, "Part Numbering Nomenclature," added "C" in the Die Revision collumn.</li> <li>In Section 6.2, "Orderable Part Numbers Addressed by this Document," added the device part numbers for Rev 2.0 silicon.</li> </ul> |