#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Core Processor                  | PowerPC e500mc                                            |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                            |

| Speed                           | 667MHz                                                    |

| Co-Processors/DSP               | -                                                         |

| RAM Controllers                 | DDR3, DDR3L                                               |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10/100/1000Mbps (5)                                       |

| SATA                            | SATA 3Gbps (2)                                            |

| USB                             | USB 2.0 + PHY (2)                                         |

| Voltage - I/O                   | 1.0V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | -                                                         |

| Package / Case                  | -                                                         |

| Supplier Device Package         | 780-FCPBGA (23x23)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=p2040nsn7flc |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                    |                 |                                    |                |                                   |                                    |                                    |               |                          |                |               |                         |               | 7                  | -  |

|------------------------------------|-----------------|------------------------------------|----------------|-----------------------------------|------------------------------------|------------------------------------|---------------|--------------------------|----------------|---------------|-------------------------|---------------|--------------------|----|

| V <sub>DD_</sub><br>CA_PL<br>[27]  | GND<br>[092]    | V <sub>DD</sub> _<br>CA_PL<br>[26] | GND<br>[091]   | V <sub>DD_</sub><br>CA_PL<br>[25] | OV <sub>DD</sub><br>[4]            | GND<br>[090]                       | ASLEEP        | UART1_<br>SOUT           | GND<br>[089]   | UART1_<br>CTS | UART1_<br>SIN           | GND<br>[088]  | SYSCLK             | R  |

| V <sub>DD</sub><br>CA_PL<br>[21]   | GND<br>[083]    | V <sub>DD</sub> _<br>CA_PL<br>[20] | GND<br>[082]   | V <sub>DD</sub><br>CA_PL<br>[19]  | OV <sub>DD</sub><br>[3]            | GND<br>[081]                       | PORESE        | THRESET                  | TMP_<br>DETECT | CKSTP<br>OUT  | OV <sub>DD</sub><br>[2] | CLK_<br>OUT   | TEST_<br>SEL       | Т  |

| V <sub>DD_</sub><br>CA_PL<br>[15]  | VDD_CB<br>[11]  | GND<br>[075]                       | VDD_CB<br>[10] | GND<br>[074]                      | V <sub>DD</sub> _<br>CA_PL<br>[14] | POVDD                              | GND<br>[073]  | IO_<br>VSEL1             | EVT<br>[4]     | GND<br>[072]  | <b>EVT</b><br>[2]       | EVT<br>[1]    | RESET_<br>REQ      | U  |

| V <sub>DD_</sub><br>CA_PL<br>[10]  | GND<br>[064]    | GND<br>[063]                       | VDD_CB<br>[09] | GND<br>[062]                      | VDD_CB<br>[08]                     | GND<br>[061]                       | AVDD_<br>PLAT | GND<br>[060]             | IIC4_<br>SDA   | IRQ<br>[04]   | EVT<br>[0]              | GND<br>[059]  | SCAN_<br>MODE      | V  |

| V <sub>DD</sub> _<br>CA_PL<br>[06] | VDD_CB<br>[07]  | GND<br>[052]                       | VDD_CB<br>[06] | GND<br>[051]                      | VDD_CB<br>[05]                     | GND<br>[050]                       | AVDD_<br>CC2  | GND<br>[049]             | EVT<br>[3]     | IIC2_<br>SCL  | OV <sub>DD</sub><br>[1] | TMS           | TDI                | W  |

| V <sub>DD_</sub><br>CA_PL<br>[02]  | GND<br>[042]    | GND<br>[041]                       | VDD_CB<br>[04] | GND<br>[040]                      | VDD_CB<br>[03]                     | IO_<br>VSEL_<br>[4]                | GND<br>[039]  | IO_<br>VSEL_<br>[3]      |                | IIRQ_<br>[00] | IIRQ_<br>[06]           | TRST          | тск                | Y  |

| GV <sub>DD</sub><br>[10]           | SENSE<br>GND_CB | GND<br>[036]                       | VDD_CB<br>[02] | GND<br>[035]                      | VDD_CB<br>[01]                     | V <sub>DD</sub> _<br>CA_PL<br>[01] | IIRQ_<br>[05] | IIRQ_<br>[07]            | GND<br>[034]   | IIC2_<br>SDA  | IIRQ_<br>[03]           | GND<br>[033]  | TDO                | AA |

| GND<br>[027]                       | SENSE<br>VDD_CB | RSRV                               | RSRV           | RSRV                              | RSRV                               | IO_<br>VSEL<br>[2]                 | GND<br>[026]  | IIC3_<br>SCL             | IIRQ_<br>[10]  | IIRQ_<br>[02] | IIC3_<br>SDA            | IIRQ_<br>[0]  | IO_<br>VSEL<br>[0] | AB |

| MBA<br>[1]                         | MBA<br>[0]      | GND<br>[024]                       | MCS<br>[0]     | MODT<br>[0]                       | GND<br>[023]                       | MCS1                               | IIRQ_<br>[08] | IIC4_<br>SCL             | IIRQ_<br>[11]  | IIC1_<br>SCL  | GND<br>[022]            | IIRQ_<br>[09] | IIC1_<br>SDA       | AC |

| GND<br>[020]                       | MDQ<br>[33]     | MDQS<br>[4]                        | MDQS<br>[4]    | MDQ<br>[35]                       | MDQ<br>[53]                        | MDQ<br>[49]                        | MODT<br>[1]   | MDQ<br>[54]              | MDQ<br>[51]    | MDQ<br>[58]   | MDQ<br>[59]             | MDQ<br>[62]   | MDQ<br>[63]        | AD |

| GND<br>[015]                       | MDQ<br>[32]     | MDM<br>[4]                         | GND<br>[014]   | MDQ<br>[34]                       | MDQ<br>[52]                        | GND<br>[013]                       | MDQS<br>[6]   | MDQS<br>[6]              | GND<br>[012]   | MDQ<br>[55]   | MDM<br>[7]              | GND<br>[011]  | MDQS<br>[7]        | AE |

| MDQ<br>[36]                        | MDQ<br>[37]     | GV <sub>DD</sub><br>[03]           | MDQ<br>[38]    | MDQ<br>[39]                       | GV <sub>DD</sub><br>[02]           | MDQ<br>[48]                        | MDM<br>[6]    | GV <sub>DD</sub><br>[01] | MDQ<br>[50]    | MDQ<br>[61]   | MDQ<br>[56]             | MDQ<br>[57]   | MDQS<br>[7]        | AF |

| MAPAR<br>_OUT                      | MA<br>[00]      | MCS<br>[2]                         | MODT<br>[2]    | GND<br>[005]                      | MCS<br>[3]                         | MDQ<br>[44]                        | GND<br>[004]  | MDQ<br>[41]              | MDQS<br>[5]    | GND<br>[003]  | MDQ<br>[47]             | MDQ<br>[43]   | MDQ<br>[60]        | AG |

| GND<br>[001]                       | MA<br>[10]      | MRAS                               | MWE            | MCAS                              | MA<br>[13]                         | MODT<br>[3]                        | MDQ<br>[45]   | MDQ<br>[40]              | MDQS<br>[5]    | MDM<br>[5]    | MDQ<br>[46]             | MDQ<br>[42]   |                    | AH |

| 15                                 | 16              | 17                                 | 18             | 19                                | 20                                 | 21                                 | 22            | 23                       | 24             | 25            | 26                      | 27            | 28                 |    |

|                                    |                 |                                    | Fig            | ure 6.                            | 780 BG/                            | A Ball I                           | Map Dia       | gram (E                  | Detail V       | iew D)        |                         |               |                    |    |

### **Pin Assignments and Reset States**

### Table 1. Pin List by Bus (continued)

| Signal | Signal Description    | Package<br>Pin Number | Pin<br>Type | Power<br>Supply             | Note |

|--------|-----------------------|-----------------------|-------------|-----------------------------|------|

| MDQS5  | Data Strobe           | AH24                  | I/O         | GV <sub>DD</sub>            | _    |

| MDQS6  | Data Strobe           |                       | I/O         | $\text{GV}_{\text{DD}}$     | _    |

| MDQS7  | Data Strobe           | AF28                  | I/O         | GV <sub>DD</sub>            | _    |

| MDQS8  | Data Strobe           | AG3                   | I/O         | $\text{GV}_{\text{DD}}$     | _    |

| MBA0   | Bank Select           | AC16                  | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MBA1   | Bank Select           | AC15                  | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MBA2   | Bank Select           | AC8                   | 0           | ${\rm GV}_{\rm DD}$         | —    |

| MA00   | Address               | AG16                  | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MA01   | Address               | AF12                  | 0           | ${\rm GV}_{\rm DD}$         | —    |

| MA02   | Address               | AC12                  | 0           | ${\rm GV}_{\rm DD}$         | —    |

| MA03   | Address               | AH11                  | 0           | $\text{GV}_{\text{DD}}$     | —    |

| MA04   | Address               | AG11                  | 0           | GV <sub>DD</sub>            | _    |

| MA05   | Address               | AH10                  | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MA06   | Address               | AC11                  | 0           | $\text{GV}_{\text{DD}}$     | —    |

| MA07   | Address               | AC10                  | 0           | GV <sub>DD</sub>            | _    |

| MA08   | Address               | AF10                  | 0           | ${\rm GV}_{\rm DD}$         | —    |

| MA09   | Address               | AH9                   | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MA10   | Address               | AH16                  | 0           | ${\rm GV}_{\rm DD}$         | —    |

| MA11   | Address               | AG9                   | 0           | $\text{GV}_{\text{DD}}$     | —    |

| MA12   | Address               | AC9                   | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MA13   | Address               | AH20                  | 0           | $\text{GV}_{\text{DD}}$     | —    |

| MA14   | Address               | AG8                   | 0           | $\mathrm{GV}_\mathrm{DD}$   | —    |

| MA15   | Address               | AH7                   | 0           | $\text{GV}_{\text{DD}}$     | _    |

| MWE    | Write Enable          | AH18                  | 0           | $\mathrm{GV}_{\mathrm{DD}}$ | —    |

| MRAS   | Row Address Strobe    | AH17                  | 0           | $\mathrm{GV}_{\mathrm{DD}}$ | —    |

| MCAS   | Column Address Strobe | AH19                  | 0           | $\mathrm{GV}_{\mathrm{DD}}$ | —    |

| MCS0   | Chip Select           | AC18                  | 0           | $\mathrm{GV}_{\mathrm{DD}}$ | —    |

| MCS1   | Chip Select           | AC21                  | 0           | $\mathrm{GV}_\mathrm{DD}$   | _    |

| MCS2   | Chip Select           | AG17                  | 0           | $\mathrm{GV}_{\mathrm{DD}}$ | —    |

| MCS3   | Chip Select           | AG20                  | 0           | $\mathrm{GV}_\mathrm{DD}$   | -    |

| MCKE0  | Clock Enable          | AB8                   | 0           | $\mathrm{GV}_\mathrm{DD}$   | —    |

| MCKE1  | Clock Enable          | AB7                   | 0           | $\mathrm{GV}_\mathrm{DD}$   | —    |

| MCKE2  | Clock Enable          | AH6                   | 0           | ${\sf GV}_{\sf DD}$         | —    |

| MCKE3  | Clock Enable          | AG6                   | 0           | $\text{GV}_{\text{DD}}$     | —    |

**Pin Assignments and Reset States**

| Table 1 | . Pin | List b | v Bus | (continued) |

|---------|-------|--------|-------|-------------|

|         |       |        | ,     | (           |

| Signal | Signal Description             | Package<br>Pin Number | Pin<br>Type | Power<br>Supply         | Note |

|--------|--------------------------------|-----------------------|-------------|-------------------------|------|

| MCK0   | Clock                          | AD14                  | 0           | GV <sub>DD</sub>        |      |

| MCK1   | Clock                          | AE13                  | 0           | GV <sub>DD</sub>        | _    |

| MCK2   | Clock                          | AG13                  | 0           | GV <sub>DD</sub>        | _    |

| МСКЗ   | Clock                          | AG14                  | 0           | GV <sub>DD</sub>        |      |

| MCK0   | Clock Complements              | AE14                  | 0           | GV <sub>DD</sub>        | -    |

| MCK1   | Clock Complements              | AD13                  | 0           | GV <sub>DD</sub>        |      |

| MCK2   | Clock Complements              | AH13                  | 0           | $\text{GV}_{\text{DD}}$ | -    |

| MCK3   | Clock Complements              | AH14                  | 0           | $\text{GV}_{\text{DD}}$ | -    |

| MODT0  | On Die Termination             | AC19                  | 0           | GV <sub>DD</sub>        | _    |

| MODT1  | On Die Termination             | AD22                  | 0           | GV <sub>DD</sub>        | _    |

| MODT2  | On Die Termination             | AG18                  | 0           | GV <sub>DD</sub>        | _    |

| MODT3  | On Die Termination             | AH21                  | 0           | GV <sub>DD</sub>        |      |

| MDICO  | Driver Impedance Calibration   | AG12                  | I/O         | $\text{GV}_{\text{DD}}$ | 16   |

| MDIC1  | Driver Impedance Calibration   | AE12                  | I/O         | GV <sub>DD</sub>        | 16   |

|        | Local Bus Controller Interface |                       | 11          |                         | 1    |

| LAD00  | Muxed Data/Address             | J6                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD01  | Muxed Data/Address             | J4                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD02  | Muxed Data/Address             | K2                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD03  | Muxed Data/Address             | K4                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD04  | Muxed Data/Address             | L1                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD05  | Muxed Data/Address             | J5                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD06  | Muxed Data/Address             | N5                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD07  | Muxed Data/Address             | N2                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD08  | Muxed Data/Address             | N3                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD09  | Muxed Data/Address             | N1                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD10  | Muxed Data/Address             | P4                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD11  | Muxed Data/Address             | R7                    | I/O         | $BV_DD$                 | 3    |

| LAD12  | Muxed Data/Address             | T4                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD13  | Muxed Data/Address             | U2                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD14  | Muxed Data/Address             | T6                    | I/O         | BV <sub>DD</sub>        | 3    |

| LAD15  | Muxed Data/Address             | T7                    | I/O         | BV <sub>DD</sub>        | 3    |

| LA16   | Address                        | K6                    | I/O         | BV <sub>DD</sub>        | 31   |

| LA17   | Address                        | КЗ                    | I/O         | BV <sub>DD</sub>        | 31   |

| LA18   | Address                        | P6                    | I/O         | BV <sub>DD</sub>        | 31   |

### **Pin Assignments and Reset States**

### Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply | Note |

|--------|--------------------|-----------------------|-------------|-----------------|------|

| GND064 | Ground             | V16                   | —           | —               | -    |

| GND063 | Ground             | V17                   | —           | —               | —    |

| GND062 | Ground             | V19                   | —           | —               | -    |

| GND061 | Ground             | V21                   | —           | —               | —    |

| GND060 | Ground             | V23                   | —           | —               | -    |

| GND059 | Ground             | V27                   | —           | _               | _    |

| GND058 | Ground             | W2                    | —           | _               | —    |

| GND057 | Ground             | W5                    | —           | —               | —    |

| GND056 | Ground             | W8                    | —           | _               | _    |

| GND055 | Ground             | W10                   | —           | _               | _    |

| GND054 | Ground             | W12                   | —           | _               | _    |

| GND053 | Ground             | W14                   | —           | —               | -    |

| GND052 | Ground             | W17                   | —           | —               | -    |

| GND051 | Ground             | W19                   | —           | —               | —    |

| GND050 | Ground             | W21                   | —           | —               | —    |

| GND049 | Ground             | W23                   | —           | —               | —    |

| GND048 | Ground             | Y6                    | —           | —               | _    |

| GND047 | Ground             | Y7                    | —           | —               | —    |

| GND046 | Ground             | Y8                    | —           | —               | —    |

| GND045 | Ground             | Y10                   | —           | —               | —    |

| GND044 | Ground             | Y12                   | —           | —               | —    |

| GND043 | Ground             | Y14                   | —           | —               | -    |

| GND042 | Ground             | Y16                   | —           | —               | -    |

| GND041 | Ground             | Y17                   | —           | —               | -    |

| GND040 | Ground             | Y19                   | —           | —               | _    |

| GND039 | Ground             | Y22                   | —           | —               | —    |

| GND038 | Ground             | AA5                   | —           | —               | _    |

| GND037 | Ground             | AA7                   | —           | —               | _    |

| GND036 | Ground             | AA17                  | —           | —               | _    |

| GND035 | Ground             | AA19                  | —           | —               | —    |

| GND034 | Ground             | AA24                  | —           | —               | -    |

| GND033 | Ground             | AA27                  | —           | —               | -    |

| GND032 | Ground             | AB2                   | —           | —               | —    |

| GND031 | Ground             | AB9                   | _           |                 | _    |

## Table 1. Pin List by Bus (continued)

| Signal      | Signal Description               | Package<br>Pin Number | Pin<br>Type | Power<br>Supply       | Note |

|-------------|----------------------------------|-----------------------|-------------|-----------------------|------|

| VDD_CA_PL50 | Core Group A and Platform Supply | L17                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL49 | Core Group A and Platform Supply | L19                   |             | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL48 | Core Group A and Platform Supply | M9                    |             | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL47 | Core Group A and Platform Supply | M11                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL46 | Core Group A and Platform Supply | M13                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL45 | Core Group A and Platform Supply | M15                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL44 | Core Group A and Platform Supply | M17                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL43 | Core Group A and Platform Supply | M19                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL42 | Core Group A and Platform Supply | N9                    | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL41 | Core Group A and Platform Supply | N11                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL40 | Core Group A and Platform Supply | N13                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL39 | Core Group A and Platform Supply | N15                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL38 | Core Group A and Platform Supply | N17                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL37 | Core Group A and Platform Supply | N19                   |             | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL36 | Core Group A and Platform Supply | P9                    | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL35 | Core Group A and Platform Supply | P11                   | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL34 | Core Group A and Platform Supply | P13                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL33 | Core Group A and Platform Supply | P15                   | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL32 | Core Group A and Platform Supply | P17                   | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL31 | Core Group A and Platform Supply | P19                   |             | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL30 | Core Group A and Platform Supply | R9                    | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL29 | Core Group A and Platform Supply | R11                   | —           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL28 | Core Group A and Platform Supply | R13                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL27 | Core Group A and Platform Supply | R15                   | —           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL26 | Core Group A and Platform Supply | R17                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL25 | Core Group A and Platform Supply | R19                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL24 | Core Group A and Platform Supply | Т9                    | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL23 | Core Group A and Platform Supply | T11                   | _           | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL22 | Core Group A and Platform Supply | T13                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL21 | Core Group A and Platform Supply | T15                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL20 | Core Group A and Platform Supply | T17                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL19 | Core Group A and Platform Supply | T19                   |             | $V_{DD\_CA\_PL}$      | 37   |

| VDD_CA_PL18 | Core Group A and Platform Supply | U9                    | _           | V <sub>DD_CA_PL</sub> | 37   |

| VDD_CA_PL17 | Core Group A and Platform Supply | U11                   | —           | V <sub>DD_CA_PL</sub> | 37   |

| IEEE 1588                                   | —              | LVdd (2.5V) | 0.004 | 0.005 | W | 1,3,6   |

|---------------------------------------------|----------------|-------------|-------|-------|---|---------|

| eLBC                                        | 32-bit, 100Mhz | BVdd (1.8V) | 0.048 | 0.120 | W | 1,3,6   |

|                                             |                | BVdd (2.5V) | 0.072 | 0.193 |   |         |

|                                             |                | BVdd (3.3V) | 0.120 | 0.277 |   |         |

|                                             | 16-bit, 100Mhz | BVdd (1.8V) | 0.021 | 0.030 | W | 1,3,6   |

|                                             |                | BVdd (2.5V) | 0.036 | 0.046 |   |         |

|                                             |                | BVdd (3.3V) | 0.057 | 0.076 |   |         |

| eSDHC                                       | —              | Ovdd (3.3V) | 0.014 | 0.150 | W | 1,3,6   |

| eSPI                                        | _              | CVdd (1.8V) | 0.004 | 0.005 | W | 1,3,6   |

|                                             |                | CVdd (2.5V) | 0.006 | 0.008 |   |         |

|                                             |                | CVdd (3.3V) | 0.010 | 0.013 |   |         |

| USB                                         | —              | USB_Vdd_3P3 | 0.012 | 0.015 | W | 1,3,6   |

| 12C                                         | —              | OVdd (3.3V) | 0.002 | 0.003 | W | 1,3,6   |

| DUART                                       | —              | OVdd (3.3V) | 0.006 | 0.008 | W | 1,3,6   |

| GPIO                                        | x8             | OVdd (1.8V) | 0.005 | 0.006 | W | 1,3,4,6 |

|                                             |                | OVdd (2.5V) | 0.007 | 0.009 |   |         |

|                                             |                | OVdd (3.3V) | 0.009 | 0.011 |   |         |

| thers (Reset, System<br>Clock, JTAG & Misc) | _              | OVdd (3.3V) | 0.003 | 0.015 | W | 1,3,4,6 |

### Table 7. P2040 I/O Power Supply Estimated Values (continued)

### Note:

1. The typical values are estimates and based on simulations at 65 °C.

2. Typical DDR power numbers are based on one 2-rank DIMM with 40% utilization.

3. Assuming 15 pF total capacitance load.

4. GPIO's are supported on 1.8 V, 2.5 V and 3.3 V rails as specified in the hardware specification.

5. Maximum DDR power numbers are based on one 2-rank DIMM with 100% utilization.

6. The maximum values are estimated and they are based on simulations at 105 °C. The values are not intended to be used as the maximum guranteed current.

7. The total power numbers of XVDD is dependent on customer application use case. This table lists all the SerDes configuration combination possible for the device. To get the XVDD power numbers, the user should add the combined lanes to match to the total SerDes lanes used, not simply multiply the power numbers by the number of lanes.

### Table 21. DDR3L SDRAM Interface DC Electrical Characteristics ( $GV_{DD}$ = 1.35 V) (continued)

For recommended operating conditions, see Table 3.

| Parameter | Symbol | Min | Max | Unit | Note |

|-----------|--------|-----|-----|------|------|

|-----------|--------|-----|-----|------|------|

### Note:

- 1. GV<sub>DD</sub> is expected to be within 50 mV of the DRAM's voltage supply at all times. The DRAM's and memory controller's voltage supply may or may not be from the same source.

- MV<sub>REF</sub>n is expected to be equal to 0.5 × GV<sub>DD</sub> and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub>n may not exceed the MV<sub>REF</sub>n DC level by more than ±1% of the DC value (that is, ±13.5 mV).

- V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made, and it is expected to be equal to MV<sub>REF</sub>n with a min value of MV<sub>REF</sub>n – 0.04 and a max value of MV<sub>REF</sub>n + 0.04. V<sub>TT</sub> should track variations in the DC level of MVREFn.

- 4. The voltage regulator for  $MV_{REF}n$  must meet the specifications stated in Table 23.

- 5. Input capacitance load for DQ, DQS, and DQS are available in the IBIS models.

- 6. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

- 7. Refer to the IBIS model for the complete output IV curve characteristics.

- 8.  $I_{OH}$  and  $I_{OL}$  are measured at  $GV_{DD} = 1.283$  V

This table provides the DDR controller interface capacitance for DDR3 and DDR3L.

### Table 22. DDR3 and DDR3L SDRAM Capacitance

For recommended operating conditions, see Table 3.

| Parameter                                       | Symbol           | Min | Мах | Unit | Note |

|-------------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS          | C <sub>IO</sub>  | 6   | 8   | pF   | 1, 2 |

| Delta input/output capacitance: DQ, DQS,<br>DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1, 2 |

Note:

- 1. This parameter is sampled.  $GV_{DD}$  = 1.5 V ± 0.075 V (for DDR3), f = 1 MHz, T<sub>A</sub> = 25 °C, V<sub>OUT</sub> =  $GV_{DD} \div 2$ , V<sub>OUT</sub> (peak-to-peak) = 0.150 V.

- 2. This parameter is sampled.  $GV_{DD} = 1.35 \text{ V} 0.067 \text{ V} \div + 0.100 \text{ V}$  (for DDR3L), f = 1 MHz, T<sub>A</sub> = 25 °C, V<sub>OUT</sub> =  $GV_{DD} \div 2$ , V<sub>OUT</sub> (peak-to-peak) = 0.167 V.

This table provides the current draw characteristics for MVREFn.

### Table 23. Current Draw Characteristics for MVREFn

For recommended operating conditions, see Table 3.

| Parameter                                       | Symbol         | Min | Мах | Unit | Note |

|-------------------------------------------------|----------------|-----|-----|------|------|

| Current draw for DDR3 SDRAM for MVREF <i>n</i>  | MVREF <i>n</i> | —   | 500 | μA   | _    |

| Current draw for DDR3L SDRAM for MVREF <i>n</i> | MVREF <i>n</i> | —   | 500 | μA   |      |

# 2.9.2 DDR3 and DDR3L SDRAM Interface AC Timing Specifications

This section provides the AC timing specifications for the DDR SDRAM controller interface. The DDR controller supports DDR3 and DDR3L memories. Note that the required  $GV_{DD}(typ)$  voltage is 1.5 V when interfacing to DDR3 SDRAM and the required  $GV_{DD}(typ)$  voltage is 1.35 V when interfacing to DDR3L SDRAM.

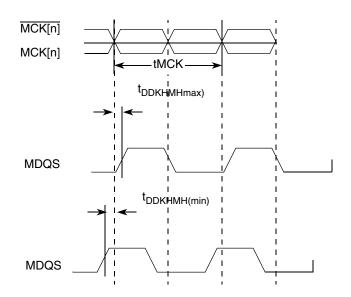

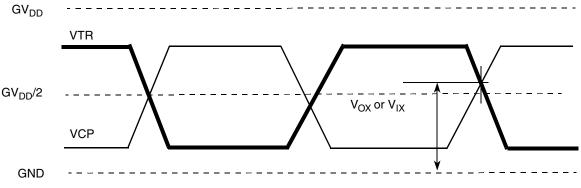

This figure shows the DDR3 and DDR3L SDRAM interface output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 10. t<sub>DDKHMH</sub> Timing Diagram

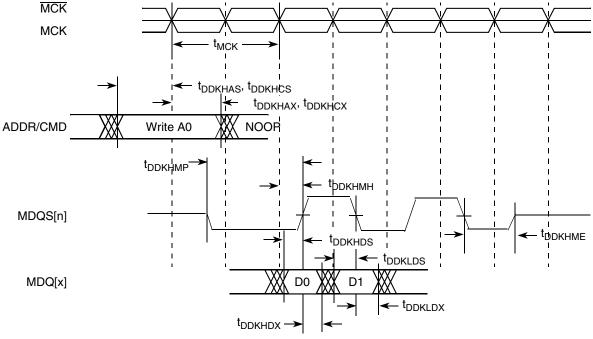

This figure shows the DDR3 and DDR3L SDRAM output timing diagram.

Figure 11. DDR3 and DDR3L Output Timing Diagram

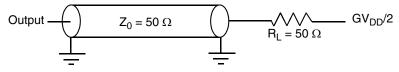

This figure provides the AC test load for the DDR3 and DDR3L controller bus.

Figure 12. DDR3 and DDR3L Controller Bus AC Test Load

# 2.9.2.3 DDR3 and DDR3L SDRAM Differential Timing Specifications

This section describes the DC and AC differential timing specifications for the DDR3 and DDR3L SDRAM controller interface. This figure shows the differential timing specification.

Figure 13. DDR3 and DDR3L SDRAM Differential Timing Specifications

### NOTE

VTR specifies the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as  $\overline{MCK}$  or  $\overline{MDQS}$ ).

This table provides the DDR3 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

### Table 28. DDR3 SDRAM Differential Electrical Characteristics<sup>1</sup>

| Parameter                                  | Symbol            | Min                       | Мах                       | Unit | Note |

|--------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| Input AC Differential Cross-Point Voltage  | V <sub>IXAC</sub> | $0.5\times GV_{DD}-0.150$ | $0.5\times GV_{DD}+0.150$ | V    | —    |

| Output AC Differential Cross-Point Voltage | V <sub>OXAC</sub> | $0.5\times GV_{DD}-0.115$ | $0.5\times GV_{DD}+0.115$ | V    | —    |

#### Note:

1. I/O drivers are calibrated before making measurements.

This table provides the DDR3L differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

### Table 29. DDR3L SDRAM Differential Electrical Characteristics<sup>1</sup>

| Parameter                                  | Symbol            | Min                       | Мах                         | Unit | Note |

|--------------------------------------------|-------------------|---------------------------|-----------------------------|------|------|

| Input AC differential cross-point voltage  | VIXAC             | $0.5\times GV_{DD}-0.135$ | $0.5 	imes GV_{DD} + 0.135$ | V    | —    |

| Output AC differential cross-point voltage | V <sub>OXAC</sub> | $0.5\times GV_{DD}-0.105$ | $0.5\times GV_{DD}+0.105$   | V    | —    |

#### Note:

1. I/O drivers are calibrated before making measurements.

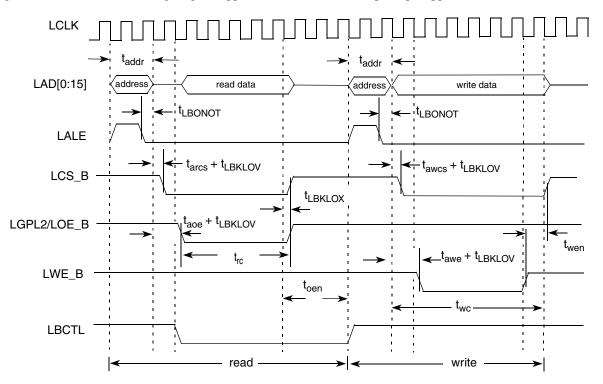

This figure shows how the AC timing diagram applies to GPCM. The same principle applies to UPM and FCM.

<sup>1</sup> t<sub>addr</sub> is programmable and determined by LCRR[EADC] and ORx[EAD].

$^{2}$   $t_{arcs}$ ,  $t_{awcs}$ ,  $t_{aoe}$ ,  $t_{rc}$ ,  $t_{oen}$ ,  $t_{awe}$ ,  $t_{wc}$ ,  $t_{wen}$  are determined by ORx. See the chip reference manual.

### Figure 22. GPCM Output Timing Diagram

# 2.15 Enhanced Secure Digital Host Controller (eSDHC)

This section describes the DC and AC electrical specifications for the eSDHC interface.

# 2.15.1 eSDHC DC Electrical Characteristics

This table provides the eSDHC electrical characteristics.

### Table 50. eSDHC Interface DC Electrical Characteristics

For recommended operating conditions, see Table 3.

| Characteristic               | Symbol                           | Condition                                            | Min                    | Мах                  | Unit | Note |

|------------------------------|----------------------------------|------------------------------------------------------|------------------------|----------------------|------|------|

| Input high voltage           | V <sub>IH</sub>                  | _                                                    | $0.625 \times CV_{DD}$ |                      | V    | 1    |

| Input low voltage            | V <sub>IL</sub>                  | —                                                    | —                      | $0.25\times CV_{DD}$ | V    | 1    |

| Input/output leakage current | I <sub>IN</sub> /I <sub>OZ</sub> | _                                                    | -50                    | 50                   | μA   | _    |

| Output high voltage          | V <sub>OH</sub>                  | I <sub>OH</sub> = −100 μA at<br>CV <sub>DD</sub> min | $0.75 \times CV_{DD}$  | _                    | V    |      |

The long run transmitter specifications use larger voltage swings that are capable of driving signals across backplanes. This allows a user to drive signals across two connectors and a backplane. The specifications allow a distance of at least 50 cm at all baud rates.

All unit intervals are specified with a tolerance of  $\pm 100$  ppm. The worst case frequency difference between any transmit and receive clock is 200 ppm.

To ensure interoperability between drivers and receivers of different vendors and technologies, AC coupling at the receiver input must be used.

# 2.20.5.1 Signal Definitions

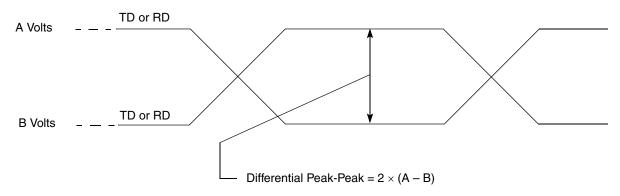

This section defines the terms used in the description and specification of the differential signals used by the LP-Serial links. This figure shows how the signals are defined. The figures show waveforms for either a transmitter output (TD and  $\overline{\text{TD}}$ ) or a receiver input (RD and  $\overline{\text{RD}}$ ). Each signal swings between A volts and B volts where A > B. Using these waveforms, the definitions are as follows:

- The transmitter output signals and the receiver input signals—TD, TD, RD, and RD—each have a peak-to-peak swing of A B volts.

- The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD} V_{\overline{TD}}$

- The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$

- The differential output signal of the transmitter and the differential input signal of the receiver each range from A B to -(A B) volts

- The peak value of the differential transmitter output signal and the differential receiver input signal is A B volts.

- The peak-to-peak value of the differential transmitter output signal and the differential receiver input signal is  $2 \times (A B)$  volts.

Figure 41. Differential Peak-Peak Voltage of Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V, and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5 V and 2.0 V. Using these values, the peak-to-peak voltage swing of the signals TD and  $\overline{\text{TD}}$  is 500 mV p-p. The differential output signal ranges between 500 mV and -500 mV. The peak differential voltage is 500 mV. The peak-to-peak differential voltage is 1000 mV p-p.

# 2.20.5.2 Equalization

With the use of high-speed serial links, the interconnect media causes degradation of the signal at the receiver and produces effects such as inter-symbol interference (ISI) or data-dependent jitter. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are as follows:

- Pre-emphasis on the transmitter

- A passive high-pass filter network placed at the receiver, often referred to as passive equalization.

• The use of active circuits in the receiver, often referred to as adaptive equalization.

# 2.20.5.3 Serial RapidIO Clocking Requirements for SD\_REF\_CLK*n* and SD\_REF\_CLK*n*

SerDes bank 1 (SD\_REF\_CLK1 and SD\_REF\_CLK1) may be used for various SerDes Serial RapidIO configurations based on the RCW configuration field SRDS\_PRTCL. Serial RapidIO is not supported on SerDes banks 2.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

# 2.20.5.4 DC Requirements for Serial RapidIO

This section explains the DC requirements for the Serial RapidIO interface.

# 2.20.5.4.1 DC Serial RapidIO Timing Transmitter Specifications

LP-Serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case is better than the following:

- $-10 \text{ dB for (Baud Frequency)} \div 10 < \text{Freq(f)} < 625 \text{ MHz}$

- $-10 \text{ dB} + 10\log(f \div 625 \text{ MHz}) \text{ dB}$  for  $625 \text{ MHz} \le \text{Freq}(f) \le \text{Baud}$  Frequency

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%–80% rise/fall time of the transmitter, as measured at the transmitter output, have a minimum value 60 ps in each case.

It is recommended that the timing skew at the output of an LP-Serial transmitter between the two signals that comprise a differential pair not exceed 20 ps at 2.50 GBaud and 15 ps at 3.125 GBaud and XX ps at 5 GBaud.

This table defines the transmitter DC specifications for Serial RapidIO operating at  $XV_{DD} = 1.5$  V or 1.8 V.

### Table 70. Serial RapidIO Transmitter DC Timing Specifications—2.5 GBaud, 3.125 GBaud, 5 GBaud

For recommended operating conditions, see Table 3.

| Parameter                             | Symbol              | Min   | Тур | Max  | Unit   | Note |

|---------------------------------------|---------------------|-------|-----|------|--------|------|

| Output voltage                        | V <sub>O</sub>      | -0.40 | _   | 2.30 | V      | 1    |

| Long-run differential output voltage  | V <sub>DIFFPP</sub> | 800   | _   | 1600 | mV p-p | _    |

| Short-run differential output voltage | V <sub>DIFFPP</sub> | 500   | _   | 1000 | mV p-p | —    |

Note:

1. Voltage relative to COMMON of either signal comprising a differential pair.

# 2.20.5.4.2 DC Serial RapidIO Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance results in a differential return loss better than 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times (Baud Frequency)$ . This includes contributions from on-chip circuitry, the chip package, and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100- $\Omega$  resistive for differential return loss and 25- $\Omega$  resistive for common mode.

### Table 83. Gen1i/1.5 G Transmitter (Tx) AC Specifications (continued)

For recommended operating conditions, see Table 3.

| Parameter | Symbol | Min | Тур | Мах | Unit | Note |  |

|-----------|--------|-----|-----|-----|------|------|--|

|-----------|--------|-----|-----|-----|------|------|--|

#### Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

### Table 84. Gen 2i/3 G Transmitter (Tx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                                                | Symbol                        | Min      | Тур      | Мах      | Unit   | Note |

|----------------------------------------------------------|-------------------------------|----------|----------|----------|--------|------|

| Channel speed                                            | t <sub>CH_SPEED</sub>         | —        | 3.0      | _        | Gbps   |      |

| Unit Interval                                            | T <sub>UI</sub>               | 333.2167 | 333.3333 | 335.1167 | ps     |      |

| Total jitter $f_{C3dB} = f_{BAUD} \div 10$               | U <sub>SATA_TXTJfB/10</sub>   | _        | _        | 0.3      | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 500$              | U <sub>SATA_TXTJfB/500</sub>  | —        | —        | 0.37     | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 1667$             | U <sub>SATA_TXTJfB/1667</sub> |          |          | 0.55     | UI p-p | 1    |

| Deterministic jitter,<br>$f_{C3dB} = f_{BAUD} \div 10$   | U <sub>SATA_TXDJfB/10</sub>   |          |          | 0.17     | UI p-p | 1    |

| Deterministic jitter,<br>$f_{C3dB} = f_{BAUD} \div 500$  | U <sub>SATA_TXDJfB/500</sub>  |          |          | 0.19     | UI p-p | 1    |

| Deterministic jitter,<br>$f_{C3dB} = f_{BAUD} \div 1667$ | U <sub>SATA_TXDJfB/1667</sub> | _        | _        | 0.35     | UI p-p | 1    |

#### Note:

1. Measured at Tx output pins peak-to-peak phase variation, random data pattern

# 2.20.7.4 AC Differential Receiver Input Characteristics

This table provides the Gen1i or 1.5 Gbits/s differential receiver input AC characteristics for the SATA interface. The AC timing specifications do not include RefClk jitter.

### Table 85. Gen 1i/1.5G Receiver (Rx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                              | Symbol                      | Min      | Typical  | Max      | Unit   | Note |

|----------------------------------------|-----------------------------|----------|----------|----------|--------|------|

| Unit Interval                          | T <sub>UI</sub>             | 666.4333 | 666.6667 | 670.2333 | ps     | _    |

| Total jitter data-data 5 UI            | U <sub>SATA_TXTJ5UI</sub>   |          | _        | 0.43     | UI p-p | 1    |

| Total jitter, data-data 250 UI         | U <sub>SATA_TXTJ250UI</sub> | —        | _        | 0.60     | UI p-p | 1    |

| Deterministic jitter, data-data 5 UI   | U <sub>SATA_TXDJ5UI</sub>   | —        | _        | 0.25     | UI p-p | 1    |

| Deterministic jitter, data-data 250 UI | U <sub>SATA_TXDJ250UI</sub> | —        | _        | 0.35     | UI p-p | 1    |

#### Note:

1. Measured at receiver.

This table provides the differential receiver input AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

Table 86. Gen 2i/3G Receiver (Rx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                                             | Symbol                        | Min      | Typical  | Мах      | Unit   | Note |

|-------------------------------------------------------|-------------------------------|----------|----------|----------|--------|------|

| Unit Interval                                         | T <sub>UI</sub>               | 333.2167 | 333.3333 | 335.1167 | ps     |      |

| Total jitter $f_{C3dB} = f_{BAUD} \div 10$            | U <sub>SATA_TXTJfB/10</sub>   |          |          | 0.46     | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 500$           | U <sub>SATA_TXTJfB/500</sub>  |          |          | 0.60     | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 1667$          | U <sub>SATA_TXTJfB/1667</sub> | —        |          | 0.65     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 10$   | U <sub>SATA_TXDJfB/10</sub>   | —        | —        | 0.35     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 500$  | U <sub>SATA_TXDJfB/500</sub>  | —        | —        | 0.42     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 1667$ | U <sub>SATA_TXDJfB/1667</sub> |          | —        | 0.35     | UI p-p | 1    |

Note:

1. Measured at receiver.

# 2.20.8 SGMII Interface

Each SGMII port features a 4-wire AC-coupled serial link from the SerDes interface of the device, as shown in Figure 44, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XGND. The reference circuit of the SerDes transmitter and receiver is shown in Figure 39.

# 2.20.8.0.1 SGMII Clocking Requirements for SD\_REF\_CLK*n* and SD\_REF\_CLK*n*

When operating in SGMII mode, the EC\_GTX\_CLK125 clock is not required for this port. Instead, a SerDes reference clock is required on SD\_REF\_CLK[1:2] and SD\_REF\_CLK[1:2] pins. SerDes banks 1–2 may be used for SerDes SGMII configurations based on the RCW Configuration field SRDS\_PRTCL.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

# 2.20.8.1 SGMII DC Electrical Characteristics

This section discusses the electrical characteristics for the SGMII interface.

# 2.20.8.1.1 SGMII Transmit DC Timing Specifications

This table describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics for 1.25 GBaud. Transmitter DC characteristics are measured at the transmitter outputs ( $SD_TXn$  and  $\overline{SD_TXn}$ ) as shown in Figure 45.

### Table 87. SGMII DC Transmitter Electrical Characteristics (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter           | Symbol          | Min                | Тур | Мах                                      | Unit | Note |

|---------------------|-----------------|--------------------|-----|------------------------------------------|------|------|

| Output high voltage | V <sub>OH</sub> | _                  | _   | 1.5 x IV <sub>OD</sub> I <sub>-max</sub> | mV   | 1    |

| Output low voltage  | V <sub>OL</sub> | $ V_{OD} _{min}/2$ | _   | —                                        | mV   | 1    |

# 3.1.2 Platform to SYSCLK PLL Ratio

This table shows the allowed platform clock-to-SYSCLK ratios.

The chip platform clock frequency is always below 666 MHz frequencies; set the RCW configuration field SYS\_PLL\_CFG = 0b01.

| Binary Value of SYS_PLL_RAT | Platform:SYSCLK Ratio |

|-----------------------------|-----------------------|

| 0_0100                      | 4:1                   |

| 0_0101                      | 5:1                   |

| 0_0110                      | 6:1                   |

| 0_0111                      | 7:1                   |

| 0_1000                      | 8:1                   |

| 0_1001                      | 9:1                   |

| All Others                  | Reserved              |

Table 94. Platform to SYSCLK PLL Ratios

# 3.1.3 e500mc Core Cluster to SYSCLK PLL Ratio

The clock ratio between SYSCLK and each of the two core cluster PLLs is determined at power up by the binary value of the RCW field CCn\_PLL\_RAT. This table describes the supported ratios. Note that a core cluster PLL frequency targeting 1 GHz and above must set RCW field CCn\_PLL\_CFG = 0b00 for frequency targeting below 1 GHz set CCn\_PLL\_CFG = 0b01.

This table lists the supported Core Cluster to SYSCLK ratios.

| Binary Value of CCn_PLL_RAT | Core Cluster:SYSCLK Ratio |

|-----------------------------|---------------------------|

| 0_1000                      | 8:1                       |

| 0_1001                      | 9:1                       |

| 0_1010                      | 10:1                      |

| 0_1011                      | 11:1                      |

| 0_1100                      | 12:1                      |

| 0_1101                      | 13:1                      |

| 0_1110                      | 14:1                      |

| 0_1111                      | 15:1                      |

| 1_0000                      | 16:1                      |

| 1_0001                      | 17:1                      |

| 1_0010                      | 18:1                      |

| All Others                  | Reserved                  |

Table 95. e500mc Core Cluster PLL to SYSCLK Ratios

#### Hardware Design Considerations

See Section 19.4 "LP-Serial Signal Descriptions," in the chip reference manual for Serial RapidIO interface width and frequency details.

# 3.1.7 SerDes PLL Ratio

The clock ratio between each of the three SerDes PLLs and their respective externally supplied SD\_REF\_CLK*n*/SD\_REF\_CLK*n* inputs is determined by the binary value of the RCW Configuration field SRDS\_RATIO\_B*n* as shown in this table. Furthermore, each SerDes lane grouping can be run at a SerDes PLL frequency divider determined by the binary value of the RCW field SRDS\_DIV\_B*n* as shown in Table 103.

This table lists the supported SerDes PLL Bank *n* to SD\_REF\_CLK*n* ratios.

| Binary Value of | SRDS_PLL_ <i>n</i> :SD_REF_CLK <i>n</i> Ratio |                       |  |  |  |

|-----------------|-----------------------------------------------|-----------------------|--|--|--|

| SRDS_RATIO_B1   | <i>n</i> = 1 (Bank)                           | <i>n</i> = 2 (Bank 2) |  |  |  |

| 000             | Reserved                                      | Reserved              |  |  |  |

| 001             | Reserved                                      | 20:1                  |  |  |  |

| 010             | 25:1                                          | 25:1                  |  |  |  |

| 011             | 40:1                                          | 40:1                  |  |  |  |

| 100             | 50:1                                          | 50:1                  |  |  |  |

| 101             | Reserved                                      | 24:1                  |  |  |  |

| 110             | Reserved                                      | 30:1                  |  |  |  |

| All Others      | Reserved                                      | Reserved              |  |  |  |

Table 101. SerDes PLL Bank *n* to SD\_REF\_CLK*n* Ratios

These tables list the supported SerDes PLL dividers.

This table shows the PLL divider support for each pair of lanes on SerDes Bank 1.

Table 102. SerDes Bank 1 PLL Dividers

| Binary Value of SRDS_DIV_B1[0:4] | SerDes Bank 1 PLL Divider  |

|----------------------------------|----------------------------|

| 0b0                              | Divide by 1 off Bank 1 PLL |

| 0b1                              | Divide by 2 off Bank 1 PLL |

Note: 1 bit (of 5 total SRDS\_DIV\_B1 bits) controls each pair of lanes.

This table shows the PLL dividers supported for each 4-lane for SerDes Banks 2.

Table 103. SerDes Banks 2 PLL Dividers

| Binary Value of SRDS_DIV_B2 | SerDes Bank 2 PLL Divider  |

|-----------------------------|----------------------------|

| 0b0                         | Divide by 1 off Bank 2 PLL |

| 0b1                         | Divide by 2 off Bank 2 PLL |

Note: 1 bit controls all four lanes of bank 2.

# 3.1.8 Frame Manager (FMan) Clock Select

The Frame Managers (FM) can each be synchronous to the platform.

#### Hardware Design Considerations

This table describes the clocking options that may be applied to each FM. The clock selection is determined by the binary value of the RCW clocking configuration fields FM\_CLK\_SEL.

| Binary Value of FM_CLK_SEL | FM Frequency                             |

|----------------------------|------------------------------------------|

| 0b0                        | Platform Clock Frequency /2              |

| 0b1                        | Core Cluster 2 Frequency /2 <sup>1</sup> |

Table 104. Frame Manager Clock Select

Notes:

<sup>1</sup> For asynchronous mode, max frequency, see Table 93.

# 3.2 Supply Power Default Setting

The device is capable of supporting multiple power supply levels on its I/O supplies. The I/O voltage select inputs, shown in Table 105, properly configure the receivers and drivers of the I/Os associated with the BVDD, CVDD, and LVDD power planes, respectively.

## WARNING

Incorrect voltage select settings can lead to irreversible device damage.

# 3.6.3 Guidelines for High-Speed Interface Termination

This section provides the guidelines for when the SerDes interface is either entirely unused or partly unused.

# 3.6.3.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected:

- SD\_TX[7:2], SD\_TX[13:10]

- <u>SD\_TX</u>[7:2], <u>SD\_TX</u>[13:10]

- SD\_IMP\_CAL\_RX

- SD\_IMP\_CAL\_TX

The following pins must be connected to SGND:

- SD\_RX[7:2], SD\_RX[13:10]

- <u>SD\_RX</u>[13:10], <u>SD\_RX</u>[13:10]

- SD\_REF\_CLK1, SD\_REF\_CLK2

- <u>SD\_REF\_CLK1</u>, <u>SD\_REF\_CLK2</u>

In the RCW configuration fields SRDS\_LPD\_B1 and SRDS\_LPD\_B2, all bits must be set to power down all the lanes in each bank.

RCW configuration field SRDS\_EN may be cleared to power down the SerDes block for power saving. Setting RCW[SRDS\_EN] = 0 power-downs the PLLs of both banks.

Additionally, software may configure SRDSBnRSTCTL[SDRD] = 1 for the unused banks to power down the SerDes bank PLLs to save power.

Note that both  $SV_{DD}$  and  $XV_{DD}$  must remain powered.

# 3.6.3.2 SerDes Interface Partly Unused

If only part of the high speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following unused pins must be left unconnected:

- $SD_TX[n]$

- $\overline{\text{SD}_{TX}}[n]$

The following unused pins must be connected to SGND:

- SD\_RX[*n*]

- $\overline{\text{SD}}_{RX}[n]$

- SD\_REF\_CLK1, <u>SD\_REF\_CLK1</u> (If entire SerDes bank 1 unused)

- SD\_REF\_CLK2, <u>SD\_REF\_CLK2</u> (If entire SerDes bank 2 unused)

In the RCW configuration field for each bank SRDS\_LPD\_B*n* with unused lanes, the respective bit for each unused lane must be set to power down the lane.

# 3.6.4 USB Controller Connections

This section details the hardware connections required for the USB controllers.

#### Hardware Design Considerations

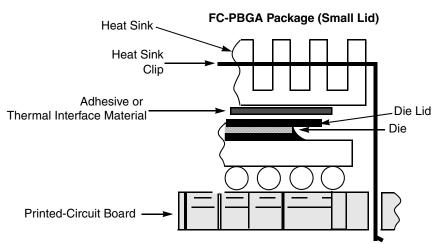

and thermal interface material. The recommended attachment method to the heat sink is illustrated in Figure 61. The heat sink must be attached to the printed-circuit board with the spring force centered over the die. This spring force should not exceed 10 pounds force (45 Newton).

Figure 61. Package Exploded Cross-Sectional View—FC-PBGA (w/ Lid) Package

The system board designer can choose between several types of heat sinks to place on the device. There are several commercially-available thermal interfaces to choose from in the industry. Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost.

# 3.8.1 Internal Package Conduction Resistance

For the package, the intrinsic internal conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-lid-top thermal resistance

- The die junction-to-board thermal resistance

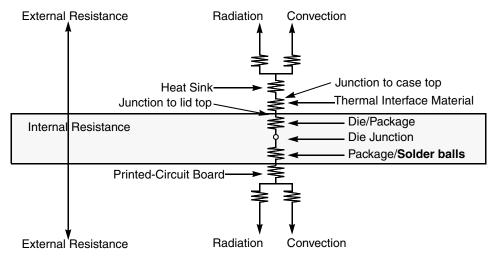

Figure 62 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

(Note the internal versus external package resistance)

### Figure 62. Package with Heat Sink Mounted to a Printed-Circuit Board

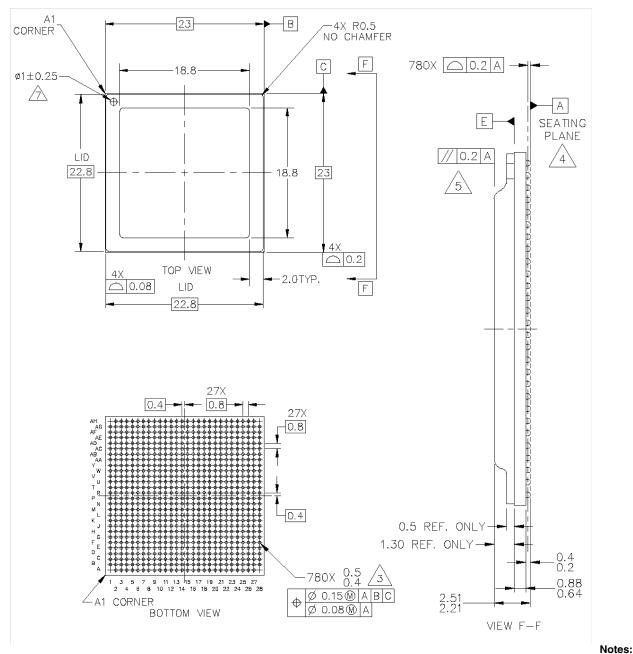

# 4.2 Mechanical Dimensions of the FC-PBGA

This figure shows the mechanical dimensions and bottom surface nomenclature of the device.

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement excludes any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

- 7. Pin 1 thru hole is centered within foot area.

### Figure 63. Mechanical Dimensions of the FC-PBGA with Full Lid